# 旬"A8396BH"供应商

PRELIMINARY

# 809XBH/839XBH/879XBH **COMMERCIAL/EXPRESS HMOS MICROCONTROLLER**

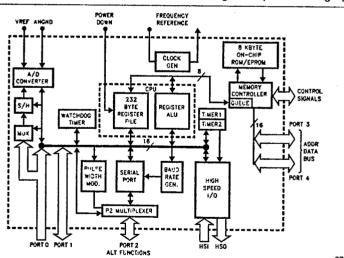

- 879XBH: an 809XBH with 8 Kbytes of On-Chip EPROM

- 839XBH: an 809XBH with 8 Kbytes of On-Chip ROM

- 232 Byte Register File

- Register-to-Register Architecture

- 10-Bit A/D Converter with S/H

- Five 8-Bit I/O Ports

- 20 Interrupt Sources

- **Pulse-Width Modulated Output**

- **ROM/EPROM Lock**

- Run-Time Programmable EPROM

- **Extended Temperature Available**

- High Speed I/O Subsystem

- Full Duplex Serial Port

- Dedicated Baud Rate Generator

- 6.25 μs 16 x 16 Multiply

- 6.25 µs 32/16 Divide

- 16-Bit Watchdog Timer

- Four 16-Bit Software Timers

- Two 16-Bit Counter/Timers

- Extended Burn-In Available

The MCS\*-96 family of 16-bit microcontrollers consists of many members, all of which are designed for highspeed control functions. The MCS-96 family members produced using Intel's HMOS-III process are described in this data sheet.

The CPU supports bit, byte, and word operations. Thirty-two bit double-words are supported for a subset of the instruction set. With a 12 MHz input frequency the 8096BH can do a 16-bit addition in 1.0 µs and a 16 x 16-bit multiply or 32/16 divide in 6.25  $\mu$ s. Instruction execution times average 1 to 2  $\mu$ s in typical applications.

Four high-speed trigger inputs are provided to record the times at which external events occur. Six high-speed pulse generator outputs are provided to trigger external events at preset times. The high-speed output unit can simultaneously perform software timer functions. Up to four 16-bit software timers can be in operation at once.

The on-chip A/D converter includes a Sample and Hold, and converts up to 8 multiplexed analog input channels to 10-bit digital values. With a 12 MHz crystal, each conversion takes 22 µs. This feature is only available on the 8X95BHs and 8X97BHs, with the 8X95BHs having 4 multiplexed analog inputs.

í

July 1992 Order Number: 270090-010 270090-50

# **8X9查**物"A8396BH"供应商

Also provided on-chip are a serial port, a Watchdog Timer and a pulse-width modulated output signal.

With the commercial (standard) temperature option, operational characteristics are guaranteed over the temperature range of 0°C to +70°C. With the extended temperature range option, operational characteristics are guaranteed over the temperature range of -40°C to +85°C. Unless otherwise noted, the specifications are the same for both options.

With the extended burn-in option, the burn-in is dynamic for a minimum time of 160 hours at 125°C with  $V_{CC} = 5.5V \pm 0.5V$ , following the guidelines in MIL-STD-883, Method 1015.

See the Packaging Information for extended temperature and extended burn-in designators.

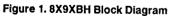

Figure 2. 8X9XBH Memory Map

### **PACKAGING**

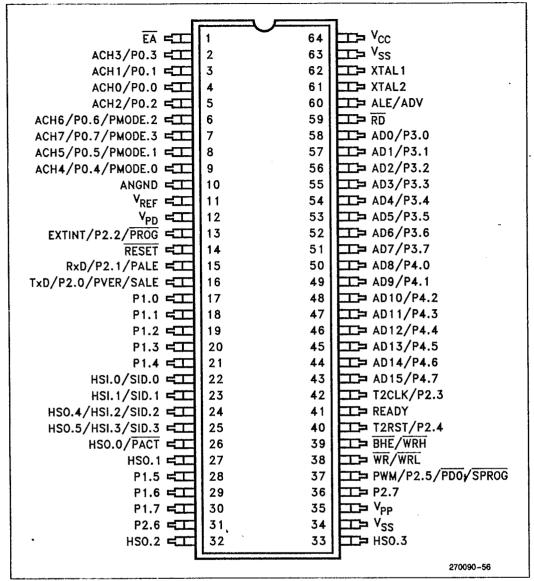

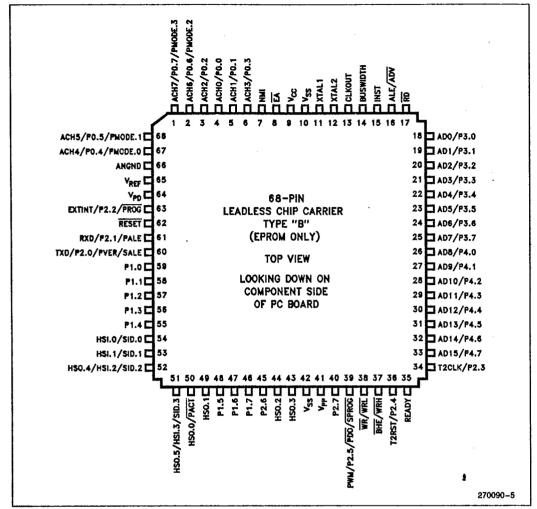

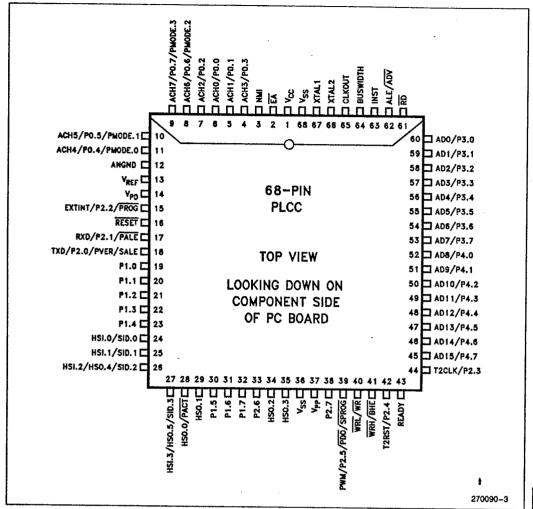

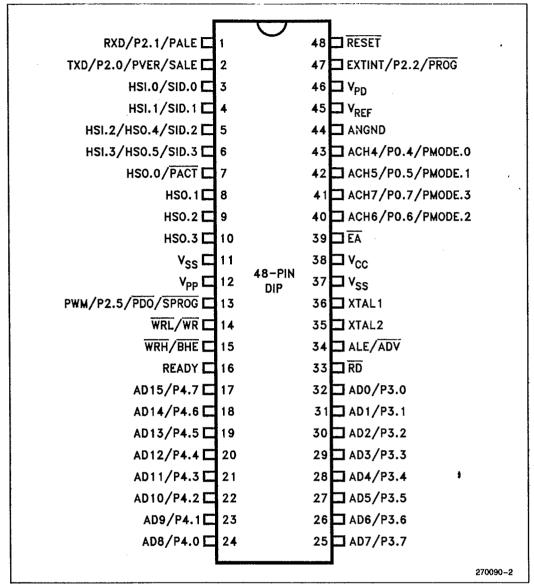

The 8096BH is available in 48-pin, 64-pin and 68-pin packages, with and without A/D, and with and without on-chip ROM or EPROM. The 8096BH numbering system is shown in Figure 3. Figures 5–10 show the pinouts for the 48-, 64- and 68-pin packages. The 48-pin version is offered in a Dual-In-Line package while the 68-pin versions come in a Plastic Leaded Chip Carrier (PLCC), a Pin Grid Array (PGA) or a Type "B" Leadless Chip Carrier.

|           | Factory Masked |        |        | CPU    |        |        | User Programmable |        |        |        |        |        |

|-----------|----------------|--------|--------|--------|--------|--------|-------------------|--------|--------|--------|--------|--------|

|           | ROM            |        |        |        | EPROM  |        | ОТР               |        |        |        |        |        |

|           | 68-Pin         | 64-Pin | 48-Pin | 68-Pin | 64-Pin | 48-Pin | 68-Pin            | 64-Pin | 48-Pin | 68-Pin | 64-Pin | 48-Pin |

| ANALOG    | 8397BH         | 8397BH | 8395BH | 8097BH | 8097BH | 8095BH | 8797BH            |        | 8795BH | 8797BH | 8797BH | l      |

| NO ANALOG | 8396BH         |        |        | 8096BH |        |        |                   |        |        |        |        |        |

Figure 3. 8X9X Packaging

Package Designators:

N = PLCC

C = Ceramic DIP

A = Ceramic Pin Grid Array

P = Plastic DIP

R = Ceramic LCC

U = Shrink DIP

| Prefix I | Designators: |

|----------|--------------|

|----------|--------------|

T = Extended Temperature

L = Extended Temperature with 160 Hours Burn-in

| Package Type    | $\theta_{ja}$ | θ <sub>jc</sub> |

|-----------------|---------------|-----------------|

| 68L PGA         | 35°C/W        | 10°C/W          |

| 68L PLCC        | 37°C/W        | 13°C/W          |

| 68L LCC         | 28°C/W        | 14°C/W          |

| 64L Shrink DIP  | 56°C/W        | _               |

| 48L Plastic DIP | 38°C/W        | 19°C/W          |

| 48L Ceramic DIP | 26°C/W        | 6.5°C/W         |

Figure 4. 8X9XBH Thermal Characteristics

All thermal impedance data is approximate for static air conditions at 1W of power dissipation. Values will change depending on operating conditions and application. See the Intel *Packaging Handbook* (Order Number 240800) for a description of Intel's thermal impedance test methodology.

# **8X9X查询**"A8396BH"供应商

Figure 5. 64-Pin Shrink-DIP Package

# Pins Facing Down

| 17    | 15 | 13  | 11           | 9     | 7    | 5  | 3  | 1  | 1  |

|-------|----|-----|--------------|-------|------|----|----|----|----|

| 18 19 | 16 | 14  | 12           | 10    | 8    | 6  | 4  | 2  | 68 |

| 20 21 |    |     |              |       |      |    |    | 67 | 66 |

| 22 23 |    |     |              | 3-P   |      |    |    | 65 | 64 |

| 24 25 |    | (   | SRID         | AR    | RAY  |    |    | 63 | 62 |

| 26 27 |    |     | TO           | )<br> | EW   |    |    | 61 | 60 |

| 28 29 |    | LOO |              |       |      |    |    | 59 | 58 |

| 30 31 |    |     | APOI<br>F PO |       |      |    |    | 57 | 56 |

| 32 33 |    | Ŭ   |              |       | , W. | •  |    | 55 | 54 |

| 34 36 | 38 | 40  | 42           | 44    | 46   | 48 | 50 | 53 | 52 |

| 35    | 37 | 39  | 41           | 43    | 45   | 47 | 49 | 51 |    |

270090-4

√ Figure 6. 68-Pin PGA Package

| PGA | Description       | PGA | Description        | PGA | Description        |

|-----|-------------------|-----|--------------------|-----|--------------------|

| 1   | ACH7/P0.7/PMODE.3 | 24  | AD6/P3.6           | 47  | P1.6               |

| 2   | ACH6/P0.6/PMODE.2 | 25  | AD7/P3.7           | 48  | P1.5               |

| 3   | ACH2/P0.2         | 26  | AD8/P4.0           | 49  | HSO.1              |

| 4   | ACH0/P0.0         | 27  | AD9/P4.1           | 50  | HSO.0/PACT         |

| 5   | ACH1/P0.1         | 28  | AD10/P4.2          | 51  | HSO.5/HSI.3/SID.3  |

| 6   | ACH3/P0.3         | 29  | AD11/P4.3          | 52  | HSO,4/HSI,2/SID,2  |

| 7   | NMI               | 30  | AD12/P4.4          | 53  | HSI,1/SID.1        |

| 8   | ĒĀ                | 31  | AD13/P4.5          | 54  | HSI.0/SID.0        |

| 9   | V <sub>CC</sub>   | 32  | AD14/P4.6          | 55  | P1.4 1             |

| 10  | V <sub>SS</sub>   | 33  | AD15/P4.7          | 56  | P1.3               |

| 11  | XTAL1             | 34  | T2CLK/P2.3         | 57  | P1.2               |

| 12  | XTAL2             | 35  | READY              | 58  | P1.1               |

| 13  | CLKOUT            | 36  | T2RST/P2.4         | 59  | P1.0               |

| 14  | BUSWIDTH          | 37  | BHE/WRH            | 60  | TXD/P2.0/PVER/SALE |

| 15  | INST              | 38  | WR/WRL             | 61  | RXD/P2.1/PALE      |

| 16  | ALE/ADV           | 39  | PWM/P2.5/PDO/SPROG | 62  | RESET              |

| 17  | RD                | 40  | P2.7               | 63  | EXTINT/P2.2/PROG   |

| 18  | AD0/P3.0          | 41  | Vpp                | 64  | V <sub>PD</sub>    |

| 19  | AD1/P3.1          | 42  | V <sub>SS</sub>    | 65  | V <sub>REF</sub>   |

| 20  | AD2/P3.2          | 43  | HSO.3              | 66  | ANGND              |

| 21  | AD3/P3.3          | 44  | HSO.2              | 67  | ACH4/P0.4/PMODE.0  |

| 22  | AD4/P3.4          | 45  | P2.6               | 68  | ACH5/P0.5/PMODE.1  |

|     |                   |     |                    |     |                    |

Figure 7. PGA Function Pinouts

P1.7

AD5/P3.5

BBE D

Figure 8. 68-Pin LCC Package

LBE D

Figure 9. 68-Pin PLCC Package

# **8X9套响**"A8396BH"供应商

# intel.

Figure 10. 48-Pin DIP Package

# PIN DESCRIPTIONS

| Symbol           | Name and Function                                                                                                                                                                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>  | Main supply voltage (5V).                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub>  | Digital circuit ground (0V). There are two VSS pins, both of which must be connected.                                                                                                                                                                                                                                          |

| V <sub>PD</sub>  | RAM standby supply voltage (5V). This voltage must be present during normal operation. In a Power Down condition (i.e. $V_{CC}$ drops to zero), if RESET is activated before $V_{CC}$ drops below spec and $V_{PD}$ continues to be held within spec., the top 16 bytes in the Register File will retain their contents.       |

| V <sub>REF</sub> | Reference voltage for the A/D converter (5V). V <sub>REF</sub> is also the supply voltage to the analog portion of the A/D converter and the logic used to read Port 0. Must be connected to use A/D or Port 0.                                                                                                                |

| ANGND            | Reference ground for the A/D converter. Must be held at nominally the same potential as $V_{\rm SS}$ .                                                                                                                                                                                                                         |

| V <sub>PP</sub>  | Programming voltage for the EPROM devices. It should be $\pm$ 12.75V for programming and will float to 5V otherwise. The pin should not be above $V_{CC}$ for ROM and CPU devices. This pin must be left floating in the application circuit for EPROM devices.                                                                |

| XTAL1            | Input of the oscillator inverter and of the internal clock generator.                                                                                                                                                                                                                                                          |

| XTAL2            | Output of the oscillator inverter.                                                                                                                                                                                                                                                                                             |

| CLKOUT*†         | Output of the internal clock generator. The frequency of CLKOUT is 1/3 the oscillator frequency. It has a 33% duty cycle.                                                                                                                                                                                                      |

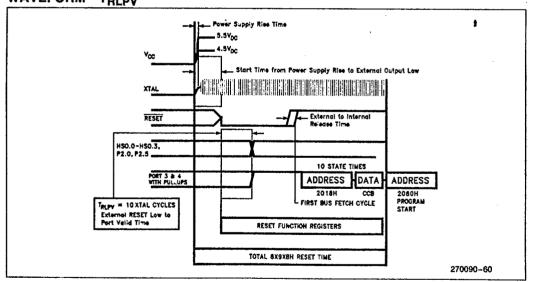

| RESET            | Reset input to the chip. Input low for a minimum 10 XTAL1 cycles to reset the chip. The subsequent low-to-high transition re-synchronizes CLKOUT and commences a 10-state-time RESET sequence.                                                                                                                                 |

| BUSWIDTH*†       | Input for bus width selection. If CCR bit 1 is a one, this pin selects the bus width for the bus cycle in progress. If BUSWIDTH is a 1, a 16-bit bus cycle occurs. If BUSWIDTH is a 0 an 8-bit cycle occurs. If CCR bit 1 is a 0, the bus is always an 8-bit bus. If this pin is left unconnected, it will rise to $V_{CC}$ .  |

| NMI*†            | A positive transition causes a vector to external memory location 0000H.                                                                                                                                                                                                                                                       |

| INST*†           | Output high during an external memory read indicates the read is an instruction fetch. INST is valid throughout the bus cycle.                                                                                                                                                                                                 |

| <u>EA</u>        | Input for memory select (External Access). EA equal to a TTL-high causes memory accesses to locations 2000H through 3FFFH to be directed to on-chip ROM/EPROM. EA equal to a TTL-low causes accesses to these locations to be directed to off-chip memory. EA equal to 12.75V causes the device to enter the Programming Mode. |

| ALE/ADV          | Address Latch Enable or Address Valid output, as selected by CCR. Both pin options provide a latch to demultiplex the address from the address/data bus. When the pin is ADV, it goes high at the end of the bus cycle. ALE/ADV is activated only during external memory accesses.                                             |

| ĀD               | Read signal output to external memory. RD is activated only during external memory reads.                                                                                                                                                                                                                                      |

| WA/WAL           | Write and Write Low output to external memory, as selected by the CCR. WR will go low for every external write, while WRL will go low only for external writes where an even byte is being written. WR/WRL is activated only during external memory writes.                                                                    |

| BHE/WRH          | Bus High Enable or Write High output to external memory, as selected by the CCR. BHE will go low for external writes to the high byte of the data bus. WRH will go low for external writes where an odd byte is being written. BHE/WRH is activated only during external memory writes.                                        |

# 8X9臺剛"A8396BH"供应商

# PIN DESCRIPTIONS (Continued)

| Symbol        | Name and Function                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READY         | Ready input to lengthen external memory cycles. If the pin is low prior to the falling edge of CLKOUT, the memory controller goes into a wait mode until the next positive transition of CLKOUT occurs with READY high. When the external memory is not being used, READY has no effect. Internal control of the number of wait states inserted into a bus cycle held not ready is available in the CCR. |

| HSI           | Inputs to High Speed Input Unit. Four HSI pins are available: HSI.0, HSI.1, HSI.2 and HSI.3. Two of them (HSI.2 and HSI.3) are shared with the HSO Unit.                                                                                                                                                                                                                                                 |

| HSO           | Outputs from High Speed Output Unit. Six HSO pins are available: HSO.0, HSO.1, HSO.2, HSO.3, HSO.4 and HSO.5. Two of them (HSO.4 and HSO.5) are shared with the HSI Unit.                                                                                                                                                                                                                                |

| Port 0‡       | 8-bit high impedance input-only port. These pins can be used as digital inputs and/or as analog inputs to the on-chip A/D converter.                                                                                                                                                                                                                                                                     |

| Port 1†       | 8-bit quasi-bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                      |

| Port 2†       | 8-bit multi-functional port. Six of its pins are shared with other functions in the 8096BH, the remaining 2 are quasi-bidirectional.                                                                                                                                                                                                                                                                     |

| Ports 3 and 4 | 8-bit bidirectional I/O ports with open drain outputs. These pins are shared with the multiplexed address/data bus which has strong internal pullups. Ports 3 and 4 are also used as a command, address and data path by EPROM devices operating in the Programming Mode.*                                                                                                                               |

| PMODE         | Determines the EPROM programming mode.                                                                                                                                                                                                                                                                                                                                                                   |

| PACT          | A low signal in Auto Programming Mode indicates that programming is in progress. A high signal indicates programming is complete.                                                                                                                                                                                                                                                                        |

| PVAL          | A low signal in Auto Programming Mode indicates that the device programmed correctly.                                                                                                                                                                                                                                                                                                                    |

| SALE          | A falling edge in Auto Programming Mode indicates that Ports 3 and 4 contain valid programming address/command information (output from master).                                                                                                                                                                                                                                                         |

| SPROG         | A falling edge in Auto Programming Mode indicates that Ports 3 and 4 contain valid programming data (output from master).                                                                                                                                                                                                                                                                                |

| SID           | Assigns a pin of Ports 3 and 4 to each slave to pass programming verification.                                                                                                                                                                                                                                                                                                                           |

| PALE          | A falling edge in Slave Programming Mode and Auto Configuration Byte Programming Mode indicates that Ports 3 and 4 contain valid programming address/command information (input to slave).                                                                                                                                                                                                               |

| PROG          | A falling edge in Slave Programming Mode indicates that Ports 3 and 4 contain valid programming data (input to slave).                                                                                                                                                                                                                                                                                   |

| PVER          | A high signal in Slave Programming Mode and Auto Configuration Byte Programming Mode indicates the byte programmed correctly.                                                                                                                                                                                                                                                                            |

| PVAL          | A high signal in Slave Programming Mode indicates the device programmed correctly.                                                                                                                                                                                                                                                                                                                       |

| PDO           | A low signal in Slave Programming Mode indicates that the PROG pulse was applied for longer than allowed.                                                                                                                                                                                                                                                                                                |

<sup>\*</sup>Not available on Shrink-DIP package †Not available on 48-pin device ‡Port 0.0.1.2.3 not available on 48-pin device

# **ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS\***

Ambient Temperature Under Bias -55°C to +125°C Storage Temperature .....-60°C to +150°C Voltage from EA or Vpp to VSS or ANGND ..... -0.3V to +13.0V Voltage from Any Other Pin to Vss or ANGND .....-0.3V to +7.0V(1) Average Output Current from Any Pin ...... 10 mA Power Dissipation<sup>(2)</sup> ......1.5W

NOTICE: This data sheet contains preliminary information on new products in production. It is valid for the devices indicated in the revision history. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### NOTES:

- 1. This includes Vpp and EA on ROM and CPU only devices.

- 2. Power dissipation is based on package heat transfer limitations, not device power consumption.

#### **OPERATING CONDITIONS**

(All characteristics in this data sheet apply to these operating conditions unless otherwise noted.)

| Symbol           | Parameter                                       | Min  | Max  | Units |

|------------------|-------------------------------------------------|------|------|-------|

| TA               | Ambient Temperature Under Bias Commercial Temp. | 0    | +70  | •c    |

| TA               | Ambient Temperature Under Bias Extended Temp.   | -40  | +85  | °C    |

| V <sub>CC</sub>  | Digital Supply Voltage                          | 4.50 | 5.50 | V     |

| V <sub>REF</sub> | Analog Supply Voltage                           | 4.50 | 5.50 | V     |

| Fosc             | Oscillator Frequency                            | 6.0  | 12   | MHz   |

| V <sub>PD</sub>  | Power-Down Supply Voltage                       | 4.50 | 5.50 | V     |

#### NOTE:

ANGND and VSS should be nominally at the same potential.

# DC CHARACTERISTICS

| Symbol           | Parameter                                              | Min  | Max  | Units | Test Conditions                       |

|------------------|--------------------------------------------------------|------|------|-------|---------------------------------------|

| lcc              | V <sub>CC</sub> Supply Current Commercial Temp.        |      | 240  | mA    | All Outputs                           |

| lcc              | V <sub>CC</sub> Supply Current Extended Temp.          |      | 270  | mA    | Disconnected.                         |

| I <sub>CC1</sub> | V <sub>CC</sub> Supply Current (T <sub>A</sub> ≥ 70°C) |      | 185  | mA    |                                       |

| IPD              | V <sub>PD</sub> Supply Current                         |      | 1    | mA    | Normal operation and Power-Down.      |

| I <sub>REF</sub> | V <sub>REF</sub> Supply Current Commercial Temp.       |      | 8    | mA    |                                       |

| IREF             | V <sub>REF</sub> Supply Current <b>Extended</b> Temp.  |      | 10   | mA    |                                       |

| VIL              | Input Low Voltage                                      | -0.3 | +0.8 | V     | · · · · · · · · · · · · · · · · · · · |

## DC CHARACTERISTICS (Continued)

| Symbol           | Parameter                                                                                | Min   | Max                   | Units | Test Conditions                             |

|------------------|------------------------------------------------------------------------------------------|-------|-----------------------|-------|---------------------------------------------|

| V <sub>IH</sub>  | Input High Voltage (Except RESET, NMI, XTAL1)                                            | 2.0   | V <sub>CC</sub> + 0.5 | ٧     |                                             |

| V <sub>IH1</sub> | Input High Voltage, RESET Rising                                                         | 2.4   | V <sub>CC</sub> + 0.5 | ٧     |                                             |

| V <sub>IH2</sub> | Input High Voltage, RESET Falling (Hysteresis)                                           | 2.1   | V <sub>CC</sub> + 0.5 | ٧     |                                             |

| V <sub>IH3</sub> | Input High Voltage, NMI, XTAL1                                                           | 2.2   | V <sub>CC</sub> + 0.5 | V     |                                             |

| lu               | Input Leakage Current to each pin of HSI, P3, P4, and to P2.1.                           |       | ±10                   | μΑ    | $V_{in} = 0$ to $V_{CC}$                    |

| l <sub>Ll1</sub> | DC Input Leakage Current to each pin of P0                                               |       | +3                    | μΑ    | $V_{in} = 0$ to $V_{CC}$                    |

| liH              | Input High Current to EA                                                                 |       | 100                   | μА    | V <sub>IH</sub> = 2.4V                      |

| IIL              | Input Low Current to each pin of P1, and to P2.6, P2.7 Commercial Temp.                  |       | -125                  | μΑ    | V <sub>IL</sub> = 0.45V                     |

| I <sub>IL</sub>  | Input Low Current to each pin of P1, and to P2.6, P2.7 Extended Temp.                    |       | -150                  | μΑ    | V <sub>IL</sub> = 0.45V                     |

| l <sub>IL1</sub> | Input Low Current to RESET                                                               | -0.25 | -2                    | mA    | $V_{IL} = 0.45V$                            |

| I <sub>IL2</sub> | Input Low Current P2.2, P2.3, P2.4, .<br>READY, BUSWIDTH                                 |       | -50                   | μA    | V <sub>IL</sub> = 0.45V                     |

| V <sub>OL</sub>  | Output Low Voltage on Quasi-<br>Bidirectional port pins and P3, P4 when<br>used as ports |       | 0.45                  | ٧     | I <sub>OL</sub> = 0.8 mA<br>(Note 1)        |

| V <sub>OL1</sub> | Output Low Voltage on Quasi-<br>Bidirectional port pins and P3, P4 when<br>used as ports |       | 0.75                  | ٧     | I <sub>OL</sub> = 2.0 mA<br>(Notes 1, 2, 3) |

| V <sub>OL2</sub> | Output Low Voltage on Standard<br>Output pins, RESET and Bus/Control<br>Pins             |       | 0.45                  | ٧     | I <sub>OL</sub> = 2.0 mA<br>(Notes 1, 2, 3) |

| VOH              | Output High Voltage on Quasi-<br>Bidirectional pins                                      | 2.4   |                       | ٧     | I <sub>OH</sub> = -20 μA<br>(Note 1)        |

| V <sub>OH1</sub> | Output High Voltage on Standard<br>Output pins and Bus/Control pins                      | 2.4   |                       | V.    | I <sub>OH</sub> = -200 μA<br>(Note 1)       |

| 10нз             | Output High Current on RESET                                                             | -50   |                       | μΑ    | V <sub>OH</sub> = 2.4V                      |

| Cs               | Pin Capacitance (Any Pin to V <sub>SS</sub> )                                            |       | 10                    | pF    | F <sub>TEST</sub> = 1.0 MHz                 |

3. During normal (non-transient) operation the following limits apply:

Total I<sub>OL</sub> on Port 1 must not exceed 8.0 mA.

Total I<sub>OL</sub> on P2.0, P2.6, RESET and all HSO pins must not exceed 15 mA.

Total I<sub>OL</sub> on Port 3 must not exceed 10 mA.

Total I<sub>OL</sub> on P2.5, P2.7, and Port 4 must not exceed 20 mA.

<sup>1.</sup> Quasi-bidirectional pins include those on P1, for P2.6 and P2.7. Standard Output Pins include TXD, RXD (Mode 0 only), PWM, and HSO pins. Bus/Control pins include CLKOUT, ALE, BHE, RD, WR, INST and AD0–15.

2. Maximum current per pin must be externally limited to the following values if V<sub>OL</sub> is held above 0.45V.

IoL on quasi-bidirectional pins and Ports 3 and 4 when used as ports: 4.0 mA

IoL on Bus/Control pins: 2.0 mA

2. Duise accomplication progration the following limits control.

# **AC CHARACTERISTICS**

Test Conditions: Load Capacitance on Output Pins = 80 pF

TIMING REQUIREMENTS (The system must meet these specifications to work with the 8X9XBH.)

| Symbol                   | Parameter                         | Min                     | Max                                     | Units |

|--------------------------|-----------------------------------|-------------------------|-----------------------------------------|-------|

| T <sub>CLYX</sub> (2, 3) | READY Hold after CLKOUT Edge      | 0(1)                    |                                         | ns    |

| TLLYV                    | End of ALE/ADV to READY Valid     |                         | 2 T <sub>OSC</sub> - 70                 | ns    |

| T <sub>LLYH</sub>        | End of ALE/ADV to READY High      | 2 T <sub>OSC</sub> + 40 | '4 T <sub>OSC</sub> 80                  | ns    |

| TYLYH                    | Non-Ready Time                    |                         | 1000                                    | ns    |

| T <sub>AVDV</sub> (4)    | Address Valid to Input Data Valid |                         | 5 T <sub>OSC</sub> - 120(5)             | ns    |

| T <sub>RLDV</sub>        | RD Active to Input Data Valid     |                         | 3 T <sub>OSC</sub> - 100 <sup>(5)</sup> | ns    |

| TRHDX                    | Data Hold after RD Inactive       | 0                       |                                         | ns    |

| TRHDZ                    | RD Inactive to Input Data Float   | 0                       | T <sub>OSC</sub> - 25                   | ns    |

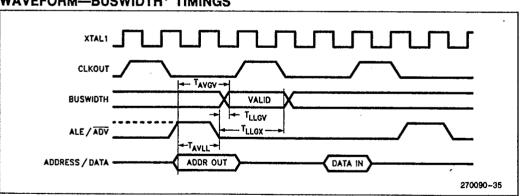

| T <sub>AVGV</sub> (2, 4) | Address Valid to BUSWIDTH Valid   |                         | 2 T <sub>OSC</sub> - 125                | ns    |

| T <sub>LLGX</sub> (2, 3) | BUSWIDTH Hold after ALE/ADV Low   | T <sub>OSC</sub> + 40   |                                         | ns    |

| T <sub>LLGV</sub> (2, 3) | ALE/ADV Low to BUSWIDTH Valid     |                         | T <sub>OSC</sub> - 75                   | ns    |

| TRLPV                    | Reset Low to Ports Valid          |                         | 10 T <sub>OSC</sub>                     | ns    |

# NOTES:

NOTES:

1. If the 48-pin or 64-pin device is being used then this timing can be generated by assuming that the CLKOUT falling edge has occurred at 2 T<sub>OSC</sub> + 55 (TLLCH(max) + TCHCL(max)) after the falling edge of ALE.

2. Pins not bonded out on 64-pin devices.

3. Pins not bonded out on 48-pin devices.

4. The term "Address Valid" applies to ADO-15, BHE and INST.

5. If wait states are used, add 3 T<sub>OSC</sub> \* N where N = number of wait states.

# 8X9季间"A8396BH"供应商

### TIMING RESPONSES (MCS-96 devices meet these specs.)

| Symbol                   | Parameter                                      | Min                        | Max                      | Units |

|--------------------------|------------------------------------------------|----------------------------|--------------------------|-------|

| FXTAL                    | Oscillator Frequency                           | 6.0                        | 12.0                     | MHz   |

| Tosc                     | Oscillator Period                              | 83                         | 166                      | ns    |

| TOHCH                    | XTAL1 Rising Edge to Clockout Rising Edge      | 0(4)                       | 120(4)                   | ns    |

| T <sub>CHCH</sub> (1, 4) | CLKOUT Period(3)                               | 3 T <sub>OSC</sub> (3)     | 3 T <sub>OSC</sub> (3)   | ns    |

| T <sub>CHCL</sub> (1, 4) | CLKOUT High Time                               | T <sub>OSC</sub> - 35      | T <sub>OSC</sub> + 10    | ns    |

| T <sub>CLLH</sub> (1, 4) | CLKOUT Low to ALE High                         | -30                        | +15                      | ns    |

| T <sub>LLCH</sub> (4)    | ALE/ADV Low to CLKOUT High(1)                  | T <sub>OSC</sub> - 25      | T <sub>OSC</sub> + 45    | ns    |

| T <sub>LHLL</sub>        | ALE/ADV High Time                              | T <sub>OSC</sub> - 30      | T <sub>OSC</sub> + 35(5) | ns    |

| T <sub>AVLL</sub> (6)    | Address Setup to End of ALE/ADV                | T <sub>OSC</sub> - 50      |                          | ns    |

| T <sub>RLAZ</sub> (7)    | RD or WR Low to Address Float Commercial Temp. | Typ. = 0                   | 10                       | ns    |

| T <sub>RLAZ</sub> (7)    | RD or WR Low to Address Float Extended Temp.   |                            | 25                       | ns    |

| TLLRL                    | End of ALE/ADV to RD or WR Active              | T <sub>OSC</sub> - 40      |                          | ns    |

| T <sub>LLAX</sub> (7)    | Address Hold after End of ALE/ADV              | T <sub>OSC</sub> - 40      |                          | ns    |

| TWLWH                    | WR Pulse Width                                 | 3 T <sub>OSC</sub> - 35(2) |                          | ns    |

| TQVWH                    | Output Data Valid to End of WR/WRL/WRH         | 3 T <sub>OSC</sub> - 60(2) |                          | ns    |

| TWHQX                    | Output Data Hold after WR/WRL/WRH              | T <sub>OSC</sub> 50        |                          | пѕ    |

| TWHLH                    | End of WR/WRL/WRH to ALE/ADV High              | T <sub>OSC</sub> - 75      |                          | ns    |

| TRLRH                    | RD Pulse Width                                 | 3 T <sub>OSC</sub> 30(2)   |                          | ns    |

| TRHLH                    | End of RD to ALE/ADV High                      | T <sub>OSC</sub> 45        |                          | ns    |

| T <sub>CLLL</sub> (4)    | CLOCKOUT Low(1) to ALE/ADV Low                 | T <sub>OSC</sub> - 40      | T <sub>OSC</sub> + 35    | ns    |

| T <sub>RHBX</sub> (4)    | RD High to INST(1), BHE, AD8-15 Inactive       | T <sub>OSC</sub> - 25      | T <sub>OSC</sub> + 30    | ns    |

| T <sub>WHBX</sub> (4)    | WR High to INST(1), BHE, AD8-15 Inactive       | T <sub>OSC</sub> 50        | T <sub>OSC</sub> + 100   | ns    |

| T <sub>HLHH</sub>        | WRL, WRH Low to WRL, WRH High                  | 2 T <sub>OSC</sub> - 35    | 2 T <sub>OSC</sub> + 40  | ns    |

| TLLHL                    | ALE/ADV Low to WRL, WRH Low                    | 2 T <sub>OSC</sub> - 30    | 2 T <sub>OSC</sub> + 55  | ns    |

| T <sub>QVHL</sub>        | Output Data Valid to WRL, WRH Low              | T <sub>OSC</sub> - 60      |                          | ns    |

### NOTES:

NOTES:

1. Pins not bonded out on 64-pin devices.

2. If more than one wait state is desired, add 3 T<sub>OSC</sub> for each additional wait state.

3. CLKOUT is directly generated as a divide by 3 of the oscillator. The period will be 3 T<sub>OSC</sub> ±10 ns if T<sub>OSC</sub> is constant and the rise and fall times on XTAL1 are less than 10 ns.

4. CLKOUT, INST, and BHE pins not bonded out on 48-pin and 64-pin devices.

5. Max spec applies only to ALE. Min spec applies to both ALE and ADV.

6. The term "Address Valid" applies to AD0-15, BHE and INST.

7. The term "Address" in this definition applies to AD0-7 for 8-bit cycles, and AD0-15 for 16-bit cycles.

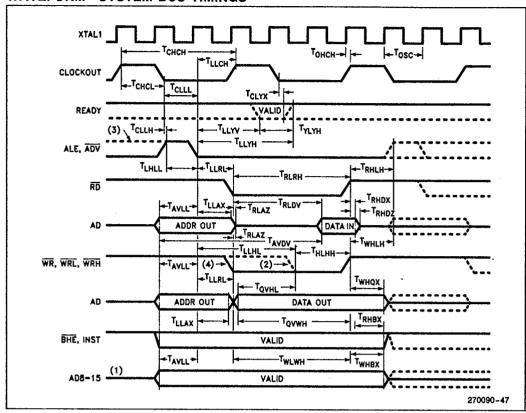

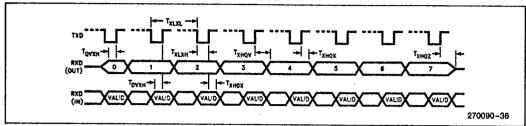

# **WAVEFORM—SYSTEM BUS TIMINGS**

- NOTES:

1. 8-bit bus only.

2. 8-bit or 16-bit bus and write strobe mode selected.

3. When ADV selected.

- 4. 8- or 16-bit bus and no write strobe mode selected.

# **WAVEFORM—BUSWIDTH\* TIMINGS**

\*Buswidth is not bonded out on 48- and 64-pin devices.

PRELIMINARY

# 8X9 查询"A8396BH"供应商

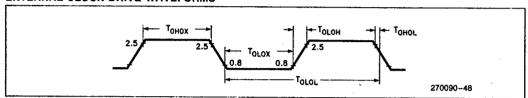

## **EXTERNAL CLOCK DRIVE**

| Symbol              | Parameter            | Min | Max | Units |

|---------------------|----------------------|-----|-----|-------|

| 1/T <sub>OLOL</sub> | Oscillator Frequency | 6   | 12  | MHz   |

| T <sub>OHOX</sub>   | High Time            | 25  |     | ns    |

| TOLOX               | Low Time             | 30  |     | ns    |

| T <sub>OLOH</sub>   | Rise Time            |     | 15  | ns    |

| TOHOL               | Fall Time            |     | 15  | ns    |

### **EXTERNAL CLOCK DRIVE WAVEFORMS**

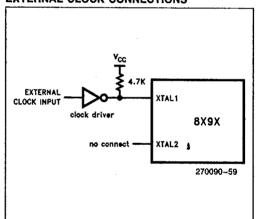

An external oscillator may encounter as much as a 100 pF load at XTAL1 when it starts up. This is due to interaction between the amplifier and its feedback capacitance. Once the external signal meets the VIL and VIH specifications the capacitance will not exceed 20 pF.

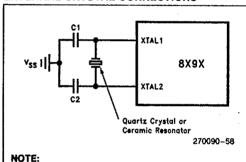

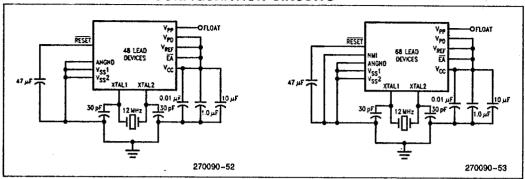

#### **EXTERNAL CRYSTAL CONNECTIONS**

Keep oscillator components close to chip and use short, direct traces to XTAL1, XTAL2 and V<sub>SS</sub>. When using crystals, C1 = 30 pF and C2 = 30 pF. When using ceramic resonators, consult manufacturerer for recommended capacitor values.

#### **EXTERNAL CLOCK CONNECTIONS**

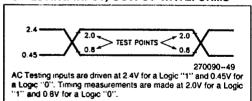

# AC TESTING INPUT, OUTPUT WAVEFORMS

# AC TESTING FLOAT WAVEFORMS

For Timing Purposes a Port Pin is no Longer Floating when a 200 mV change from Load Voltage Occurs, and Begins to Float when a 200 mV change from the Loaded V<sub>OH</sub>/V<sub>OL</sub> Level occurs IOL/IOH ≥ ±8 mA.

# MINIMUM HARDWARE CONFIGURATION CIRCUITS

# AC CHARACTERISTICS—SERIAL PORT—SHIFT REGISTER MODE

### SERIAL PORT TIMING-SHIFT REGISTER MODE

Test Conditions: Load Capacitance = 80 pF

| Symbol            | Parameter                                      | Min                      | Max                     | Units |

|-------------------|------------------------------------------------|--------------------------|-------------------------|-------|

| T <sub>XLXL</sub> | Serial Port Clock Period                       | 8 T <sub>OSC</sub>       |                         | ns    |

| T <sub>XLXH</sub> | Serial Port Clock Falling Edge to Rising Edge  | 4 T <sub>OSC</sub> - 50  | 4 T <sub>OSC</sub> + 50 | ns    |

| TQVXH             | Output Data Setup to Clock Rising Edge         | 3 T <sub>OSC</sub>       |                         | ns    |

| T <sub>XHQX</sub> | Output Data Hold After Clock Rising Edge       | 2 T <sub>OSC</sub> - 70  |                         | ns    |

| T <sub>XHQV</sub> | Next Output Data Valid After Clock Rising Edge |                          | 2 T <sub>OSC</sub> + 50 | ns    |

| T <sub>DVXH</sub> | Input Data Setup to Clock Rising Edge          | 2 T <sub>OSC</sub> + 200 |                         | ns    |

| T <sub>XHDX</sub> | Input Data Hold After Clock Rising Edge        | 0                        |                         | ns    |

| T <sub>XHQZ</sub> | Last Clock Rising to Output Float              |                          | 5 T <sub>OSC</sub>      | ns    |

# WAVEFORM-TRLPV

PRELIMINARY

68E D

**8X9查恂**"A8396BH"供应商

# WAVEFORM—SERIAL PORT—SHIFT REGISTER MODE

### SERIAL PORT WAVEFORM—SHIFT REGISTER MODE

### A/D CONVERTER SPECIFICATIONS

A/D Converter operation is verified only on the 8097BH, 8397BH, 8395BH, 8395BH, 8797BH, 8795BH.

The absolute conversion accuracy is dependent on the accuracy and stability of V<sub>REF</sub>.

See the MCS-96 A/D Converter Quick Reference for definitions of A/D Converter terms

| Parameter                                                              | Typical*                | Minimum                  | Maximum                  | Units**                    | Notes       |

|------------------------------------------------------------------------|-------------------------|--------------------------|--------------------------|----------------------------|-------------|

| Resolution                                                             |                         | 1024<br>10               | 1024<br>10               | Levels<br>Bits             |             |

| Absolute Error                                                         |                         | 0                        | ±4                       | LSBs                       |             |

| Full Scale Error                                                       | -0.5 ±0.5               |                          |                          | LSBs                       |             |

| Zero Offset Error                                                      | ±0.5                    |                          |                          | LSBs                       |             |

| Non-Linearity                                                          |                         | 0                        | ±4                       | LSBs                       |             |

| Differential Non-Linearity                                             |                         | >-1                      | +2                       | LSBs                       |             |

| Channel-to-Channel Matching                                            |                         | 0                        | ±1                       | LSBs                       |             |

| Repeatability                                                          | ±0.25                   |                          |                          | LSBs                       |             |

| Temperature Coefficients: Offset Full Scale Differential Non-Linearity | 0.009<br>0.009<br>0.009 |                          |                          | LSB/°C<br>LSB/°C<br>LSB/°C |             |

| Off Isolation                                                          |                         | -60                      |                          | dB                         | 1, 3        |

| Feedthrough                                                            | -60                     |                          |                          | dB                         | 1           |

| V <sub>CC</sub> Power Supply Rejection                                 | 60                      |                          |                          | dB                         | 1           |

| Input Series Resistance                                                |                         | 1K                       | 5K                       | Ω                          | 4           |

| DC Input Leakage                                                       |                         | 0                        | . 3.0                    | μΑ                         | <del></del> |

| Sample Delay                                                           |                         | 3 T <sub>OSC</sub> - 50  | 3 T <sub>OSC</sub> + 50  | ns                         | 2           |

| Sample Time                                                            |                         | 12 T <sub>OSC</sub> - 50 | 12 T <sub>OSC</sub> + 50 | ns                         |             |

| Sampling Capacitor                                                     |                         |                          | 2                        | ρF                         |             |

#### NOTES:

- \* These values are expected for most devices at 25°C.

- \*\* An "LSB", as used here, is defined in the MCS-96 A/D Converter Quick Reference and has a value of approximately 5 mV.

- 1. DC to 100 KHz.

- 2. For starting the A/D with an HSO Command.

- 3. Multiplexer Break-Before-Make Guaranteed.

- 4. Resistance from device pin, through internal MUX, to sample capacitor.

### **EPROM SPECIFICATIONS**

### **EPROM PROGRAMMING OPERATING CONDITIONS**

| Symbol                                                   | Parameter                                              | Min   | Max  | Units |

|----------------------------------------------------------|--------------------------------------------------------|-------|------|-------|

| TA                                                       | Ambient Temperature during Programming                 | 20    | 30   | °C    |

| V <sub>CC</sub> , V <sub>PD</sub> , V <sub>REF</sub> (1) | Supply Voltages during Programming                     | 4.5   | 5.5  | V     |

| VEA                                                      | Programming Mode Supply Voltage                        | 9.0   | 13.0 | V(2)  |

| V <sub>PP</sub>                                          | EPROM Programming Supply Voltage                       | 12.50 | 13.0 | V(2)  |

| V <sub>SS</sub> , ANGND(3)                               | Digital and Analog Ground                              | 0     | 0    | V     |

| F <sub>OSC</sub> 1                                       | Oscillator Frequency during Auto and Slave Programming | 6.0   | 6.0  | MHz   |

| F <sub>OSC</sub> 2                                       | Oscillator Frequency during Run-Time Programming       | 6.0   | 12.0 | MHz   |

NOTES:

1. V<sub>CC</sub>, V<sub>PD</sub> and V<sub>REF</sub> should nominally be at the same voltage during programming.

2. V<sub>EA</sub> and V<sub>PP</sub> must never exceed the maximum voltage for any amount of time or the device may be damaged.

3. V<sub>SS</sub> and ANGND should nominally be at the same voltage (0V) during programming.

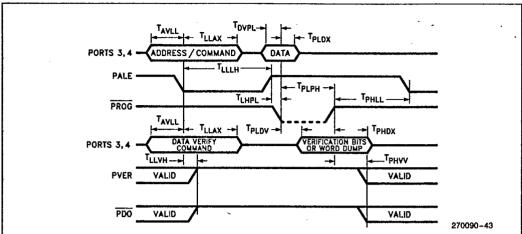

# **AC EPROM PROGRAMMING CHARACTERISTICS**

| Symbol            | Parameter                                | Min                  | Max                                     | Units  |

|-------------------|------------------------------------------|----------------------|-----------------------------------------|--------|

| TAVLL             | ADDRESS/COMMAND Valid to PALE Low        | a                    |                                         | Tosc   |

| T <sub>LLAX</sub> | ADDRESS/COMMAND Hold After PALE Low      | 80                   |                                         | Tosc   |

| T <sub>DVPL</sub> | Output Data Setup Before PROG Low        | 0                    |                                         | Tosc   |

| T <sub>PLDX</sub> | Data Hold After PROG Falling             | 80                   |                                         | Tosc   |

| T <sub>LLLH</sub> | PALE Pulse Width                         | 180                  |                                         | Tosc   |

| Трцрн             | PROG Pulse Width                         | 250 T <sub>OSC</sub> | 100 μs +<br>144 Tosc                    |        |

| TLHPL             | PALE High to PROG Low                    | 250                  |                                         | Tosc   |

| T <sub>PHLL</sub> | PROG High to Next PALE Low               | 600                  |                                         | Tosc   |

| T <sub>PHDX</sub> | Data Hold After PROG High                | 30                   |                                         | * Tosc |

| T <sub>PHVV</sub> | PROG High to PVER/PDO Valid              | 500                  |                                         | Tosc   |

| T <sub>LLVH</sub> | PALE Low to PVER/PDO High                | 100                  |                                         | Tosc   |

| T <sub>PLDV</sub> | PROG Low to VERIFICATION/DUMP Data Valid | 100                  | *************************************** | Tosc   |

| T <sub>SHLL</sub> | RESET High to First PALE Low (not shown) | 2000                 |                                         | Tosc   |

# DC EPROM PROGRAMMING CHARACTERISTICS

| Symbol | Parameter                                             | Min | Max | Units |

|--------|-------------------------------------------------------|-----|-----|-------|

| Ірр    | V <sub>PP</sub> Supply Current (Whenever Programming) |     | 100 | mA    |

# **8X%**間"A8396BH"供应商

# intel

### **WAVEFORM—EPROM PROGRAMMING**

#### **8X9XBH ERRATA**

Devices covered by this data sheet (see Revision History) have the following errata.

#### 1. INDEXED, 3 OPERAND MULTIPLY

The displacement portion of an indexed, three operand (byte or word) multiply may not be in the range of 200H thru 17FFH inclusive. If you must use these displacements, execute an indexed, two operand multiply and a move if necessary.

#### 2. HSI FIFO OPERATION

The High Speed Input (HSI) has three deviations from the specifications. Note that "events" are defined as one or more pin transitions. "Entries" are defined as the recording of one or more events.

- A. The resolution is nine states instead of eight states. Events occurring on the same pin more frequently than once every nine states may be lost.

- B. A mismatch between the nine state HSI resolution and the eight state hardware timer causes one time-lag value to be skipped every nine timer counts. Events may receive a time-tag one count later than expected.

- C. If the FIFO and Holding Register are empty, the first event will transfer into the Holding Register, leaving the FIFO empty again. The next event that occurs will be the first event loaded into the empty FIFO. If the first two events into an empty FIFO (not counting the Holding Register) occur coincident with each other, both are recorded as one entry with one time-tag. If the second event

occurs within 9 states after the first, the events will be entered separately with time-tags at least one count apart. If the second event enters the FIFO coincident with the "skipped" time-tag situation (see B above) the time tags will be at least two counts apart.

#### 3. RESERVED LOCATION 2019H

The 1990 Architectural Overview recommended that address 2019H be loaded with 0FFH. The recommendation is now 20H.

## 4. RESERVED LOCATION 201CH

Reading reserved location 201CH, either internally or externally, will return "201C" as data.

#### 5. SERIAL PORT SECTION

Serial Port Flags—Reading SP\_STAT may not clear the TI or RI flag if that flag was set within two state times prior to the read. In addition, the parity error bit (RPE/RB8) may not be correct if it is read within two state times after RI is set. Use the following code to replace ORB sp\_image, SP\_STAT.

SP\_READ: LDB TEMP, SP\_STAT

ORB SP\_IMAGE, TEMP

JBS TEMP,5,SP\_READ; if TI is

set then read again

JBS TEMP,6,SP\_READ; if RI is

set then read again

ANDB SP\_IMAGE,#7FH; clear

false RB8/RPE

ORB SP\_IMAGE, TEMP; load

correct RB8/RPE

7-20

# int。 (Page 18396BH"供应商

#### **DATA SHEET REVISION HISTORY**

This data sheet (270090-010) is valid for devices marked with an "E" at the end of the topside tracking number. Data sheets are changed as new device information becomes available. Verify with your local Intel sales office that you have the latest version before finalizing a design or ordering devices.

The difference between this data sheet (-010) and the previous one (-009) is the  $I_{OL}/I_{OH}$  for float waveform testing changed from  $\pm 15$  mA to  $\pm 8$  mA (this data sheet).

The following differences exist between (-009) data sheet and (-008).

- The Express (extended temperature and burn-in options) were added to this data sheet. The 8X9XBH Express data sheet (270433-004) is now obsolete.

- Changes were made to the format of the data sheet and the SFR descriptions were removed. No specification changes made.

- 3. Added Reserved Location 201CH errata.

The following differences exist between the -008 data sheet and the -007 data sheet.

- The -007 data sheet was valid for devices marked with a "D" at the end of the top side tracking number.

- The following errata were removed: RESET and the Quasi-Bidirectional Ports, Software RESET Timing, and Using T2CLK as the source for Timer2.

- The HSI FIFO Operation errata definition was changed to match change in the HSI FIFO Operation.

The following differences exist between the -007 data sheet and the -006 data sheet.

- 1. T<sub>CCLH</sub> changed from Min = -20 ns, Max = +25 ns to Min = -30 ns, Max = +15 ns.

- 2. T<sub>XHQX</sub> changed from Min = 2 T<sub>OSC</sub> 50 ns to Min = 2 T<sub>OSC</sub> 70 ns.

- T<sub>OLOX</sub> changed from Min = 25 ns to Min = 30 ns.

- An errata was added changing the recommendation for address 2019H from 0FFH to 20H.

- The power supply sequencing section has been deleted. The information is in the Hardware Design Information.

- The method of identifying the current change indicator was added to the differences between the -005 and -004 data sheets.

8X9XBH

7. A bug was not documented in the -004 data sheet and was fixed before the -005 data sheet. Information on the bug was added to the difference between the -005 and -004 data sheets.

Differences between -006 and -005 data sheets.

- All EPROM programming mode information has been deleted and moved to the Hardware Design Information chapter.

- 2. Shrink-DIP package information has been added.

- A new RESET timing specification has been added for clarity.

- Software Reset pin timing information has been added.

- HSO I<sub>OL</sub> specifications have been improved so that all HS0 pins have the same drive capability.

- Port 3 and Port 4 pin descriptions were clarified, indicating the necessity of pullup if the pins are used as ports.

- 7. HSI FIFO overflow description added.

Differences between the -005 and the -004 data sheets.

- The -005 data sheet corresponds to devices marked with a "D" at the end of the topside tracking number. The -004 data sheet corresponded to devices which are not marked with a "D".

- Much of the description of device functionality has been deleted. All of this information is already in the MCS-96 Architectural Overview.

- The A/D converter specification for Differential Non-linearity has been changed to be a minimum of > −1 lsbs to a maximum of +2 LSBs.

- 4. 8X9XBH errata section. The JBS and JBC on Port 0 errata has been fixed on the latest device stepping.

- 8X9XBH errata section. The errata for the 48-pin devices has been fixed on the latest device stepping. This errata caused the upper 8 bits on the Address/Data bus to be latched when resetting into an 8-bit external memory system.

- 6. 8X9XBH errata section. An errata existed which caused the device to be held in RESET for extended periods of time with the internal RESET pin pulled down internally. The condition occurred when the XTAL inputs were driven before V<sub>CC</sub> was stable and within the data sheet specification. The condition was worse at cold. This errata was not documented in the -004 data sheet. It has been fixed on the latest device stepping.

- 8X9XBH errata section. Errata 3 and 4 have been added to the errata list. These errata exist for all steppings of the device.

# **8x9查询**"A8396BH"供应商

Differences between the -004 and the -003 data

- 1. The bus control figures and bus timing diagrams were modified to more accurately describe their operation. In particular the 8-bit bus modes now reflect the use of Write Strobe Mode.

- 2. Additional text was added to the Analog/Digital description of the conversion process to clarify its operation and usefulness.

- 3. Text was added to the interrupt description section to indicate the maximum transition speed of the input signal relative to the CPU's state timing. A figure was included to graphically demonstrate the interrupt response timing.

- 4. The pin descriptions were modified to indicate that Vpp must normally float in the application.

- 5. The input low voltage specification (V<sub>IL1</sub>) was deleted and is covered by the ViL specification.

- 6. A suggested minimum configuration circuit was added to the material.

- 7. The A/D Converter Specifications for Differential Non-Linearity has been corrected to be a maximum of +2 LSB's.

- 8. The EPROM programming section figures were corrected to indicate the correct interface to a 2764A-2. A reset circuit was added to these figures and the signal PVAL (Port 3.X and Port 4.X) is now identified as the valid signal for program verification in the Auto Programming Mode. Text was added to this section to reference the requirement of using the Auto Configuration Byte Programming Mode for 48-lead devices. Figure 22A was edited for corrections to the text, and now indicates PVER (Port 2.0). The EPROM circuits were corrected to show 6 MHz operation for programming devices from internal microcode.

- 9. The protected memory section was edited to indicate that the CPU will enter a "JUMP ON SELF" condition when ROM/EPROM dump mode is complete.

- 10. An 8X9XBH ERRATA section was added.

- 11. This REVISION HISTORY was added.