February 1999

#### LM4755

# **Stereo 11W Audio Power Amplifier with Mute**

#### **General Description**

The LM4755 is a stereo audio amplifier capable of delivering 11W per channel of continuous average output power to a  $4\Omega$  load or 7W per channel into  $8\Omega$  using a single 24V supply at 10% THD+N. The internal mute circuit and pre-set gain resistors provide for a very economical design solution.

Output power specifications at both 20V and 24V supplies and low external component count offer high value to consumer electronic manufacturers for stereo TV and compact stereo applications. The LM4755 is specifically designed for single supply operation.

#### **Key Specifications**

- Output power at 10% THD with 1 kHz into  $4\Omega$  at  $V_{CC} = 24V 11W(typ)$

- Output power at 10% THD with 1 kHz into  $8\Omega$  at  $V_{CC}$  = 24V 7W(typ)

- Closed loop gain 34 dB(typ)

- P<sub>O</sub> at 10% THD @ 1 kHz into 4Ω single-ended TO-263 pkg. at V<sub>CC</sub>=12V 2.5W(typ)

$\blacksquare$  P  $_{\rm O}$  at 10% THD @ 1 kHz into 8Ω bridged TO-263 pkg. at V  $_{\rm CC}$  =12V  $\,$  5W(typ)

#### **Features**

- Drives  $4\Omega$  and  $8\Omega$  loads

- Integrated mute function

- Internal Gain Resistors

- Minimal external components needed

- Single supply operation

- Internal current limiting and thermal protection

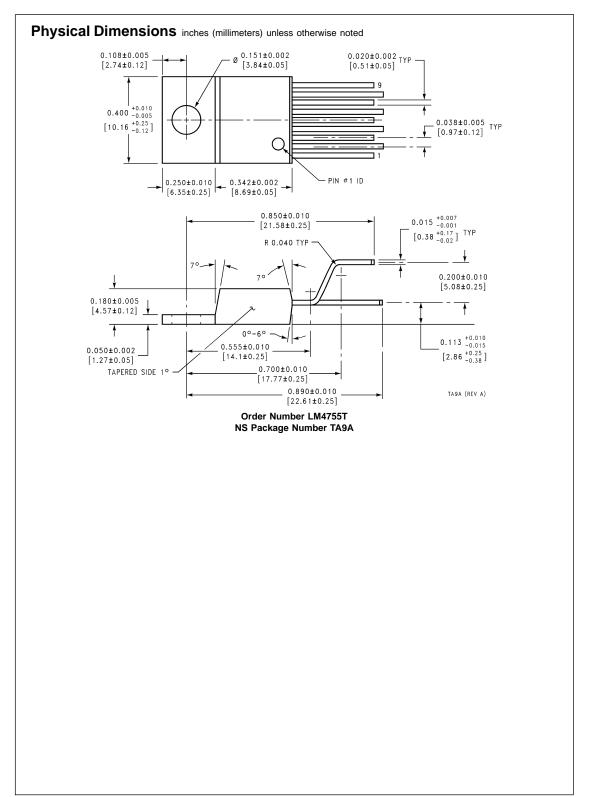

- Compact 9-lead TO-220 package

## **Applications**

■ Stereos TVs

DS100059-1

- Compact stereos

- Mini component stereos

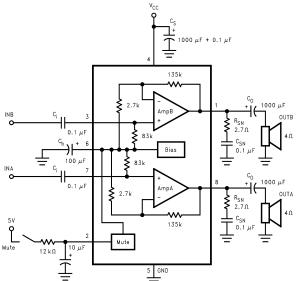

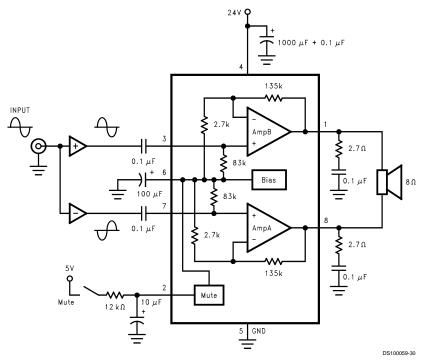

# **Typical Application**

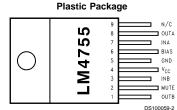

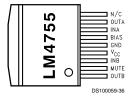

## **Connection Diagrams**

FIGURE 1. Typical Audio Amplifier Application Circuit

Package Description Top View Order Number LM4755T Package Number TA09A

Top View

Order Number LM4755TS

Package Number TS9A

#### **Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 40V

Input Voltage ±0.7V

Output Current Internally Limited

Power Dissipation (Note 3) 62.5W ESD Susceptability (Note 4) 2 kV Junction Temperature 150°C

Soldering Information

T Package (10 seconds) 250°C Storage Temperature -40°C to 150°C

### **Operating Ratings**

Temperature Range

$$\begin{split} T_{MIN} &\leq T_{A} \leq T_{MAX} & -40 \,^{\circ}\text{C} \leq T_{A} \leq +85 \,^{\circ}\text{C} \\ \text{Supply Voltage} & 9\text{V to } 32\text{V} \\ \theta_{\text{JC}} & 2 \,^{\circ}\text{C/W} \\ \theta_{\text{JA}} & 76 \,^{\circ}\text{C/W} \end{split}$$

#### **Electrical Characteristics**

The following specifications apply to each channel with  $V_{CC}$  = 24V,  $T_A$  = 25°C unless otherwise specified.

| Symbol                 | Parameter                                | Conditions                                                                           | LM4755              |       | l la ita          |

|------------------------|------------------------------------------|--------------------------------------------------------------------------------------|---------------------|-------|-------------------|

|                        |                                          |                                                                                      | Typical<br>(Note 5) | Limit | Units<br>(Limits) |

| I <sub>TOTAL</sub>     | Total Quiescent Power                    | Mute Off                                                                             | 10                  | 15    | mA(max)           |

|                        | Supply Current                           |                                                                                      |                     | 7     | mA(min)           |

|                        |                                          | Mute On                                                                              | 7                   |       | mA                |

| Po                     | Output Power (Continuous                 | $f = 1 \text{ kHz}, \text{ THD+N} = 10\%, R_L = 8\Omega$                             | 7                   |       | W                 |

|                        | Average per Channel)                     | $f = 1 \text{ kHz}, \text{ THD+N} = 10\%, R_L = 4\Omega$                             | 11                  | 10    | W(min)            |

|                        |                                          | $V_S = 20V, R_L = 8\Omega$                                                           | 4                   |       | W                 |

|                        |                                          | $V_S = 20V, R_L = 4\Omega$                                                           | 7                   |       | w                 |

|                        |                                          | $f = 1 \text{ kHz}, THD+N = 10\%, R_L = 4\Omega$<br>$V_S = 12V, TO-263 \text{ Pkg}.$ | 2.5                 |       | w                 |

| THD                    | Total Harmonic Distortion                | $f = 1 \text{ kHz}, P_O = 1 \text{ W/ch}, R_L = 8\Omega$                             | 0.08                |       | %                 |

| V <sub>osw</sub>       | Output Swing                             | $P_O = 10W, R_L = 8\Omega$                                                           | 15                  |       | V                 |

|                        |                                          | $P_O = 10W, R_L = 4\Omega$                                                           | 14                  |       | V                 |

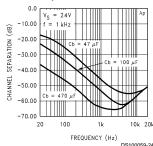

| X <sub>TALK</sub>      | Channel Separation                       | See Apps. Circuit                                                                    | 55                  |       | dB                |

|                        |                                          | f = 1 kHz, V <sub>O</sub> = 4 Vrms                                                   |                     |       |                   |

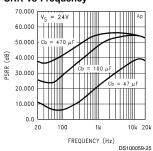

| PSRR                   | Power Supply Rejection Ratio             | See Apps. Circuit                                                                    | 50                  |       | dB                |

|                        |                                          | $f = 120 \text{ Hz}, V_O = 1 \text{ mVrms}$                                          |                     |       |                   |

| V <sub>ODV</sub>       | Differential DC Output Offset<br>Voltage | V <sub>IN</sub> = 0V                                                                 | 0.09                | 0.4   | V(max)            |

| SR                     | Slew Rate                                |                                                                                      | 2                   |       | V/µs              |

| R <sub>IN</sub>        | Input Impedance                          |                                                                                      | 83                  |       | kΩ                |

| PBW                    | Power Bandwidth                          | 3 dB BW at $P_O$ = 2.5W, $R_L$ = $8\Omega$                                           | 65                  |       | kHz               |

| A <sub>VCL</sub>       | Closed Loop Gain                         | $R_L = 8\Omega$                                                                      | 34                  | 33    | dB(min)           |

|                        | (Internally Set)                         |                                                                                      |                     | 35    | dB(max)           |

| $\epsilon_{\text{IN}}$ | Noise                                    | IHF-A Weighting Filter, $R_L = 8\Omega$<br>Output Referred                           | 0.2                 |       | mVrms             |

| Io                     | Output Short Circuit Limit               | $V_{IN} = 0.5V, R_L = 2\Omega$                                                       |                     | 2     | A(min)            |

| Mute Pin               | Mute Low Input Voltage                   | Not in Mute Mode                                                                     |                     | 0.8   | V(max)            |

| V <sub>IH</sub>        | Mute High Input Voltage                  | In Mute Mode                                                                         | 2.0                 | 2.5   | V(min)            |

| A <sub>M</sub>         | Mute Attenuation                         | V <sub>MUTE</sub> = 5.0V                                                             | 80                  |       | dB                |

| ' 'M                   | mato / ttoridation                       | *MUTE - 0.0 V                                                                        |                     |       |                   |

Note 1: All voltages are measured with respect to the GND pin (5), unless otherwse specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 3: For operating at case temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and a thermal resistance of  $\theta_{JC} = 2$ °C/W (junction to case). Refer to the section Determining the Maximum Power Dissipation in the Application Information section for more information.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

# **Electrical Characteristics** (Continued)

Note 5: Typicals are measured at 25°C and represent the parametric norm.

Note 6: Limits are guaranteed that all parts are tested in production to meet the stated values.

Note 7: The TO-263 Package is not recommended for  $V_S > 16V$  due to impractical heatsinking limitations.

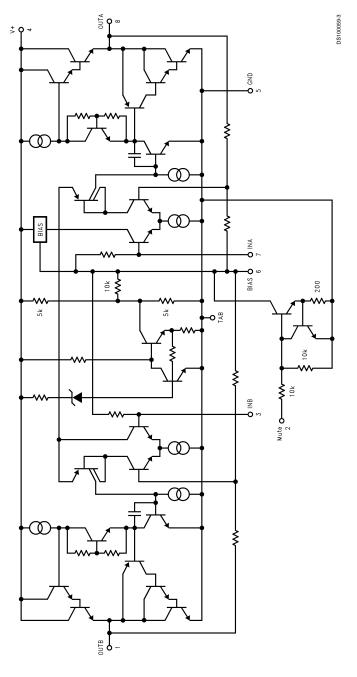

# **Equivalent Schematic**

# System Application Circuit VCC $C_S$ $1000 \mu F + 0.1 \mu F$ $C_S$ C

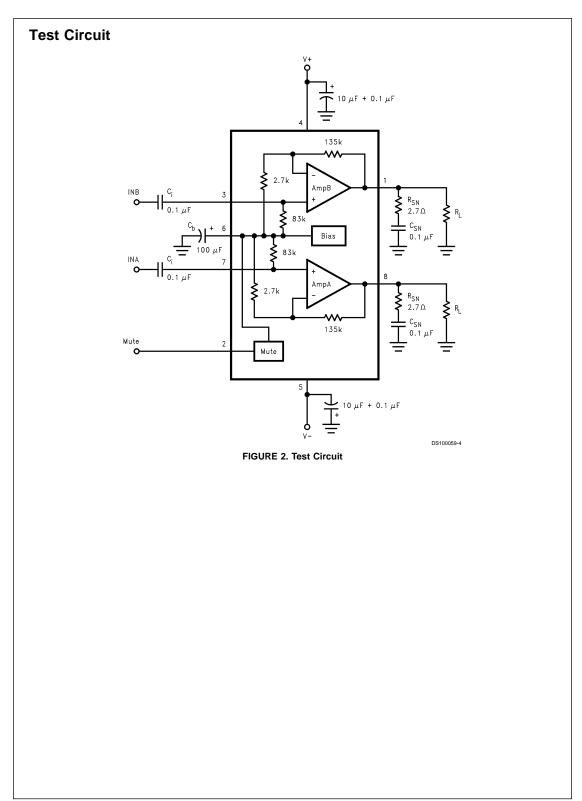

FIGURE 3. Circuit for External Components Description

# **External Components Description**

| Components |                | Function Description                                                                                                                                                                   |  |  |

|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 2       | Cs             | Provides power supply filtering and bypassing.                                                                                                                                         |  |  |

| 3, 4       | $R_{SN}$       | Works with C <sub>SN</sub> to stabilize the output stage from high frequency oscillations.                                                                                             |  |  |

| 5, 6       | $C_{SN}$       | Works with R <sub>SN</sub> to stabilize the output stage from high frequency oscillations.                                                                                             |  |  |

| 7          | $C_b$          | Provides filtering for the internally generated half-supply bias generator.                                                                                                            |  |  |

| 8, 9       | $C_{i}$        | Input AC coupling capacitor which blocks DC voltage at the amplifier's input terminals. Also creates a high pass filter with fc=1/( $2 \cdot \pi \cdot \text{Rin} \cdot \text{Cin}$ ). |  |  |

| 10, 11     | C <sub>o</sub> | Output AC coupling capacitor which blocks DC voltage at the amplifier's output terminal. Creates a high pass filter with fc=1/( $2 \cdot \pi \cdot \text{Rout} \cdot \text{Cout}$ ).   |  |  |

| 12, 13     | $R_{i}$        | Voltage control - limits the voltage level allowed to the amplifier's input terminals.                                                                                                 |  |  |

| 14         | $R_{m}$        | Works with C <sub>m</sub> to provide mute function timing.                                                                                                                             |  |  |

| 15         | $C_{m}$        | Works with R <sub>m</sub> to provide mute function timing.                                                                                                                             |  |  |

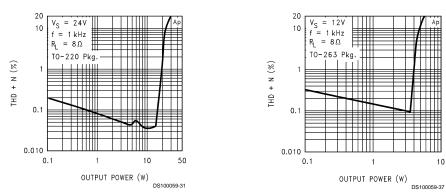

#### Typical Performance Characteristics(Note 5) THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power (Note 7) THD + N (%) THD + N (%) 0.1 10 20 0.1 10 0.1 OUTPUT POWER (W) DS100059-12 OUTPUT POWER (W) DS100059-13 OUTPUT POWER (W) DS100059-14 THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power $V_S = 24$ , f = 60 Hz $R_{|_{L}} = 4\Omega$ V<sub>S</sub> = 24V f = 20 kHz R<sub>L</sub> = 4Ω = 1 kHz = 4 Ω THD + N (%) THD + N (%) 0.1 0.1 0.1 OUTPUT POWER (W) DS100059-6 OUTPUT POWER (W) DS100059-7 OUTPUT POWER (W) DS100059-8 THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power THD + N (%) THD + N (%) THD + N (%) 0.010 OUTPUT POWER (W) DS100059-15 OUTPUT POWER (W) DS100059-16 OUTPUT POWER (W) DS100059-17 THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power f = 20 kHz R<sub>L</sub> = 4Ω (%) N + THD + N (%) THD . 0.010 0.010 0.010 0.1 0.1 OUTPUT POWER (W) DS100059-10 OUTPUT POWER (W) DS100059-11 OUTPUT POWER (W) DS100059-9

# Typical Performance Characteristics(Note 5) (Continued) THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power THD + N (%) THD + N (%) 0.010 OUTPUT POWER (W) DS100059-38 OUTPUT POWER (W) DS100059-39 OUTPUT POWER (W) DS100059-40 THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power THD + N (%) THD + N (%) 0.010 0.010 0.1 0.1 OUTPUT POWER (W) DS100059-41 OUTPUT POWER (W) DS100059-42 OUTPUT POWER (W) DS100059-43 THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power (%) N + THD + N (%) THD . THD+N vs Output Power THD+N vs Output Power THD+N vs Output Power V<sub>S</sub> = 12v f = 60 Hz R<sub>L</sub> = 4Ω = 20 kHz = 4 Ω THD + N (%) THD . 0.010 OUTPUT POWER (W) DS100059-48 OUTPUT POWER (W) DS100059-49 OUTPUT POWER (W) DS100059-47

# Typical Performance Characteristics(Note 5) (Continued)

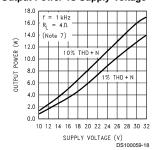

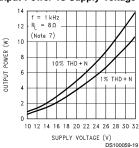

#### **Output Power vs Supply Voltage**

#### **Output Power vs Supply Voltage**

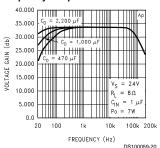

#### Frequency Response

#### THD+N vs Frequency

#### THD+N vs Frequency

#### Frequency Response

#### **Channel Separation**

#### PSRR vs Frequency

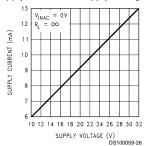

Supply Current vs Supply Voltage

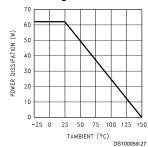

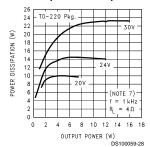

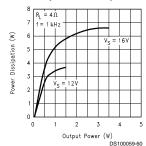

#### **Power Derating Curve**

Power Dissipation vs Output Power

Power Dissipation vs Output Power

#### Typical Performance Characteristics(Note 5) (Continued)

#### **Power Dissipation vs Output Power**

#### Power Dissipation vs Output Power

## **Application Information**

The LM4755 contains circuitry to pull down the bias line internally, effectively shutting down the input stage. An external R-C should be used to adjust the timing of the pull-down. If the bias line is pulled down too quickly, currents induced in the internal bias resistors will cause a momentary DC voltage to appear across the inputs of each amplifier's internal differential pair, resulting in an output DC shift towards Vsupply. An R-C timing circuit should be used to limit the pull-down time such that output "pops" and signal feedthroughs will be minimized. The pull-down timing is a function of a number of factors, including the internal mute circuitry, the voltage used to activate the mute, the bias capacitor, the half-supply voltage, and internal resistances used in the half-supply generator. *Table 1* shows a list of recommended values for the external R-C.

**TABLE 1. Recommended Values for Mute Circuit**

| V <sub>MUTE</sub> | V <sub>cc</sub> | Rm     | Cm    |

|-------------------|-----------------|--------|-------|

| 5V                | 12V             | 18 kΩ  | 10 μF |

| 5V                | 15V             | 18 kΩ  | 10 μF |

| 5V                | 20V             | 12 kΩ  | 10 μF |

| 5V                | 24V             | 12 kΩ  | 10 μF |

| 5V                | 28V             | 8.2 kΩ | 10 μF |

| 5V                | 30V             | 8.2 kΩ | 10 μF |

# CAPACITOR SELECTION AND FREQUENCY RESPONSE

With the LM4755, as in all single supply amplifiers, AC coupling capacitors are used to isolate the DC voltage present at the inputs (pins 3, 7) and outputs (pins 1, 8). As mentioned

earlier in the **External Components** section these capacitors create high-pass filters with their corresponding input/ output impedances. The **Typical Application Circuit** shown in *Figure 1* shows input and output capacitors of 0.1  $\mu$ F and 1,000  $\mu$ F respectively. At the input, with an 83 k $\Omega$  typical input resistance, the result is a high pass 3 dB point occurring at 19 Hz. There is another high pass filter at 39.8 Hz created with the output load resistance of  $4\Omega$ . Careful selection of these components is necessary to ensure that the desired frequency response is obtained. The Frequency Response curves in the **Typical Performance Characteristics** section show how different output coupling capacitors affect the low frequency roll-off.

#### **OPERATING IN BRIDGE-MODE**

Though designed for use as a single-ended amplifier, the LM4755 can be used to drive a load differentially (bridge-mode). Due to the low pin count of the package, only the non-inverting inputs are available. An inverted signal must be provided to one of the inputs. This can easily be done with the use of an inexpensive op-amp configured as a standard inverting amplifier. An LF353 is a good low-cost choice. Care must be taken, however, for a bridge-mode amplifier must theoretically dissipate four times the power of a single-ended type. The load seen by each amplifier is effectively half that of the actual load being used, thus an amplifier designed to drive a  $4\Omega$  load in single-ended mode should drive an  $8\Omega$  load when operating in bridge-mode.

## Application Information (Continued)

FIGURE 4. Bridge-Mode Application

FIGURE 5. THD+N vs P<sub>OUT</sub> for Bridge-Mode Application

#### PREVENTING OSCILLATIONS

With the integration of the feedback and bias resistors onchip, the LM4755 fits into a very compact package. However, due to the close proximity of the non-inverting input pins to the corresponding output pins, the inputs should be AC terminated at all times. If the inputs are left floating, the amplifier will have a positive feedback path through high impedance coupling, resulting in a high frequency oscillation. In most applications, this termination is typically provided by the previous stage's source impedance. If the application will require an external signal, the inputs should be terminated to ground with a resistance of 50 k $\!\Omega$  or less on the AC side of the input coupling capacitors.

#### UNDERVOLTAGE SHUTDOWN

If the power supply voltage drops below the minimum operating supply voltage, the internal under-voltage detection circuitry pulls down the half-supply bias line, shutting down the preamp section of the LM4755. Due to the wide operating supply range of the LM4755, the threshold is set to just under 9V. There may be certain applications where a higher

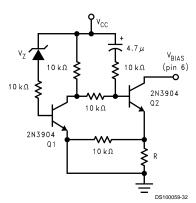

#### Application Information (Continued)

threshold voltage is desired. One example is a design requiring a high operating supply voltage, with large supply and bias capacitors, and there is little or no other circuitry connected to the main power supply rail. In this circuit, when the power is disconnected, the supply and bias capacitors will discharge at a slower rate, possibly resulting in audible output distortion as the decaying voltage begins to clip the output signal. An external circuit may be used to sense for the desired threshold, and pull the bias line (pin 6) to ground to disable the input preamp. Figure 6 shows an example of such a circuit. When the voltage across the zener diode drops below its threshold, current flow into the base of Q1 is interrupted. Q2 then turns on, discharging the bias capacitor. This discharge rate is governed by several factors, including the bias capacitor value, the bias voltage, and the resistor at the emitter of Q2. An equation for approximating the value of the emitter discharge resistor, R, is given below:

$$R = (0.7v) / (Cb \cdot (V_{CC}/2) / 0.1s)$$

Note that this is only a linearized approximation based on a discharge time of 0.1s. The circuit should be evaluated and adjusted for each application.

As mentioned earlier in the **Built-in Mute Circuit** section, when using an external circuit to pull down the bias line, the rate of discharge will have an effect on the turn-off induced distortions. Please refer to the **Built-in Mute Circuit** section for more information.

FIGURE 6. External Undervoltage Pull-Down

# THERMAL CONSIDERATIONS

#### **Heat Sinking**

Proper heatsinking is necessary to ensure that the amplifier will function correctly under all operating conditions. A heat-sink that is too small will cause the die to heat excessively and will result in a degraded output signal as the thermal protection circuitry begins to operate.

The choice of a heatsink for a given application is dictated by several factors: the maximum power the IC needs to dissipate, the worst-case ambient temperature of the circuit, the junction-to-case thermal resistance, and the maximum junction temperature of the IC. The heat flow approximation equation used in determining the correct heatsink maximum thermal resistance is given below:

$$T_J - T_A = P_{DMAX} \bullet (\theta_{JC} + \theta_{CS} + \theta_{SA})$$

where:

P<sub>DMAX</sub> = maximum power dissipation of the IC

$T_{I}(^{\circ}C)$  = junction temperature of the IC

$T_A(^{\circ}C)$  = ambient temperature

$\theta_{JC}(^{\circ}C/W)$  = junction-to-case thermal resistance of the IC  $\theta_{CS}(^{\circ}C/W)$  = case-to-heatsink thermal resistance (typically 0.2 to 0.5  $^{\circ}C/W)$

$\theta_{SA}(^{\circ}C/W)$  = thermal resistance of heatsink

When determining the proper heatsink, the above equation should be re-written as:

$$\theta_{SA} \le [(T_J - T_A) / P_{DMAX}] - \theta_{JC} - \theta_{CS}$$

#### **TO-263 HEATSINKING**

Surface mount applications will be limited by the thermal dissipation properties of printed circuit board area. The TO-263 package is not recommended for surface mount applications with  $\rm V_S > 16\rm V$  due to limited printed circuit board area. There are TO-263 package enhancements, such as clip-on heatsinks and heatsinks with adhesives, that can be used to improve performance.

Standard FR-4 single-sided copper clad will have an approximate Thermal resistance  $(\theta_{\text{SA}})$  ranging from:

1.5 x 1.5 in. sq.

$$20-27^{\circ}$$

C/W ( $T_A=28^{\circ}$ C, Sine wave 2 x 2 in. sq.  $16-23^{\circ}$ C/W testing, 1 oz. Copper)

The above values for  $\theta_{SA}$  vary widely due to dimensional proportions (i.e. variations in width and length will vary  $\theta_{SA}$ ). For audio applications, where peak power levels are short in duration, this part will perform satisfactory with less heatsinking/copper clad area. As with any high power design proper bench testing should be undertaken to assure the design can dissipate the required power. Proper bench testing requires attention to worst case ambient temperature and air flow. At high power dissipation levels the part will show a tendency to increase saturation voltages, thus limiting the undistorted power levels.

#### DETERMINING MAXIMUM POWER DISSIPATION

For a single-ended class AB power amplifier, the theoretical maximum power dissipation point is a function of the supply voltage,  $V_{\rm S}$ , and the load resistance,  $R_{\rm L}$  and is given by the following equation:

(single channel)

$$\mathsf{P}_{\mathsf{DMAX}}\left(\mathsf{W}\right) = \left[\mathsf{V_S}^2 \, / \, (2 \, \bullet \, \pi^2 \, \bullet \, \mathsf{R_L})\right]$$

The above equation is for a single channel class-AB power amplifier. For dual amplifiers such as the LM4755, the equation for calculating the total maximum power dissipated is:

(dual channel)

$$P_{DMAX} (W) = 2 \bullet [V_S^2 / (2 \bullet \pi^2 \bullet R_L)]$$

or

$$V_S^2 / (\pi^2 \bullet R_L)$$

(Bridged Outputs)

$\mathsf{P}_{\mathsf{DMAX}}\left(\mathsf{W}\right) = 4[\mathsf{V_S}^2 \, / \, (2\pi^2 \, \bullet \, \mathsf{R_L})]$

#### **HEATSINK DESIGN EXAMPLE:**

Determine the system parameters:

$V_S = 24V$  Operating Supply Voltage  $R_L = 4\Omega$  Minimum Load Impedance  $T_A = 55^{\circ}\text{C}$  Worst Case Ambient Temperature

Device parameters from the datasheet:

$T_J = 150$ °C Maximum Junction Temperature

#### Application Information (Continued)

$\theta_{JC} = 2^{\circ}C/W$  Junction-to-Case Thermal Resistance

#### Calculations:

2 •

$$P_{DMAX}$$

= 2 •  $[V_S^2 / 2 • \pi^2 • R_L)]$  =  $(24V)^2 / (2 • \pi^2 • 4\Omega)$  = 14.6W

$\theta_{SA} \le [(T_J - T_A) / P_{DMAX}] - \theta_{JC} - \theta_{CS} = [(150^{\circ}C - 55^{\circ}C) / 14.6W] - 2^{\circ}C/W - 0.2^{\circ}C/W = 4.3^{\circ}C/W$

Conclusion: Choose a heatsink with  $\theta_{SA} \le 4.3^{\circ}$ C/W.

#### **TO-263 HEATSINK DESIGN EXAMPLES:**

Example 1: (Stereo Single-Ended Output)

Given:  $T_A=30^{\circ}C$   $T_J=150^{\circ}C$   $R_L=4\Omega$   $V_S=12V$  $\theta_{JC}=2^{\circ}C/W$

P<sub>DMAX</sub> from P<sub>D</sub> vs P<sub>O</sub> Graph:

$$P_{DMAX} \approx 3.7W$$

Calculating P<sub>DMAX</sub>:

$P_{DMAX} = V_{CC}^2/(\pi^2 R_L) = (12V)^2/\pi^2(4\Omega)) = 3.65W$

Calculating Heatsink Thermal Resistance:

$$\theta_{SA} < T_J - T_A / P_{DMAX} - \theta_{JC} - \theta_{CS}$$

$\theta_{SA} < 120^{\circ}C/3.7W - 2.0^{\circ}C/W - 0.2^{\circ}C/W = 30.2^{\circ}C/W$

Therefore the recommendation is to use 1.5 x 1.5 square inch of single-sided copper clad.

Example 2: (Stereo Single-Ended Output)

Given:  $T_A=50$ °C

$T_{J}=150^{\circ}C$   $R_{L}=4\Omega$   $V_{S}=12V$   $\theta_{JC}=2^{\circ}C/W$

$P_{DMAX}$  from  $P_D$  vs  $P_O$  Graph:

$P_{DMAX} \approx 3.7W$

Calculating  $P_{\text{DMAX}}$ :

$P_{DMAX} = V_{CC}^2/(\pi^2 R_L) = (12V)^2/(\pi^2 (4\Omega)) = 3.65W$

Calculating Heatsink Thermal Resistance:

$$\theta_{SA} < [(T_J - T_A) / P_{DMAX}] - \theta_{JC} - \theta_{CS}$$

$\theta_{SA} < 100^{\circ}C/3.7W - 2.0^{\circ}C/W - 0.2^{\circ}C/W = 24.8^{\circ}C/W$

Therefore the recommendation is to use 2.0 x 2.0 square inch of single-sided copper clad.

Example 3: (Bridged Output)

Given:  $T_A = 50$ °C

$T_J=150^{\circ}C$  $R_L=8\Omega$

$V_S=12V$  $\theta_{JC}=2^{\circ}C/W$

Calculating  $P_{DMAX}$ :

$P_{DMAX} = 4[V_{CC}^2/(2\pi^2R_L)] = 4(12V)^2/(2\pi^2(8\Omega)) = 3.65W$

Calculating Heatsink Thermal Resistance:

$$\theta_{SA} < [(T_J - T_A) / P_{DMAX}] - \theta_{JC} - \theta_{CS}$$

$\theta_{SA} < 100^{\circ}\text{C} / 3.7\text{W} - 2.0^{\circ}\text{C/W} - 0.2^{\circ}\text{C/W} = 24.8^{\circ}\text{C/W}$

Therefore the recommendation is to use 2.0 x 2.0 square inch of single-sided copper clad.

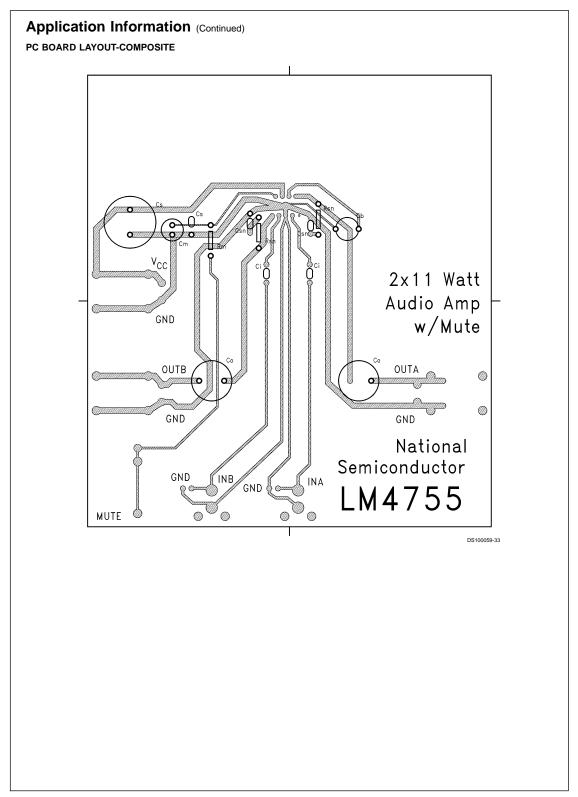

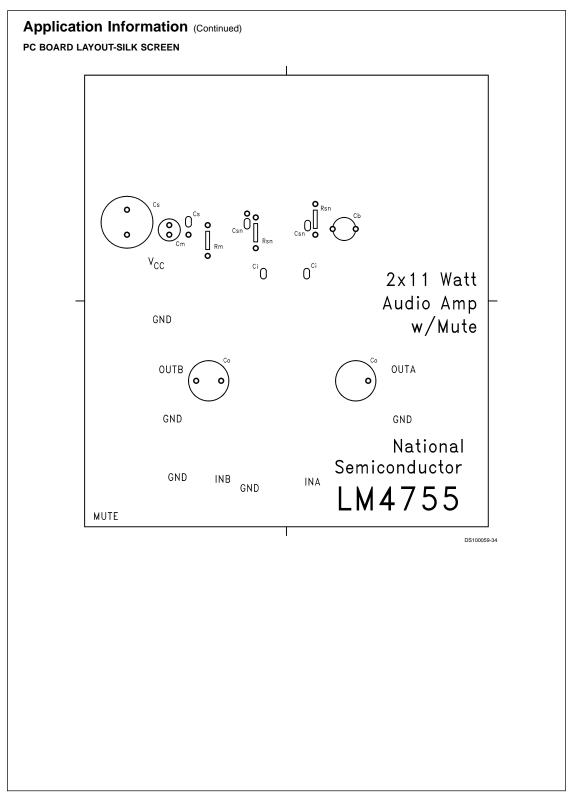

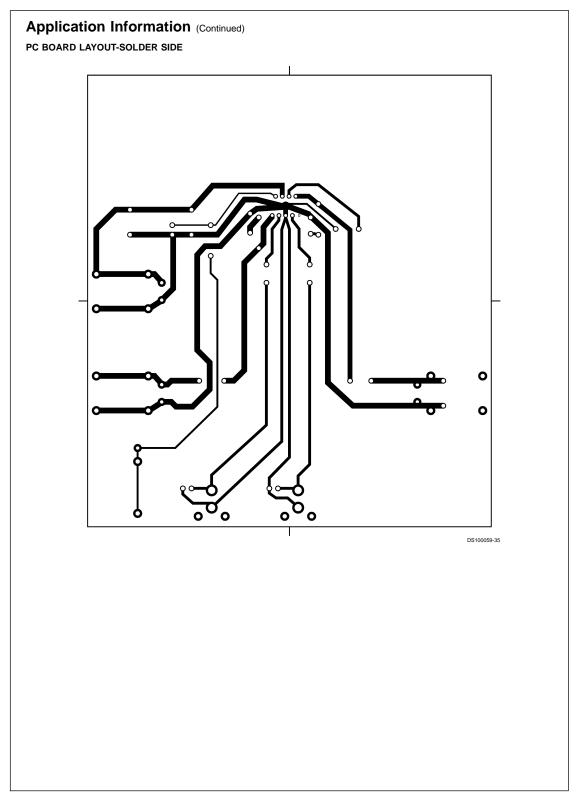

#### LAYOUT AND GROUND RETURNS

Proper PC board layout is essential for good circuit performance. When laying out a PC board for an audio power amplifier, particular attention must be paid to the routing of the output signal ground returns relative to the input signal and bias capacitor grounds. To prevent any ground loops, the ground returns for the output signals should be routed separately and brought together at the supply ground. The input signal grounds and the bias capacitor ground line should also be routed separately. The 0.1  $\mu\text{F}$  high frequency supply bypass capacitor should be placed as close as possible to the IC

# 查询"LM4755T"供应商

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.038±0.005 TYP 0.270±0.010 -10° ± 3° TYP [0.97±0.12] [6.86±0.251] 0.575 0.400+0.010 [14.61] 0.095 [2.41] TYP $[10.16^{+0.25}_{-0.12}]$ 0.024 TYP 0.20±0.002 TYP [0.51±0.05] [0.61] 0.425 0.38 -[0.97] TYP [10.80] 0.342+0.002 [8.69±0.05] 0.030 [0.76] MAX TYP 0.050 MAX 0.015-0.030 0.410 [0.38-0.76] [10.41] [0.89] 0.180+0.002 LEAD POSITION OVERLAY [14.57±0.05] 0.004 [0.1] 0.250 MIN 0.050±0.002 SIDE [6.35][12.45] 0.200 <sub>MIN</sub> 0.565 [5.08] [14.35] CONTROLLING DIMENSION: INCH TS9A (REV B)

Order Number LM4755TS NS Package Number TS9A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Tel: 1-800-272-9959

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Français Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80 National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507