# 16-, 14-, 12-Bit, Six-Channel, Simultaneous Sampling ANALOG-TO-DIGITAL CONVERTERS

#### **FEATURES**

- Family of 16-, 14-, 12-Bit, Pin- and Software-Compatible ADCs

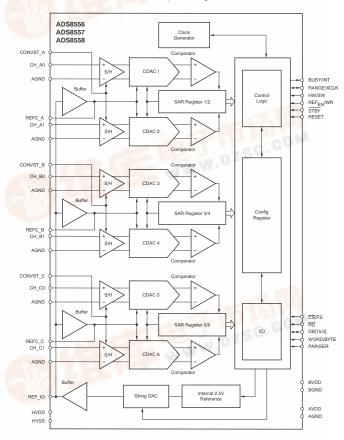

- Six SAR ADCs Grouped in Three Pairs

- Maximum Data Rate Per Channel with Internal Conversion Clock and Reference:

ADS8556: 630kSPS (PAR) or 450kSPS (SER) ADS8557: 670kSPS (PAR) or 470kSPS (SER) ADS8558: 730kSPS (PAR) or 500kSPS (SER)

- Maximum Data Rate with External Conversion Clock and Reference: 800kSPS (PAR) or 530kSPS (SER)

- Pin-Selectable or Programmable Input Voltage Ranges: Up to ±12V

- **Excellent Signal-to-Noise Performance:** 91.5dB (ADS8556) 85dB (ADS8557) 73.9dB (ADS8558)

- Programmable and Buffered Internal Reference: 0.5V to 2.5V and 0.5V to 3.0V

- Comprehensive Power-Down Modes: Deep Power-Down (Standby Mode) Partial Power-Down Auto-Nap Power-Down

- Selectable Parallel or Serial Interface

- **Operating Temperature Range:** -40°C to +125°C

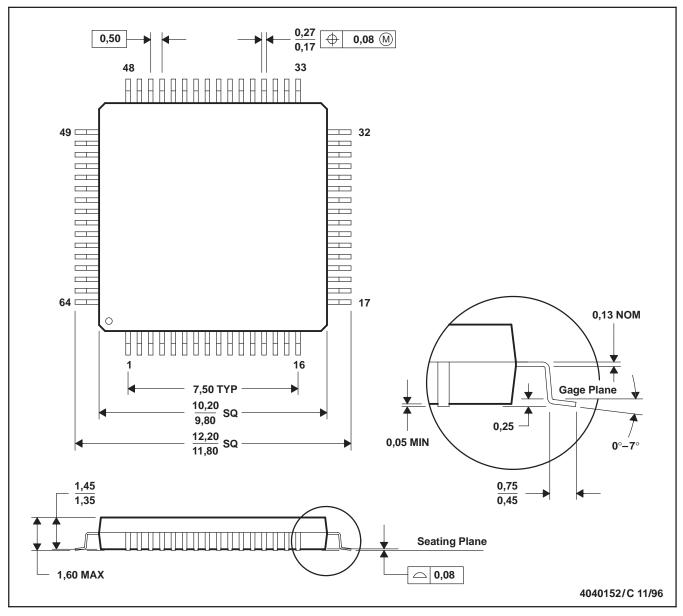

- LQFP-64 Package

### **APPLICATIONS**

- **Power Quality Measurement**

- **Protection Relays**

- **Multi-Axis Motor Control**

- **Programmable Logic Controllers**

- **Industrial Data Acquisition**

#### DESCRIPTION

The ADS8556/7/8 contain six low-power, 16-, 14-, or 12-bit, successive approximation register (SAR) based analog-to-digital converters (ADCs) with true bipolar inputs. Each channel contains sample-and-hold circuit that allows simultaneous high-speed multi-channel signal acquisition.

The ADS8556/7/8 support data rates of up to 730kSPS in parallel interface mode or up to 500kSPS if the serial interface is used. The bus width of the parallel interface can be set to eight or 16 bits. In serial mode, up to three output channels can be activated.

The ADS8556/7/8 is specified over the full industrial temperature range of -40°C to +125°C and is available in an LQFP-64 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

df.dzsc.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

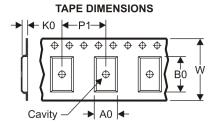

### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT  | RESOLUTION<br>(Bits) | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|----------|----------------------|------------------|-----------------------|--------------------|------------------------------|

| ADS8556I | 16                   | LQFP-64          | PM                    | ADS8556IPM         | Tray, 160                    |

| AD363361 | 10                   | LQFF-04          | FIVI                  | ADS8556IPMR        | Tape and Reel, 1000          |

| AD005571 | 4.4                  | LOED C4          | DM                    | ADS8557IPM         | Tray, 160                    |

| ADS8557I | 14                   | LQFP-64          | PM                    | ADS8557IPMR        | Tape and Reel, 1000          |

| ADCOCEOL | 40                   | LOED CA          | DM                    | ADS8558IPM         | Tray, 160                    |

| ADS8558I | 12                   | LQFP-64          | PM                    | ADS8558IPMR        | Tape and Reel, 1000          |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                                          |                                                                           | ADS8556, ADS8557, ADS8558 | UNIT |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------|------|

| Supply voltage,                                                          | HVDD to AGND                                                              | -0.3 to +18               | V    |

| Supply voltage,                                                          | HVSS to AGND                                                              | -18 to +0.3               | V    |

| Supply voltage,                                                          | AVDD to AGND                                                              | -0.3 to +6                | V    |

| Supply voltage,                                                          | BVDD to BGND                                                              | -0.3 to +6                | V    |

| Analog input vo                                                          | Itage                                                                     | HVSS - 0.3 to HVDD + 0.3  | V    |

| Reference input voltage with respect to AGND                             |                                                                           | AGND – 0.3 to AVDD + 0.3  | V    |

| Digital input volt                                                       | tage with respect to BGND                                                 | BGND - 0.3 to BVDD + 0.3  | V    |

| Ground voltage                                                           | difference AGND to BGND                                                   | ±0.3                      | V    |

| Input current to                                                         | all pins except supply                                                    | -10 to +10                | mA   |

| Maximum virtua                                                           | ll junction temperature, T <sub>J</sub>                                   | +150                      | °C   |

| CCD ratings                                                              | Human body model (HBM) JEDEC standard 22, test method A114-C.01, all pins | ±2000                     | V    |

| Charged device model (CDM) JEDEC standard 22, test method C101, all pins |                                                                           | ±500                      | V    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# RECOMMENDED OPERATING CONDITIONS

|                                                     |                                  | MIN                   | TYP | MAX                   | UNIT |

|-----------------------------------------------------|----------------------------------|-----------------------|-----|-----------------------|------|

| Supply voltage, AVDD to AGND                        |                                  | 4.5                   | 5   | 5.5                   | V    |

| Cupply voltage BV/DD to BCND                        | Low-voltage levels               | 2.7                   | 3.0 | 3.6                   | V    |

| Supply voltage, BVDD to BGND                        | 5V logic levels                  | 4.5                   | 5   | 5.5                   | V    |

| lanut quantu voltaga LIV/DD to ACND                 | Range 1 (±2 x V <sub>REF</sub> ) | 2 × V <sub>REF</sub>  |     | 16.5                  | V    |

| Input supply voltage, HVDD to AGND                  | Range 2 (±4 x V <sub>REF</sub> ) | 4 × V <sub>REF</sub>  |     | 16.5                  | V    |

| Innut quanturaltaga IIV/SS to ACND                  | Range 1 (±2 x V <sub>REF</sub> ) | -16.5                 |     | −2 × V <sub>REF</sub> | V    |

| Input supply voltage, HVSS to AGND                  | Range 2 (±4 x V <sub>REF</sub> ) | -16.5                 |     | −4 × V <sub>REF</sub> | V    |

| Reference input voltage (V <sub>REF</sub> )         |                                  | 0.5                   | 2.5 | 3.0                   | V    |

| Analog inputs                                       | Range 1 (±2 x V <sub>REF</sub> ) | −2 × V <sub>REF</sub> |     | +2 × V <sub>REF</sub> | V    |

| (also see the <i>Analog Inputs</i> section)         | Range 1 (±4 x V <sub>REF</sub> ) | −4 × V <sub>REF</sub> |     | +4 × V <sub>REF</sub> | V    |

| Operating ambient temperature range, T <sub>A</sub> |                                  | -40                   |     | +125                  | °C   |

# **DISSIPATION RATINGS**(1)

| PACKAGE | DERATING FACTOR              | T <sub>A</sub> ≤ +25°C | T <sub>A</sub> = +70°C | T <sub>A</sub> = +85°C | T <sub>A</sub> = +125°C |

|---------|------------------------------|------------------------|------------------------|------------------------|-------------------------|

|         | ABOVE T <sub>A</sub> = +25°C | POWER RATING           | POWER RATING           | POWER RATING           | POWER RATING            |

| LQFP-64 | 20.8mW/°C                    | 2.60W                  | 1.66W                  | 1.35W                  | 0.52W                   |

<sup>(1)</sup> Based on High-K  $\theta_{JA}$ .

### THERMAL CHARACTERISTICS

Over recommended operating conditions, unless otherwise noted.

|                |                                     |                                                                                             | ADS85 | 56, ADS8557, A | NDS8558 |      |

|----------------|-------------------------------------|---------------------------------------------------------------------------------------------|-------|----------------|---------|------|

|                | PARAMETER                           | TEST CONDITIONS                                                                             | MIN   | TYP            | MAX     | UNIT |

| 0              | lunding to distribute and a single  | Low-K thermal resistance <sup>(1)</sup>                                                     |       | 74             |         | °C/W |

| $\theta_{JA}$  | Junction-to-air thermal resistance  | High-K thermal resistance <sup>(1)</sup>                                                    |       | 48             |         | °C/W |

| $\theta_{JC}$  | Junction-to-case thermal resistance |                                                                                             |       | 16             |         | °C/W |

|                |                                     | ADS8556, HVDD = +15V, HVSS = -15V, AVDD = 5V, BVDD = 3V, and f <sub>DATA</sub> = maximum    |       | 251.7          | 298.5   | mW   |

| P <sub>D</sub> | Device power dissipation            | ADS8557, HVDD = +15V, HVSS = -15V, AVDD = 5V, BVDD = 3V, and f <sub>DATA</sub> = maximum    |       | 253.2          | 303.0   | mW   |

|                |                                     | ADS8558, HVDD = +15V, HVSS = -15V, AVDD = 5V,<br>BVDD = 3V, and f <sub>DATA</sub> = maximum |       | 262.2          | 318.0   | mW   |

<sup>(1)</sup> Modeled in accordance with the Low-K or High-K thermal metric definitions of EIA/JESD51-3.

# **ELECTRICAL CHARACTERISTICS: ADS8556**

Over recommended operating free-air temperature range of -40°C to +125°C, AVDD = 4.5V to 5V, BVDD = 2.7V to 5.5V, HVDD = 10V to 15V, HVSS = -15V to -10V,  $V_{REF} = 2.5V$  (internal), and  $f_{DATA} = 630kSPS$  in parallel mode or 450kSPS in serial mode, unless otherwise noted.

|                                    |                   |                                                               |       | ADS8556            |       |                   |

|------------------------------------|-------------------|---------------------------------------------------------------|-------|--------------------|-------|-------------------|

| PARAMETER                          |                   | CONDITIONS                                                    | MIN   | TYP <sup>(1)</sup> | MAX   | UNIT              |

| DC ACCURACY                        |                   |                                                               | -     |                    |       |                   |

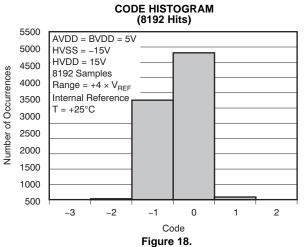

| Resolution                         |                   |                                                               |       | 16                 |       | Bits              |

| No missing codes                   |                   |                                                               | 16    |                    |       | Bits              |

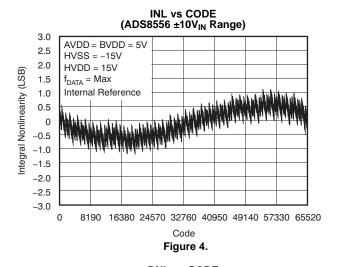

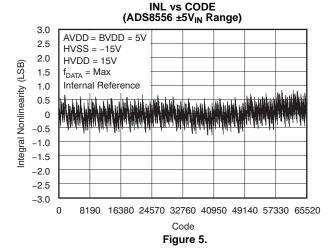

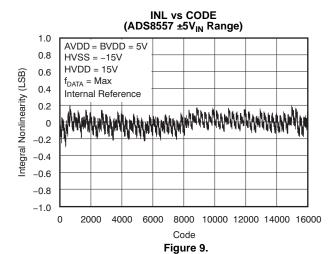

| lete and the enity case.           | INL               | At $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$       | -3    | ±1.5               | 3     | LSB               |

| Integral linearity error           | INL               | At T <sub>A</sub> = -40°C to +125°C                           | -4    | ±1.5               | 4     | LSB               |

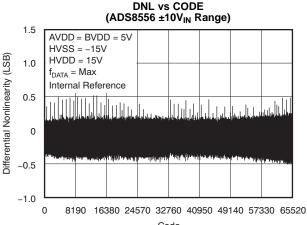

| D''' '' '' ''                      | 5111              | At $T_A = -40$ °C to +85°C                                    | -1    | ±0.75              | 1.5   | LSB               |

| Differential linearity error       | DNL               | At T <sub>A</sub> = -40°C to +125°C                           | -1    | ±0.75              | 2     | LSB               |

| Offset error                       |                   |                                                               | -4.0  | ±0.8               | 4.0   | mV                |

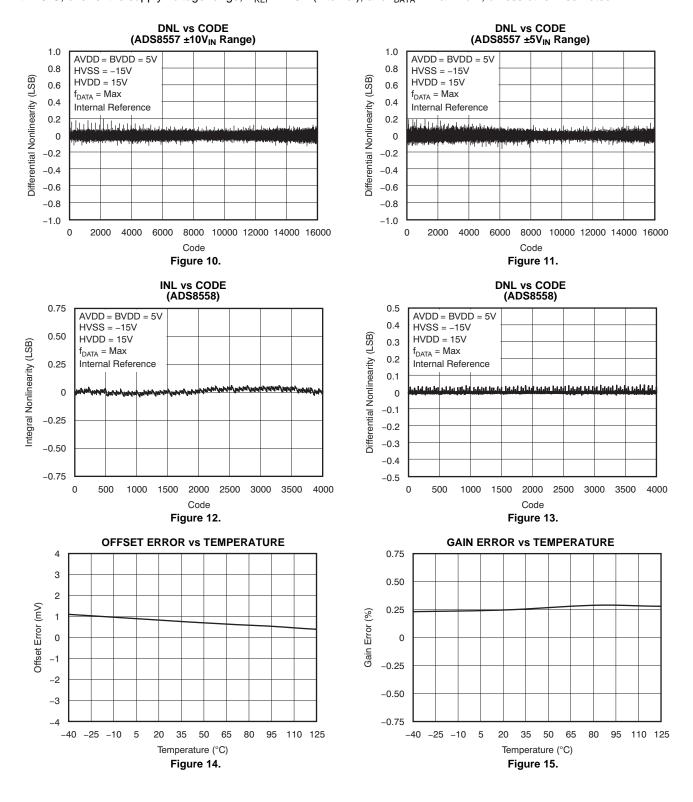

| Offset error drift                 |                   |                                                               |       | ±3.5               |       | μV/°C             |

| Gain error                         |                   | Referenced to voltage at REFIO                                | -0.75 | ±0.25              | 0.75  | %FSR              |

| Gain error drift                   |                   | Referenced to voltage at REFIO                                |       | ±6                 |       | ppm/°C            |

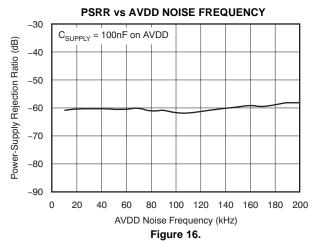

| Power-supply rejection ratio       | PSRR              | At output code FFFFh, related to AVDD                         |       | 60                 |       | dB                |

| SAMPLING DYNAMICS                  |                   |                                                               |       |                    |       |                   |

| Acquisition time                   | t <sub>ACQ</sub>  |                                                               | 280   |                    |       | ns                |

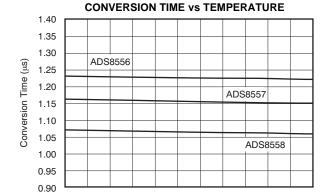

| Conversion time per ADC            | t <sub>CONV</sub> |                                                               |       |                    | 1.26  | μs                |

|                                    | t <sub>CCLK</sub> |                                                               |       |                    | 18.5  | t <sub>CCLK</sub> |

| Internal conversion clock period   |                   |                                                               |       |                    | 68.0  | ns                |

| T                                  | ,                 | Parallel interface, internal clock and reference              |       |                    | 630   | kSPS              |

| Throughput rate                    | f <sub>DATA</sub> | Serial interface, internal clock and reference                |       |                    | 450   | kSPS              |

| AC ACCURACY                        |                   |                                                               | -     |                    |       |                   |

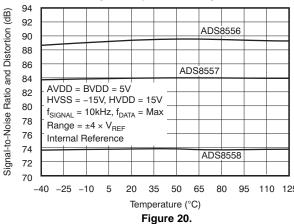

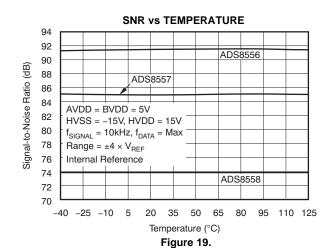

| 0. 1                               | OND               | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$  | 90    | 91.5               |       | dB                |

| Signal-to-noise ratio              | SNR               | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ | 89    | 91.5               |       | dB                |

| 0                                  | OILLAD            | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$  | 87    | 89.5               |       | dB                |

| Signal-to-noise ratio + distortion | SINAD             | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ | 86.5  | 89.5               |       | dB                |

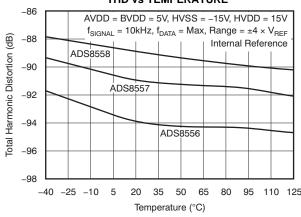

| Total harmonic distortion (2)      | TUD               | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$  |       | -94                | -90   | dB                |

| Total narmonic distortion (=)      | THD               | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ |       | -94                | -89.5 |                   |

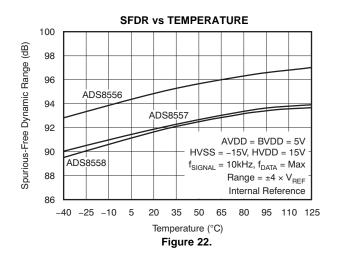

| 0                                  | 0555              | At $f_{IN} = 10kHz$ , $T_A = -40$ °C to +85°C                 | 90    | 95                 |       | dB                |

| Spurious-free dynamic range        | SFDR              | At $f_{IN} = 10kHz$ , $T_A = -40^{\circ}C$ to +125°C          | 89.5  | 95                 |       | dB                |

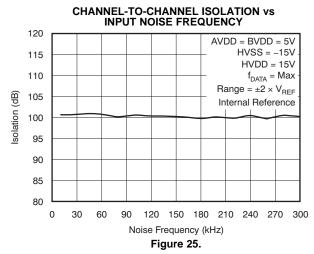

| Channel-to-channel isolation       |                   | At f <sub>IN</sub> = 10kHz                                    |       | 100                |       | dB                |

| 0.15                               |                   | In 4 × V <sub>REF</sub> mode                                  |       | 48                 |       | MHz               |

| –3dB small-signal bandwidth        |                   | In 2 × V <sub>REF</sub> mode                                  |       | 24                 |       | MHz               |

<sup>(1)</sup>

All values are at  $T_A$  = +25°C. Calculated on the first nine harmonics of the input frequency.

# **ELECTRICAL CHARACTERISTICS: ADS8557**

Over recommended operating free-air temperature range of -40°C to +125°C, AVDD = 4.5V to 5.5V, BVDD = 2.7V to 5.5V, HVDD = 10V to 15V, HVSS = -15V to -10V,  $V_{REF} = 2.5V$  (internal), and  $f_{DATA} = 670kSPS$  in parallel mode or 470kSPS in serial mode, unless otherwise noted.

|                                         |                   |                                                  |       | ADS8557            |          |                   |

|-----------------------------------------|-------------------|--------------------------------------------------|-------|--------------------|----------|-------------------|

| PARAMETER                               |                   | CONDITIONS                                       | MIN   | TYP <sup>(1)</sup> | MAX      | UNIT              |

| DC ACCURACY                             |                   |                                                  |       |                    | <u> </u> |                   |

| Resolution                              |                   |                                                  |       | 14                 |          | Bits              |

| No missing codes                        |                   |                                                  | 14    |                    |          | Bits              |

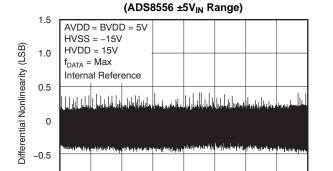

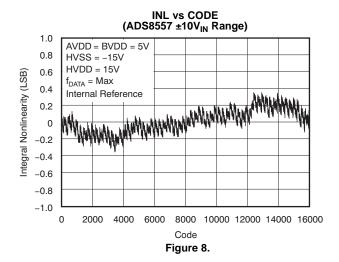

| Integral linearity error                | INL               |                                                  | -1    | ±0.4               | 1        | LSB               |

| Differential linearity error            | DNL               |                                                  | -1    | ±0.25              | 1        | LSB               |

| Offset error                            |                   |                                                  | -4    | ±0.8               | 4        | mV                |

| Offset error drift                      |                   |                                                  |       | ±3.5               |          | μV/°C             |

| Gain error                              |                   | Referenced to voltage at REFIO                   | -0.75 | ±0.25              | 0.75     | %FSR              |

| Gain error drift                        |                   | Referenced to voltage at REFIO                   |       | ±6                 |          | ppm/°C            |

| Power-supply rejection ratio            | PSRR              | At output code FFFFh, related to AVDD            |       | 60                 |          | dB                |

| SAMPLING DYNAMICS                       |                   |                                                  |       | •                  | •        |                   |

| Acquisition time                        | t <sub>ACQ</sub>  |                                                  | 280   |                    |          | ns                |

| Conversion time per ADC                 | t <sub>CONV</sub> |                                                  |       |                    | 1.19     | μs                |

| latera el conservacion el calcacación d |                   |                                                  |       |                    | 18.5     | t <sub>CCLK</sub> |

| Internal conversion clock period        | t <sub>CCLK</sub> |                                                  |       |                    | 64.1     | ns                |

| Thereselves and                         | į.                | Parallel interface, internal clock and reference |       |                    | 670      | kSPS              |

| Throughput rate                         | f <sub>DATA</sub> | Serial interface, internal clock and reference   |       |                    | 470      | kSPS              |

| AC ACCURACY                             |                   |                                                  |       |                    |          |                   |

| Signal-to-noise ratio                   | SNR               | At f <sub>IN</sub> = 10kHz                       | 84    | 85                 |          | dB                |

| Signal-to-noise ratio + distortion      | SINAD             | At f <sub>IN</sub> = 10kHz                       | 83    | 84                 |          | dB                |

| Total harmonic distortion (2)           | THD               | At f <sub>IN</sub> = 10kHz                       |       | -91                | -86      | dB                |

| Spurious-free dynamic range             | SFDR              | At f <sub>IN</sub> = 10kHz                       | 86    | 92                 |          | dB                |

| Channel-to-channel isolation            |                   | At f <sub>IN</sub> = 10kHz                       |       | 100                |          | dB                |

| OdD corell signed benedicidth           |                   | In 4 × V <sub>REF</sub> mode                     |       | 48                 |          | MHz               |

| –3dB small-signal bandwidth             |                   | In 2 × V <sub>REF</sub> mode                     |       | 24                 |          | MHz               |

All values are at  $T_A = +25$ °C. Calculated on the first nine harmonics of the input frequency.

# **ELECTRICAL CHARACTERISTICS: ADS8558**

Over recommended operating free-air temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, AVDD = 4.5V to 5V, BVDD = 2.7V to 5.5V, HVDD = 10V to 15V, HVSS = -15V to -10V, V<sub>REF</sub> = 2.5V (internal), and f<sub>DATA</sub> = 730kSPS in parallel mode or 500kSPS in serial mode, unless otherwise noted.

|                                          |                   |                                                  |       | ADS8558            |      |                   |

|------------------------------------------|-------------------|--------------------------------------------------|-------|--------------------|------|-------------------|

| PARAMETER                                |                   | CONDITIONS                                       | MIN   | TYP <sup>(1)</sup> | MAX  | UNIT              |

| DC ACCURACY                              |                   |                                                  |       |                    |      |                   |

| Resolution                               |                   |                                                  |       | 12                 |      | Bits              |

| No missing codes                         |                   |                                                  | 12    |                    |      | Bits              |

| Integral linearity error                 | INL               |                                                  | -0.75 | ±0.2               | 0.75 | LSB               |

| Differential linearity error             | DNL               |                                                  | -0.5  | ±0.2               | 0.5  | LSB               |

| Offset error                             |                   |                                                  | -4    | ±0.8               | 4    | mV                |

| Offset error drift                       |                   |                                                  |       | ±3.5               |      | μV/°C             |

| Gain error                               |                   | Referenced to voltage at REFIO                   | -0.75 | ±0.25              | 0.75 | %FSR              |

| Gain error drift                         |                   | Referenced to voltage at REFIO                   |       | ±6                 |      | ppm/°C            |

| Power-supply rejection ratio             | PSRR              | At output code FFFFh, related to AVDD            |       | 60                 |      | dB                |

| SAMPLING DYNAMICS                        |                   |                                                  |       |                    |      |                   |

| Acquisition time                         | t <sub>ACQ</sub>  |                                                  | 280   |                    |      | ns                |

| Conversion time per ADC                  | t <sub>CONV</sub> |                                                  |       |                    | 1.09 | μs                |

| laternal services alask assist           |                   |                                                  |       |                    | 18.5 | t <sub>CCLK</sub> |

| Internal conversion clock period         | t <sub>CCLK</sub> |                                                  |       |                    | 58.8 | ns                |

| Thereselves to set                       |                   | Parallel interface, internal clock and reference |       |                    | 730  | kSPS              |

| Throughput rate                          | f <sub>DATA</sub> | Serial interface, internal clock and reference   |       |                    | 500  | kSPS              |

| AC ACCURACY                              |                   |                                                  |       |                    |      |                   |

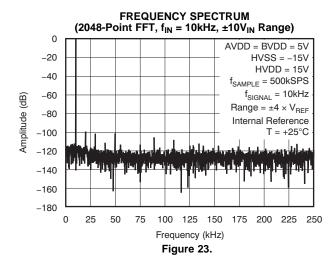

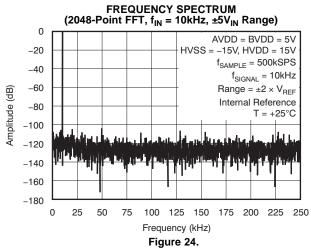

| Signal-to-noise ratio                    | SNR               | At f <sub>IN</sub> = 10kHz                       | 73    | 73.9               |      | dB                |

| Signal-to-noise ratio + distortion       | SINAD             | At f <sub>IN</sub> = 10kHz                       | 73    | 73.8               |      | dB                |

| Total harmonic distortion <sup>(2)</sup> | THD               | At f <sub>IN</sub> = 10kHz                       |       | -89                | -84  | dB                |

| Spurious-free dynamic range              | SFDR              | At f <sub>IN</sub> = 10kHz                       | 84    | 92                 |      | dB                |

| Channel-to-channel isolation             |                   | At f <sub>IN</sub> = 10kHz                       |       | 100                |      | dB                |

| OdD II -i I b dwidth                     |                   | In 4 × V <sub>REF</sub> mode                     |       | 48                 |      | MHz               |

| –3dB small-signal bandwidth              |                   | In 2 x V <sub>REF</sub> mode                     |       | 24                 |      | MHz               |

<sup>(1)</sup> All values are at  $T_A = +25$ °C.

<sup>(2)</sup> Calculated on the first nine harmonics of the input frequency.

# **ELECTRICAL CHARACTERISTICS: GENERAL**

Over recommended operating free-air temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, AVDD = 4.5V to 5.5V, BVDD = 2.7V to 5.5V, HVDD = 10V to 15V, HVSS = -15V to -10V,  $V_{REF}$  = 2.5V (internal), and  $f_{DATA}$  = maximum, unless otherwise noted.

|                                      |                         |                                                              | ADS855                 | 6, ADS8557, A      | ADS8558               |        |

|--------------------------------------|-------------------------|--------------------------------------------------------------|------------------------|--------------------|-----------------------|--------|

| PARAMETER                            |                         | CONDITIONS                                                   | MIN                    | TYP <sup>(1)</sup> | MAX                   | UNIT   |

| ANALOG INPUT                         |                         |                                                              |                        |                    |                       |        |

| Pipelar full cools range             | CHXX                    | RANGE pin/RANGE bit = 0                                      | −4 x V <sub>REF</sub>  |                    | +4 x V <sub>REF</sub> | V      |

| Bipolar full-scale range             | СПХХ                    | RANGE pin/RANGE bit = 1                                      | −2 × V <sub>REF</sub>  |                    | +2 × V <sub>REF</sub> | V      |

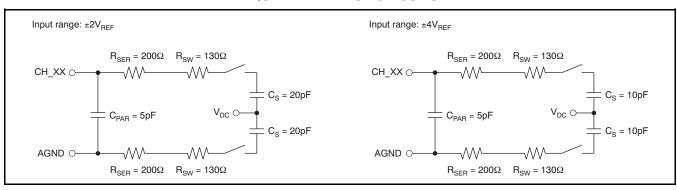

| Input capacitance                    |                         | Input range = ±4 x V <sub>REF</sub>                          |                        | 10                 |                       | pF     |

| input capacitance                    |                         | Input range = $\pm 2 \times V_{REF}$                         |                        | 20                 |                       | pF     |

| Input leakage current                |                         | No ongoing conversion                                        |                        |                    | ±1                    | μΑ     |

| Aperture delay                       |                         |                                                              |                        | 5                  |                       | ns     |

| Aperture delay matching              |                         | Common CONVST for all channels                               |                        | 250                |                       | ps     |

| Aperture jitter                      |                         |                                                              |                        | 50                 |                       | ps     |

| EXTERNAL CLOCK INPUT (XCL)           | K)                      |                                                              |                        |                    |                       |        |

| External clock frequency             | f <sub>XCLK</sub>       | An external reference must be used for $f_{XCLK} > f_{CCLK}$ | 1                      | 18                 | 20                    | MHz    |

| External clock duty cycle            |                         |                                                              | 45                     |                    | 55                    | %      |

| REFERENCE VOLTAGE OUTPUT             | Γ (REF <sub>OUT</sub> ) |                                                              |                        | I                  |                       |        |

|                                      |                         | 2.5V operation, REFDAC = 0x3FF                               | 2.485                  | 2.5                | 2.515                 | V      |

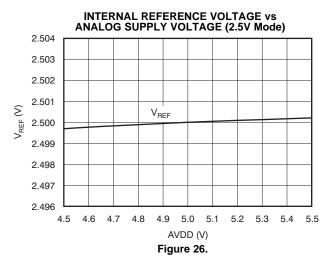

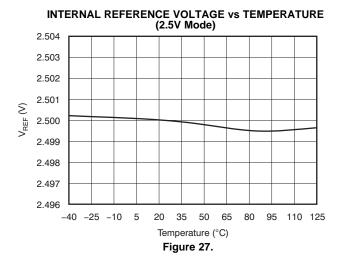

| Defenses with an                     |                         | 2.5V operation, REFDAC = 0x3FF at +25°C                      | 2.496                  | 2.5                | 2.504                 | V      |

| Reference voltage                    | $V_{REF}$               | 3.0V operation, REFDAC = 0x3FF                               | 2.985                  | 3.0                | 3.015                 | V      |

|                                      |                         | 3.0V operation, REFDAC = 0x3FF at +25°C                      | 2.995                  | 3.0                | 3.005                 | V      |

| Reference voltage drift              | dV <sub>REF</sub> /dT   |                                                              |                        | ±10                |                       | ppm/°C |

| Power-supply rejection ratio         | PSRR                    |                                                              |                        | 73                 |                       | dB     |

| Output current                       | I <sub>REFOUT</sub>     | DC current                                                   | -2                     |                    | 2                     | mA     |

| Short-circuit current <sup>(2)</sup> | I <sub>REFSC</sub>      |                                                              |                        | 50                 |                       | mA     |

| Turn-on settling time                | t <sub>REFON</sub>      |                                                              |                        | 10                 |                       | ms     |

| External land conscitores            |                         | At CREF_x pins                                               | 4.7                    | 10                 |                       | μF     |

| External load capacitance            |                         | At REFIO pins                                                | 100                    | 470                |                       | nF     |

| Tuning range                         | REFDAC                  | Internal reference output voltage range                      | 0.2 x V <sub>REF</sub> |                    | $V_{REF}$             | V      |

| REFDAC resolution                    |                         |                                                              | 10                     |                    |                       | Bits   |

| REFDAC differential nonlinearity     | $DNL_DAC$               |                                                              | -1                     | ±0.1               | 1                     | LSB    |

| REFDAC integral nonlinearity         | $INL_DAC$               |                                                              | -2                     | ±0.1               | 2                     | LSB    |

| REFDAC offset error                  | $V_{OSDAC}$             | $V_{REF} = 0.5V (DAC = 0x0CC)$                               | -4                     | ±0.65              | 4                     | LSB    |

| REFERENCE VOLTAGE INPUT (            | REF <sub>IN</sub> )     |                                                              |                        |                    |                       |        |

| Reference input voltage              | $V_{REFIN}$             |                                                              | 0.5                    | 2.5                | 3.025                 | V      |

| Input resistance                     |                         |                                                              |                        | 100                |                       | ΜΩ     |

| Input capacitance                    |                         |                                                              |                        | 5                  |                       | pF     |

| Reference input current              |                         |                                                              |                        |                    | 1                     | μΑ     |

| SERIAL CLOCK INPUT (SCLK)            |                         |                                                              |                        |                    |                       |        |

| Serial clock input frequency         | f <sub>SCLK</sub>       |                                                              | 0.1                    |                    | 36                    | MHz    |

| Serial clock period                  | t <sub>SCLK</sub>       |                                                              | 0.0278                 |                    | 10                    | μs     |

| Serial clock duty cycle              |                         |                                                              | 40                     |                    | 60                    | %      |

| DIGITAL INPUTS(3)                    |                         |                                                              |                        |                    |                       |        |

| Logic family                         |                         |                                                              | CMOS                   | with Schmitt-      | Trigger               |        |

| High-level input voltage             |                         |                                                              | 0.7 × BVDD             |                    | BVDD + 0.3            | V      |

| Low-level input voltage              |                         |                                                              | BGND - 0.3             |                    | 0.3 × BVDD            | V      |

| Input current                        |                         | V <sub>I</sub> = BVDD to BGND                                | -50                    |                    | +50                   | nA     |

| Input capacitance                    |                         |                                                              |                        | 5                  |                       | pF     |

<sup>(1)</sup> All values are at  $T_A = +25$ °C.

<sup>(2)</sup> Reference output current is not limited internally.

<sup>(3)</sup> Specified by design.

# **ELECTRICAL CHARACTERISTICS: GENERAL (continued)**

Over recommended operating free-air temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, AVDD = 4.5V to 5.5V, BVDD = 2.7V to 5.5V, HVDD = 10V to 15V, HVSS = -15V to -10V,  $V_{REF}$  = 2.5V (internal), and  $f_{DATA}$  = maximum, unless otherwise noted.

|                                              |       |                                                                 | ADS8556    | , ADS8557, A       | ADS8558    |      |

|----------------------------------------------|-------|-----------------------------------------------------------------|------------|--------------------|------------|------|

| PARAMETER                                    |       | CONDITIONS                                                      | MIN        | TYP <sup>(1)</sup> | MAX        | UNIT |

| DIGITAL OUTPUTS <sup>(4)</sup>               |       |                                                                 |            |                    |            |      |

| Logic family                                 |       |                                                                 |            | CMOS               |            |      |

| High-level output voltage                    |       | I <sub>OH</sub> = 100μA                                         | BVDD - 0.6 |                    | BVDD       | V    |

| Low-level output voltage                     |       | $I_{OH} = -100 \mu A$                                           | BGND       |                    | BGND + 0.4 | V    |

| High-impedance-state output curre            | nt    |                                                                 | -50        |                    | 50         | nA   |

| Output capacitance                           |       |                                                                 |            | 5                  |            | pF   |

| Load capacitance                             |       |                                                                 |            |                    | 30         | pF   |

| POWER-SUPPLY REQUIREMENT                     | гѕ    |                                                                 |            |                    |            |      |

| Analog supply voltage                        | AVDD  |                                                                 | 4.5        | 5.0                | 5.5        | V    |

| Buffer I/O supply voltage                    | BVDD  |                                                                 | 2.7        | 3.0                | 5.5        | V    |

| Input positive supply voltage                | HVDD  |                                                                 | 5.0        | 10.0               | 16.5       | V    |

| Input negative supply voltage                | HVSS  |                                                                 | -16.5      | -10.0              | -5.0       | V    |

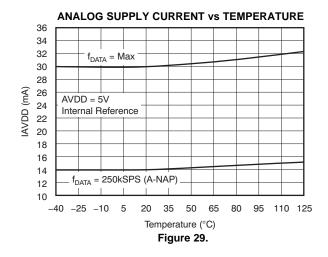

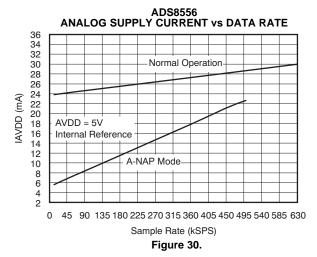

|                                              |       | f <sub>DATA</sub> = maximum                                     |            | 30.0               | 36.0       | mA   |

|                                              | IAVDD | ADS8556, f <sub>DATA</sub> = 250kSPS (auto-NAP mode)            |            | 14.0               | 16.5       | mA   |

|                                              |       | ADS8557, f <sub>DATA</sub> = 250kSPS (auto-NAP mode)            |            | 14.0               | 17.0       | mA   |

| Analog supply current <sup>(5)</sup>         |       | ADS8558, f <sub>DATA</sub> = 250kSPS (auto-NAP mode)            |            | 14.0               | 18.0       | mA   |

|                                              |       | Auto-NAP mode, no ongoing conversion, internal conversion clock |            | 4.0                | 6.0        | mA   |

|                                              |       | Power-down mode                                                 |            | 0.1                | 50.0       | μΑ   |

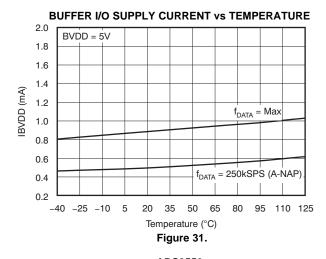

|                                              |       | f <sub>DATA</sub> = maximum                                     |            | 0.9                | 2.0        | mA   |

|                                              |       | f <sub>DATA</sub> = 250kSPS (auto-NAP mode)                     |            | 0.5                | 1.5        | mA   |

| Buffer I/O supply current <sup>(6)</sup>     | IBVDD | Auto-NAP mode, no ongoing conversion, internal conversion clock |            | 0.1                | 10.0       | μΑ   |

|                                              |       | Power-down mode                                                 |            | 0.1                | 10.0       | μΑ   |

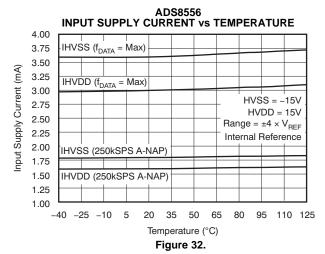

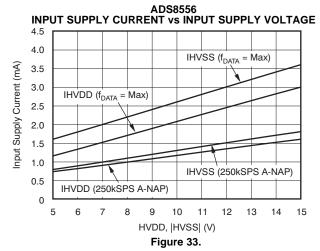

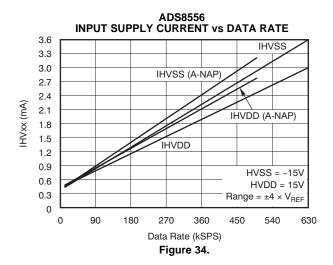

|                                              |       | ADS8556, f <sub>DATA</sub> = maximum                            |            | 3.0                | 3.5        | mA   |

|                                              |       | ADS8557, f <sub>DATA</sub> = maximum                            |            | 3.1                | 3.6        | mA   |

|                                              |       | ADS8558, f <sub>DATA</sub> = maximum                            |            | 3.3                | 4.0        | mA   |

| Input positive supply current <sup>(7)</sup> | IHVDD | f <sub>DATA</sub> = 250kSPS (auto-NAP mode)                     |            | 1.6                | 2.0        | mA   |

|                                              |       | Auto-NAP mode, no ongoing conversion, internal conversion clock |            | 0.2                | 0.3        | μΑ   |

|                                              |       | Power-down mode                                                 |            | 0.1                | 10.0       | μΑ   |

|                                              |       | ADS8556, f <sub>DATA</sub> = maximum                            |            | 3.6                | 4.0        | mA   |

|                                              |       | ADS8557, f <sub>DATA</sub> = maximum                            |            | 3.6                | 4.2        | mA   |

|                                              |       | ADS8558, f <sub>DATA</sub> = maximum                            |            | 4.0                | 4.8        | mA   |

| Input negative supply current <sup>(8)</sup> | IHVSS | f <sub>DATA</sub> = 250kSPS (auto-NAP mode)                     |            | 1.8                | 2.2        | mA   |

|                                              |       | Auto-NAP mode, no ongoing conversion, internal conversion clock |            | 0.2                | 0.25       | μА   |

|                                              |       | Power-down mode                                                 |            | 0.1                | 10.0       | μΑ   |

<sup>(4)</sup> Specified by design.

<sup>(5)</sup> At AVDD = 5V.

<sup>(6)</sup> At BVDD = 3V, parallel mode, load capacitance = 6pF/pin.

<sup>(7)</sup> At HVDD = 15 $^{\circ}$ .

<sup>(8)</sup> At HVSS = -15V.

<u>₩營销®₩DS8558I"供应商</u>

# **ELECTRICAL CHARACTERISTICS: GENERAL (continued)**

Over recommended operating free-air temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, AVDD = 4.5V to 5.5V, BVDD = 2.7V to 5.5V, HVDD = 10V to 15V, HVSS = -15V to -10V,  $V_{REF} = 2.5$ V (internal), and  $f_{DATA} = maximum$ , unless otherwise noted.

|                                  |                                                                 | ADS8556, ADS8557, ADS8558 |                    |       |      |

|----------------------------------|-----------------------------------------------------------------|---------------------------|--------------------|-------|------|

| PARAMETER                        | CONDITIONS                                                      | MIN                       | TYP <sup>(1)</sup> | MAX   | UNIT |

| POWER-SUPPLY REQUIREMENTS (c     | ontinued)                                                       | •                         |                    | •     |      |

|                                  | ADS8556, f <sub>DATA</sub> = maximum                            |                           | 251.7              | 298.5 | mW   |

|                                  | ADS8557, f <sub>DATA</sub> = maximum                            |                           | 253.2              | 303.0 | mW   |

|                                  | ADS8558, f <sub>DATA</sub> = maximum                            |                           | 262.2              | 318.0 | mW   |

|                                  | ADS8556, f <sub>DATA</sub> = 250kSPS (auto-NAP mode)            |                           | 122.5              | 150.0 | mW   |

| Power dissipation <sup>(9)</sup> | ADS8557, f <sub>DATA</sub> = 250kSPS (auto-NAP mode)            |                           | 122.5              | 152.5 | mW   |

|                                  | ADS8558, f <sub>DATA</sub> = 250kSPS (auto-NAP mode)            |                           | 122.5              | 157.5 | mW   |

|                                  | Auto-NAP mode, no ongoing conversion, internal conversion clock |                           | 26.0               | 38.3  | mW   |

|                                  | Power-down mode                                                 |                           | 3.8                | 580.0 | μW   |

(9) At AVDD = 5V, BVDD = 3V, HVDD = 15V, and HVSS = -15V.

#### **EQUIVALENT INPUT CIRCUITS**

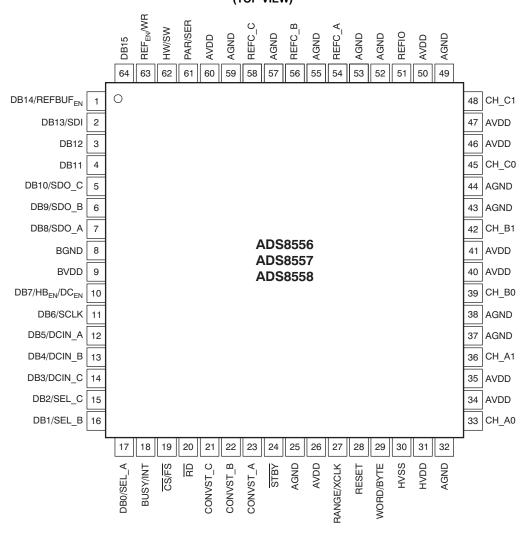

### PIN CONFIGURATION

#### PM PACKAGE LQFP-64 (TOP VIEW)

# **"≝街™**DS8558!"供应商

#### **TERMINAL FUNCTIONS**

| DESCRIPTION |                   |                                                                                                                                                                          |                                                                                                                                                                                                              |  |  |  |

|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN#        | TYPE(1)           | PARALLEL INTERFACE (PAR/SER = 0)                                                                                                                                         | SERIAL INTERFACE (PAR/SER = 1)                                                                                                                                                                               |  |  |  |

| 1           | DIO/DI            | Data bit 14 input/output Output is '0' for the ADS8557/8                                                                                                                 | Hardware mode (HW/SW = 0):<br>Reference buffers enable input.<br>When low, all reference buffers are enabled (mandatory if<br>internal reference is used). When high, all reference buffers<br>are disabled. |  |  |  |

|             |                   |                                                                                                                                                                          | Software mode (HW/SW = 1):Connect to BGND or BVDD. The reference buffers are controlled by bit C24 (REFBUF) in control register (CR).                                                                        |  |  |  |

| _           | D10/D1            | Data bit 13 input/output                                                                                                                                                 | Hardware mode (HW/SW = 0): Connect to BGND                                                                                                                                                                   |  |  |  |

| 2           | טוט/טו            | ADS8558                                                                                                                                                                  | Software mode (HW/SW = 1): Serial data input                                                                                                                                                                 |  |  |  |

| 3           | DIO               | Data bit 12 input/output<br>Output is '0' for the ADS8558                                                                                                                | Connect to BGND                                                                                                                                                                                              |  |  |  |

| 4           | DIO               | Data bit 11 input/output<br>Output is MSB for the ADS8558                                                                                                                | Connect to BGND                                                                                                                                                                                              |  |  |  |

| 5           | DIO/DO            | Data bit 10 input/output                                                                                                                                                 | When SEL_C = 1, data output for channel C When SEL_C = 0, this pin should be tied to BGND                                                                                                                    |  |  |  |

| 6           | DIO/DO            | Data bit 9 input/output                                                                                                                                                  | When SEL_B = 1, data output for channel B When SEL_B = 0, this pin should be tied to BGND When SEL_C = 0, data from channel C1 are also available on this output                                             |  |  |  |

| 7           | DIO/DO            | Data bit 8 input/output                                                                                                                                                  | Data output for channel A When SEL_C = 0, data from channel C0 are also available on this output When SEL_C = 0 and SEL_B = 0, SDO_A acts as the single data output for all channels                         |  |  |  |

| 8           | Р                 | Buffer IO ground, connect to digital ground plane                                                                                                                        |                                                                                                                                                                                                              |  |  |  |

| 9           | Р                 | Buffer IO supply, connect to digital supply (2.7V to 5 of 100nF and 10μF ceramic capacitors to BGND.                                                                     | 5.5V). Decouple with a $1\mu\text{F}$ ceramic capacitor or a combination                                                                                                                                     |  |  |  |

|             |                   | Word mode (WORD/BYTE = 0):<br>Data bit 7 input/output                                                                                                                    |                                                                                                                                                                                                              |  |  |  |

| 10          | DIO/DI/DI         | Byte mode (WORD/BYTE = 1):<br>High byte enable input.<br>When high, the high byte is output first on<br>DB[15:8]. When low, the low byte is output first on<br>DB[15:8]. | Daisy-chain enable input.  When high, DB[5:3] serve as daisy-chain inputs DCIN[A:C]. If daisy-chain mode is not used, connect to BGND.                                                                       |  |  |  |

| 11          | DIO/DI            | Word mode (WORD/BYTE = 0):<br>Data bit 6 input/output                                                                                                                    | Serial interface clock input (36MHz max)                                                                                                                                                                     |  |  |  |

| ""          | DIO/DI            | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                                    | Serial Illienace clock input (Solvinz Max)                                                                                                                                                                   |  |  |  |

| 10          | DIO/DI            | Word mode (WORD/BYTE = 0): Data bit 5 input/output                                                                                                                       | When DC <sub>EN</sub> = 1, daisy-chain data input for channel A                                                                                                                                              |  |  |  |

| 12          | DIO/DI            | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                                    | When DC <sub>EN</sub> = 0, connect to BGND                                                                                                                                                                   |  |  |  |

| 13          | חוט/טו            | Word mode (WORD/BYTE = 0):<br>Data bit 4 input/output                                                                                                                    | When SEL_B = 1 and DC <sub>EN</sub> = 1, daisy-chain data input for channel B                                                                                                                                |  |  |  |

| 13          | БІО/БІ            | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                                    | When DC <sub>EN</sub> = 0, connect to BGND                                                                                                                                                                   |  |  |  |

| 14          | חוט/טו            | Word mode (WORD/BYTE = 0):<br>Data bit 3 input/output                                                                                                                    | When SEL_C = 1 and DC <sub>EN</sub> = 1, daisy-chain data input for channel C                                                                                                                                |  |  |  |

| 14          | וט/טוט            | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                                    | When DC <sub>EN</sub> = 0, connect to BGND                                                                                                                                                                   |  |  |  |

| 15          | חוט/טו            | Word mode (WORD/BYTE = 0):<br>Data bit 2 input/output                                                                                                                    | Select SDO_C input.                                                                                                                                                                                          |  |  |  |

| 15          | וט/טוט            | Byte mode (WORD/BYTE = 1):<br>Connect to BGND or BVDD                                                                                                                    | When high, SDO_C is active. When low, SDO_C is disabled                                                                                                                                                      |  |  |  |

| 16          | DIO/DI            | Word mode (WORD/BYTE = 0):<br>Data bit 1 input/output                                                                                                                    | Select SDO_B input. When high, SDO_B is active. When low, SDO_B is disabled                                                                                                                                  |  |  |  |

|             | 1 2 3 4 5 6 7 8 9 | 1 DIO/DI 2 DIO/DI 3 DIO 4 DIO 5 DIO/DO 6 DIO/DO 7 DIO/DO 8 P 9 P 10 DIO/DI/DI 11 DIO/DI 12 DIO/DI 13 DIO/DI 13 DIO/DI 14 DIO/DI                                          | DIO/DI                                                                                                                                                                                                       |  |  |  |

<sup>(1)</sup> AI = analog input; AIO = analog input/output; DI = digital input; DO = digital output; DIO = digital input/output; and P = power supply.

# **TERMINAL FUNCTIONS (continued)**

|            |                                                               |         | DE                                                                                                                                                                                                                                                                                                                                                          | ESCRIPTION                                                                                                                                                                                       |  |  |  |

|------------|---------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | PIN#                                                          | TYPE(1) | PARALLEL INTERFACE (PAR/SER = 0)                                                                                                                                                                                                                                                                                                                            | SERIAL INTERFACE (PAR/SER = 1)                                                                                                                                                                   |  |  |  |

| DB0/SEL_A  | 17                                                            | DIO/DI  | Word mode (WORD/BYTE = 0): Data bit 0 (LSB) input/output  Byte mode (WORD/BYTE = 1):                                                                                                                                                                                                                                                                        | Select SDO_A input. When high, SDO_A is active. When low, SDO_A is disabled. Should always be high.                                                                                              |  |  |  |

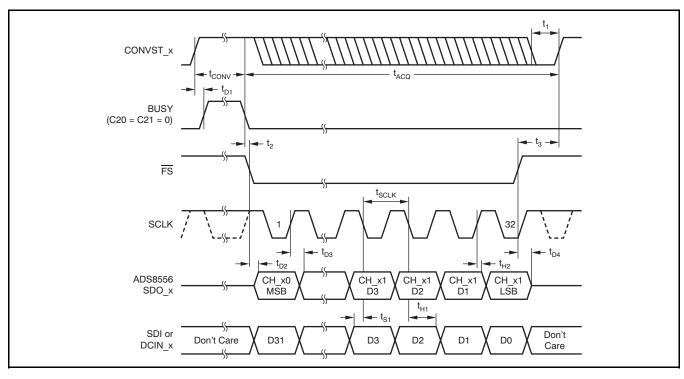

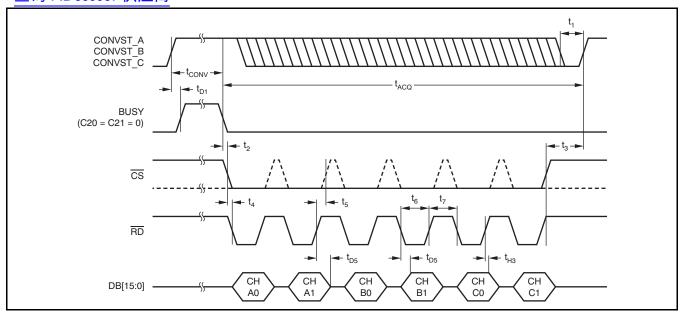

| BUSY/INT   | 18                                                            | DO      | started and remains high during the entire process. are latched to the output register and remains low the In sequential mode (SEQ = 1 in the CR), the BUSY and goes low for a single conversion clock cycle (tcc                                                                                                                                           | output transitions high when a conversion has been started (CLK) whenever a channel pair conversion is completed.  It. This bit transitions high after a conversion has been self has been read. |  |  |  |

| CS/FS      | 19                                                            | DI/DI   | Chip select input. When low, the parallel interface is enabled. When high, the interface is disabled.                                                                                                                                                                                                                                                       | Frame synchronization. The falling edge of FS controls the frame transfer.                                                                                                                       |  |  |  |

| RD         | 20                                                            | DI      | Read data input. When low, the parallel data output is enabled. When high, the data output is disabled.                                                                                                                                                                                                                                                     | Connect to BGND                                                                                                                                                                                  |  |  |  |

| CONVST_C   | 21                                                            | DI      |                                                                                                                                                                                                                                                                                                                                                             | conversion of analog signals at inputs CH_C[1:0]. CONVST_0<br>le, otherwise both ADCs of channel C are put in partial                                                                            |  |  |  |

|            |                                                               |         | Software mode (HW/SW = 1): Conversion start of characteristics of the connect to BGND or BVDD otherwise                                                                                                                                                                                                                                                     | nannel pair C in sequential mode (CR bit C23 = 1) only;                                                                                                                                          |  |  |  |

| CONVST_B   | 22                                                            | DI      |                                                                                                                                                                                                                                                                                                                                                             | conversion of analog signals at inputs CH_B[1:0]. CONVST_E<br>le; otherwise, both ADCs of channel B are put into partial                                                                         |  |  |  |

|            |                                                               |         | Software mode (HW/SW = 1): Conversion start of channel pair B in sequential mode (CR bit C23 = 1) only; connect to BGND or BVDD otherwise                                                                                                                                                                                                                   |                                                                                                                                                                                                  |  |  |  |

| CONVST_A   | 23                                                            | DI      | Hardware mode (HW/SW = 0): Conversion start of channel pair A.  The rising edge of this signal initiates simultaneous conversion of analog signals at inputs CH_A[1:0]. CONVST should remain high during the entire conversion cycle; otherwise, both ADCs of channel A are put into partial power-down mode (see the Reset and Power-down Modes sections). |                                                                                                                                                                                                  |  |  |  |

|            |                                                               |         | Software mode (HW/SW = 1): Conversion start of al (CR bit C23 = 1): Conversion start of channel pair A                                                                                                                                                                                                                                                      |                                                                                                                                                                                                  |  |  |  |

| STBY       | 24                                                            | DI      | Standby mode input. When low, the entire device is When high, the device operates in normal mode.                                                                                                                                                                                                                                                           | powered-down (including the internal clock and reference).                                                                                                                                       |  |  |  |

| AGND       | 25, 32,<br>37, 38,<br>43, 44,<br>49, 52,<br>53, 55,<br>57, 59 | Р       | Analog ground, connect to analog ground plane Pin 25 may have a dedicated ground if the difference ±300mV.                                                                                                                                                                                                                                                  | e between its potential and AGND is always kept within                                                                                                                                           |  |  |  |

| AVDD       | 26, 34,<br>35, 40,<br>41, 46,<br>47, 50,<br>60                | Р       | additional 10μF capacitor to AGND close to the devi                                                                                                                                                                                                                                                                                                         | pin with a 100nF ceramic capacitor to AGND. Use an ce but without compromising the placement of the smaller ly if the difference between its potential and AVDD is always                        |  |  |  |

| DANCE/VOLK | 27                                                            | DI/DIO  | Hardware mode (HW/SW = 0): Input voltage range s<br>When low, the analog input range is ±4V <sub>REF</sub> . When                                                                                                                                                                                                                                           |                                                                                                                                                                                                  |  |  |  |

| RANGE/XCLK | 27                                                            | DI/DIO  |                                                                                                                                                                                                                                                                                                                                                             | lock input, if CR bit C11 (CLKSEL) is set high or internal I) is set high. If not used, connect to BVDD or BGND.                                                                                 |  |  |  |

| RESET      | 28                                                            | DI      | Reset input, active high. Aborts any ongoing converse RESET pulse should be at least 50ns long.                                                                                                                                                                                                                                                             | sions. Resets the internal control register to 0x000003FF. The                                                                                                                                   |  |  |  |

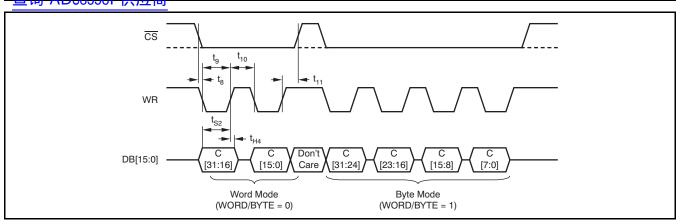

| WORD/BYTE  | 29                                                            | DI      | Output mode selection input. When low, data are transferred in word mode using DB[15:0]. When high, data are transferred in byte mode using DB[15:8] with the byte order controlled by HB $_{\rm EN}$ pin while two accesses are required for a complete 16-bit transfer.                                                                                   | Connect to BGND                                                                                                                                                                                  |  |  |  |

| HVSS       | 30                                                            | Р       | Negative supply voltage for the analog inputs (–16.5 Decouple with a 100nF ceramic capacitor to AGND to the device but without compromising the placeme                                                                                                                                                                                                     | placed next to the device and a 10μF capacitor to AGND clos                                                                                                                                      |  |  |  |

<u>₩豐梅•飛D\$8558I"供应商</u>

# **TERMINAL FUNCTIONS (continued)**

|                       |      |         | DE                                                                                                                                                                                                                                                             | ESCRIPTION                                                                                                                                                                                                                                                            |

|-----------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | PIN# | TYPE(1) | PARALLEL INTERFACE (PAR/SER = 0)                                                                                                                                                                                                                               | SERIAL INTERFACE (PAR/SER = 1)                                                                                                                                                                                                                                        |

| HVDD                  | 31   | Р       |                                                                                                                                                                                                                                                                | 16.5V). Decouple with a 100nF ceramic capacitor to AGND GND close to the device but without compromising the                                                                                                                                                          |

| CH_A0                 | 33   | AI      | Analog input of channel A0. The input voltage range (RANGE_A) in software mode.                                                                                                                                                                                | is controlled by RANGE pin in hardware mode or CR bit C2                                                                                                                                                                                                              |

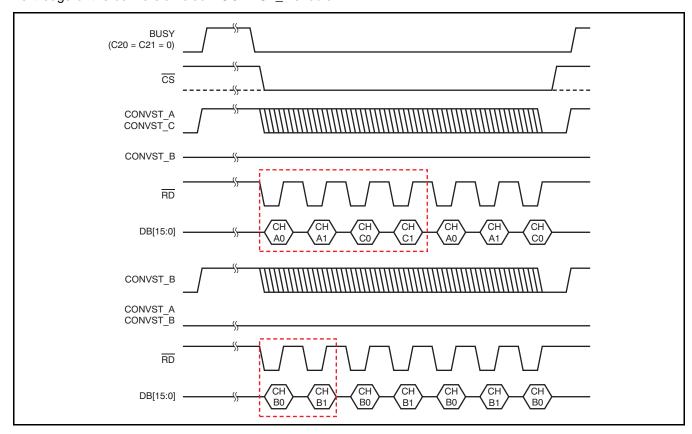

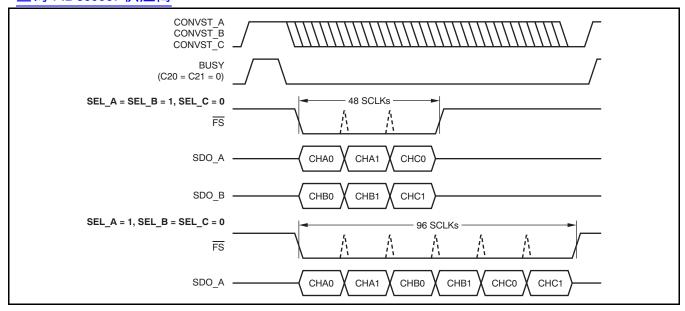

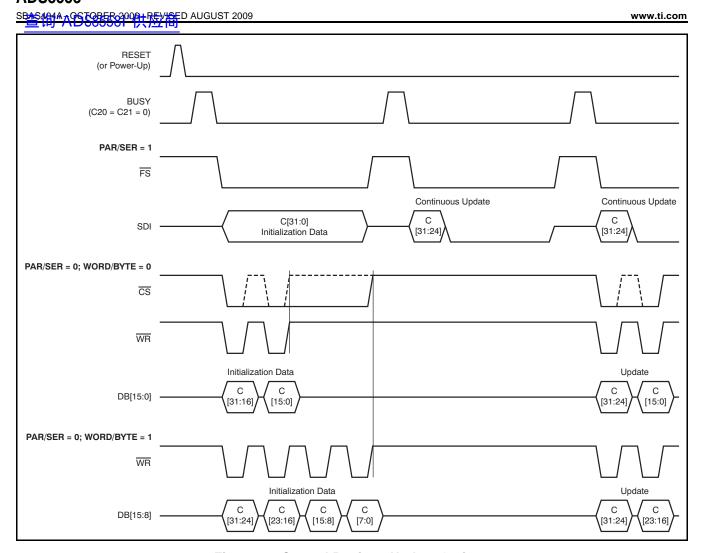

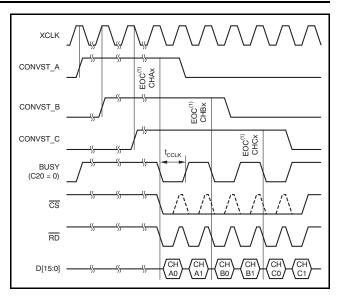

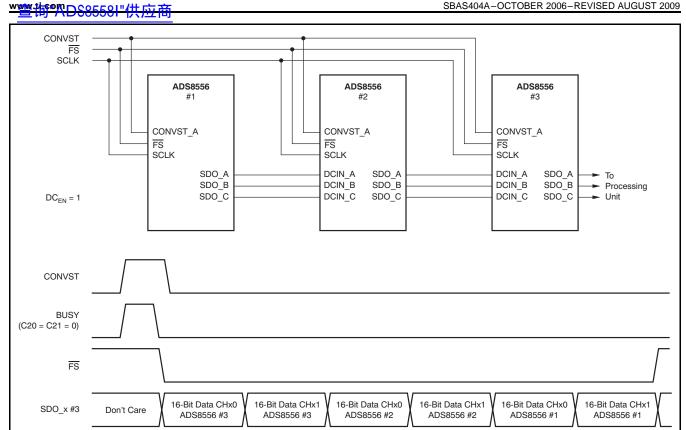

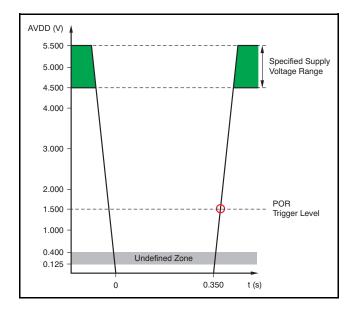

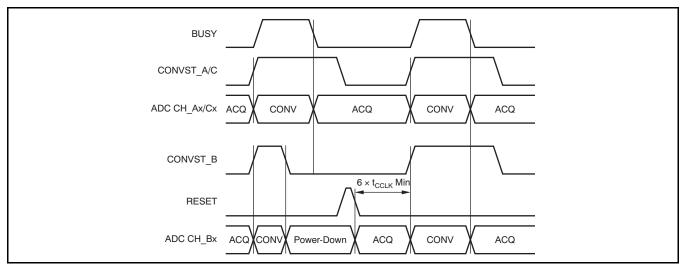

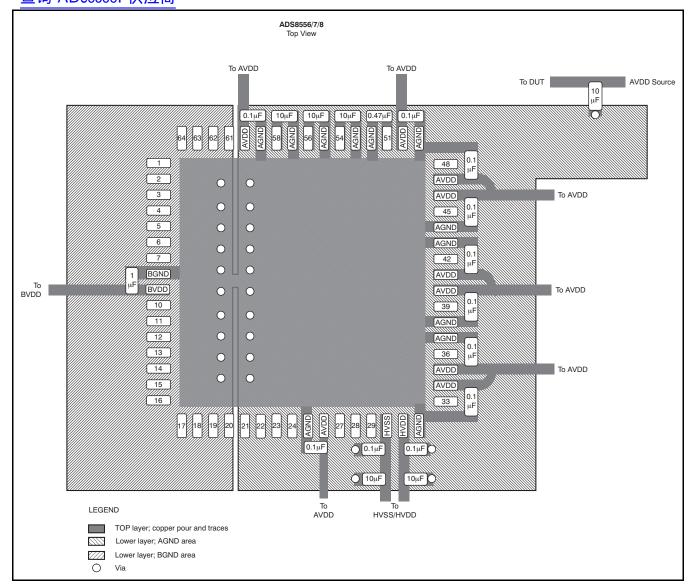

| CH_A1                 | 36   | AI      | Analog input of channel A1. The input voltage range (RANGE_A) in software mode.                                                                                                                                                                                | e is controlled by RANGE pin in hardware mode or CR bit C2                                                                                                                                                                                                            |