# Zero-Drift, Single-Supply, Rail-to-Rail Input/Output Operational Amplifiers

# AD8571/AD8572/AD8574

#### **FEATURES**

Low offset voltage: 1  $\mu V$  Input offset drift: 0.005  $\mu V/^{\circ}C$  Rail-to-rail input and output swing 5 V/2.7~V single-supply operation

High gain: 145 dB typical CMRR: 140 dB typical PSRR: 130 dB typical

Ultralow input bias current: 10 pA typical Low supply current: 750 µA/op amp Overload recovery time: 50 µs No external capacitors required

#### **APPLICATIONS**

Temperature sensors

Pressure sensors

Precision current sensing

Strain gage amplifiers

Medical instrumentation

Thermocouple amplifiers

#### **GENERAL DESCRIPTION**

This family of amplifiers has ultralow offset, drift, and bias current. The AD8571, AD8572, and AD8574 are single, dual, and quad amplifiers, respectively, featuring rail-to-rail input and output swings. All are guaranteed to operate from 2.7 V to 5 V single supply.

The AD857x family provides benefits previously found only in expensive auto-zeroing or chopper-stabilized amplifiers. Using Analog Devices, Inc. topology, these zero-drift amplifiers combine low cost with high accuracy. (No external capacitors are required.) Using a patented spread-spectrum, auto-zero technique, the AD857x family eliminates the intermodulation effects from interaction of the chopping function with the signal frequency in ac applications.

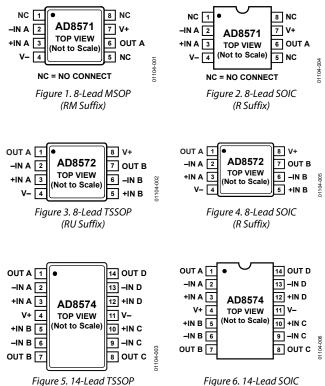

#### PIN CONFIGURATIONS

Figure 6. 14-Lead SOIC (R Suffix)

With an offset voltage of only 1  $\mu$ V and drift of 0.005  $\mu$ V/°C, the AD857x family is perfectly suited for applications where error sources cannot be tolerated. Position and pressure sensors, medical equipment, and strain gage amplifiers benefit greatly from nearly zero drift over their operating temperature range. Many more systems require the rail-to-rail input and output swings provided by the AD857x family.

(RU Suffix)

The AD857x family is specified for the extended industrial/automotive ( $-40^{\circ}$ C to  $+125^{\circ}$ C) temperature range. The AD8571 single amplifier is available in 8-lead MSOP and narrow 8-lead SOIC packages. The AD8572 dual amplifier is available in 8-lead narrow SOIC and 8-lead TSSOP surface-mount packages. The AD8574 quad amplifier is available in 14-lead narrow SOIC and 14-lead TSSOP packages.

# AD8571/AD8572/AD8574 查询"AD8571ARMZ-R2"供应商

# **TABLE OF CONTENTS**

| Features1                                       |

|-------------------------------------------------|

| Applications                                    |

| Pin Configurations                              |

| General Description                             |

| Revision History                                |

| Specifications                                  |

| 5 V Electrical Characteristics                  |

| 2.7 V Electrical Characteristics                |

| Absolute Maximum Ratings5                       |

| Thermal Characteristics5                        |

| ESD Caution5                                    |

| Typical Performance Characteristics6            |

| Functional Description                          |

| Amplifier Architecture14                        |

| Basic Auto-Zero Amplifier Theory14              |

| Auto-Zero Phase14                               |

| Amplification Phase15                           |

| High Gain, CMRR, and PSRR16                     |

| Maximizing Performance Through Proper Layout 16 |

|                                                 |

|                                                 |

|   | 1/f Noise Characteristics                              | 17 |

|---|--------------------------------------------------------|----|

|   | Random Auto-Zero Correction Eliminates Intermodulation |    |

|   | Distortion                                             | 17 |

| B | roadband and External Resistor Noise Considerations    | 18 |

|   | Output Overdrive Recovery                              | 18 |

|   | Input Overvoltage Protection                           | 18 |

|   | Output Phase Reversal                                  | 18 |

|   | Capacitive Load Drive                                  | 19 |

|   | Power-Up Behavior                                      | 19 |

| A | pplications2                                           | 20 |

|   | 5 V Precision Strain Gage Circuit                      | 20 |

|   | 3 V Instrumentation Amplifier                          | 20 |

|   | High Accuracy Thermocouple Amplifier                   | 21 |

|   | Precision Current Meter                                | 21 |

|   | Precision Voltage Comparator                           | 21 |

| О | outline Dimensions2                                    | 22 |

|   | Ordering Guide                                         | 23 |

#### **REVISION HISTORY**

| 5/07—Rev. B to Rev. C                                 |    |

|-------------------------------------------------------|----|

| Changes to Features                                   | 1  |

| Changes to Table 1                                    | 3  |

| Changes to Table 2                                    | 4  |

| Changes to Basic Auto-Zero Amplifier Theory Section . | 14 |

| Changes to Figure 50                                  | 15 |

| Changes to Figure 55                                  | 16 |

| Changes to Figure 66                                  |    |

| Undated Outline Dimensions                            | 22 |

#### 9/06—Rev. A to Rev. B

| Changes to Table 1                               | 3    |

|--------------------------------------------------|------|

| Changes to Table 2                               | 4    |

| Changes to Figure 50                             | . 14 |

| Changes to Figure 51                             | . 15 |

| Changes to Figure 66                             | . 21 |

| Deleted Figure 69 and SPICE Macro-Model Section  | . 17 |

| Deleted SPICE Macro-Model for the AD857x Section | . 18 |

| Updated Outline Dimensions                       | . 22 |

| Changes to Ordering Guide                        | . 23 |

| 7/03—Rev. 0 to Rev. A                            |      |

| Renumbered Figures                               | rsal |

| Changes to Ordering Guide                        | 4    |

| Change to Figure 15.                             | . 16 |

| Updated Outline Dimensions                       | . 19 |

|                                                  |      |

10/99—Revision 0: Initial Version

# **SPECIFICATIONS**

## **5 V ELECTRICAL CHARACTERISTICS**

$V_S$  = 5 V,  $V_{CM}$  = 2.5 V,  $V_O$  = 2.5 V,  $T_A$  = 25°C, unless otherwise noted.

Table 1.

| Parameter                              | Symbol                                | Conditions                                                                                 | Min  | Тур        | Max  | Unit             |

|----------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------|------|------------|------|------------------|

| INPUT CHARACTERISTICS                  |                                       |                                                                                            |      |            |      |                  |

| Offset Voltage                         | Vos                                   |                                                                                            |      | 1          | 5    | μV               |

|                                        |                                       | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |      |            | 10   | μV               |

| Input Bias Current                     | I <sub>B</sub>                        |                                                                                            |      | 10         | 50   | pА               |

| AD8571/AD8574                          |                                       | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |      | 1.0        | 1.5  | nA               |

| AD8572                                 |                                       | $-40$ °C $\leq T_A \leq +85$ °C                                                            |      | 160        | 300  | pА               |

|                                        |                                       | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                            |      | 2.5        | 4    | nA               |

| Input Offset Current                   | los                                   |                                                                                            |      | 20         | 70   | рА               |

| AD8571/AD8574                          |                                       | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |      | 150        | 200  | рA               |

| AD8572                                 |                                       | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                      |      | 30         | 150  | рA               |

|                                        |                                       | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |      | 150        | 400  | pA               |

| Input Voltage Range                    |                                       |                                                                                            | 0    |            | 5    | V                |

| Common-Mode Rejection Ratio            | CMRR                                  | $V_{CM} = 0 V \text{ to } 5 V$                                                             | 120  | 140        | •    | dB               |

| common mode nejection natio            | Civilia                               | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                   | 115  | 130        |      | dB               |

| Large Signal Voltage Gain <sup>1</sup> | Avo                                   | $R_L = 10 \text{ k}\Omega$ , $V_O = 0.3 \text{ V to } 4.7 \text{ V}$                       | 125  | 145        |      | dB               |

| Large Signal Voltage Gain              | 7.00                                  | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                   | 120  | 135        |      | dB               |

| Offset Voltage Drift                   | $\Delta V_{OS}/\Delta_T$              | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                   | 120  | 0.005      | 0.04 | μV/°C            |

| OUTPUT CHARACTERISTICS                 | Δ V OS/Δ1                             | -40 C S TA S +123 C                                                                        |      | 0.003      | 0.04 | μν/ С            |

|                                        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | D 100 kO to CND                                                                            | 4.00 | 4.000      |      | V                |

| Output Voltage High                    | V <sub>OH</sub>                       | $R_L = 100 \text{ k}\Omega$ to GND                                                         | 4.99 | 4.998      |      | V                |

|                                        |                                       | $R_L = 100 \text{ k}\Omega \text{ to GND @ } -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 4.99 | 4.997      |      |                  |

|                                        |                                       | $R_L = 10 \text{ k}\Omega \text{ to GND}$                                                  | 4.95 | 4.98       |      | V                |

|                                        |                                       | $R_L = 10 \text{ k}\Omega \text{ to GND } @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$  | 4.95 | 4.975      |      | V                |

| Output Voltage Low                     | V <sub>OL</sub>                       | $R_L = 100 \text{ k}\Omega \text{ to V} +$                                                 |      | 1          | 10   | mV               |

|                                        |                                       | $R_L = 100 \text{ k}\Omega \text{ to V+ } @ -40^{\circ}\text{C to +125}^{\circ}\text{C}$   |      | 2          | 10   | mV               |

|                                        |                                       | $R_L = 10 \text{ k}\Omega \text{ to V} +$                                                  |      | 10         | 30   | mV               |

|                                        |                                       | $R_L = 10 \text{ k}\Omega \text{ to V+ } @ -40^{\circ}\text{C to +125}^{\circ}\text{C}$    |      | 15         | 30   | mV               |

| Short-Circuit Limit                    | I <sub>SC</sub>                       |                                                                                            | ±25  | ±50        |      | mA               |

|                                        |                                       | −40°C to +125°C                                                                            |      | ±40        |      | mA               |

| Output Current                         | lo                                    |                                                                                            |      | ±30        |      | mA               |

|                                        |                                       | −40°C to +125°C                                                                            |      | ±15        |      | mA               |

| POWER SUPPLY                           |                                       |                                                                                            |      |            |      |                  |

| Power Supply Rejection Ratio           | PSRR                                  | $V_S = 2.7 \text{ V to } 5.5 \text{ V}$                                                    | 120  | 130        |      | dB               |

|                                        |                                       | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                     | 115  | 130        |      | dB               |

| Supply Current/Amplifier               | I <sub>SY</sub>                       | $V_O = 0 V$                                                                                |      | 850        | 975  | μΑ               |

|                                        |                                       | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |      | 1000       | 1075 | μΑ               |

| DYNAMIC PERFORMANCE                    |                                       |                                                                                            |      |            |      |                  |

| Slew Rate                              | SR                                    | $R_L = 10 \text{ k}\Omega$                                                                 |      | 0.4        |      | V/µs             |

| Overload Recovery Time                 |                                       |                                                                                            |      | 0.05       | 0.3  | ms               |

| Gain Bandwidth Product                 | GBP                                   |                                                                                            |      | 1.5        |      | MHz              |

| NOISE PERFORMANCE                      |                                       |                                                                                            |      |            |      | 1                |

|                                        | e <sub>n</sub> p-p                    | 0 Hz to 10 Hz                                                                              |      | 1.3        |      | μV p-p           |

| Voltage Noise                          | 1 5 1 7 7                             | J (0 10112                                                                                 | 1    |            |      |                  |

| Voltage Noise                          |                                       | 0 Hz to 1 Hz                                                                               |      | 0.41       |      | l IIV n-n        |

| Voltage Noise  Voltage Noise Density   | en                                    | 0 Hz to 1 Hz<br>f = 1 kHz                                                                  |      | 0.41<br>51 |      | μV p-p<br>nV/√Hz |

$<sup>^{\</sup>mbox{\tiny 1}}$  Gain testing is dependent upon test bandwidth.

# AD8571/AD8572/AD8574 查询"AD8571ARMZ-R2"供应商

## 2.7 V ELECTRICAL CHARACTERISTICS

$V_S$  = 2.7 V,  $V_{CM}$  = 1.35 V,  $V_O$  = 1.35 V,  $T_A$  = 25°C, unless otherwise noted.

Table 2.

| Parameter                              | Symbol             | Conditions                                                                                 | Min   | Тур        | Max   | Unit       |

|----------------------------------------|--------------------|--------------------------------------------------------------------------------------------|-------|------------|-------|------------|

| INPUT CHARACTERISTICS                  |                    |                                                                                            |       |            |       |            |

| Offset Voltage                         | Vos                |                                                                                            |       | 1          | 5     | μV         |

|                                        |                    | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |       |            | 10    | μV         |

| Input Bias Current                     | I <sub>B</sub>     |                                                                                            |       | 10         | 50    | pА         |

| AD8571/AD8574                          |                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                     |       | 1.0        | 1.5   | nA         |

| AD8572                                 |                    | $-40$ °C $\leq T_A \leq +85$ °C                                                            |       | 160        | 300   | pА         |

|                                        |                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                     |       | 2.5        | 4     | nA         |

| Input Offset Current                   | los                |                                                                                            |       | 10         | 50    | pА         |

| AD8571/AD8574                          |                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                     |       | 150        | 200   | pА         |

| AD8572                                 |                    | $-40$ °C $\leq T_A \leq +85$ °C                                                            |       | 30         | 150   | pА         |

|                                        |                    | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                            |       | 150        | 400   | pА         |

| Input Voltage Range                    |                    |                                                                                            | 0     |            | 2.7   | V          |

| Common-Mode Rejection Ratio            | CMRR               | $V_{CM} = 0 V \text{ to } 2.7 V$                                                           | 115   | 130        |       | dB         |

|                                        |                    | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                   | 110   | 130        |       | dB         |

| Large Signal Voltage Gain <sup>1</sup> | Avo                | $R_L = 10 \text{ k}\Omega$ , $V_0 = 0.3 \text{ V to } 2.4 \text{ V}$                       | 110   | 140        |       | dB         |

|                                        | 1.10               | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                   | 105   | 130        |       | dB         |

| Offset Voltage Drift                   | ΔVος/ΔΤ            | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                   |       | 0.005      | 0.04  | μV/°C      |

| OUTPUT CHARACTERISTICS                 | 2103/21            | 10 0 1 1/2 1/20 0                                                                          |       | 0.000      | 0.0 . | p.,, c     |

| Output Voltage High                    | V <sub>OH</sub>    | $R_L = 100 \text{ k}\Omega \text{ to GND}$                                                 | 2.685 | 2.697      |       | V          |

| output voltage riigii                  | VOH                | $R_L = 100 \text{ k}\Omega \text{ to GND } @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 2.685 | 2.696      |       | v          |

|                                        |                    | $R_L = 10 \text{ k}\Omega \text{ to GND}$                                                  | 2.67  | 2.68       |       | v          |

|                                        |                    | $R_L = 10 \text{ k}\Omega \text{ to GND } @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$  | 2.67  | 2.675      |       | v          |

| Output Voltage Low                     | V <sub>OL</sub>    | $R_L = 100 \text{ k}\Omega \text{ to V+}$                                                  | 2.07  | 1          | 10    | mV         |

| Output Voltage Low                     | VOL                | $R_L = 100 \text{ k}\Omega \text{ to V} + @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$  |       | 2          | 10    | mV         |

|                                        |                    | $R_L = 100 \text{ kg/s} \text{ to V} + 60 \text{ cm} \text{ for } 123 \text{ cm}$          |       | 10         | 20    | mV         |

|                                        |                    | $R_L = 10 \text{ k}\Omega \text{ to V} + @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$   |       | 15         | 20    | mV         |

| Short-Circuit Limit                    | I <sub>SC</sub>    | 11 - 10 K2 to V+ @ -40 C to +125 C                                                         | ±10   | ±15        | 20    | mA         |

| Short-circuit Limit                    | ISC                | -40°C to +125°C                                                                            | 110   | ±10        |       | mA         |

| Output Current                         | lo                 | -40 C to +123 C                                                                            |       | ±10<br>±10 |       | mA         |

| Output Current                         | 10                 | -40°C to +125°C                                                                            |       | ±10<br>±5  |       | mA         |

| POWER SUPPLY                           |                    | -40 C t0 +123 C                                                                            |       | Ξ3         |       | IIIA       |

|                                        | PSRR               | V - 27V+055V                                                                               | 120   | 130        |       | dB         |

| Power Supply Rejection Ratio           | PORK               | $V_S = 2.7 \text{ V to } 5.5 \text{ V}$                                                    |       |            |       |            |

| Supply Current/Amplifier               |                    | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$<br>$V_{0} = 0 \text{ V}$          | 115   | 130<br>750 | 900   | dB         |

| Supply Current/Ampliner                | I <sub>SY</sub>    |                                                                                            |       |            |       | μΑ         |

| DVALANIC DEDECORMANICE                 |                    | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                            |       | 950        | 1000  | μΑ         |

| DYNAMIC PERFORMANCE                    | CD                 | D 1010                                                                                     |       | 0.5        |       | \//··-     |

| Slew Rate                              | SR                 | $R_L = 10 \text{ k}\Omega$                                                                 |       | 0.5        |       | V/µs       |

| Overload Recovery Time                 | CDD                |                                                                                            |       | 0.05       |       | ms<br>MII- |

| Gain Bandwidth Product                 | GBP                |                                                                                            |       | 1          |       | MHz        |

| NOISE PERFORMANCE                      |                    |                                                                                            |       | 2.0        |       |            |

| Voltage Noise                          | e <sub>n</sub> p-p | 0 Hz to 10 Hz                                                                              |       | 2.0        |       | μV p-p     |

| Voltage Noise Density                  | e <sub>n</sub>     | f = 1  kHz                                                                                 |       | 94         |       | nV/√Hz     |

| Current Noise Density                  | i <sub>n</sub>     | f = 10 Hz                                                                                  |       | 2          |       | fA/√Hz     |

$<sup>^{\</sup>mbox{\tiny 1}}$  Gain testing is dependent upon test bandwidth.

# **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                               | Rating               |

|-----------------------------------------|----------------------|

| Supply Voltage                          | 6 V                  |

| Input Voltage                           | GND to $V_S + 0.3 V$ |

| Differential Input Voltage <sup>1</sup> | ±5.0 V               |

| ESD (Human Body Model)                  | 2000 V               |

| Output Short-Circuit Duration to GND    | Indefinite           |

| Storage Temperature Range               | −65°C to +150°C      |

| Operating Temperature Range             | -40°C to +125°C      |

| Junction Temperature Range              | −65°C to +150°C      |

| Lead Temperature (Soldering, 60 sec)    | 300°C                |

$<sup>^1</sup>$  Differential input voltage is limited to  $\pm 5.0$  V or the supply voltage, whichever is less.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

$\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for a device soldered in a circuit board for SOIC and TSSOP packages.

**Table 4. Thermal Resistance**

| Package Type       | θја | <b>Ө</b> лс | Unit |

|--------------------|-----|-------------|------|

| 8-Lead MSOP (RM)   | 190 | 44          | °C/W |

| 8-Lead TSSOP (RU)  | 240 | 43          | °C/W |

| 8-Lead SOIC (R)    | 158 | 43          | °C/W |

| 14-Lead TSSOP (RU) | 180 | 36          | °C/W |

| 14-Lead SOIC (R)   | 120 | 36          | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# TYPICAL PERFORMANCE CHARACTERISTICS

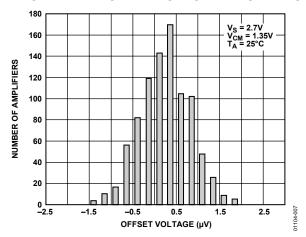

Figure 7. Input Offset Voltage Distribution at 2.7 V

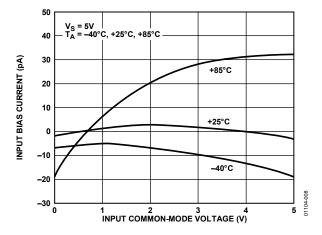

Figure 8. Input Bias Current vs. Input Common-Mode Voltage

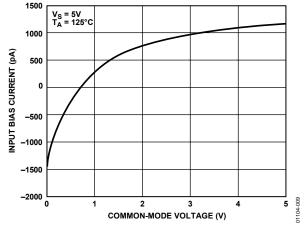

Figure 9. Input Bias Current vs. Common-Mode Voltage

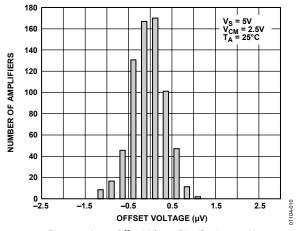

Figure 10. Input Offset Voltage Distribution at 5 V

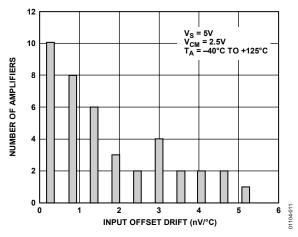

Figure 11. Input Offset Voltage Drift Distribution at 5 V

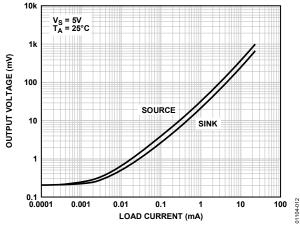

Figure 12. Output Voltage to Supply Rail vs. Output Current at 5 V

# AD8571/AD8572/AD8574

## 查询"AD8571ARMZ-R2"供应商

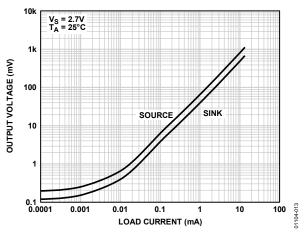

Figure 13. Output Voltage to Supply Rail vs. Output Current at 2.7 V

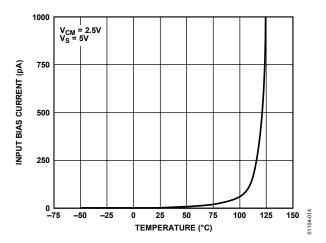

Figure 14. Input Bias Current vs. Temperature

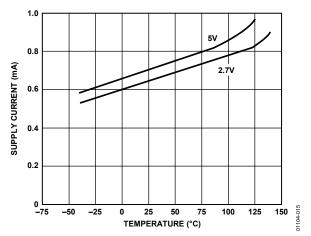

Figure 15. Supply Current vs. Temperature

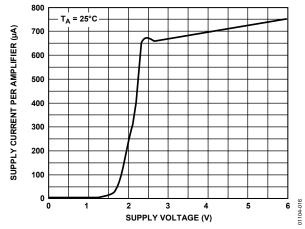

Figure 16. Supply Current vs. Supply Voltage

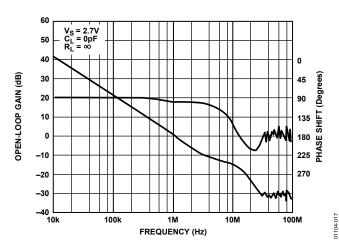

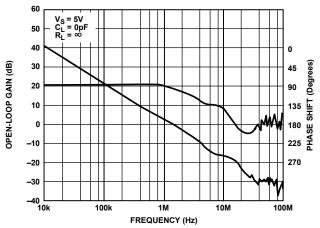

Figure 17. Open-Loop Gain and Phase Shift vs. Frequency at 2.7 V

Figure 18. Open-Loop Gain and Phase Shift vs. Frequency at 5 V

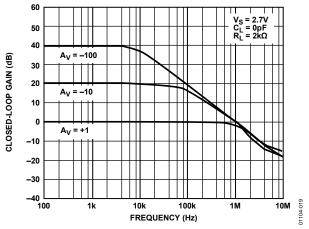

Figure 19. Closed-Loop Gain vs. Frequency at 2.7 V

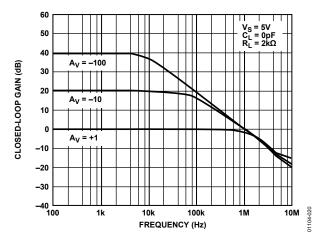

Figure 20. Closed-Loop Gain vs. Frequency at 5 V

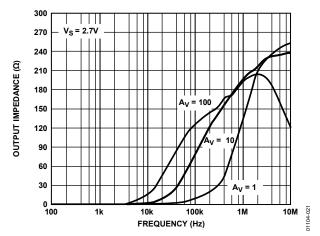

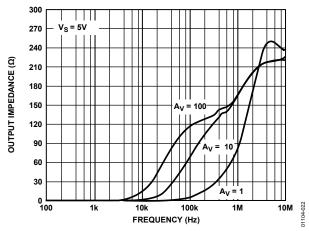

Figure 21. Output Impedance vs. Frequency at 2.7 V

Figure 22. Output Impedance vs. Frequency at 5 V

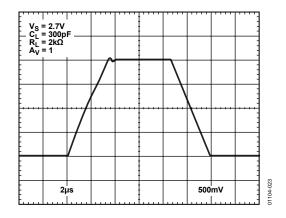

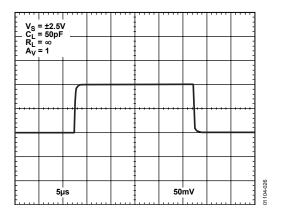

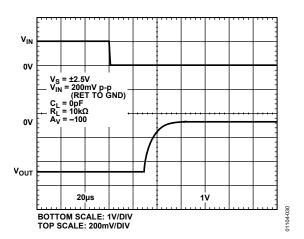

Figure 23. Large Signal Transient Response at 2.7 V

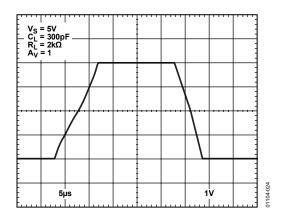

Figure 24. Large Signal Transient Response at 5 V

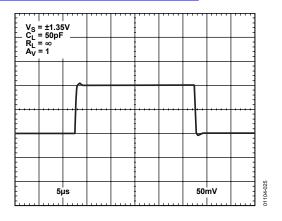

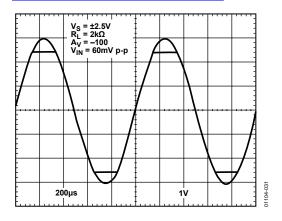

Figure 25. Small Signal Transient Response at 2.7 V

Figure 26. Small Signal Transient Response at 5 V

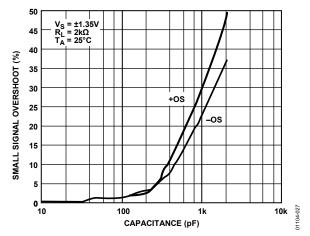

Figure 27. Small Signal Overshoot vs. Load Capacitance at 2.7 V

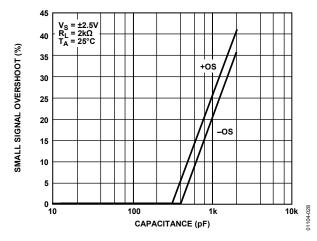

Figure 28. Small Signal Overshoot vs. Load Capacitance at 5 V

Figure 29. Positive Overvoltage Recovery

Figure 30. Negative Overvoltage Recovery

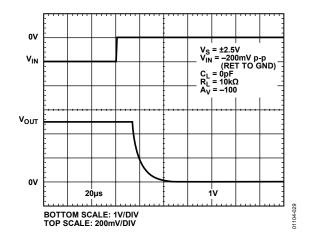

Figure 31. No Phase Reversal

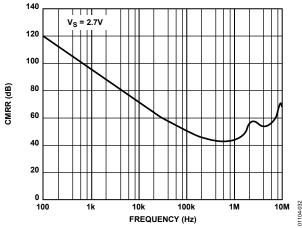

Figure 32. CMRR vs. Frequency at 2.7 V

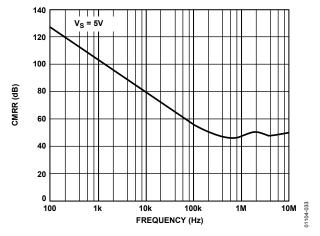

Figure 33. CMRR vs. Frequency at 5 V

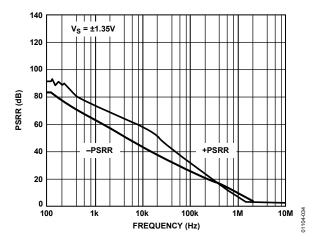

Figure 34. PSRR vs. Frequency at  $\pm 1.35 \, V$

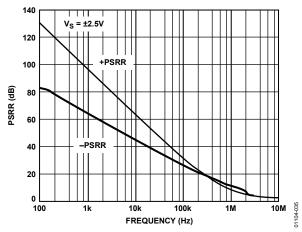

Figure 35. PSRR vs. Frequency at ±2.5 V

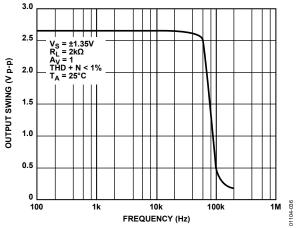

Figure 36. Maximum Output Swing vs. Frequency at 2.7 V

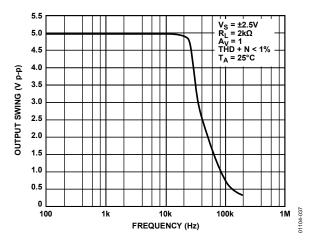

Figure 37. Maximum Output Swing vs. Frequency at 5 V

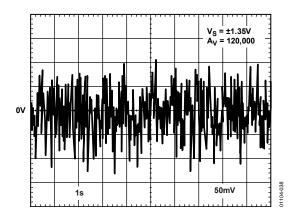

Figure 38. 0.1 Hz to 10 Hz Noise at 2.7 V

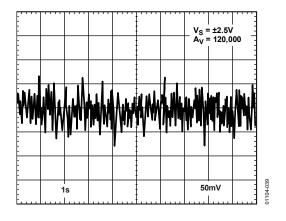

Figure 39. 0.1 Hz to 10 Hz Noise at 5 V

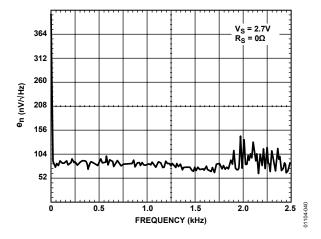

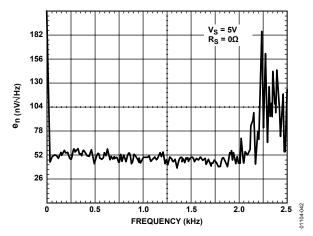

Figure 40. Voltage Noise Density at 2.7 V from 0 Hz to 2.5 kHz

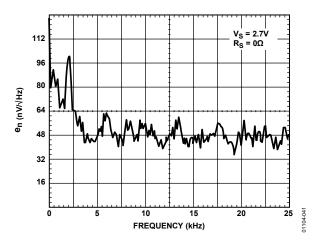

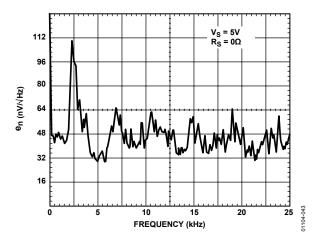

Figure 41. Voltage Noise Density at 2.7 V from 0 Hz to 25 kHz

Figure 42. Voltage Noise Density at 5 V from 0 Hz to 2.5 kHz

Figure 43. Voltage Noise Density at 5 V from 0 Hz to 25 kHz

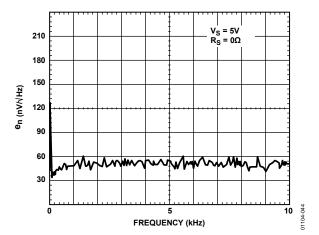

Figure 44. Voltage Noise Density at 5 V from 0 Hz to 10 Hz

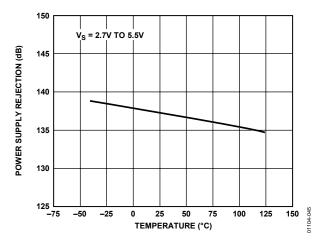

Figure 45. Power Supply Rejection vs. Temperature

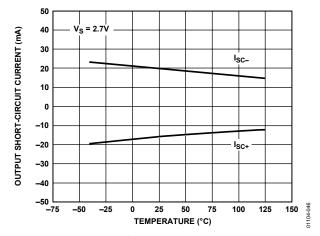

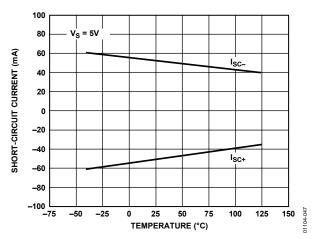

Figure 46. Output Short-Circuit Current vs. Temperature

# AD8571/AD8572/AD8574

# 查询"AD8571ARMZ-R2"供应商

Figure 47. Output Short-Circuit Current vs. Temperature

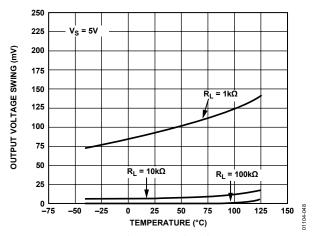

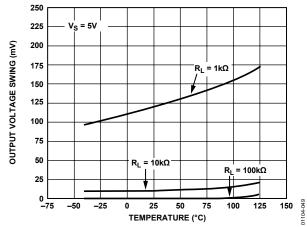

Figure 48. Output Voltage to Supply Rail vs. Temperature

Figure 49. Output Voltage to Supply Rail vs. Temperature

## **FUNCTIONAL DESCRIPTION**

The AD8571/AD8572/AD8574 are CMOS amplifiers that achieve their high degree of precision through random frequency auto-zero stabilization. The autocorrection topology allows the AD857x to maintain its low offset voltage over a wide temperature range, and the randomized auto-zero clock eliminates any intermodulation distortion (IMD) errors at the amplifier output.

The AD857x can be run from a single-supply voltage as low as 2.7 V. The extremely low offset voltage of 1  $\mu V$  and no IMD products allow the amplifier to be easily configured for high gains without risk of excessive output voltage errors, which makes the AD857x an ideal amplifier for applications requiring both dc precision and low distortion for ac signals. The extremely small temperature drift of 5 nV/°C ensures a minimum of offset voltage error over its  $-40\,^{\circ}\text{C}$  to  $+125\,^{\circ}\text{C}$  temperature range. These combined features make the AD857x an excellent choice for a variety of sensitive measurement and automotive applications.

#### **AMPLIFIER ARCHITECTURE**

Each AD857x op amp consists of two amplifiers: a main amplifier and a secondary amplifier that is used to correct the offset voltage of the main amplifier. Both consist of a rail-to-rail input stage, allowing the input common-mode voltage range to reach both supply rails. The input stage consists of an NMOS differential pair operating concurrently with a parallel PMOS differential pair. The outputs from the differential input stages are combined in another gain stage whose output is used to drive a rail-to-rail output stage.

The wide voltage swing of the amplifier is achieved by using two output transistors in a common-source configuration. The output voltage range is limited by the drain-to-source resistance of these transistors. As the amplifier is required to source or sink more output current, the voltage drop across these transistors increases due to their on resistance ( $R_{\rm DS}$ ). Simply put, the output voltage does not swing as close to the rail under heavy output current conditions as it does with light output current. This is a characteristic of all rail-to-rail output amplifiers. Figure 12 and Figure 13 show how close the output voltage can get to the rails with a given output current. The output of the AD857x is short-circuit protected to approximately 50 mA of current.

The AD857x amplifiers have exceptional gain, yielding greater than 120 dB of open-loop gain with a load of 2 k $\Omega$ . Because the output transistors are configured in a common-source configuration, the gain of the output stage, and thus the open-loop gain of the amplifier, is dependent on the load resistance. Open-loop gain decreases with smaller load resistances, which is another characteristic of rail-to-rail output amplifiers.

#### **BASIC AUTO-ZERO AMPLIFIER THEORY**

Autocorrection amplifiers are not a new technology. Various IC implementations have been available for more than 15 years, and some improvements have been made over time. The AD857x design offers a number of significant performance improvements over older versions while attaining a very substantial reduction in device cost. This section offers a simplified explanation of how the AD857x is able to offer extremely low offset voltages and high open-loop gains.

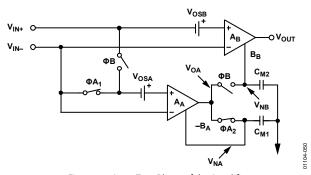

As noted in the Amplifier Architecture section, each AD857x op amp contains two internal amplifiers. One is used as the primary amplifier, the other as an autocorrection, or nulling, amplifier. Each amplifier has an associated input offset voltage that can be modeled as a dc voltage source in series with the noninverting input. In Figure 50 and Figure 51, these are labeled as  $V_{\rm OSA}$  and  $V_{\rm OSB}$ , where A denotes the nulling amplifier and B denotes the primary amplifier. The open-loop gain for the +IN and –IN inputs of each amplifier is given as  $A_{\rm X}$ . Both amplifiers also have a third voltage input with an associated open-loop gain of  $B_{\rm X}$ .

There are two modes of operation determined by the action of two sets of switches in the amplifier: an auto-zero phase and an amplification phase.

#### **AUTO-ZERO PHASE**

In this phase, all  $\phi A$  switches are closed, and all  $\phi B$  switches are opened. Here, the nulling amplifier is taken out of the gain loop by shorting its two inputs together. Of course, there is a degree of offset voltage, shown as  $V_{OSA}$ , inherent in the nulling amplifier that maintains a potential difference between the +IN and –IN inputs. The nulling amplifier feedback loop is closed through  $\phi A_2$ , and  $V_{OSA}$  appears at the output of the nulling amplifier and on  $C_{M1}$ , an internal capacitor in the AD857x. Mathematically, this can be expressed in the time domain as

$$V_{OA}[t] = A_A V_{OSA}[t] - B_A V_{OA}[t]$$

$$\tag{1}$$

this can also be expressed as

$$V_{OA}[t] = \frac{A_A V_{OSA}[t]}{1 + B_A} \tag{2}$$

This shows that the offset voltage of the nulling amplifier times a gain factor appears at the output of the nulling amplifier and thus on the  $C_{\rm M1}$  capacitor.

Figure 50. Auto-Zero Phase of the Amplifier

#### **AMPLIFICATION PHASE**

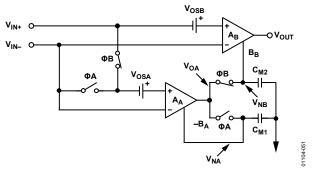

When the  $\phi B$  switches close and the  $\phi A$  switches open for the amplification phase, the offset voltage remains on  $C_{M1}$  and essentially corrects any error from the nulling amplifier. The voltage across  $C_{M1}$  is designated as  $V_{NA}$ . The potential difference between the two inputs to the primary amplifier is designated as  $V_{IN}$ , or  $V_{IN}=(V_{IN+}-V_{IN-}).$  The output of the nulling amplifier can then be expressed as

$$V_{OA}[t] = A_A (V_{IN}[t] - V_{OSA}[t] - B_A V_{NA}[t]$$

(3)

Figure 51. Output Phase of the Amplifier

Because  $\phi A$  is now open and there is no place for  $C_{M1}$  to discharge, the voltage ( $V_{NA}$ ) at the present time (t) is equal to the voltage at the output of the nulling amp ( $V_{OA}$ ) at the time when  $\phi A$  was closed. If the period of the autocorrection switching frequency is designated as  $T_{S}$ , the amplifier switches between phases every  $0.5\times T_{S}$ . Therefore, in the amplification phase

$$V_{NA}[t] = V_{NA}\left[t - \frac{1}{2}T_{S}\right] \tag{4}$$

and substituting Equation 4 and Equation 2 into Equation 3 yields

$$V_{OA}[t] = A_A V_{IN}[t] + A_A V_{OSA}[t] - \frac{A_A B_A V_{OSA}[t - \frac{1}{2} T_S]}{1 + B_A}$$

(5)

For the sake of simplification, it can be assumed that the autocorrection frequency is much faster than any potential change in  $V_{\rm OSA}$  or  $V_{\rm OSB}$ . This is a good assumption because changes in offset voltage are a function of temperature

variation or long-term wear time, both of which are much slower than the auto-zero clock frequency of the AD857x, which effectively makes the  $V_{\rm OS}$  time invariant, and Equation 5 can be rewritten as

$$V_{OA}[t] = A_A V_{IN}[t] + \frac{A_A (1 + B_A) V_{OSA} - A_A B_A V_{OSA}}{1 + B_A}$$

(6)

or

$$V_{OA}[t] = A_A \left( V_{IN}[t] + \frac{V_{OSA}}{1 + B_A} \right)$$

(7)

Here, the auto-zeroing becomes apparent. Note that the  $V_{\rm OS}$  term is reduced by a  $1+B_{\rm A}$  factor, which shows how the nulling amplifier has greatly reduced its own offset voltage error even before correcting the primary amplifier. Therefore, the primary amplifier output voltage is the voltage at the output of the AD857x amplifier. It is equal to

$$V_{OUT}[t] = A_B (V_{IN}[t] + V_{OSB}) + B_B V_{NB}$$

(8)

In the amplification phase,  $V_{OA} = V_{NB}$ , so this can be rewritten as

$$V_{OUT}[t] =$$

$$A_{B}V_{IN}[t] + A_{B}V_{OSB} + B_{B} \left[ A_{A} \left( V_{IN}[t] + \frac{V_{OSA}}{1 + B_{A}} \right) \right]$$

(9)

combining terms yields

$$V_{OUT}[t] = V_{IN}[t](A_B + A_A B_B) + \frac{A_A B_B V_{OSA}}{1 + B_A} + A_B V_{OSB}$$

(10)

The AD857x architecture is optimized in such a way that  $A_A = A_B$ ,  $B_A = B_B$ , and  $B_A >> 1$ . In addition, the gain product to  $A_A B_B$  is much greater than  $A_B$ . Therefore, Equation 10 can be simplified to

$$V_{OUT}[t] = V_{IN}[t]A_AB_A + A_A(V_{OSA} + V_{OSB})$$

(11)

Most obvious is the gain product of both the primary and nulling amplifiers. This  $A_AB_A$  term is what gives the AD857x its extremely high open-loop gain. To understand how  $V_{OSA}$  and  $V_{OSB}$  relate to the overall effective input offset voltage of the complete amplifier, set up the generic amplifier equation of

$$V_{OUT} = k \times (V_{IN} + V_{OS,EFF})$$

(12)

where:

k is the open-loop gain of an amplifier.  $V_{OS, EFF}$  is its effective offset voltage.

Putting Equation 12 into the form of Equation 11 gives

$$V_{OUT}[t] = V_{IN}[t]A_AB_A + V_{OSEFF}A_AB_A \tag{13}$$

Therefore,

$$V_{OS,EFF} \approx \frac{V_{OSA} + V_{OSB}}{B_A} \tag{14}$$

Thus, the offset voltages of both the primary and nulling amplifiers are reduced by the gain factor B<sub>A</sub>, which takes a typical input offset voltage from several millivolts down to an effective input offset voltage of submicrovolts. This autocorrection scheme makes the AD857x family of amplifiers extremely precise.

#### HIGH GAIN, CMRR, AND PSRR

Common-mode and power supply rejection are indications of the amount of offset voltage an amplifier has as a result of a change in its input common-mode or power supply voltages. As shown in the Amplification Phase section, the autocorrection architecture of the AD857x allows it to effectively minimize offset voltages. The technique also corrects for offset errors caused by common-mode voltage swings and power supply variations, which results in superb CMRR and PSRR figures in excess of 130 dB. Because the autocorrection occurs continuously, these figures can be maintained across the entire temperature range of the device, from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

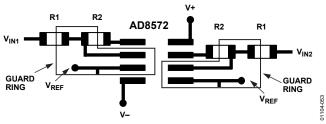

# MAXIMIZING PERFORMANCE THROUGH PROPER LAYOUT

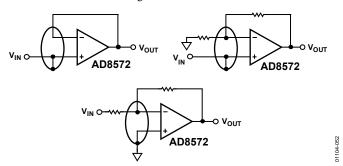

To achieve the maximum performance of the extremely high input impedance and low offset voltage of the AD857x, care should be taken in the circuit board layout. The PCB surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board reduces surface moisture and provides a humidity barrier, reducing parasitic resistance on the board. The use of guard rings around the amplifier inputs further reduces leakage currents. Figure 52 shows how the guard ring should be configured, and Figure 53 shows the top view of how a surface-mount layout can be arranged. The guard ring does not need to be a specific width, but it should form a continuous loop around both inputs. By setting the guard ring voltage equal to the voltage at the noninverting input, parasitic capacitance is minimized as well. For further reduction of leakage currents, components can be mounted to the PCB using Teflon® standoff insulators.

Figure 52. Guard Ring Layout and Connections to Reduce PCB Leakage Currents

Figure 53. Top View of AD8572 SOIC Layout with Guard Rings

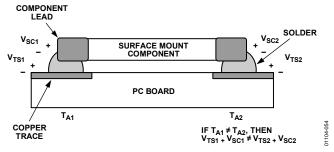

Other potential sources of offset error are thermoelectric voltages on the circuit board. This voltage, also called Seebeck voltage, occurs at the junction of two dissimilar metals and is proportional to the junction temperature. The most common metallic junctions on a circuit board are solder-to-board trace and solder-to-component lead. Figure 54 shows a cross-section view of the thermal voltage error sources. When the temperature of the PCB at one end of the component  $(T_{\rm A1})$  differs from the temperature at the other end  $(T_{\rm A2})$ , the Seebeck voltages are not equal, resulting in a thermal voltage error.

This thermocouple error can be reduced by using dummy components to match the thermoelectric error source. Placing the dummy component as close as possible to its partner ensures both Seebeck voltages are equal, thus canceling the thermocouple error. Maintaining a constant ambient temperature on the circuit board further reduces this error. The use of a ground plane helps distribute heat throughout the board and also reduces EMI noise pickup.

Figure 54. Mismatch in Seebeck Voltages Causes a Thermoelectric Voltage Error

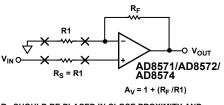

R<sub>S</sub> SHOULD BE PLACED IN CLOSE PROXIMITY AND ALIGNMENT TO R1 TO BALANCE SEEBECK VOLTAGES

Figure 55. Using Dummy Components to Cancel Thermoelectric Voltage Errors

#### 1/f NOISE CHARACTERISTICS

Another advantage of auto-zero amplifiers is their ability to cancel flicker noise. Flicker noise, also known as 1/f noise, is noise inherent in the physics of semiconductor devices and increases 3 dB for every octave decrease in frequency. The 1/f corner frequency of an amplifier is the frequency at which the flicker noise is equal to the broadband noise of the amplifier. At lower frequencies, flicker noise dominates, causing higher degrees of error for sub-Hertz frequencies or dc precision applications.

Because the AD857x amplifiers are self-correcting op amps, they do not have increasing flicker noise at lower frequencies. In essence, low frequency noise is treated as a slowly varying offset error and is greatly reduced as a result of autocorrection. The correction becomes more effective as the noise frequency approaches dc, offsetting the tendency of the noise to increase exponentially as frequency decreases, which allows the AD857x to have lower noise near dc than standard low noise amplifiers that are susceptible to 1/f noise.

# RANDOM AUTO-ZERO CORRECTION ELIMINATES INTERMODULATION DISTORTION

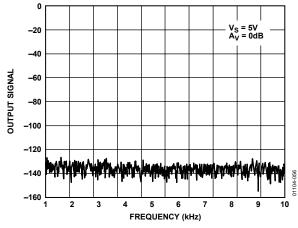

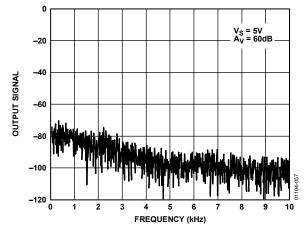

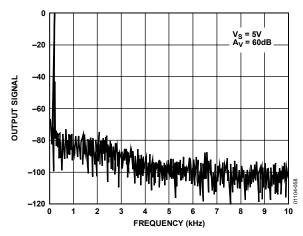

The AD857x can be used as a conventional op amp for gains up to 1 MHz. The auto-zero correction frequency of the device continuously varies, based on a pseudorandom generator with a uniform distribution from 2 kHz to 4 kHz. The randomization of the autocorrection clock creates a continuous randomization of intermodulation distortion (IMD) products that show up as simple broadband noise at the output of the amplifier. This broadband noise naturally combines with the amplifier voltage noise in a root-squared-sum fashion, resulting in an output free IMD. Figure 56 shows the spectral output of an AD8572 with the amplifier configured for unity gain and the input grounded. Figure 57 shows the spectral output with the amplifier configured for a gain of 60 dB.

Figure 56. Spectral Analysis of AD8572 Output in Unity Gain Configuration

Figure 57. Spectral Analysis of AD857x Output with 60 dB Gain

Figure 58 shows the spectral output of an AD8572 configured in a high gain (60 dB) with a 1 mV input signal applied. Note the absence of any IMD products in the spectrum. The signal-to-noise ratio (SNR) of the output signal is better than 60 dB, or 0.1%.

Figure 58. Spectral Analysis of AD8572 in High Gain with an Input Signal

## BROADBAND AND EXTERNAL RESISTOR NOISE CONSIDERATIONS

The total broadband noise output from any amplifier is primarily a function of three types of noise: input voltage noise from the amplifier, input current noise from the amplifier, and Johnson noise from the external resistors used around the amplifier. Input voltage noise, or  $e_n$ , is strictly a function of the amplifier used. The Johnson noise from a resistor is a function of the resistance and the temperature. Input current noise, or  $i_n$ , creates an equivalent voltage noise proportional to the resistors used around the amplifier. These noise sources are not correlated with each other and their combined noise sums in a rootsquared-sum fashion. The full equation is given as

$$e_{n,TOTAL} = [e_n^2 + 4kTr_s + (i_n r_s)^2]^{1/2}$$

(15)

where:

$e_n$  is the input voltage noise of the amplifier.

$i_n$  is the input current noise of the amplifier.

$r_s$  is the source resistance connected to the noninverting terminal.

*k* is Boltzmann's constant (1.38 ×  $10^{-23}$  J/K).

*T* is the ambient temperature in Kelvin ( $K = 273.15 + {}^{\circ}C$ ).

The input voltage noise density,  $e_n$ , of the AD857x is 51 nV/ $\sqrt{Hz}$ , and the input noise,  $i_n$ , is 2 fA/ $\sqrt{Hz}$ . The  $e_{n, TOTAL}$  is dominated by the input voltage noise provided that the source resistance is less than 172 k $\Omega$ . With source resistance greater than 172 k $\Omega$ , the overall noise of the system is dominated by the Johnson noise of the resistor itself.

Because the input current noise of the AD857x is very small,  $i_n$  does not become a dominant term unless  $r_s > 4$  G $\Omega$ , which is an impractical value of source resistance.

The total noise,  $e_n$ ,  $_{TOTAL}$ , is expressed in volts-per-square-root Hertz, and the equivalent rms noise over a certain bandwidth can be found as

$$e_n = e_{n, TOTAL} \times \sqrt{BW} \tag{16}$$

where BW is the bandwidth of interest in Hertz.

#### **OUTPUT OVERDRIVE RECOVERY**

The AD857x amplifiers have an excellent overdrive recovery of only 200  $\mu$ s from either supply rail. This characteristic is particularly difficult for autocorrection amplifiers because the nulling amplifier requires a substantial amount of time to error correct the main amplifier back to a valid output. Figure 29 and Figure 30 show the positive and negative overdrive recovery times for the AD857x.

The output overdrive recovery for an autocorrection amplifier is defined as the time it takes for the output to correct to its final voltage from an overload state. It is measured by placing the amplifier in a high gain configuration with an input signal that forces the output voltage to the supply rail. The input voltage is then stepped down to the linear region of the amplifier, usually to halfway between the supplies. The time from the input signal step-down to the output settling to within  $100~\mu V$  of its final value is the overdrive recovery time. Many autocorrection amplifiers require a number of auto-zero clock cycles to recover from output overdrive, and some can take several milliseconds for the output to settle properly.

#### INPUT OVERVOLTAGE PROTECTION

Although the AD857x are rail-to-rail input amplifiers, care should be taken to ensure that the potential difference between the inputs does not exceed 5 V. Under normal operating conditions, the amplifier corrects its output to ensure the two inputs are at the same voltage. However, if the device is configured as a comparator, or is under some unusual operating condition, the input voltages may be forced to different potentials, which could cause excessive current to flow through the internal diodes in the AD857x used to protect the input stage against overvoltage.

If either input exceeds either supply rail by more than 0.3 V, large amounts of current begin to flow through the ESD protection diodes in the amplifier. These diodes are connected between the inputs and each supply rail to protect the input transistors against an electrostatic discharge event and are normally reverse-biased. However, if the input voltage exceeds the supply voltage, these ESD diodes become forward-biased. Without current-limiting, excessive amounts of current can flow through these diodes, causing permanent damage to the device. If inputs are subject to overvoltage, appropriate series resistors should be inserted to limit the diode current to less than 2 mA.

#### **OUTPUT PHASE REVERSAL**

Output phase reversal occurs in some amplifiers when the input common-mode voltage range is exceeded. As common-mode voltage moves outside the common-mode range, the outputs of these amplifiers suddenly jump in the opposite direction to the supply rail. This is the result of the differential input pair shutting down, causing a radical shifting of internal voltages that results in the erratic output behavior.

The AD857x amplifier has been carefully designed to prevent any output phase reversal, provided both inputs are maintained within the supply voltages. If one or both inputs exceed either supply voltage, a resistor should be placed in series with the input to limit the current to less than 2 mA to ensure the output does not reverse its phase.

#### **CAPACITIVE LOAD DRIVE**

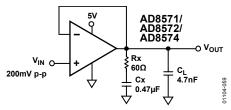

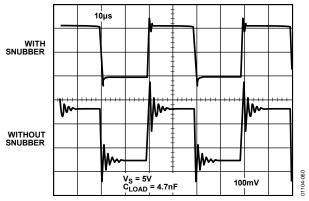

The AD857x have excellent capacitive load driving capabilities and can safely drive up to 10 nF from a single 5 V supply. Although the device is stable, capacitive loading limits the bandwidth of the amplifier. Capacitive loads also increase the amount of overshoot and ringing at the output. An RC snubber network, shown in Figure 59, can be used to compensate the amplifier against capacitive load ringing and overshoot.

Figure 59. Snubber Network Configuration for Driving Capacitive Loads

Although the snubber does not recover the loss of amplifier bandwidth from the load capacitance, it does allow the amplifier to drive larger values of capacitance while maintaining a minimum of overshoot and ringing. Figure 60 shows the output of an AD857x driving a 1 nF capacitor with and without a snubber network.

Figure 60. Overshoot and Ringing Are Substantially Reduced Using a Snubber Network

The optimum value for the resistor and capacitor is a function of the load capacitance and is best determined empirically since actual C<sub>LOAD</sub> includes stray capacitances and can differ substantially from the nominal capacitive load. Table 5 shows some snubber network values that can be used as starting points.

Table 5. Snubber Network Values for Driving Capacitive Loads

| C <sub>LOAD</sub> (nF) | Rx (Ω) | Сх      |

|------------------------|--------|---------|

| 1                      | 200    | 1 nF    |

| 4.7                    | 60     | 0.47 μF |

| 10                     | 20     | 10 μF   |

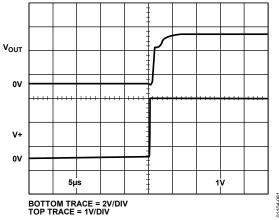

#### **POWER-UP BEHAVIOR**

On power-up, the AD857x settle to a valid output within 5  $\mu s$ . Figure 61 shows an oscilloscope photo of the output of the amplifier along with the power supply voltage. Figure 62 shows the test circuit. With the amplifier configured for unity gain, the device takes approximately 5  $\mu s$  to settle to its final output voltage, hundreds of microseconds faster than many other autocorrection amplifiers.

Figure 61. AD857x Output Behavior on Power-Up

Figure 62. AD857x Test Circuit for Turn-On Time

### **APPLICATIONS**

#### **5 V PRECISION STRAIN GAGE CIRCUIT**

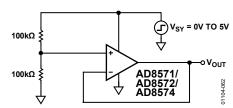

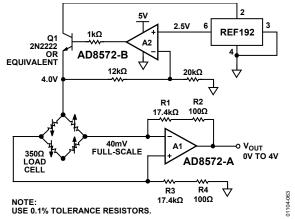

The extremely low offset voltage of the AD8572 makes it an ideal amplifier for any application requiring accuracy with high gains, such as a weigh scale or strain gage. Figure 63 shows a configuration for a single-supply, precision strain gage measurement system.

The REF192 provides a 2.5 V precision reference voltage for A2. The A2 amplifier boosts this voltage to provide a 4.0 V reference for the top of the strain gage resistor bridge. Q1 provides the current drive for the 350  $\Omega$  bridge network. A1 is used to amplify the output of the bridge with the full-scale output voltage equal to

$$\frac{2 \times (RI + R2)}{R_R} \tag{17}$$

where  $R_B$  is the resistance of the load cell.

Using the values given in Figure 63, the output voltage linearly varies from 0 V with no strain to 4 V under full strain.

Figure 63. 5 V Precision Strain Gage Amplifier

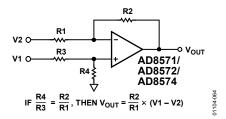

#### **3 V INSTRUMENTATION AMPLIFIER**

The high common-mode rejection, high open-loop gain, and operation down to 3 V of supply voltage make the AD857x family an excellent choice of op amp for discrete single-supply instrumentation amplifiers. The common-mode rejection ratio of the AD857x is greater than 120 dB, but the CMRR of the system is also a function of the external resistor tolerances. The gain of the difference amplifier shown in Figure 64 is given as

$$V_{OUT} = VI \left( \frac{R4}{R3 + R4} \right) \left( 1 + \frac{R1}{R2} \right) - V2 \left( \frac{R2}{R1} \right)$$

(18)

Figure 64. Using the AD857x as a Difference Amplifier

In an ideal difference amplifier, the ratio of the resistors is set equal to

$$A_V = \frac{R2}{R1} = \frac{R4}{R3} \tag{19}$$

Set the output voltage of the system to

$$V_{OUT} = A_V \left( V1 - V2 \right) \tag{20}$$

Due to finite component tolerance, the ratio between the four resistors is not exactly equal, and any mismatch results in a reduction of common-mode rejection from the system. Referring to Figure 64, the exact common-mode rejection ratio can be expressed as

$$CMRR = \frac{R1R4 + 2R2R4 + R2R3}{2R1R4 - 2R2R3} \tag{21}$$

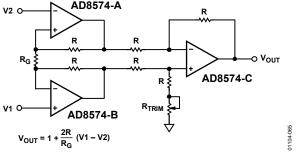

In the 3-op amp instrumentation amplifier configuration shown in Figure 65, the output difference amplifier is set to unity gain with all four resistors equal in value. If the tolerance of the resistors used in the circuit is given as  $\delta$ , the worst-case CMRR of the instrumentation amplifier is

$$CMRR_{MIN} = \frac{1}{28}$$

(22)

Figure 65. Discrete Instrumentation Amplifier Configuration

Therefore, using 1% tolerance resistors results in a worst-case system CMRR of 0.02, or 34 dB. To achieve high common-mode rejection, either high precision resistors or an additional trimming resistor, as shown in Figure 65, should be used. The value of this trimming resistor should be equal to the value of R multiplied by its tolerance. For example, using 10 k $\Omega$  resistors with 1% tolerance would require a series trimming resistor equal to 100  $\Omega$ .

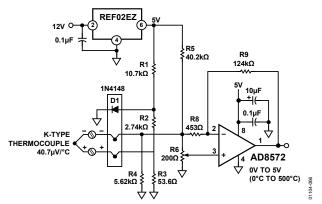

#### HIGH ACCURACY THERMOCOUPLE AMPLIFIER

Figure 66 shows a K-type thermocouple amplifier configuration with cold-junction compensation. Even from a 5 V supply, the AD8571 can provide enough accuracy to achieve a resolution of better than 0.02°C from 0°C to 500°C. D1 is used as a temperature measuring device to correct the cold-junction error from the thermocouple and should be placed as close as possible to the two terminating junctions. With the thermocouple measuring tip immersed in a 0°C ice bath, R6 should be adjusted until the output is at 0 V.

Using the values shown in Figure 66, the output voltage tracks temperature at 10 mV/°C. For a wider range of temperature measurement, R9 can be decreased to 62 k $\Omega$ . This creates a 5 mV/°C change at the output, allowing measurements of up to 1000°C.

Figure 66. Precision K-Type Thermocouple Amplifier with Cold-Junction Compensation

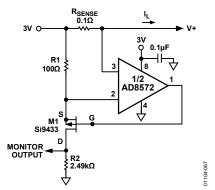

#### **PRECISION CURRENT METER**

Because of its low input bias current and superb offset voltage at single-supply voltages, the AD857x family is an excellent amplifier for precision current monitoring. Its rail-to-rail input allows the amplifier to be used as either a high-side or a low-side current monitor. Using both amplifiers in the AD8572 provides a simple method to monitor both current supply and return paths for load or fault detection.

Figure 67 shows a high-side current monitor configuration. Here, the input common-mode voltage of the amplifier is at or near the positive supply voltage. The rail-to-rail input of the amplifier provides a precise measurement, even with the input common-mode voltage at the supply voltage. The CMOS input structure does not draw any input bias current, ensuring a minimum of measurement error.

The 0.1  $\Omega$  resistor creates a voltage drop to the noninverting input of the AD857x. The output of the amplifier is corrected until this voltage appears at the inverting input, which creates a current through R1 that in turn flows through R2. The monitor output is given by

Monitor Output =

$$R2 \times (R_{SENSE}/R1) \times I_L$$

(23)

Using the components shown in Figure 67, the monitor output transfer function is 2.5 V/A.

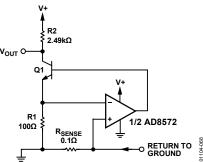

Figure 68 shows the low-side monitor equivalent. In this circuit, the input common-mode voltage to the AD8572 is at or near ground. Again, a 0.1  $\Omega$  resistor provides a voltage drop proportional to the return current. The output voltage is given as

$$V_{OUT} = V_{+} - \left(\frac{R2}{R1} \times R_{SENSE} \times I_{L}\right)$$

(24)

For the component values shown in Figure 68, the output transfer function decreases from V at -2.5 V/A.

Figure 67. High-Side Load Current Monitor

Figure 68. Low-Side Load Current Monitor

#### PRECISION VOLTAGE COMPARATOR

The AD857x can be operated open-loop and used as a precision comparator. The AD857x have less than 50  $\mu V$  of offset voltage when run in this configuration. The slight increase of offset voltage stems from the fact that the autocorrection architecture operates with the lowest offset in a closed-loop configuration, that is, one with negative feedback. With 50 mV of overdrive, the device has a propagation delay of 15  $\mu s$  on the rising edge and 8  $\mu s$  on the falling edge.

Care should be taken to ensure the maximum differential voltage of the device is not exceeded. For more information, see the Input Overvoltage Protection section.

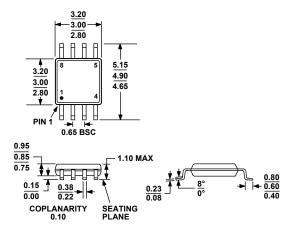

# **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 69. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-012-A A CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

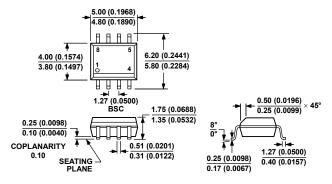

Figure 70. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8) Dimensions shown in millimeters and inches

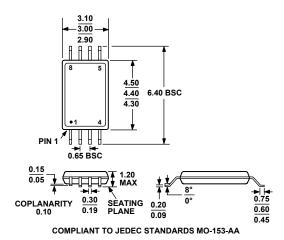

Figure 71. 8-Lead Thin Shrink Small Outline Package [TSSOP] (RU-8) Dimensions shown in millimeters

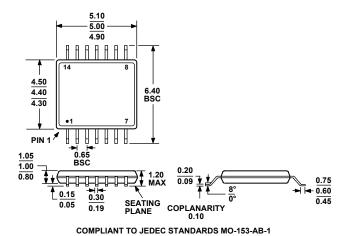

Figure 72. 14-Lead Thin Shrink Small Outline Package [TSSOP] (RU-14)

Dimensions shown in millimeters

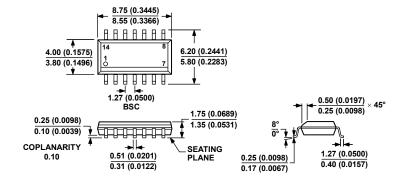

COMPLIANT TO JEDEC STANDARDS MS-012-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 73. 14-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-14) Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description | Package Option | Branding |

|------------------------------|-------------------|---------------------|----------------|----------|

| AD8571AR                     | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571AR-REEL                | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571AR-REEL7               | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARZ <sup>1</sup>       | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARZ-REEL7 <sup>1</sup> | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARM-R2                 | −40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA      |

| AD8571ARM-REEL               | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA      |

| AD8571ARMZ-R2 <sup>1</sup>   | −40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA#     |

| AD8571ARMZ-REEL <sup>1</sup> | −40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA#     |

| AD8572AR                     | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572AR-REEL                | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572AR-REEL7               | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARZ <sup>1</sup>       | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARZ-REEL <sup>1</sup>  | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARU                    | −40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8572ARU-REEL               | -40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8572ARUZ <sup>1</sup>      | -40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8572ARUZ-REEL <sup>1</sup> | -40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8574AR                     | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574AR-REEL                | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574AR-REEL7               | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARZ <sup>1</sup>       | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARZ-REEL <sup>1</sup>  | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARZ-REEL7 <sup>1</sup> | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARU                    | −40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8574ARU-REEL               | −40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8574ARUZ <sup>1</sup>      | −40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8574ARUZ-REEL <sup>1</sup> | −40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

$<sup>^1</sup>$  Z = RoHS Compliant Part, # denote RoHS compliant product may be top or bottom marked.

AD8571/AD8572/AD8574 查询"AD8571ARMZ-R2"供应商

**NOTES**