# Quad IMUX Ethernet Mapper

#### www.maxim-ic.com

## **GENERAL DESCRIPTION**

DALLAS SEMICONDUCTOR

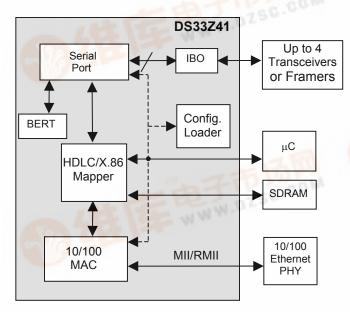

The DS33Z41 extends a 10/100 Ethernet LAN segment by encapsulating MAC frames in HDLC or X.86 (LAPS) for transmission over up to four interleaved PDH/TDM data streams using robust, balanced, and programmable inverse multiplexing. The Interleave Bus (IBO) serial link supports seamless bidirectional interconnection with Dallas Semiconductor's T1/E1 framers and transceivers.

The device performs store-and-forward of packets with full wire-speed transport capability. The built-in Committed Information Rate (CIR) Controller provides fractional bandwidth allocation up to the line rate in increments of 512kbps.

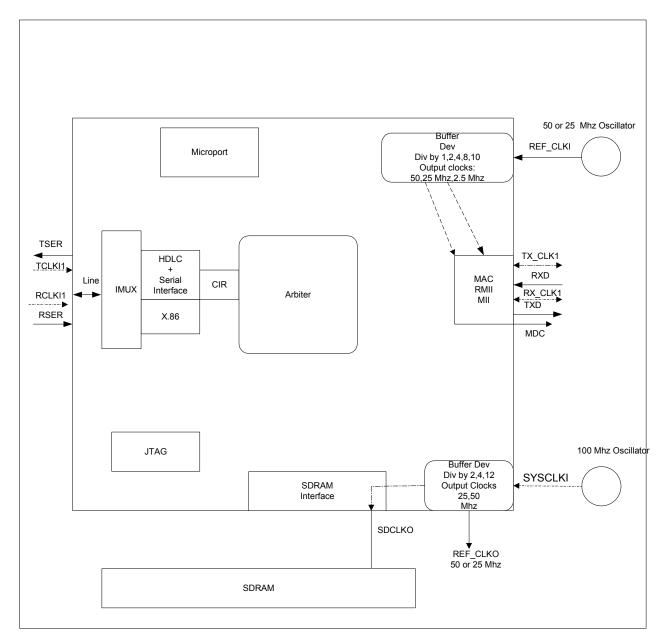

## FUNCTIONAL DIAGRAM

#### **FEATURES**

SC.COM

- 10/100 IEEE 802.3 Ethernet MAC (MII and RMII) Half/Full Duplex with Automatic Flow Control

- Layer 1 Inverse Multiplexing Allows Bonding of Up to 4 T1/E1/J1 or DSL Links

- Supports Up to 7.75ms Differential Delay

- Channel (Byte) Interleaved Bus Operation

- In-Band OAM and Signaling Capability

- HDLC/LAPS Encapsulation with Programmable FCS, Interframe Fill

- Committed Information Rate Controller Provides

Fractional Allocation in 512kbps Increments

- Programmable BERT for the Serial Interface

- External 16MB, 100MHz SDRAM Buffering

- Parallel Microprocessor Interface

- 1.8V Operation with 3.3V Tolerant I/O

- IEEE 1149.1 JTAG Support

Features continued on page <u>8</u>.

## **APPLICATIONS**

Bonded Transparent LAN Service LAN Extension Ethernet Delivery Over T1/E1/J1, T3/E3, OC-1/EC-1, G.SHDSL, or HDSL2/4

## **ORDERING INFORMATION**

| PART    | TEMP RANGE     | PIN-PACKAGE |

|---------|----------------|-------------|

| DS33Z41 | -40°C to +85°C | 169 CSBGA   |

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

## **TABLE OF CONTENTS**

| 1 | DESCRIPTION                                                                 | 7  |

|---|-----------------------------------------------------------------------------|----|

| 2 | FEATURE HIGHLIGHTS                                                          | 8  |

|   | 2.1 General                                                                 | 8  |

|   | 2.2 LINK AGGREGATION (INVERSE MULTIPLEXING)                                 | 8  |

|   | 2.3 HDLC                                                                    |    |

|   | 2.4 COMMITTED INFORMATION RATE (CIR) CONTROLLER                             |    |

|   | 2.5 X.86 SUPPORT                                                            |    |

|   | 2.6 SDRAM INTERFACE                                                         |    |

|   | <ul> <li>2.7 MAC INTERFACE</li></ul>                                        |    |

|   | <ul> <li>MICROPROCESSOR INTERFACE</li></ul>                                 |    |

|   | 2.9 TEST AND DIAGNOSTICS                                                    |    |

| 2 | APPLICATIONS                                                                |    |

| 3 |                                                                             |    |

| 4 | ACRONYMS AND GLOSSARY                                                       | 12 |

| 5 | MAJOR OPERATING MODES                                                       | 13 |

| 6 | BLOCK DIAGRAMS                                                              | 12 |

|   |                                                                             |    |

| 7 | PIN DESCRIPTIONS                                                            |    |

|   | 7.1 PIN FUNCTIONAL DESCRIPTION                                              |    |

| 8 | FUNCTIONAL DESCRIPTION                                                      | 22 |

|   | 3.1 PROCESSOR INTERFACE                                                     |    |

|   | 8.1.1 Read-Write/Data Strobe Modes                                          |    |

|   | <ul><li>8.1.2 Clear on Read</li><li>8.1.3 Interrupt and Pin Modes</li></ul> |    |

|   | 3.2 CLOCK STRUCTURE                                                         |    |

|   | 8.2.1 Serial Interface Clock Modes                                          |    |

|   | 8.2.2 Ethernet Interface Clock Modes                                        |    |

|   | 3.3 RESETS AND LOW-POWER MODES                                              |    |

|   | 3.4 INITIALIZATION AND CONFIGURATION                                        |    |

|   | 3.5 GLOBAL RESOURCES                                                        |    |

|   | <ul> <li>B.6 PER-PORT RESOURCES.</li> <li>B.7 DEVICE INTERRUPTS.</li> </ul> |    |

|   | <ul> <li>B.7 DEVICE INTERRUPTS</li> <li>B.8 SERIAL INTERFACE</li> </ul>     |    |

|   | 3.9 LINK AGGREGATION (IMUX)                                                 |    |

|   | 8.9.1 Microprocessor Requirements                                           |    |

|   | 8.9.2 IMUX Command Protocol                                                 |    |

|   | 8.9.3 Out of Frame (OOF) Monitoring                                         |    |

|   | 8.9.4 Data Transfer                                                         |    |

|   | 3.10 CONNECTIONS AND QUEUES                                                 |    |

|   | 3.11 ARBITER                                                                |    |

|   | 8.12 FLOW CONTROL<br>8.12.1 Full-Duplex Flow Control                        |    |

|   | 8.12.7 Full-Duplex Flow Control                                             |    |

|   | 8.12.3 Host-Managed Flow control                                            |    |

|   | 3.13 ETHERNET INTERFACE PORT                                                | 42 |

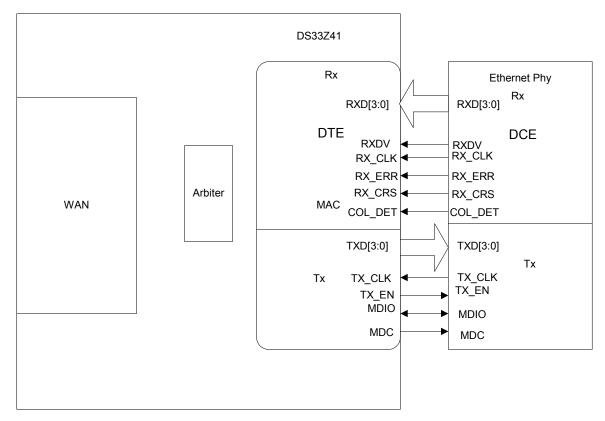

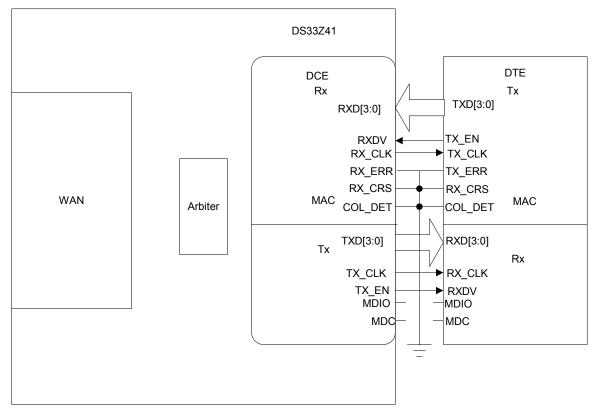

|   | 8.13.1 DTE and DCE Mode                                                     | 43 |

| Ĩ  | ううう<br>ううしてもの<br>ううしてもの<br>していていていていていていていていていていていていていていていていていていてい | azaniut mað                                         | .46 |

|----|--------------------------------------------------------------------|-----------------------------------------------------|-----|

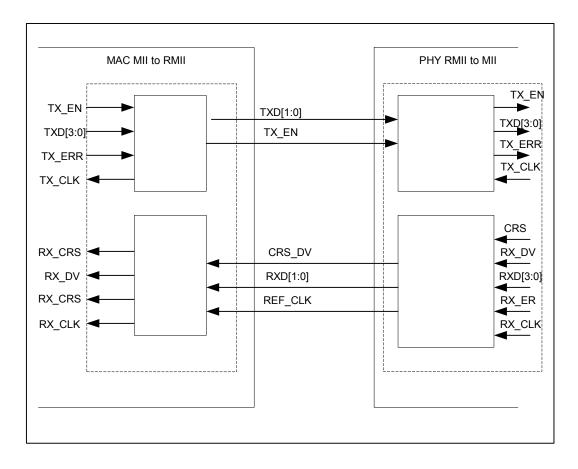

|    |                                                                    | MII Mode                                            |     |

|    |                                                                    | RMII Mode                                           |     |

|    |                                                                    | PHY MII Management Block and MDIO Interface         |     |

|    |                                                                    | RT                                                  |     |

|    |                                                                    | BERT Features                                       |     |

|    |                                                                    | Receive Data Interface                              |     |

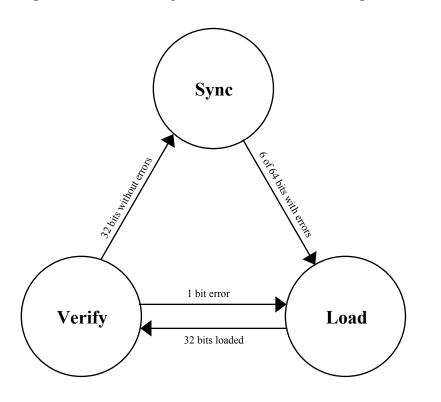

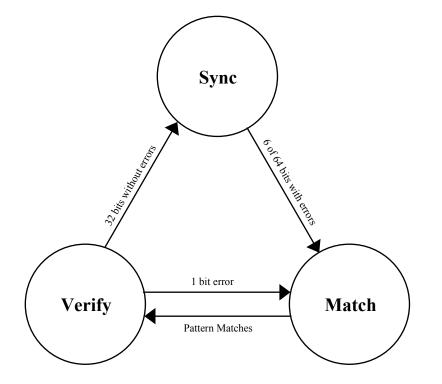

|    |                                                                    | Repetitive Pattern Synchronization                  |     |

|    |                                                                    | Pattern Monitoring                                  |     |

|    |                                                                    | Pattern Generation                                  |     |

|    |                                                                    | ANSMIT PACKET PROCESSOR                             |     |

|    |                                                                    | CEIVE PACKET PROCESSOR                              |     |

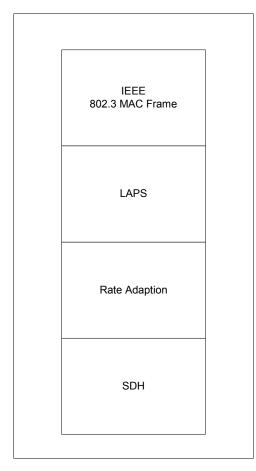

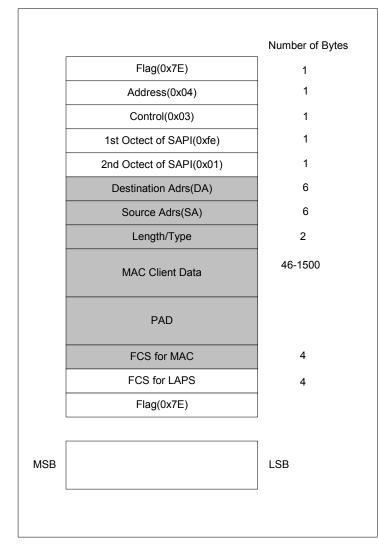

|    | 8.18 X.8                                                           | 6 ENCODING AND DECODING                             | .55 |

|    | 8.19 Co                                                            | MMITTED INFORMATION RATE CONTROLLER                 | .58 |

| 9  | DEVIC                                                              | CE REGISTERS                                        | .60 |

|    | 9.1 REG                                                            | GISTER BIT MAPS                                     | .61 |

|    | 9.1.1                                                              | Global Register Bit Map                             |     |

|    | 9.1.2                                                              | Arbiter Register Bit Map                            |     |

|    | 9.1.3                                                              | BERT Register Bit Map                               |     |

|    | 9.1.4                                                              | Serial Interface Register Bit Map                   | 63  |

|    | 9.1.5                                                              | Ethernet Interface Register Bit Map                 | 65  |

|    | 9.1.6                                                              | MAC Register Bit Map                                | 66  |

|    | 9.2 GL                                                             | OBAL REGISTER DEFINITIONS                           | .68 |

|    | 9.3 ARE                                                            | BITER REGISTERS                                     | .81 |

|    | 9.3.1                                                              | Arbiter Register Bit Descriptions                   | 81  |

|    | 9.4 BE                                                             | RT REGISTERS                                        | .82 |

|    | 9.5 SEF                                                            | RIAL INTERFACE REGISTERS                            | .89 |

|    | 9.5.1                                                              | Serial Interface Transmit and Common Registers      |     |

|    | 9.5.2                                                              | Serial Interface Transmit Register Bit Descriptions |     |

|    | 9.5.3                                                              | Transmit HDLC Processor Registers                   |     |

|    | 9.5.4                                                              | X.86 Registers                                      |     |

|    | 9.5.5                                                              | Receive Serial Interface                            | 99  |

|    | 9.6 ETH                                                            | HERNET INTERFACE REGISTERS                          | 112 |

|    | 9.6.1                                                              | Ethernet Interface Register Bit Descriptions        | 112 |

|    | 9.6.2                                                              | MAC Registers                                       |     |

| 1( |                                                                    |                                                     | 140 |

|    |                                                                    | AND RMII INTERFACES                                 |     |

|    |                                                                    |                                                     |     |

| 11 |                                                                    | ATING PARAMETERS                                    |     |

|    | 11.1 THE                                                           | ERMAL CHARACTERISTICS                               | 143 |

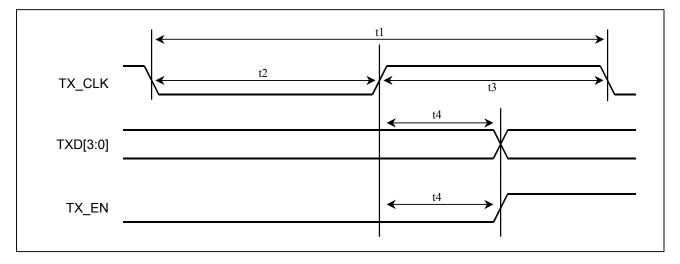

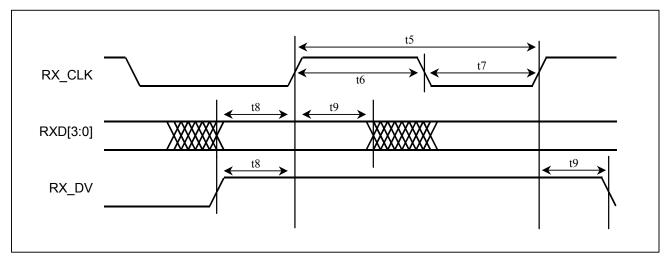

|    | 11.2 MI                                                            | INTERFACE                                           | 144 |

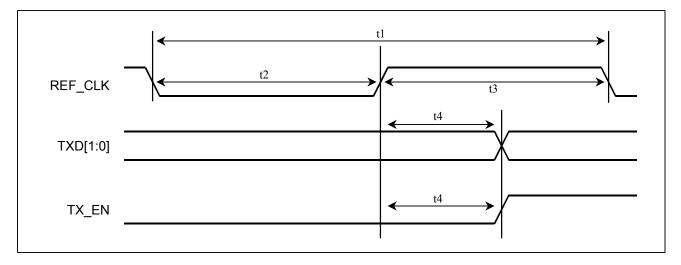

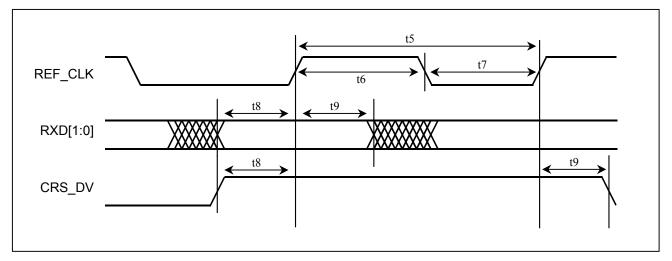

|    | 11.3 RM                                                            | III INTERFACE                                       | 146 |

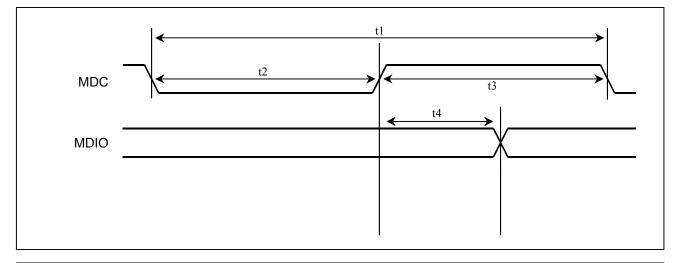

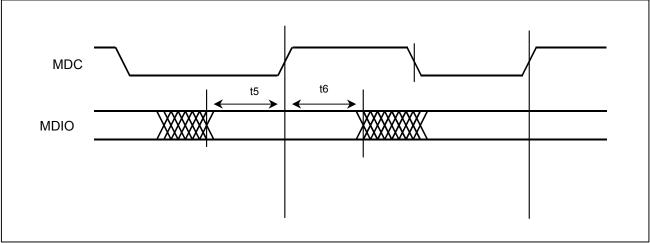

|    | 11.4 MD                                                            | NO INTERFACE                                        | 148 |

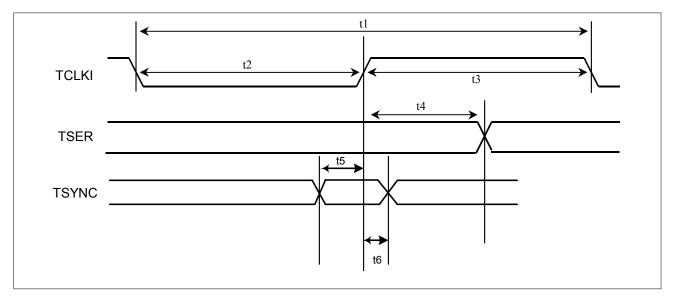

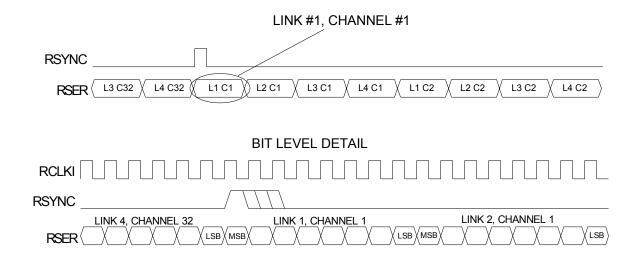

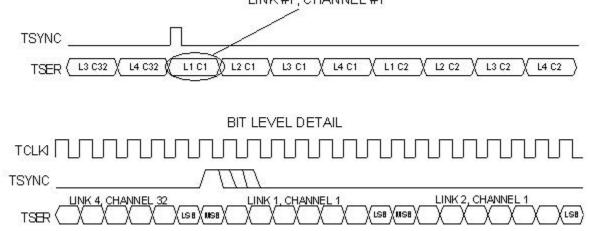

|    |                                                                    | ANSMIT WAN INTERFACE                                |     |

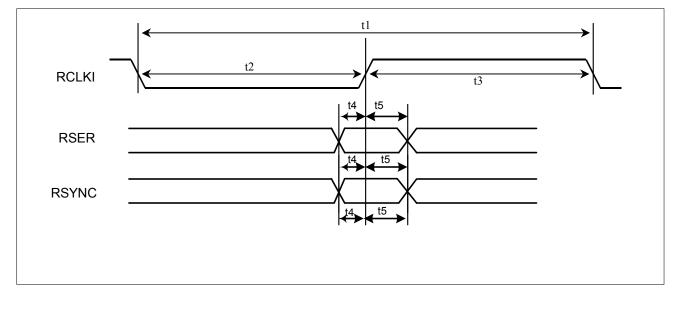

|    |                                                                    | CEIVE WAN INTERFACE                                 |     |

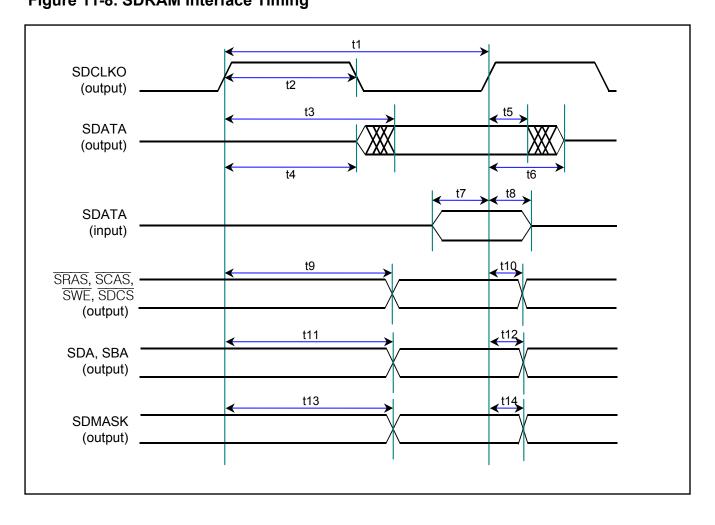

|    | -                                                                  | RAM TIMING                                          |     |

|    |                                                                    | CROPROCESSOR BUS AC CHARACTERISTICS                 |     |

|    |                                                                    | AG INTERFACE TIMING                                 |     |

|    |                                                                    |                                                     |     |

| 12 |                                                                    | INFORMATION                                         |     |

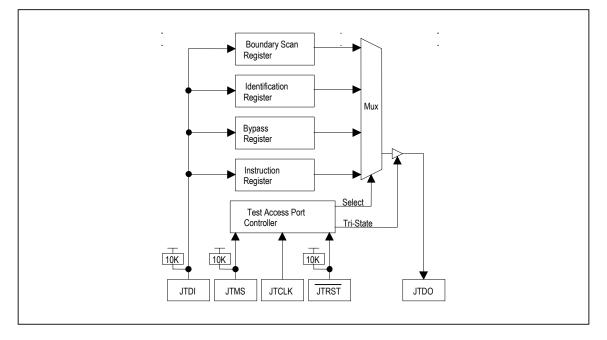

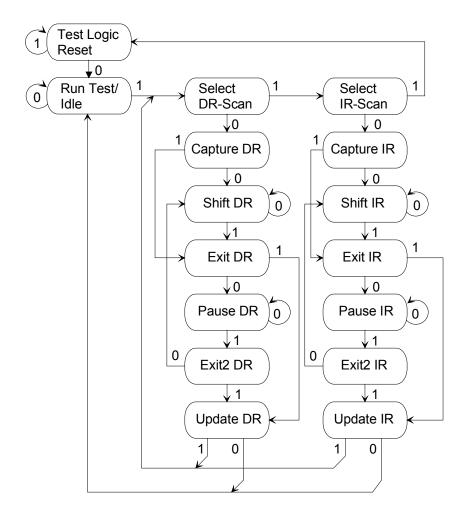

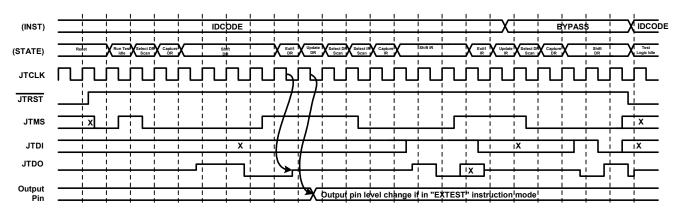

|    | 12.1 JTA                                                           | AG TAP CONTROLLER STATE MACHINE DESCRIPTION         | 160 |

|    |                                                                    | TRUCTION REGISTER                                   |     |

|    |                                                                    | SAMPLE:PRELOAD                                      |     |

|    |                                                                    |                                                     | -   |

| 查询205237442/2520商                               |     |

|-------------------------------------------------|-----|

| 12.2.3 EXTEST                                   |     |

| 12.2.4 CLAMP                                    |     |

| 12.2.5 HIGHZ                                    |     |

| 12.2.6 IDCODE                                   |     |

| 12.3 JTAG ID CODES                              |     |

| 12.4 TEST REGISTERS                             |     |

| 12.4.1 Boundary Scan Register                   |     |

| 12.4.2 Bypass Register                          |     |

| 12.4.3 Identification Register                  |     |

| 12.5 JTAG FUNCTIONAL TIMING                     |     |

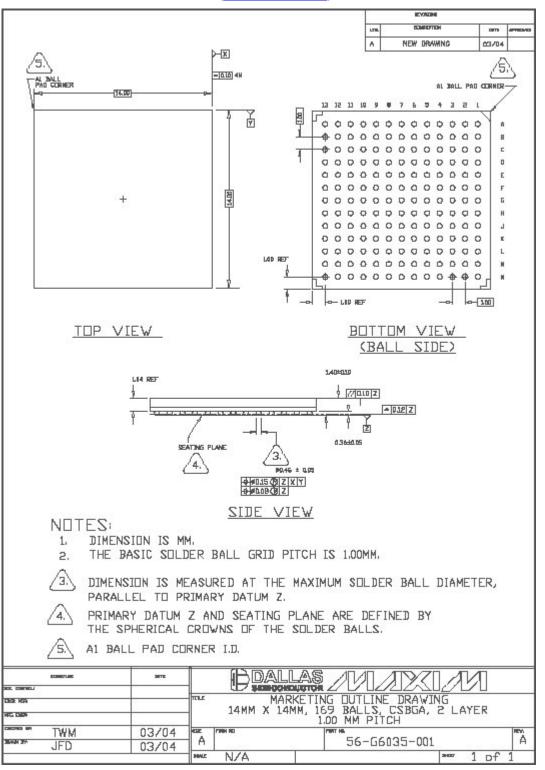

| 13 PACKAGE INFORMATION                          |     |

| 13.1 169-BALL CSBGA, 14мм х 14мм (56-G6035-001) |     |

| 14 DOCUMENT REVISION HISTORY                    | 167 |

## LIST OF FIGURES

| Figure 3-1. Quad T1/E1 SCT to DS33Z41                                    |      |

|--------------------------------------------------------------------------|------|

| Figure 6-1. Detailed Block Diagram                                       | . 13 |

| Figure 7-1. DS33Z41 256-Ball CSBGA Pinout                                | . 21 |

| Figure 8-1. Clocking for the DS33Z41                                     | . 25 |

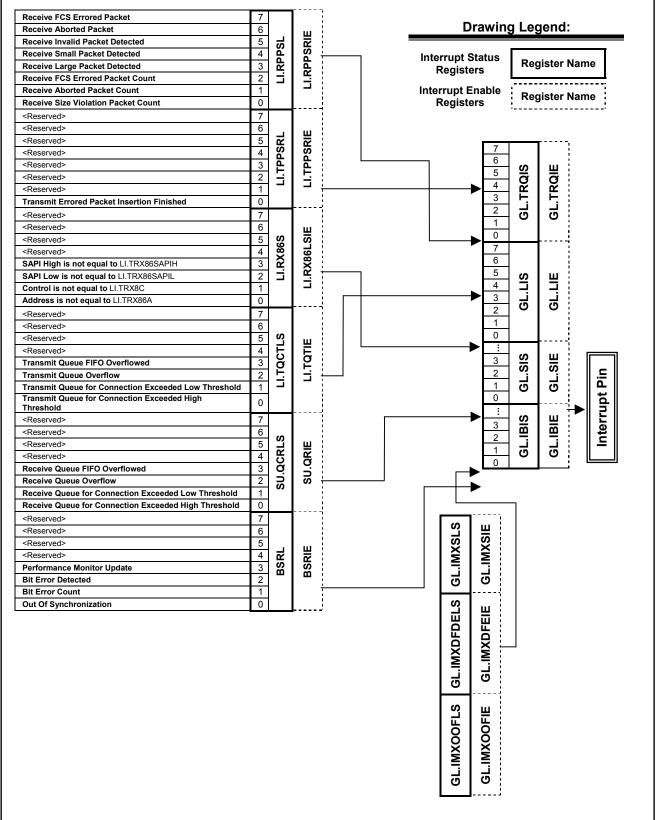

| Figure 8-2. Device Interrupt Information Flow Diagram                    | . 30 |

| Figure 8-3. IMUX Interface to T1/E1 Transceivers                         | . 32 |

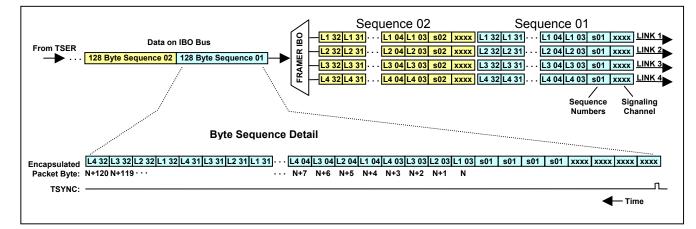

| Figure 8-4. Diagram of Data Transmission with IMUX Operation             |      |

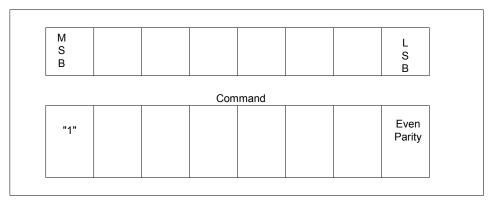

| Figure 8-5. Command Structure for IMUX Function                          |      |

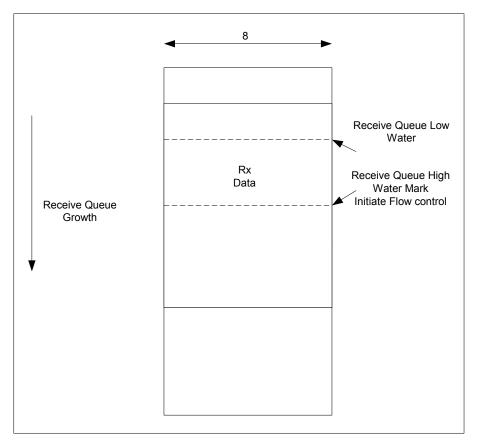

| Figure 8-6. Flow Control Using Pause Control Frame                       |      |

| Figure 8-7. IEEE 802.3 Ethernet Frame                                    | . 42 |

| Figure 8-8. Configured as DTE Connected to an Ethernet PHY in MII Mode   | . 44 |

| Figure 8-9. DS33Z41 Configured as a DCE in MII Mode                      | . 45 |

| Figure 8-10. RMII Interface                                              | . 47 |

| Figure 8-11. MII Management Frame                                        | . 48 |

| Figure 8-12. PRBS Synchronization State Diagram                          |      |

| Figure 8-13. Repetitive Pattern Synchronization State Diagram            |      |

| Figure 8-14. LAPS Encoding of MAC Frames Concept                         |      |

| Figure 8-15. X.86 Encapsulation of the MAC field                         |      |

| Figure 8-16. CIR in the WAN Transmit Path                                |      |

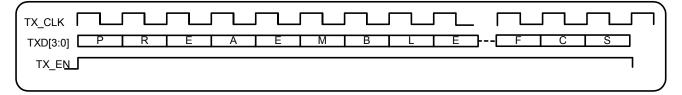

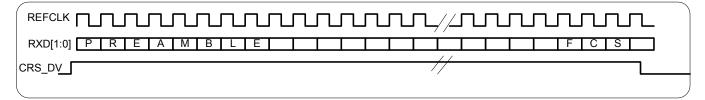

| Figure 10-1. MII Transmit Functional Timing                              | 140  |

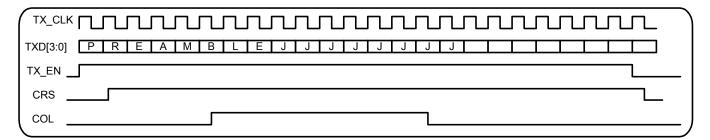

| Figure 10-2. MII Transmit Half Duplex with a Collision Functional Timing |      |

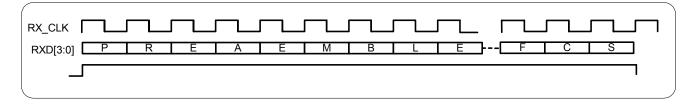

| Figure 10-3. MII Receive Functional Timing                               |      |

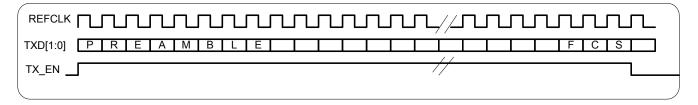

| Figure 10-4. RMII Transmit Interface Functional Timing                   |      |

| Figure 10-5 RMII Receive Interface Functional Timing                     |      |

| Figure 11-1. Transmit MII Interface                                      |      |

| Figure 11-2. Receive MII Interface Timing                                | 145  |

| Figure 11-3. Transmit RMII Interface                                     |      |

| Figure 11-4. Receive RMII Interface Timing                               | 147  |

| Figure 11-5. MDIO Timing                                                 |      |

| Figure 11-6. Transmit WAN Timing                                         |      |

| Figure 11-7. Receive WAN Timing                                          |      |

| Figure 11-8. SDRAM Interface Timing                                      | 152  |

| Figure 11-9. Receive IBO Channel Interleave Mode Timing                  |      |

| Figure 11-10. Transmit IBO Channel Interleave Mode Timing                | 154  |

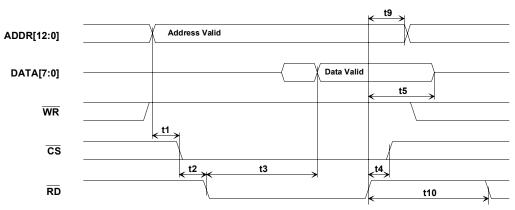

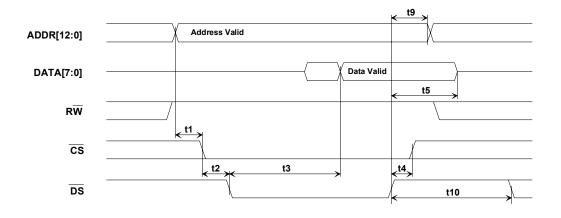

| Figure 11-11. Intel Bus Read Timing (MODEC = 00)                         | 156  |

| Figure 11-12. Intel Bus Write Timing (MODEC = 00)                        | 156  |

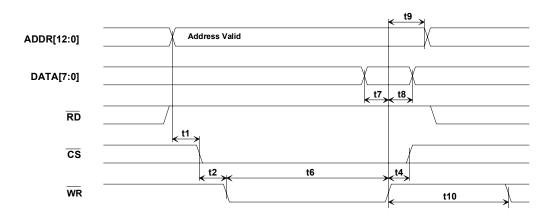

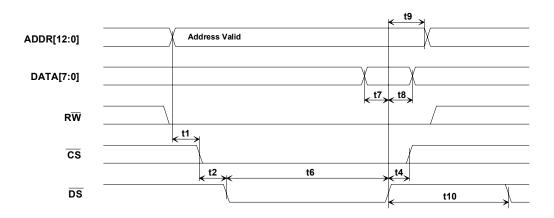

| Figure 11-13. Motorola Bus Read Timing (MODEC = 01)                      | 157  |

| Figure 11-14. Motorola Bus Write Timing (MODEC = 01)                     | 157  |

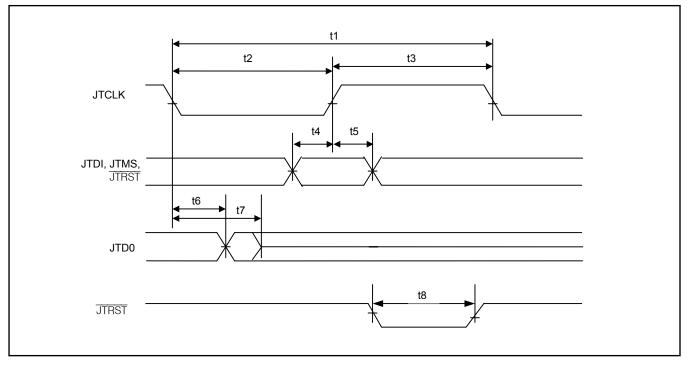

| Figure 11-15. JTAG Interface Timing Diagram                              |      |

| Figure 12-1. JTAG Functional Block Diagram                               |      |

| Figure 12-2. TAP Controller State Diagram                                |      |

| Figure 12-3. JTAG Functional Timing                                      | 165  |

## LIST OF TABLES

| Table 2-1. T1 Related Telecommunications Specifications                | 10  |

|------------------------------------------------------------------------|-----|

| Table 7-1. Detailed Pin Descriptions                                   |     |

| Table 8-1. Clock Selection for the Ethernet (LAN) Interface            |     |

| Table 8-2. Reset Functions                                             |     |

| Table 8-3. Commands Sent and Received on the IMUX Links                |     |

| Table 8-4. Command and Status for the IMUX for Processor Communication | 35  |

| Table 8-5. Registers Related to Connections and Queues                 |     |

| Table 8-6. Options for Flow Control.                                   | 39  |

| Table 8-7. Registers Related to the Ethernet Port                      |     |

| Table 8-8. MAC Control Registers                                       |     |

| Table 8-9. MAC Status Registers                                        | 46  |

| Table 9-1. Register Address Map                                        |     |

| Table 9-2. Global Register Bit Map                                     |     |

| Table 9-3. Arbiter Register Bit Map                                    |     |

| Table 9-4. BERT Register Bit Map                                       |     |

| Table 9-5. Serial Interface Register Bit Map                           |     |

| Table 9-6. Ethernet Interface Register Bit Map                         |     |

| Table 9-7. MAC Indirect Register Bit Map                               |     |

| Table 11-1. Recommended DC Operating Conditions                        |     |

| Table 11-2. DC Electrical Characteristics                              |     |

| Table 11-3. Thermal Characteristics                                    |     |

| Table 11-4. Theta-JA vs. Airflow                                       |     |

| Table 11-5. Transmit MII Interface                                     |     |

| Table 11-6. Receive MII Interface                                      |     |

| Table 11-7. Transmit RMII Interface                                    |     |

| Table 11-8. Receive RMII Interface                                     | 147 |

| Table 11-9. MDIO Interface                                             |     |

| Table 11-10. Transmit WAN Interface                                    |     |

| Table 11-11. Receive WAN Interface                                     |     |

| Table 11-12. SDRAM Interface Timing                                    |     |

| Table 11-13. AC Characteristics—Microprocessor Bus Timing              | 155 |

| Table 11-14. JTAG Interface Timing                                     | 158 |

| Table 12-1. Instruction Codes for IEEE 1149.1 Architecture             |     |

| Table 12-2. ID Code Structure                                          | 164 |

#### **1 DESCRIPTION**

The DS33Z41 provides interconnection and mapping functionality between Ethernet Packet Systems and WAN Time-Division Multiplexed (TDM) systems such as T1/E1/J1, HDSL, and T3/E3. The device is composed of a 10/100 Ethernet MAC, Packet Arbiter, Committed Information Rate controller (CIR), HDLC/X.86 (LAPS) Mapper, SDRAM interface, control ports, and Bit Error Rate Tester (BERT). The packet interface consists of an Ethernet interface using several physical layer protocols. The Ethernet interface can be configured for 10Mbps or 100Mbps service. The DS33Z41 encapsulates Ethernet traffic with HDLC or X.86 (LAPS) to be transmitted over the WAN interface also receives encapsulated Ethernet packets and transmits the extracted packets over the Ethernet port. The WAN physical interface is based on the Dallas Semiconductor Interleaved Bus Operation (IBO), running at 8.192Mbps. The IBO interface can be configured to allow up to four bonded T1 or E1 data streams. The IBO interface provides for seamless connection to the Dallas Semiconductor/Maxim multi-port T1/E1/J1 Framers and Single-Chip Transceivers (SCTs). See *Application Note 3411: DS33Z11—Ethernet LAN to Unframed T1/E1 WAN Bridge* for an example of a complete LAN to WAN solution.

The DS33Z41 is controlled through an 8-bit microcontroller port. The DS33Z41 has a 100MHz SDRAM controller and interfaces to a 32-bit wide 128Mb SDRAM. The SDRAM is used to buffer the data from the Ethernet and WAN ports for transport. The external SDRAM can accommodate up to 8192 frames with a maximum frame size of 2016 bytes. The DS33Z41 operates with a 1.8V core supply and 3.3V I/O supply.

## 2 FEATURE HIGHLIGHTS

#### 2.1 General

- 169-pin, 14mm x 14mm CSBGA package

- 1.8V supply with 3.3V tolerant inputs and outputs

- IEEE 1149.1 JTAG boundary scan

- Software access to device ID and silicon revision

- Development support includes evaluation kit, driver source code, and reference designs

#### 2.2 Link Aggregation (Inverse Multiplexing)

- Link aggregation for up to 4 T1/E1 Links

- 8.192Mbps IBO interface to Dallas Semiconductor Framers/Transceivers

- Differential delay compensation up to 7.75ms for the 4 T1/E1 links

- Handshaking protocol between local and distant end for establishment of aggregation

#### 2.3 HDLC

- HDLC controller engine

- Compatible with polled or interrupt driven environments

- Programmable FCS insertion and extraction

- Programmable FCS type

- Supports FCS error insertion

- Programmable packet size limits (Minimum 64 bytes and maximum 2016 bytes)

- Supports bit stuffing/destuffing

- Selectable packet scrambling/descrambling (X<sup>43</sup>+1)

- Separate FCS errored packet and aborted packet counts

- Programmable inter-frame fill for transmit HDLC

#### 2.4 Committed Information Rate (CIR) Controller

- CIR controller limits transmission of data from the Ethernet Interface to the Serial Interface.

- CIR granularity at 512kbps

- CIR Averaging for smoothing traffic peaks

#### 2.5 X.86 Support

- Programmable X.86 address/control fields for transmit and receive

- Programmable 2-byte protocol (SAPI) field for transmit and receive

- 32 bit FCS

- Transmit Transparency processing 7E is replaced by 7D, 5E

- Transmit Transparency processing 7D replaced by 7D, 5D

- Receive rate adaptation (7D, DD) is deleted.

- Receive Transparency processing 7D, 5E is replaced by 7E

- Receive Transparency processing 7D, 5D is replaced by 7D

- Receive Abort Sequence the LAPS packet is dropped if 7D7E is detect

- Self-synchronizing X<sup>43</sup>+1 payload scrambling.

- Frame indication due to bad Address/Control/SAPI, FCS error, abort sequence or frame size longer than preset max.

#### 2.6 SDRAM Interface

- Interface for 128Mb, 32-bit-wide SDRAM

- SDRAM Interface speed up to 100MHz

- Auto Refresh Timing

- Automatic Precharge

- Master clock provided to the SDRAM

- No external components required for SDRAM connectivity

#### 2.7 MAC Interface

- MAC port with standard MII (less TX\_ER) or RMII

- 10Mbps and 100Mbps Data rates

- Configurable DTE or DCE modes

- Facilitates auto-negotiation by host microprocessor

- Programmable half and full-duplex modes

- Flow control for both half-duplex (back-pressure) and full-duplex (PAUSE) modes

- Programmable Maximum MAC frame size up to 2016 bytes

- Minimum MAC frame size: 64 bytes

- Discards frames greater than Programmed Maximum MAC frame size and Runt, non-octet bounded, or bad-FCS frames upon reception

- Programmable threshold for SDRAM queues to initiate flow control and status indication

- MAC Loopback support for Transmit data looped to Receive Data at the MII/RMII interface

#### 2.8 Microprocessor Interface

- 8 bit data bus

- Non-multiplexed Intel and Motorola Timing Modes

- Internal software reset and External Hardware reset input pin

- Global interrupt output pin

#### 2.9 Test and Diagnostics

- IEEE 1149.1 Support

- Programmable on-chip Bit Error Rate Tester (BERT)

- Patterns include Pseudorandom QRSS, Daly, and user-defined repetitive patterns

- Loopbacks (remote, local, analog, and per-channel loopback)

## 2.10 Specifications compliance

The DS33Z41 meets relevant telecommunications specifications. The following table provides the specifications and relevant sections that are applicable to the DS33Z41.

#### Table 2-1. T1 Related Telecommunications Specifications

IEEE 802.3-2002—CSMA/CD access method and physical layer specifications

RFC1662—PPP in HDLC-like Framing

RFC2615—PPP over SONET/SDH

X.86—*Ethernet over LAPS*

RMII—Industry Implementation Agreement for "Reduced MII Interface" (Sept. 1997)

## **3 APPLICATIONS**

- Bonded Transparent LAN Service

- LAN Extension

- Ethernet Delivery Over T1/E1/J1, T3/E3, OC-1/EC-1, G.SHDSL, or HDSL2/4

Refer also to Application Note 3411: DS33Z11—Ethernet LAN to Unframed T1/E1 WAN Bridge for an example of a complete LAN to WAN design.

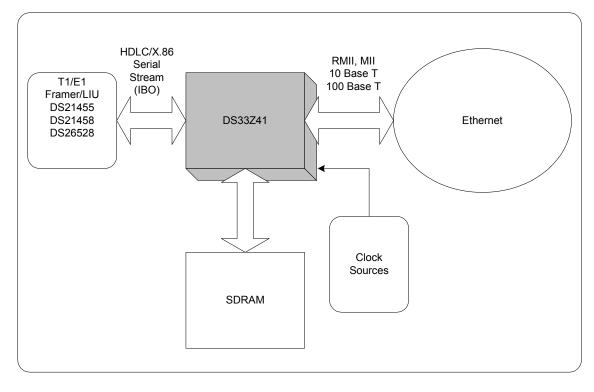

## Figure 3-1. Quad T1/E1 SCT to DS33Z41

## 4 ACRONYMS AND GLOSSARY

- BERT—Bit Error Rate Tester

- DCE—Data Communication Interface

- DTE—Data Terminating Interface

- FCS—Frame Check Sequence

- HDLC—High Level Data Link Control

- MAC—Media Access Control

- MII—Media Independent Interface

- RMII—Reduced Media Independent Interface

- WAN—Wide Area Network

**Note 1:** Previous versions of this document used the term "Subscriber" to refer to the Ethernet Interface function. The register names have been allowed to remain with a "SU." prefix to avoid register renaming.

**Note 2:** Previous versions of this document used the term "Line" to refer to the Serial Interface. The register names have been allowed to remain with a "LI." prefix to avoid register renaming.

**Note 3:** The terms "Transmit Queue" and "Receive Queue" are with respect to the Ethernet Interface. The Receive Queue is the queue for the data that arrives on the MII/RMII interface, is processed by the MAC and stored in the SDRAM. Transmit queue is for data that arrives from the Serial port, is processed by the HDLC and stored in the SDRAM to be sent to the MAC transmitter.

**Note 4:** This data sheet assumes a particular nomenclature of the T1 and E1 operating environment. In each  $125\mu$ s T1 frame, there are 24 8-bit channels plus a framing bit. It is assumed that the framing bit is sent first followed by channel 1.

#### TIME SLOT NUMBERING SCHEMES

| Time Slot | 0 | 1 | 2        | 3 | 4 | 5 | 6 | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|-----------|---|---|----------|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Channel   | 1 | 2 | 3        | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

| Phone     |   | 1 | <u>ر</u> | 2 | 4 | 5 | 6 | 7 | 0 | 0  | 10 | 11 | 10 | 12 | 14 | 15 |    | 16 | 17 | 10 | 10 | 20 | 21 | 22 | 22 | 24 | 25 | 26 | 27 | 20 | 20 | 30 |

| Channel   |   |   | 2        | 3 | 4 | 5 | 0 | ' | 0 | 9  | 10 | 11 | 12 | 13 | 14 | 15 |    | 10 | 17 | 10 | 19 | 20 | 21 | 22 | 23 | 24 | 20 | 20 | 21 | 20 | 29 | 30 |

## 5 MAJOR OPERATING MODES

Operation of the DS33Z41 operation requires a host microprocessor for initialization and maintenance of the link aggregation functions. Microprocessor control is possible through the 8-bit parallel control port. More information on microprocessor control is available in Section <u>8.1</u>.

## 6 BLOCK DIAGRAMS

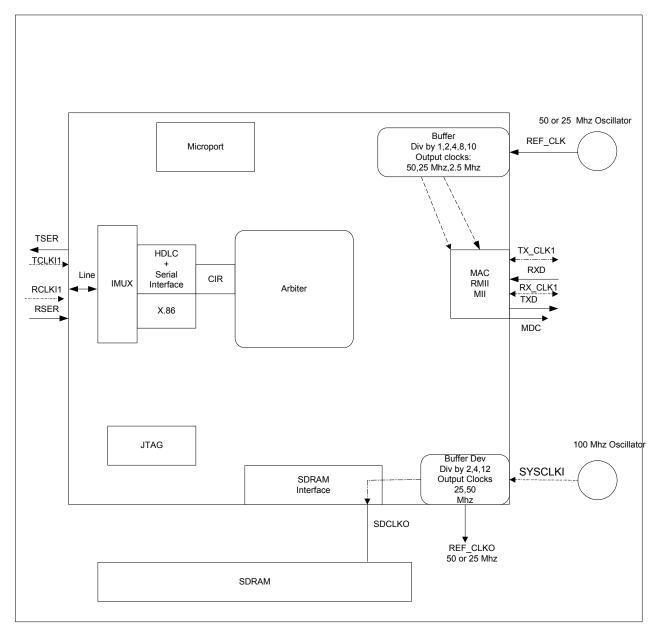

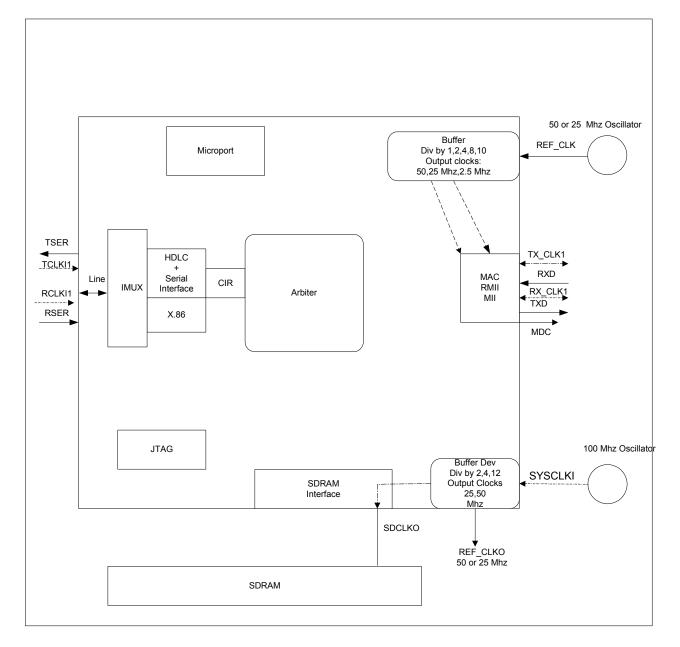

## Figure 6-1. Detailed Block Diagram

## 7 PIN DESCRIPTIONS

#### 7.1 Pin Functional Description

Note that all digital pins are inout pins in JTAG mode. This feature increases the effectiveness of board level ATPG patterns.

#### Table 7-1. Detailed Pin Descriptions

Note: I = Input; O = Output; Ipu = Input with pullup; Oz = Output with tri-state; IO = Bidirectional pin; IOz = Bidirectional pin with tri-state.

| NAME     | PIN | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     |      | SERIAL INTERFACE IO PINS                                                                                                                                                                                                                                                                                                                                            |

| TCLKI    | F1  | I    | <b>Serial Interface Transmit Clock Input.</b> The clock reference for TSER, which is output on the rising edge of the clock. TCLKI supports gapped clocking, up to a maximum frequency of 52MHz.                                                                                                                                                                    |

| TSER     | F2  | 0    | <b>Transmit Serial Data Output.</b> Output on the rising edge of TCLKI.<br>Selective clock periods can be skipped for output of TSER with a<br>gapped clock input on TCLKI. The maximum data rate is 52Mbps.                                                                                                                                                        |

| TSYNC    | G3  | I    | <b>Transmit Synchronization Input.</b> An 8IHz synchronization pulse, used to denote the first Channel 1 of the 8.192Mbps byte-interleaved IBO data stream. Note that this input is also used to generate the transmit byte synchronization if X.86 mode is enabled.                                                                                                |

| RCLKI    | G2  | I    | Serial Interface Receive Clock Input. Reference clock for receive serial data on RSER. Gapped clocking is supported, up to the maximum RCLKI frequency of 52MHz.                                                                                                                                                                                                    |

| RSER     | H1  | I    | <b>Receive Serial Data Input.</b> Receive Serial data arrives on the rising edge of the clock.                                                                                                                                                                                                                                                                      |

| RSYNC    | G1  | I    | <b>Receive Synchronization Input.</b> An 8kHz synchronization pulse, used to denote the first Channel 1 of the 8.192Mbps byte-interleaved IBO data stream. Note that this input is also used to generate the receive byte synchronization if X.86 mode is enabled.                                                                                                  |

|          |     |      | MII/RMII PORT                                                                                                                                                                                                                                                                                                                                                       |

| REF_CLK  | D13 | I    | Reference Clock (RMII and MII). When in RMII mode, all signals from<br>the PHY are synchronous to this clock input for both transmit and<br>receive. This required clock can be up to 50MHz and should have<br>±100ppm accuracy.<br>When in MII mode in DCE operation, the DS33Z41 uses this input to<br>generate the RX_CLK and TX_CLK outputs as required for the |

|          |     |      | Ethernet PHY interface. When the MII interface is used with DTE operation, this clock is not required and should be tied low.<br>In DCE and RMII modes, this input must have a stable clock input                                                                                                                                                                   |

|          |     |      | before setting the $\overline{RST}$ pin high for normal operation.                                                                                                                                                                                                                                                                                                  |

| REF_CLKO | E13 | ο    | <b>Reference Clock Output (RMII and MII).</b> A derived clock output up to 50MHz, generated by internal division of the SYSCLKI signal.<br>Frequency accuracy of the REF_CLKO signal will be proportional to the accuracy of the user-supplied SYSCLKI signal. See Section <u>8.2.2</u> for more information.                                                       |

| 查询"DS33Z41<br>NAME                   | "供应商                     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_CLK                               | A8                       | ю    | Transmit Clock (MII). Timing reference for TX_EN and TXD[3:0]. The TX_CLK frequency is 25MHz for 100Mbps operation and 2.5MHz for 10Mbps operation.<br>In DTE mode, this is a clock input provided by the PHY. In DCE mode, this is an output derived from REF_CLK providing 2.5MHz (10Mbps operation) or 25MHz (100Mbps operation).                                                                                                                                                                                      |

| TX_EN                                | E10                      | 0    | Transmit Enable (MII):         This pin is asserted high when data TXD [3:0] is being provided by the DS33Z41. The signal is deasserted prior to the first nibble of the next frame. This signal is synchronous with the rising edge TX_CLK. It is asserted with the first bit of the preamble.         Transmit Enable (RMII):         When this signal is asserted, the data on TXD [1:0] is valid. This signal is synchronous to the REF_CLK.                                                                          |

| TXD[0]<br>TXD[1]<br>TXD[2]<br>TXD[3] | B9<br>C9<br>D9<br>E9     | 0    | Transmit Data 0 through 3(MII). TXD [3:0] is presented synchronously with the rising edge of TX_CLK. TXD [0] is the least significant bit of the data. When TX_EN is low the data on TXD should be ignored. Transmit Data 0 through 1(RMII). Two bits of data TXD [1:0] presented synchronously with the rising edge of REF_CLK.                                                                                                                                                                                          |

| RX_CLK                               | A10                      | IO   | <b>Receive Clock (MII).</b> Timing reference for RX_DV, RX_ERR and RXD[3:0], which are clocked on the rising edge. RX_CLK frequency is 25MHz for 100Mbps operation and 2.5MHz for 10Mbps operation. In DTE mode, this is a clock input provided by the PHY. In DCE mode, this is an output derived from REF_CLK providing 2.5MHz (10Mbps operation) or 25MHz (100Mbps operation).                                                                                                                                         |

| RXD[0]<br>RXD[1]<br>RXD[2]<br>RXD[3] | B11<br>C11<br>D11<br>A11 | I    | Receive Data 0 through 3(MII). Four bits of received data, sampled synchronously with the rising edge of RX_CLK. For every clock cycle, the PHY transfers 4 bits to the DS33Z41. RXD[0] is the least significant bit of the data. Data is not considered valid when RX_DV is low.<br>Receive Data 0 through 1(RMII). Two bits of received data, sampled synchronously with REF_CLK with 100Mbps mode. Accepted when CRS_DV is asserted. When configured for 10Mbps mode, the data is sampled once every 10 clock periods. |

| RX_DV                                | D10                      | I    | <b>Receive Data Valid (MII).</b> This active high signal indicates valid data from the PHY. The data RXD is ignored if RX_DV is not asserted high.                                                                                                                                                                                                                                                                                                                                                                        |

| RX_CRS/<br>CRS_DV                    | C8                       | I    | <ul> <li>Receive Carrier Sense (MII). Should be asserted (high) when data from the PHY (RXD[3:0) is valid. For each clock pulse 4 bits arrive from the PHY. Bit 0 is the least significant bit. In DCE mode, connect to V<sub>DD</sub>.</li> <li>Carrier Sense/Receive Data Valid (RMII). This signal is asserted (high) when data is valid from the PHY. For each clock pulse 2 bits arrive from the PHY. In DCE mode, this signal must be grounded.</li> </ul>                                                          |

| RX_ERR                               | B12                      | I    | Receive Error (MII). Asserted by the MAC PHY for one or more<br>RX_CLK periods indicating that an error has occurred. Active High<br>indicates Receive code group is invalid. If CRS_DV is low, RX_ERR<br>has no effect. This is synchronous with RX_CLK. In DCE mode, this<br>signal must be grounded.<br>Receive Error (RMII). Signal is synchronous to REF_CLK.                                                                                                                                                        |

| 查询"DS33Z41<br>NAME | *供应商 | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COL_DET            | B13  | I    | <b>Collision Detect (MII).</b> Asserted by the MAC PHY to indicate that a collision is occurring. In DCE Mode this signal should be connected to ground. This signal is only valid in half duplex mode, and is ignored in full duplex mode                                                                                                                                                                                                  |

| MDC                | C12  | 0    | <b>Management Data Clock (MII).</b> Clocks management data between the PHY and DS33Z41. The clock is derived from SYSCLKI, with a maximum frequency is 1.67MHz. The user must leave this pin unconnected in the DCE Mode.                                                                                                                                                                                                                   |

| MDIO               | C13  | Ю    | <b>MII Management data IO (MII).</b> Data path for control information<br>between the PHY and DS33Z41. When not used, pull to logic high<br>externally through a $10k\Omega$ resistor. The MDC and MDIO pins are used<br>to write or read up to 32 Control and Status Registers in 32 PHY<br>Controllers. This port can also be used to initiate Auto-Negotiation for<br>the PHY. The user must leave this pin unconnected in the DCE Mode. |

|                    |      |      | MICROPROCESSOR PORT                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A0                 | A1   | I    | Address Bit 0. Address bit 0 of the microprocessor interface. Least Significant Bit.                                                                                                                                                                                                                                                                                                                                                        |

| A1                 | B1   | I    | Address Bit 1. Address bit 1 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A2                 | A2   | I    | Address Bit 2. Address bit 2 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A3                 | B2   | I    | Address Bit 3. Address bit 3 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A4                 | C2   | I    | Address Bit 4. Address bit 4 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A5                 | A3   | Ι    | Address Bit 5. Address bit 5 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A6                 | B3   | I    | Address Bit 6. Address bit 6 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A7                 | C3   | I    | Address Bit 7. Address bit 7 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A8                 | A4   | I    | Address Bit 8. Address bit 8 of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| A9                 | B4   | Т    | Address Bit 9. Address bit 9 of the microprocessor interface. Most Significant Bit.                                                                                                                                                                                                                                                                                                                                                         |

| D0                 | A5   | IOZ  | <b>Data Bit 0.</b> Bidirectional data bit 0 of the microprocessor interface.<br>Least Significant Bit. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                        |

| D1                 | A6   | IOZ  | <b>Data Bit 1.</b> Bidirectional data bit 1 of the microprocessor interface. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                                                  |

| D2                 | A7   | IOZ  | <b>Data Bit 2.</b> Bidirectional data bit 2 of the microprocessor interface. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                                                  |

| D3                 | B5   | IOZ  | <b>Data Bit 3.</b> Bidirectional data bit 3 of the microprocessor interface. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                                                  |

| D4                 | B6   | IOZ  | <b>Data Bit 4.</b> Bidirectional data bit 4 of the microprocessor interface. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                                                  |

| D5                 | B7   | IOZ  | <b>Data Bit 5.</b> Bidirectional data bit 5 of the microprocessor interface. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                                                  |

| D6                 | C5   | IOZ  | <b>Data Bit 6.</b> Bidirectional data bit 6 of the microprocessor interface. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                                                  |

| D7                 | C6   | IOZ  | <b>Data Bit 7.</b> Bidirectional data bit 7 of the microprocessor interface. Most Significant Bit. Not driven when $\overline{CS} = 1$ or $\overline{RST} = 0$ .                                                                                                                                                                                                                                                                            |

| CS                 | C1   | I    | <b>Chip Select.</b> This pin must be taken low for read/write operations. When $\overline{CS}$ is high, the $\overline{RD}/\overline{DS}$ and $\overline{WR}$ signals are ignored.                                                                                                                                                                                                                                                          |

| 查询"DS33Z41<br>NAME   | "供应商     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD/DS                | E1       | 1    | <b>Read Data Strobe (Intel Mode).</b> The DS33Z41 drives the data bus (D0-D7) with the contents of the addressed register while $\overline{RD}$ and $\overline{CS}$ are both low.                                                                                                                                                                                                                                                              |

|                      |          |      | <b>Data Strobe (Motorola Mode).</b> Used to latch data through the microprocessor interface. $\overline{\text{DS}}$ must be low during read and write operations.                                                                                                                                                                                                                                                                              |

| WR/RW                | E2       | I    | <b>Write (Intel Mode).</b> The DS33Z41 captures the contents of the data bus (D0:D7) on the rising edge of $\overline{WR}$ and writes them to the addressed register location. $\overline{CS}$ must be held low during write operations.<br><b>Read Write (Motorola Mode).</b> Used to indicate read or write operation. $\overline{RW}$ must be set high for a register read cycle and low for a register write cycle.                        |

| ĪNT                  | F3       | OZ   | <b>Interrupt Output.</b> Outputs a logic zero when an unmasked interrupt event is detected. Outputs a logic zero when an unmasked interrupt event is detected. INT is deasserted when all interrupts have been acknowledged and serviced. Active low. Inactive state is programmable in register GL.CR1. is deasserted when all interrupts have been acknowledged and serviced. Active low. Inactive state is programmable in register GL.CR1. |

| RST                  | D8       | I    | <b>Reset.</b> An active-low signal on this pin resets the internal registers and logic. This pin should remain low until power, SYSCLKI, RX_CLK, and TX_CLK are stable, then set high for normal operation. This input requires a clean edge with a rise time of 25ns or less to properly reset the device.                                                                                                                                    |

| MODEC[0]<br>MODEC[1] | D6<br>D7 | I    | Mode Control<br>00 = Read/Write Strobe Used (Intel Mode)<br>01 = Data Strobe Used (Motorola Mode)<br>10 = Reserved. Do not use.<br>11 = Reserved. Do not use.                                                                                                                                                                                                                                                                                  |

| DCEDTES              | A13      | I    | <b>DCE or DTE Selection.</b> The user must set this pin high for DCE Mode selection or low for DTE Mode. In DCE Mode, the DS33Z41 MAC port can be directly connected to another MAC. In DCE Mode, the Transmit clock (TX_CLK) and Receive clock (RX_CLK) are output by the DS33Z41. Note that there is no software bit selection of DCEDTES. Note that DCE Mode is only relevant when the MAC interface is in MII mode.                        |

| RMIIMIIS             | C4       | I    | <b>RMII or MII Selection.</b> Set high to configure the MAC for RMII interfacing. Set low for MII interfacing.                                                                                                                                                                                                                                                                                                                                 |

| 查询"DS33Z41<br>NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | "供应商                                                                                                                                                                                                     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | 1    | SDRAM CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDATA[0]         SDATA[1]         SDATA[2]         SDATA[3]         SDATA[4]         SDATA[5]         SDATA[6]         SDATA[6]         SDATA[7]         SDATA[8]         SDATA[10]         SDATA[11]         SDATA[12]         SDATA[13]         SDATA[14]         SDATA[15]         SDATA[16]         SDATA[17]         SDATA[16]         SDATA[20]         SDATA[20]         SDATA[20]         SDATA[21]         SDATA[22]         SDATA[23]         SDATA[24]         SDATA[26]         SDATA[27]         SDATA[28]         SDATA[29]         SDATA[30]         SDATA[31] | $\begin{array}{c} M1\\ L2\\ N1\\ M2\\ N2\\ N4\\ N3\\ L4\\ J3\\ M3\\ H3\\ J1\\ J2\\ K1\\ K2\\ L1\\ M12\\ H11\\ M11\\ N13\\ N11\\ L13\\ N12\\ K13\\ J12\\ H13\\ H12\\ G12\\ F11\\ G11\\ L10\\ \end{array}$ | IOZ  | SDRAM Data Bus Bits 0 to 31: The 32 pins of the SDRAM data bus<br>are inputs for read operations and outputs for write operations. At all<br>other times, these pins are high impedance.<br>Note: All SDRAM operations are controlled entirely by the DS33Z41.<br>No user programming for SDRAM buffering is required.                                                                                                                                                   |

| SDA[0]<br>SDA[1]<br>SDA[2]<br>SDA[3]<br>SDA[4]<br>SDA[5]<br>SDA[6]<br>SDA[6]<br>SDA[7]<br>SDA[8]<br>SDA[9]<br>SDA[10]<br>SDA[11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N9<br>N10<br>L11<br>L7<br>L8<br>L9<br>L5<br>M5<br>M7<br>M8<br>N8                                                                                                                                         | Ο    | <b>SDRAM Address Bus 0 to 11.</b> The 12 pins of the SDRAM address bus output the row address first, followed by the column address. The row address is determined by SDA0 to SDA11 at the rising edge of clock. Column address is determined by SDA0-SDA9 and SDA11 at the rising edge of the clock. SDA10 is used as an auto-precharge signal. Note: All SDRAM operations are controlled entirely by the DS33Z41. No user programming for SDRAM buffering is required. |

| SBA[0]<br>SBA[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | M6<br>N7                                                                                                                                                                                                 | I    | <b>SDRAM Bank Select.</b> These 2 bits select 1 of 4 banks for the read/write/precharge operations.<br>Note: All SDRAM operations are controlled entirely by the DS33Z41.<br>No user programming for SDRAM buffering is required.                                                                                                                                                                                                                                        |

| SRAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | K6                                                                                                                                                                                                       | ο    | <b>SDRAM Row Address Strobe.</b> Active-low output, used to latch the row address on rising edge of SDCLKO. It is used with commands for Bank Activate, Precharge, and Mode Register Write.                                                                                                                                                                                                                                                                              |

| 查询"DS33Z41<br>NAME                               | "供应商                  | TYPE       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------------------------------------------|-----------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SCAS                                             | H4                    | о          | <b>SDRAM Column Address Strobe.</b> Active-low output, used to latch the column address on the rising edge of SDCLKO. It is used with commands for Bank Activate, Precharge, and Mode Register Write.                                                                                                                                                                                                     |  |  |  |  |

| SWE                                              | M4                    | 0          | <b>SDRAM Write Enable.</b> This active-low output enables write operation and auto precharge.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| SDMASK[0]<br>SDMASK[1]<br>SDMASK[2]<br>SDMASK[3] | N6<br>G4<br>M10<br>M9 | 0          | <b>SDRAM Mask 0 to 3.</b> When high, a write is done for that byte. The least significant byte is SDATA7 to SDATA0. The most significant byte is SDATA31 to SDATA24.                                                                                                                                                                                                                                      |  |  |  |  |

| SDCLKO                                           | N5                    | O<br>(4mA) | <b>SDRAM CLK Out.</b> System clock output to the SDRAM. This clock is a buffered version of SYSCLKI.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| SYSCLKI                                          | G13                   | I          | <b>System Clock In.</b> 100MHz System Clock input to the DS33Z41, used for internal operation. This clock is buffered and provided at SDCLKO for the SDRAM interface. The DS33Z41 also provides a divided version output at the REF_CLKO pin. A clock supply with ±100ppm frequency accuracy is suggested.                                                                                                |  |  |  |  |

| SDCS                                             | L6                    | 0          | SDRAM Chip Select. Active-low output enables SDRAM access.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                                  | QUEUE STATUS          |            |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| QOVF                                             | C7                    | 0          | <b>Queue Overflow.</b> This pin goes high when the transmit or receive queue has overflowed. This pin will go low when the high watermark is reached again.                                                                                                                                                                                                                                               |  |  |  |  |

|                                                  |                       |            | JTAG INTERFACE                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| JTRST                                            | E6                    | lpu        | <b>JTAG Reset.</b> JTRST is used to asynchronously reset the test access port controller. After power-up, a rising edge on JTRST will reset the test port and cause the device I/O to enter the JTAG DEVICE ID mode. Pulling JTRST low restores normal device operation. JTRST is pulled HIGH internally via a $10k\Omega$ resistor operation. If boundary scan is not used, this pin should be held low. |  |  |  |  |

| JTCLK                                            | D4                    | lpu        | <b>JTAG Clock.</b> This signal is used to shift data into JTDI on the rising edge and out of JTDO on the falling edge.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| JTDO                                             | E5                    | Oz         | <b>JTAG Data Out.</b> Test instructions and data are clocked out of this pin on the falling edge of JTCLK. If not used, this pin should be left unconnected.                                                                                                                                                                                                                                              |  |  |  |  |

| JTDI                                             | E4                    | lpu        | <b>JTAG Data In.</b> Test instructions and data are clocked into this pin on the rising edge of JTCLK. This pin has a $10k\Omega$ pullup resistor.                                                                                                                                                                                                                                                        |  |  |  |  |

| JTMS                                             | F7                    | lpu        | <b>JTAG Mode Select.</b> This pin is sampled on the rising edge of JTCLK and is used to place the test access port into the various defined IEEE 1149.1 states. This pin has a $10k\Omega$ pullup resistor.                                                                                                                                                                                               |  |  |  |  |

| 查询"DS33Z41"供应商<br>NAME |                                                                                                                                                     |   | FUNCTION                                  |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------|--|--|--|--|--|

|                        | POWER SUPPLIES                                                                                                                                      |   |                                           |  |  |  |  |  |

| VDD3.3                 | G5–G10,<br>H2, H5,<br>H6,<br>H7–H10                                                                                                                 | I | VDD3.3: Connect to 3.3V Power Supply      |  |  |  |  |  |

| VDD1.8                 | D3, D2,<br>E3, F4,<br>J4, K4,<br>L3, F10,<br>E11, E12,<br>D12, M13,<br>L12                                                                          | I | VDD1.8: Connect to 1.8V Power Supply      |  |  |  |  |  |

| VSS                    | A9, A12,<br>B10, C10,<br>D1, D5,<br>E7, E8,<br>F6, F8,<br>F12, F13,<br>J5, J6,<br>J11, J7,<br>J8, J9,<br>J10, K3,<br>K5, K7,<br>K8, K9,<br>K10, K12 | I | VSS: Connect to the Common Supply Ground  |  |  |  |  |  |

| N.C.                   | F5, F9, B8                                                                                                                                          | _ | No Connection. Do not connect these pins. |  |  |  |  |  |

#### F 音调: DF: 3月: 205: 35: 256-Ball CSBGA Pinout

|   | 1             | 2         | 3         | 4         | 5      | 6           | 7        | 8       | 9         | 10        | 11        | 12        | 13        |

|---|---------------|-----------|-----------|-----------|--------|-------------|----------|---------|-----------|-----------|-----------|-----------|-----------|

| А | A0            | A2        | A5        | A8        | D0     | D1          | D2       | TX_CLK  | VSS       | RX_CLK    | RXD[3]    | VSS       | DCEDTES   |