## **GROUND FAULT INTERRUPTER**

#### DESCRIPTION

The UTC LM1851 is designed to provide ground fault protection for AC power outlets in consumer and industrial environments. Ground fault currents greater than a presentable threshold value will trigger an external SCR-driven circuit breaker to interrupt the AC line and remove the fault condition. In addition to detection of conventional hot wire to ground faults, the neutral fault condition is also detected.

Full advantage of the U.S. UL943 timing specification is taken to insure maximum immunity to false triggering due to line noise. Special features include circuitry that rapidly resets the timing capacitor in the event that noise pulses introduce unwanted charging currents and a memory circuit that allows firing of even a sluggish breaker on either half-cycle of the line voltage when external full-wave rectification is used.

#### FEATURES

- \* Internal power supply shunt regulator

- \* Externally programmable fault current threshold

- \* Externally programmable fault current integration time

- \* Direct interface to SCR

- \* Operates under line reversal; both load vs line and hot vs neutral

- \* Detects neutral line faults

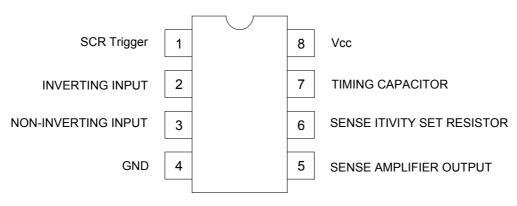

### PIN CONFIGURATION

**UTC** UNISONIC TECHNOLOGIES CO., LTD. 1

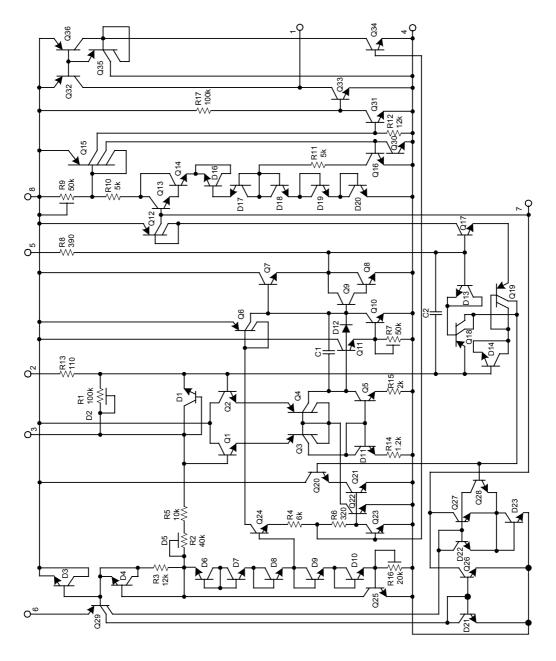

INTERNAL SCHEMATIC DIAGRAM

${\small UTC} \quad {\scriptstyle UNISONIC \, TECHNOLOGIES} \quad {\scriptstyle CO., \, LTD.} \quad {\scriptstyle 2}$

## UTC LM1851

# LINEAR INTEGRATED CIRCUIT

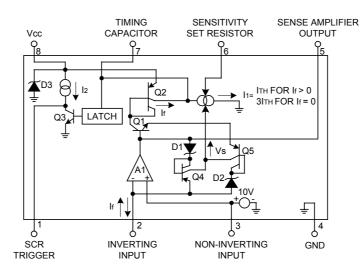

**BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS

| PARAMETER                  | SYMBOL | RATINGS    | UNIT |  |

|----------------------------|--------|------------|------|--|

| Supply Current             | lcc    | 19         | mA   |  |

| Power Dissipation (Note 1) | PD     | 1250       | mW   |  |

| Operating Temperature      | Topr   | -40 ~ +70  | °C   |  |

| Storage Temperature        | Tstg   | -55 ~ +150 | °C   |  |

| Lead Soldering Temperature |        |            |      |  |

| DIP-8 (10 sec.)            |        | 260        | °C   |  |

| SOP-8                      | TLED   |            |      |  |

| Vapor Phase (60 sec.)      |        | 215        | °C   |  |

| Infrared (15 sec.)         |        | 220        | °C   |  |

## DC ELECTRICAL CHARACTERISTICS (Ta = 25 °C, Iss=5mA)

| PARAMETER                                     | TEST CONDITIONS                                                             | MIN | TYP  | MAX | UNIT             |

|-----------------------------------------------|-----------------------------------------------------------------------------|-----|------|-----|------------------|

| Power Supply Shunt Regulator<br>Voltage       | Pin 8, Average Value                                                        | 22  | 26   | 30  | V                |

| Latch Trigger Voltage                         | Pin 7                                                                       | 15  | 17.5 | 20  | V                |

| Sensitivity Set Voltage                       | Pin 8 to Pin 6                                                              | 6   | 7    | 8.2 | V                |

| Output Drive Current                          | Pin 1, With Fault                                                           | 0.5 | 1    | 2.4 | mA               |

| Output Saturation Voltage                     | Pin 1, Without Fault                                                        |     | 100  | 240 | mV               |

| Output Saturation Resistance                  | Pin 1, Without Fault                                                        |     | 100  |     | Ω                |

| Output External Current Sinking<br>Capability | Pin 1, Without Fault<br>Vpin 1 Held to 0.3V (Note 4)                        | 2.0 | 5    |     | mA               |

| Noise Integration Sink Current Ratio          | Pin 7, Ratio of Discharge Currents Between<br>No Fault and Fault Conditions | 2.0 | 2.8  | 3.6 | $\mu$ A/ $\mu$ A |

UTC UNISONIC TECHNOLOGIES CO., LTD. 3

| AC ELECTRICAL CHARACTERISTICS (Ta = 25 °C, Iss=5mA) |                                                |     |     |     |      |  |

|-----------------------------------------------------|------------------------------------------------|-----|-----|-----|------|--|

| PARAMETER                                           | TEST CONDITIONS                                | MIN | TYP | MAX | UNIT |  |

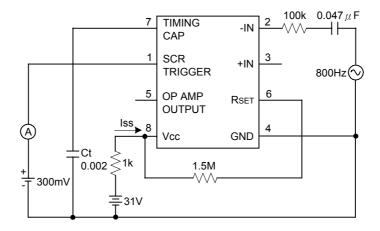

| Normal Fault Current Sensitivity                    | Figure 1 (Note 3)                              | 3   | 5   | 7   | mA   |  |

| Normal Fault Trip Time                              | 500 $\Omega$ Fault, Figure 2 (Note 2)          |     | 18  |     | ms   |  |

| Normal Fault with Grounded Neutral                  | 500 $\Omega$ Normal Fault, 2 $\Omega$ Neutral, |     | 18  |     | ms   |  |

| Fault Trip Time                                     | Figure 2 (Note 2)                              |     |     |     |      |  |

Note 1: For operation in ambient temperatures above 25  $^\circ\!\mathrm{C}$  , the device must be debated based on a 125  $^\circ\!\mathrm{C}$

maximum junction temperature and a thermal resistance of 80°C/W junction to ambient for the DIP and 162/W for the SO Package.

Note 2: Average of 10 trials.

Note 3: Required UL sensitivity tolerance is such that external trimming of UTC LM1851 sensitivity will be necessary. Note 4: This externally applied current is in addition to the internal "output drive current" source.

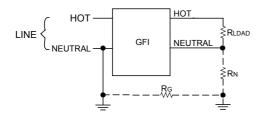

FIGURE 1.Normal Fault Sensitivity Test Circuit

#### CIRCUIT DESCRIPTION (Refer to Block and Connection Diagram)

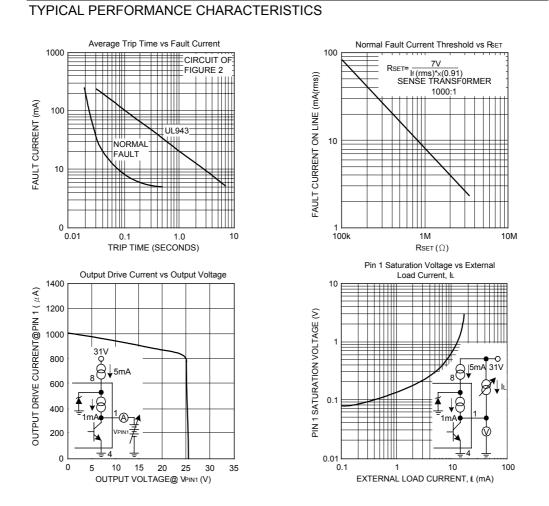

The UTC LM1851 operates from 26V as set by an internal shunt regulator, D3. In the absence of a fault (Ir=0) the feedback path status signal (Vs) is correspondingly zero. Under these conditions the capacitor discharge current, I1, sits quiescently at three times its threshold value, ITH, so that noise induced charge on the timing capacitor will be rapidly removed. When a fault current, Ir, is induced in the secondary of the external sense transformer, the operational amplifier, A1, uses feedback to force a virtual ground at the input as it extracts Ir. The presence of Ir during either half-cycle will cause Vs to go high, which in turn changes I1 from 3ITH to ITH. Although ITH discharges the timing capacitor during both half-cycles of the line, Ir only charges the capacitor during the half-cycle in which Ir exits pin 2. Thus during one half-cycle Ir-ITH charges the timing capacitor, while during the other half-cycle ITH discharges it. When the capacitor voltage reaches 17.5V, the latch engages and turns off Q3 permitting I2 to drive the gate of an SCR.

#### APPLICATION CIRCUITS

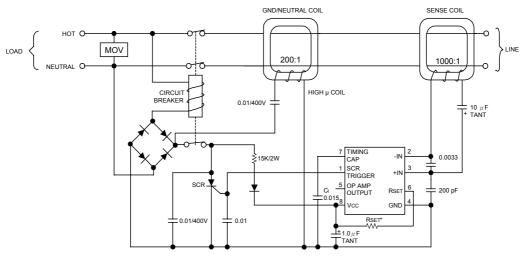

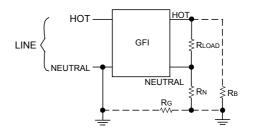

A typical ground fault interrupter circuit is shown in Figure 2. It is designed to operate on 120 Vac line voltage with 5 mA normal fault sensitivity.

A full-wave rectifier bridge and a 15k/2W resistor are used to supply the DC power required by the IC. A 1 µ F capacitor at pin 8 used to filter the ripple of the supply voltage and is also connected across the SCR to allow firing of the SCR on either half-cycle. When a fault causes the SCR to trigger, the circuit breaker is energized and line voltage is removed from the load. At this time no fault current flows and the IC discharge current increases from ITH to 3ITH (see Circuit Description and Block Diagram). This quickly resets both the timing capacitor and the output latch. At this time the circuit breaker can be reset and the line voltage again supplied to the load, assuming the fault has been removed A 10001 sense transformer is used to detect the normal fault. The fault current which is basically the difference current between the hot and neutral lines, is stepped down by 1000 and fed into the input pins of the operational amplifier through a 10  $\mu$  F capacitor. The 0.0033  $\mu$  F capacitor between pin 2 and pin 3 and the 200 pF between pins 3 and 4 are added to obtain better noise immunity. The normal fault sensitivity is determined by the timing capacitor discharging current, ITH. ITH can be calculated by:

$$ITH = \frac{7V}{RSET} \div 2$$

(1)

At the decision point, the average fault current just equals the threshold current, ITH.

$$I_{\text{TH}} = \frac{\text{If } (\text{rms})}{2} \times 0.91 \tag{2}$$

Where If(rms) is the rms input fault current to the operational amp and the factor of 2 is due to the fact that If charges the timing capacitor only during one half-cycle, while ITH discharges the capacitor continuously. The factor 0.91 converts the rms value to an average value. Combining equations (1) and (2) we have

$$RSET = \frac{7V}{If (rms) \times 0.91}$$

(3)

For example, to obtain 5mA (rms) sensitivity for the circuit in Figure 2 we have:

$$R_{SET} = \frac{7V}{\frac{5mA \times 0.91}{1000}} = 1.5M\Omega$$

(4)

The correct value for RSET can also be determined from the characteristic curve that plots equation (3). Note that this is an approximate calculation; the exact value of RSET depends on the specific sense transformer used and UTC LM1851 tolerances. Inasmuch as UL943 specifies a sensitivity " window " of 4mA ~ 6mA, provision should be made to adjust RSET on a per-product basis.

Independent of setting sensitivity, the desired integration time can be obtained through proper selection of the timing capacitor, Ct. Due to the large number of variables involved, proper selection of Ct is best done empirically. The following design example, then should only be used as a guideline.

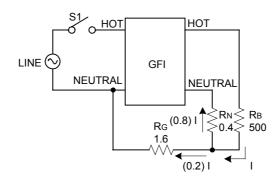

Assume the goal is to meet UL943 timing requirements. Also assume that worst-case timing occurs during GF1 Start-up (S1 closure) with both a heavy normal fault and a 2 $\Omega$  grounded neutral fault present. This situation is shown diagrammatically below.

UL943 specifies  $\leq$ 25 ms average trip time under these conditions. Calculation of C<sub>t</sub> based upon charging currents due to normal fault only is as follows:

${\leq}25\,\text{ms}$  Specification

-3 ms GFI turn-on time (15k and 1  $\mu$  F)

-8 ms Potential loss of one half-cycle due to fault current sense of half-cycles only

-4 ms Time required to open a sluggish circuit breaker

$\leq$ 10 ms Maximum integration time that could be allowed

8 ms Value of integration time that accommodates component tolerances and other variables

$$C_{t} = \frac{1 \times T}{V}$$

(5)

Where T=integration time

V=threshold voltage

I=average fault current into C<sub>t</sub>

I =  $\left(\frac{120VAC(rms)}{RB}\right) \times \left(\frac{R_{N}}{RG + R_{N}}\right)$

heavy fault portion of

current generated fault current

(swamps ITH) shunted

around GFI

$\times \left(\frac{1 \text{ turn}}{1000 \text{ turns}}\right) \times \left(\frac{1}{2}\right) \times \left(\frac{0.91}{2}\right)$

(6)

current Ct charging rms to

division of on half-average

input sense cycles only conversion

transformer

therefore:

$$C_{t} = \left[\left(\frac{120}{500}\right) \times \left(\frac{0.4}{1.6+0.4}\right) \times \left(\frac{1}{1000}\right) \times \left(\frac{1}{2}\right) \times \left(0.91\right)\right] \times 0.0008$$

(7)

Ct =  $0.01 \,\mu$  F

(5)

## APPLICATION CIRCUITS

In practice, the actual value of C1 will have to be modified to include the effects of the neutral loop upon the net charging current. The effect of neutral loop induced currents is difficult to quartile, but typically they sum with normal fault currents, thus allowing a larger value of C1.

For UL943 requirements, 0.015  $\mu$  F has been found to be the best compromise between timing and noise.

For those GFI standards not requiring grounded neutral detection, a still larger value capacitor can be used and better noise immunity obtained. The larger capacitor can be accommodated because RN and RG are not present, allowing the full fault current, I, to enter the GFI.

In Figure 2, grounded neutral detection is accomplished by feeding the neutral coil with 120 Hz energy continuously and allowing some of the energy to couple into the sense transformer during conditions of neutral fault.

## TYPICAL APPLICATION

\* Adjust RSET for desired sensitivity

FIGURE 2. 120Hz Neutral Transformer Approach

# UTC UNISONIC TECHNOLOGIES CO., LTD. 7

## UTC LM1851

# LINEAR INTEGRATED CIRCUIT

## **DEFINITION OF TERMS**

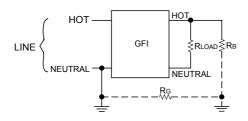

Normal Fault An unintentional electrical path ,  ${\bf R},$  between the load terminal of the hot line and the ground, as shown by the dashed lines

Grounded Neutral Fault: An unintentional electrical path between the load terminal of the neutral line and the ground, as shown by the dashed lines.

Normal Fault plus Grounded Neutral fault: The combination of the normal fault and the grounded neutral fault, as shown by the dashed lines.

UTC UNISONIC TECHNOLOGIES CO., LTD. 8

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.

UTC UNISONIC TECHNOLOGIES CO., LTD. 9