# 31.5 dB Range, 0.5 dB Step Size Programmable VGA

Preliminary Technical Data 0750

# ADL5201

#### **GENERAL DESCRIPTION**

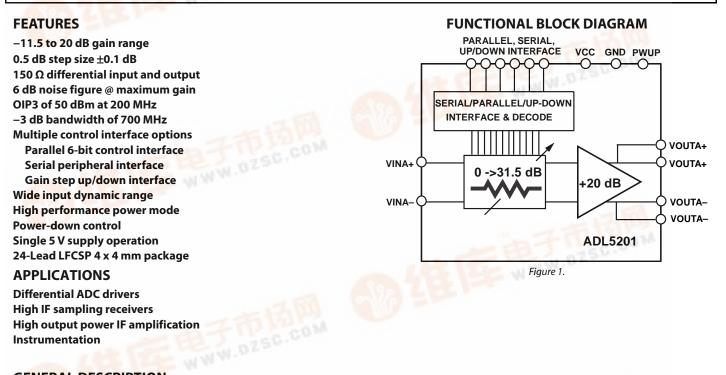

The ADL5201 is a digitally controlled, variable gain wide bandwidth amplifier that provides precise gain control, high IP3 and low noise figure. The excellent distortion performance and high signal bandwidth makes the ADL5201 an excellent gain control device for a variety of receiver applications.

For wide input dynamic range applications, the ADL5201 provides a broad 31.5 dB gain range with 0.5 dB resolution. The gain is adjustable through multiple gain control interface options: parallel, serial peripheral interface, or gain step up/down.

Using a high speed SiGe process and incorporating proprietary distortion cancellation techniques, the ADL5201 achieves better than 50 dBm output IP3 at frequencies approaching 200 MHz for all gain settings.

The ADL5201 is powered on by applying the appropriate logic level to the PWUP pin. The quiescent current of the ADL5201 is typically 80 mA. It may be configured for higher quiescent current of 110 mA, in high performance power mode, for more demanding applications. When powered down, the ADL5201 consumes less than 9 mA and offers excellent input to output isolation. The gain setting is preserved when powered down.

Fabricated on an ADI's high speed SiGe process, the ADL5201 provides precise gain adjustment capabilities with good distortion performance. The ADL5201 amplifier comes in a compact, thermally enhanced 4 x 4mm 24-lead LFCSP package and operates over the temperature range of -40°C to +85°C

#### Rev. PrD

df.dzsc.com

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No ficence is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2010 Analog Devices, Inc. All rights reserved.

## ADL5201 查询"ADL5201"供应商

## TABLE OF CONTENTS

| Features                 | 1 |

|--------------------------|---|

| Functional Block Diagram | 1 |

| General Description      | 1 |

| Revision History         | 2 |

| Specifications           |   |

| Absolute Maximum Ratings | 6 |

| Thermal Resistance       | 6 |

#### **REVISION HISTORY**

10/10—Rev. PrD

10/10—Rev. PrC

9/10—Rev. PrB

9/10—Rev. PrA

| ESD Caution                                  |

|----------------------------------------------|

| Pin Configuration and Function Descriptions7 |

| Digital Interface Overview                   |

| Typical Performance Characteristics9         |

| Outline Dimensions                           |

| Ordering Guide10                             |

## **SPECIFICATIONS**

$V_s = 5 V$ ,  $T = 25^{\circ}C$ ,  $Z_s = Z_L = 150\Omega$  at 100MHz, PM = 0 V, 2 V p-p differential output unless otherwise noted.

| Parameter                            | Conditions                                      | Min | Тур   | Max | Unit   |

|--------------------------------------|-------------------------------------------------|-----|-------|-----|--------|

| DYNAMIC PERFORMANCE                  |                                                 |     |       |     |        |

| –3 dB Bandwidth                      | V <sub>оυт</sub> < 2 V p-p (5.2dBm)             |     | 700   |     | MHz    |

| Slew Rate                            |                                                 |     | TBD   |     | V/nsec |

| INPUT STAGE                          | Pins VIN+ and VIN-                              |     |       |     |        |

| Maximum Input Swing                  | Gain Code = 111111                              |     | 8     |     | V p-p  |

| Differential Input Resistance        | Differential                                    |     | 150   |     | Ω      |

| Common-Mode Input Voltage            |                                                 |     | 1.5   |     | V      |

| CMRR                                 | Gain Code = 000000                              |     | TBD   |     | dB     |

| GAIN                                 |                                                 |     |       |     |        |

| Maximum Voltage Gain                 | Gain Code = 000000                              |     | 20    |     | dB     |

| Minimum Voltage Gain                 | Gain Code = 111111                              |     | -11.5 |     | dB     |

| Gain Step Size                       |                                                 |     | 0.5   |     | dB     |

| Gain Flatness                        | $30 \text{ MHz} < f_C < 200 \text{MHz}$         |     | TBD   |     | dB     |

| Gain Temperature Sensitivity         | Gain Code = 000000                              |     | TBD   |     | mdB/°C |

| Gain Step Response                   | For $V_{IN} = 0.2V$ , Gain Code 111111to 000000 |     | 15    |     | ns     |

| Gain Conformance Error               | Normalized to 10dB gain step                    |     | ±0.03 |     | dB     |

| Phase Conformance Error              | Normalized to 10dB gain step                    |     | 1.0   |     | deg    |

| OUTPUT STAGE                         | Pins OUT+ and OUT-                              |     |       |     |        |

| Output Voltage Swing                 | At P1dB, Gain Code = 000000                     |     | 10    |     | V р-р  |

| Differential Output Resistance       | Differential                                    |     | 150   |     | Ω      |

| NOISE/HARMONIC PERFORMANCE           |                                                 |     |       |     |        |

| 46 MHz [High Performance Power Mode] | Gain Code = 000000, LP = Low                    |     |       |     |        |

| Noise Figure                         |                                                 |     | 7.6   |     | dB     |

| Second Harmonic                      | $V_{OUT} = 2 V p - p$                           |     | -90   |     | dBc    |

| Third Harmonic                       | $V_{OUT} = 2 V p - p$                           |     | -100  |     | dBc    |

| Output IP3                           |                                                 |     | 47.1  |     | dBm    |

| Output 1 dB Compression Point        |                                                 |     | 19.0  |     | dBm    |

| 46 MHz [Nominal Power Mode]          | Gain Code = 000000, PM = High                   |     |       |     |        |

| Noise Figure                         |                                                 |     | TBD   |     | dB     |

| Second Harmonic                      | $V_{OUT} = 2 V p - p$                           |     | -90   |     | dBc    |

| Third Harmonic                       | $V_{OUT} = 2 V p - p$                           |     | -92   |     | dBc    |

| Output IP3                           |                                                 |     | TBD   |     | dBm    |

| Output 1 dB Compression Point        |                                                 |     | TBD   |     | dBm    |

| NOISE/HARMONIC PERFORMANCE           |                                                 |     |       |     |        |

| 70 MHz [High Performance Power Mode] | Gain Code = 000000, LP = Low                    |     |       |     |        |

| Noise Figure                         |                                                 |     | 7.4   |     | dB     |

| Second Harmonic                      | $V_{OUT} = 2 V p - p$                           |     | -95   |     | dBc    |

| Third Harmonic                       | $V_{OUT} = 2 V p - p$                           |     | -100  |     | dBc    |

| Output IP3                           |                                                 |     | 46.9  |     | dBm    |

| Output 1 dB Compression Point        |                                                 |     | 19.9  |     | dBm    |

## ADL5201 查询"ADL5201"供应商

| Parameter                                | Conditions                    | Min Typ Ma | k Unit |

|------------------------------------------|-------------------------------|------------|--------|

| 70 MHz [Nominal Power Mode]              | Gain Code = 000000, PM = High |            |        |

| Noise Figure                             |                               | TBD        | dB     |

| Second Harmonic                          | V <sub>OUT</sub> = 2 V p-p    | -90        | dBc    |

| Third Harmonic                           | V <sub>OUT</sub> = 2 V p-p    | -96        | dBc    |

| Output IP3                               |                               |            | dBm    |

| Output 1 dB Compression Point            |                               | TBD        | dBm    |

| NOISE/HARMONIC PERFORMANCE               |                               |            |        |

| 140 MHz [High Performance Power<br>Mode] | Gain Code = 000000, LP = Low  |            |        |

| Noise Figure                             |                               | 6.8        | dB     |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$         | -90        | dBc    |

| Third Harmonic                           | V <sub>OUT</sub> = 2 V p-p    | -96        | dBc    |

| Output IP3                               |                               | 47         | dBm    |

| Output 1 dB Compression Point            |                               | 20.1       | dBm    |

| 140 MHz [Nominal Power Mode]             | Gain Code = 000000, PM = High |            |        |

| Noise Figure                             |                               | TBD        | dB     |

| Second Harmonic                          | V <sub>OUT</sub> = 2 V p-p    | -90        | dBc    |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$         | -94        | dBc    |

| Output IP3                               |                               | TBD        | dBm    |

| Output 1 dB Compression Point            |                               | TBD        | dBm    |

| NOISE/HARMONIC PERFORMANCE               |                               |            |        |

| 170 MHz [High Performance Power<br>Mode] | Gain Code = 000000, LP = Low  |            |        |

| Noise Figure                             |                               | 6.8        | dB     |

| Second Harmonic                          | V <sub>OUT</sub> = 2 V p-p    | -84        | dBc    |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$         | -94        | dBc    |

| Output IP3                               |                               | 47.2       | dBm    |

| Output 1 dB Compression Point            |                               | 20.1       | dBm    |

| 170 MHz [Nominal Power Mode]             | Gain Code = 000000, PM = High |            |        |

| Noise Figure                             |                               | TBD        | dB     |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$         | -80        | dBc    |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$         | -93        | dBc    |

| Output IP3                               |                               | TBD        | dBm    |

| Output 1 dB Compression Point            |                               | TBD        | dBm    |

| NOISE/HARMONIC PERFORMANCE               |                               |            |        |

| 240 MHz [High Performance Power<br>Mode] | Gain Code = 000000, LP = Low  |            |        |

| Noise Figure                             |                               | 7.0        | dB     |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$         | -78        | dBc    |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$         | -95        | dBc    |

| Output IP3                               |                               | 46.7       | dBm    |

| Output 1 dB Compression Point            |                               | 20.1       | dBm    |

| 240 MHz [Nominal Power Mode]             | Gain Code = 000000, PM = High |            |        |

| Noise Figure                             |                               | TBD        | dB     |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$         | -77        | dBc    |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$         | -95        | dBc    |

| Output IP3                               |                               | TBD        | dBm    |

| Output 1 dB Compression Point            |                               | TBD        | dBm    |

### Preliminary Technical Data 查询"ADL5201"供应商

## ADL5201

| Parameter                                | Conditions                                                               | Min | Тур       | Max | Unit     |

|------------------------------------------|--------------------------------------------------------------------------|-----|-----------|-----|----------|

| NOISE/HARMONIC PERFORMANCE               |                                                                          |     |           |     |          |

| 300 MHz [High Performance Power<br>Mode] | Gain Code = 000000, LP = Low                                             |     |           |     |          |

| Noise Figure                             |                                                                          |     | 7.6       |     | dB       |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$                                                    |     | -78       |     | dBc      |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$                                                    |     | -90       |     | dBc      |

| Output IP3                               |                                                                          |     | 45.6      |     | dBm      |

| Output 1 dB Compression Point            |                                                                          |     | 19.8      |     | dBm      |

| 300 MHz [Nominal Power Mode]             | Gain Code = 000000, PM = High                                            |     |           |     |          |

| Noise Figure                             |                                                                          |     | TBD       |     | dB       |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$                                                    |     | -77       |     | dBc      |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$                                                    |     | -87       |     | dBc      |

| Output IP3                               |                                                                          |     | TBD       |     | dBm      |

| Output 1 dB Compression Point            |                                                                          |     | TBD       |     | dBm      |

| NOISE/HARMONIC PERFORMANCE               |                                                                          |     |           |     |          |

| 380 MHz [High Performance Power<br>Mode] | Gain Code = 000000, LP = Low                                             |     |           |     |          |

| Noise Figure                             |                                                                          |     | 7.8       |     | dB       |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$                                                    |     | -73       |     | dBc      |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$                                                    |     | -80       |     | dBc      |

| Output IP3                               |                                                                          |     | TBD       |     | dBm      |

| Output 1 dB Compression Point            |                                                                          |     | 18.8      |     | dBm      |

| 380 MHz [Nominal Power Mode]             | Gain Code = 000000, PM = High                                            |     |           |     |          |

| Noise Figure                             |                                                                          |     | TBD       |     | dB       |

| Second Harmonic                          | $V_{OUT} = 2 V p - p$                                                    |     | -74       |     | dBc      |

| Third Harmonic                           | $V_{OUT} = 2 V p - p$                                                    |     | -80       |     | dBc      |

| Output IP3                               |                                                                          |     | TBD       |     | dBm      |

| Output 1 dB Compression Point            |                                                                          |     | TBD       |     | dBm      |

| ENABLE INTERFACE                         | Pin PWUP                                                                 |     |           |     |          |

| Enable Threshold                         | Minimum voltage to enable the device                                     |     |           | 1.4 | v        |

| PWUP Input Bias Current                  |                                                                          |     | TBD       |     | nA       |

| GAIN CONTROL INTERFACE                   | Digital pins                                                             |     |           |     |          |

| VIH                                      | Minimum voltage for a logic high                                         | 1.4 |           |     | V        |

| VIL                                      | Maximum voltage for a logic low                                          |     |           | 0.8 |          |

| Maximum Input Bias Current               |                                                                          |     | TBD       |     | nA       |

| POWER-INTERFACE                          |                                                                          | 4.5 |           |     |          |

| Supply Voltage                           | DM - Low (High Dorfermen - Dower Marda)                                  | 4.5 | 110       | 5.5 | V        |

| Quiescent Current                        | PM = Low (High Performance Power Mode)<br>PM = High (Nominal Power Mode) |     | 110<br>80 |     | mA       |

| Power Down Current                       | PWI = High (Nominal Power Mode)<br>PWUP Low                              |     | 80<br>18  |     | mA<br>mA |

|                                          |                                                                          |     | 10        |     |          |

## **ABSOLUTE MAXIMUM RATINGS**

Table Summary

#### Table 2. Parameter Rating Supply Voltage, VPOS 5.5 V **PWUP**, Digital Pins -0.6 to (V<sub>POS</sub> + 0.6V) Input Voltage, V<sub>IN+</sub>, V<sub>IN-</sub> -0.6 to +3.1V Internal Power Dissipation TBD mW $\theta_{JA}$ (Exposed paddle soldered down) TBD°C/W TBD°C/W $\theta_{JA}$ (Exposed paddle not soldered down) $\theta_{JC}$ (At exposed paddle) TBD°C/W Maximum Junction Temperature TBD°C **Operating Temperature Range** -40°C to +85°C Storage Temperature Range -65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Preliminary Technical Data**

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type | Αιθ | οıc | Unit |

|--------------|-----|-----|------|

|              |     |     |      |

|              |     |     |      |

|              |     |     |      |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Preliminary Technical Data 查询"ADL5201"供应商

ADL5201

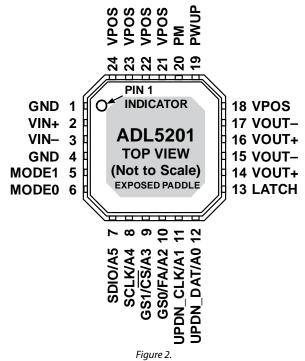

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### **Table 4. Pin Function Descriptions**

| Pin No.               | Mnemonic    | Description                                                                                                                  |

|-----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, EP <sup>1</sup> | GND         | Ground                                                                                                                       |

| 2                     | VIN+        | positive input.                                                                                                              |

| 3                     | VIN-        | negative input.                                                                                                              |

| 5                     | MODE1       | Mode control parallel, SPI, up/down (MSB)                                                                                    |

| 6                     | MODE0       | Mode control parallel, SPI, up/down (LSB)                                                                                    |

| 7                     | SDIO/A5     | Multifunction pin: Serial data input/output (bidirectional pin) in Parallel mode, this is bit 5. (MSB)                       |

| 8                     | SCLK/A4     | Multifunction pin: Serial clock input. In parallel mode this bit 4.                                                          |

| 9                     | GS1/CS/A3   | Multifunction pin: MSB for gain step function, chip select and bit 3 in parallel operation.                                  |

| 10                    | GS0/FA/A2   | Multifunction pin: LSB for gain step function, a logic high enables fast attack mode and in parallel mode this pin is bit 2. |

| 11                    | UPDN_CLK/A1 | Multifunction pin: Clock input for up down function. In parallel mode this pin is bit 1.                                     |

| 12                    | UPDN_DAT/A0 | Multifunction pin: Data pin for up down function. In parallel mode this is bit 0 (LSB)                                       |

| 13                    | LATCH       | Latch, a low input results in gain change. A high input results in no gain change.                                           |

| 14, 16                | VOUT+       | Positive output.                                                                                                             |

| 15, 17                | VOUT-       | Negative output.                                                                                                             |

| 18, 21, 23, 24        | VPOS        | Positive power supply.                                                                                                       |

| 19                    | PWUP        | Power up pin. A logic high enables the part.                                                                                 |

| 20                    | PM          | High performance power mode (active high), Nominal power mode (low)                                                          |

<sup>1</sup> Exposed Paddle

## **DIGITAL INTERFACE OVERVIEW**

The ADL5201 DVGA has three digital control interface options:

- Parallel Control Interface

- Serial Peripheral Interface

- Gain Step Up/Down Interface

The digital control interface selection is made via 2 digital pins, MODE1 and MODE0, as shown in Table 5. There are two common digital control pins, PM and PWUP. PM selects between two power modes. PWUP is a power up pin. The gain code used is 6 bit binary.

Physical pins are shared between 3 interfaces resulting in as many as 3 different functions per digital pin (seeTable 4).

| MODE1 | MODE0 | Interface    |

|-------|-------|--------------|

| 0     | 0     | Parallel     |

| 0     | 1     | Serial (SPI) |

| 1     | 0     | Up/Down      |

| 1     | 1     | Up/Down      |

#### **Parallel Digital Interface**

The parallel digital interface uses 6 gain control bits and a latch pin. The latch pin controls whether the input data latch is transparent or latched. In transparent mode, gain changes as input gain control bits change. In latched mode, gain is determined by the latched gain setting and does not change with changing input gain control bits.

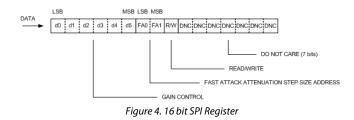

#### Serial Peripheral Interface (SPI)

The SPI uses 3 pins (SDIO, SCLK and  $\overline{CS}$ ). The SPI data register consists of 2 bytes: 6 gain control bits, 2 attenuation step size address bits, 1 read/write bit, and 7 do not care bits.

The SPI uses a bidirectional pin, SDIO, for writing to the SPI register and for reading from the SPI register. In order to write to the SPI register  $\overline{\text{CS}}$  needs to be pulled low and 16 clock pulses must be applied.

In order to read the SPI register value, the R/W bit needs to be set high,  $\overline{\text{CS}}$  needs to be pulled low, and the part clocked. Once the register has been read out the R/W bit needs to be set low and SPI put in write mode.

SPI fast attack mode is controlled by FA pin. A logic high on the FA pin results in an attenuation selected by FA1 and FA0 bits in the SPI register.

| Table 6. SPI 2-bit attenuation step size truth table |     |                |  |  |

|------------------------------------------------------|-----|----------------|--|--|

| FA1                                                  | FA0 | Step Size (dB) |  |  |

| 0                                                    | 0   | 2              |  |  |

| 0                                                    | 1   | 4              |  |  |

| 1                                                    | 0   | 8              |  |  |

| 1                                                    | 1   | 16             |  |  |

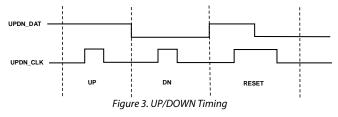

#### **UP/DOWN** Interface

The UP/DOWN interface uses two digital pins to control the gain. Gain is increased by a clock pulse on UPDN\_CLK (rising and falling edges) when UPDN\_DAT is high. Gain is decreased by a clock pulse on UPDN\_CLK when UPDN\_DAT is low. Reset is detected by a rising edge latching data having one polarity with the falling edge latching the opposite polarity. Reset results in minimum gain code 111111<sub>bin</sub>.

The step size is selectable by pins GS1 and GS0. The default step size is 0.5dB. The gain code count will rail at the top and bottom of the control range.

#### Table 7. Step size control truth table

| ruble // step size control truth tuble |     |                |  |  |  |

|----------------------------------------|-----|----------------|--|--|--|

| GS1                                    | GS0 | Step Size (dB) |  |  |  |

| 0                                      | 0   | 0.5            |  |  |  |

| 0                                      | 1   | 1              |  |  |  |

| 1                                      | 0   | 2              |  |  |  |

| 1                                      | 1   | 4              |  |  |  |

|                                        |     |                |  |  |  |

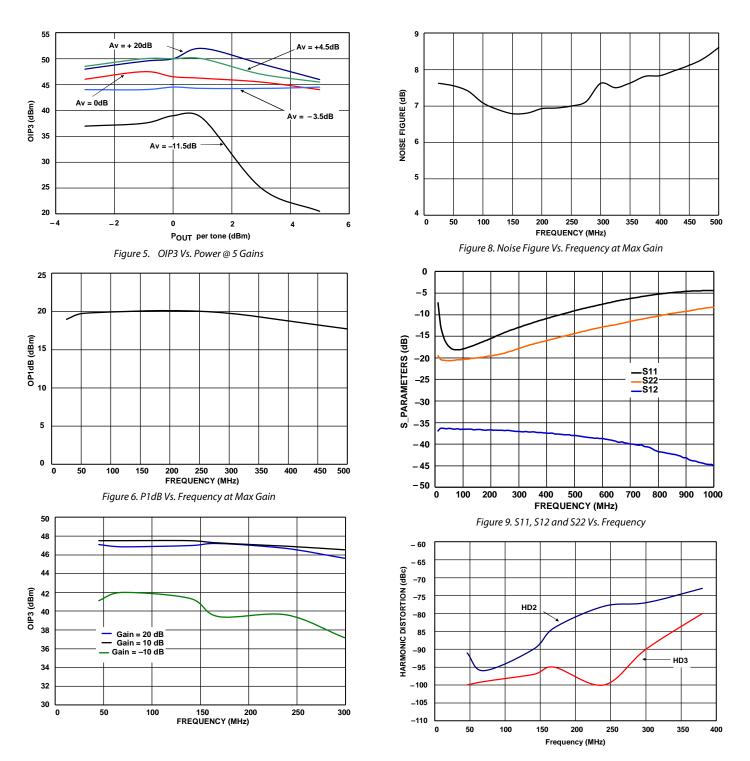

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 7. OIP3 Vs. Gain and Frequency

Figure 10. Harmonic Distortion Vs. Frequency 2Vp-p Out

ADL5201 查询"ADL5201"供应商

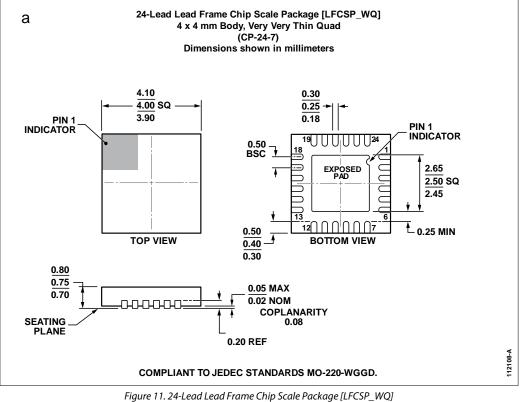

### **OUTLINE DIMENSIONS**

Figure 11. 24-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 4 mm × 4 mm Body, Very Thin Quad (CP-24-7) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                      | Temperature Range | Package Description           | Package Option |

|----------------------------|-------------------|-------------------------------|----------------|

| ADL5201XCPZ-R71            | –40°C to +85°C    | 24 Lead LFCSP_WQ, 7" Reel     | CP-24-7        |

| ADL5201XCPZ-WP1            | –40°C to +85°C    | 24 Lead LFCSP_WQ, Waffle Pack | CP-24-7        |

| ADL5201-EVALZ <sup>1</sup> | -40°C to +85°C    | Evaluation Board              |                |

$^{1}$  Z = RoHS Compliant Part

www.analog.com

Rev. PrD | Page 10 of 10