#### LM3503

# **Dual-Display Constant Current LED Driver with Analog Brightness Control**

## **General Description**

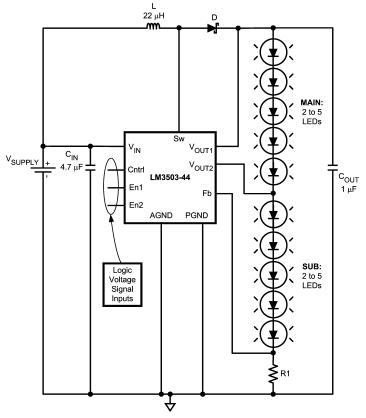

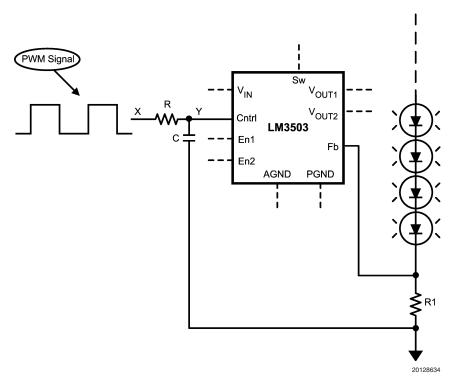

The LM3503 is a white LED driver for lighting applications. For dual display backlighting applications, the LM3503 provides a complete solution. The LM3503 contains two internal white LED current bypass FET (Field Effect Transistor) switches. The white LED current can be adjusted with a DC voltage from a digital to analog converter or RC filtered PWM (pulse-width-modulated) signal at the Cntrl pin.

With no external compensation, cycle-by-cycle current limit, output over-voltage protection, input under-voltage protection, and dynamic white LED current control capability, the LM3503 offers superior performance over other step-up white LED drivers.

#### **Features**

Drives up to 4, 6, 8 or 10 White LEDs for Dual Display Backlighting

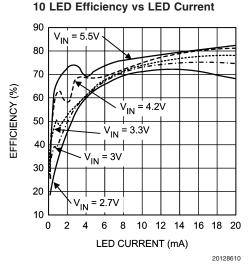

- >80% Peak Efficiency

- Output Voltage Protection Options: 16V, 25V, 35V & 44V

- Input Under-Voltage Protection

- Internal Soft Start Eliminates Inrush Current

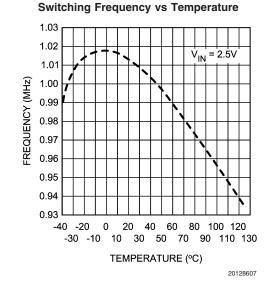

- 1 MHz Constant-Switching Frequency

- Analog Brightness Control

- Wide Input Voltage Range: 2.5V to 5.5V

- Low Profile Packages: <1 mm Height

- 10 Bump MicroSMD

- 16 Pin LLP

#### **Applications**

- Dual-Display Display Backlighting in Portable devices

- Cellular Phones and PDAs

#### **Typical Application**

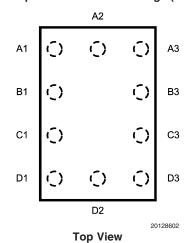

Connection Diagrams 事间"LM3503|TL-16"供放通SMD Package (TLP10)

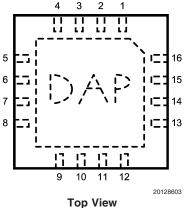

#### 16-Lead Thin Leadless Leadframe Package (SQA16A)

#### **Pin Descriptions/Functions**

| <del></del> | LM3503IT  | L <del>-16"供应</del><br>Name | Description                                                                                     |  |

|-------------|-----------|-----------------------------|-------------------------------------------------------------------------------------------------|--|

| A1          | 9         | Cntrl                       | White LED Current Control Connection                                                            |  |

| B1          | 7         | Fb                          | Feedback Voltage Connection                                                                     |  |

| C1          | 6         | V <sub>OUT2</sub>           | Drain Connections of the NMOS and PMOS Field Effect Transistor (FET) Switches                   |  |

|             |           | 0012                        | (Figure 1: N2 and P1). Connect 100nF at V <sub>OUT2</sub> node if V <sub>OUT2</sub> is not used |  |

| D1          | 4         | V <sub>OUT1</sub>           | Over-Voltage Protection (OVP) and Source Connection of the PMOS FET Switch                      |  |

|             |           | 3311                        | (Figure 1: P1)                                                                                  |  |

| D2          | 2 and 3   | Sw                          | Drain Connection of the Power NMOS Switch (Figure 1: N1)                                        |  |

| D3          | 15 and 16 | Pgnd                        | Power Ground Connection                                                                         |  |

| C3          | 14        | Agnd                        | Analog Ground Connection                                                                        |  |

| B3          | 13        | V <sub>IN</sub>             | nput Voltage Connection                                                                         |  |

| A3          | 12        | En2                         | NMOS FET Switch Control Connection                                                              |  |

| A2          | 10        | En1                         | PMOS FET Switch Control Connection                                                              |  |

|             | 1         | NC                          | No Connection                                                                                   |  |

|             | 5         | NC                          | No Connection                                                                                   |  |

|             | 8         | NC                          | No Connection                                                                                   |  |

|             | 11        | NC                          | No Connection                                                                                   |  |

|             | DAP       | DAP                         | Die Attach Pad (DAP), to be soldered to the printed circuit board's ground plane for            |  |

|             |           |                             | enhanced thermal dissipation.                                                                   |  |

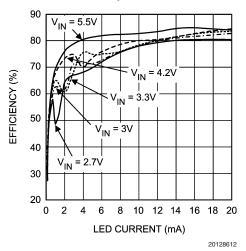

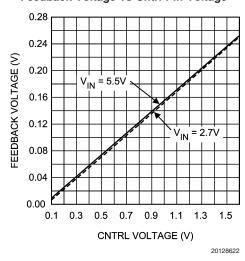

**Cntrl (Bump A1):** White LED current control pin. Use this pin to control the feedback voltage with an external DC voltage. The feedback voltage is given as  $V_{Fb} = (0.156) * (V_{Cntrl})$  for the control voltage range of  $0V \le V_{Cntrl} \le 3.5V$ .

Fb (Bump B1):Output voltage feedback connection.

$\rm V_{OUT2}$  (Bump C1):Drain connections of the internal PMOS and NMOS FET switches (*Figure 1*: P1 and N2). It is recommended to connect 100nF at  $\rm V_{OUT2}$  if  $\rm V_{OUT2}$  is not used for LM3503-35V & LM3503-44V versions.

#### V<sub>OUT1</sub>(Bump D1):

Source connection of the internal PMOS FET switch (*Figure 1*: P1) and OVP sensing node. The output capacitor must be connected as close to the device as possible, between the  $V_{OUT1}$  pin and ground plane. Also connect the Schottky diode as close as possible to the  $V_{OUT1}$  pin to minimize trace resistance and EMI radiation.

#### Sw (Bump D2):

Drain connection of the internal power NMOS FET switch (*Figure 1*: N1). Minimize the metal trace length and maximize the metal trace width connected to this pin to reduce EMI radiation and trace resistance.

**Pgnd (Bump D3):** Power ground pin. Connect directly to the ground plane.

**Agnd (Bump C3):**Analog ground pin. Connect the analog ground pin directly to the Pgnd pin.

$V_{IN}$  (Bump B3): Input voltage connection pin. The  $C_{IN}$  capacitor should be as close to the device as possible, between the  $V_{IN}$  pin and ground plane.

**En2 (Bump A3):** Enable pin for the internal NMOS FET switch (*Figure 1*: N2) during device operation. When  $V_{En2}$  is ≥ 1.4V, the internal NMOS FET switch turns off and the SUB display is turned on. The En2 pin has an internal pull down circuit, thus the internal NMOS FET switch is normally in the on state of operation with the SUB display turned off. When  $V_{En2}$  is ≤ 0.3V, the internal NMOS FET switch turns on and the SUB display is turned off. If both  $V_{En1}$  and  $V_{En2}$  are ≤ 0.3V the LM3503 will shutdown. If  $V_{OUT2}$  is not used, En2 must be floating or grounded and En1 used to enable the device.

**En1 (Bump A2):** Enable pin for the internal PMOS FET switch (*Figure 1*: P1) during device operation. When  $V_{En1}$  is ≤ 0.3V, the internal PMOS FET switch turns on and the MAIN display is turned off. When  $V_{En1}$  is ≥ 1.4V, the internal PMOS FET switch turns off and the MAIN display is turned on. If both  $V_{En1}$  and  $V_{En2}$  are ≤ 0.3V the LM3503 will shutdown. The En1 pin has an internal pull down circuit, thus the internal PMOS FET switch is normally in the on state of operation with the MAIN display turned off. If  $V_{OUT2}$  is not used, En2 must be grounded and En1 use to enable the device.

# See Ordering Information 事词"LM3503ITL-16"供应商

| Voltage | L-16~1 <del>八.沙百</del><br>Order Number | Package | Supplied As               |

|---------|----------------------------------------|---------|---------------------------|

| Option  |                                        | Marking |                           |

| 16      | LM3503ITL-16                           | SBHB    | 250 Units, Tape-and-Reel  |

| 16      | LM3503ITLX-16                          | SBHB    | 3000 Units, Tape-and-Reel |

| 16      | LM3503SQ-16                            | L00045B | 1000 Units, Tape-and-Reel |

| 16      | LM3503SQX-16                           | L00045B | 4500 Units, Tape-and-Reel |

| 25      | LM3503ITL-25                           | SBJB    | 250 Units, Tape-and-Reel  |

| 25      | LM3503ITLX-25                          | SBJB    | 3000 Units, Tape-and-Reel |

| 25      | LM3503SQ-25                            | L00046B | 1000 Units, Tape-and-Reel |

| 25      | LM3503SQX-25                           | L00046B | 4500 Units, Tape-and-Reel |

| 35      | LM3503ITL-35                           | SBKB    | 250 Units, Tape-and-Reel  |

| 35      | LM3503ITLX-35                          | SBKB    | 3000 Units, Tape-and-Reel |

| 35      | LM3503SQ-35                            | L00047B | 1000 Units, Tape-and-Reel |

| 35      | LM3503SQX-35                           | L00047B | 4500 Units, Tape-and-Reel |

| 44      | LM3503ITL-44                           | SDNB    | 250 Units, Tape-and-Reel  |

| 44      | LM3503ITLX-44                          | SDNB    | 3000 Units, Tape-and-Reel |

| 44      | LM3503SQ-44                            | L00053B | 1000 Units, Tape-and-Reel |

| 44      | LM3503SQX-44                           | L00053B | 4500 Units, Tape-and-Reel |

#### **Absolute Maximum Ratings** (Note 1)

If miary Act of pade specifications are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| V <sub>IN</sub> Pin          | -0.3V to +5.5V             |

|------------------------------|----------------------------|

| Sw Pin                       | -0.3V to +48V              |

| Fb Pin                       | -0.3V to +5.5V             |

| Cntrl Pin                    | -0.3V to +5.5V             |

| $V_{OUT_1}Pin$               | -0.3V to +48V              |

| V <sub>OUT2</sub> Pin        | –0.3V to $V_{\text{OUT1}}$ |

| En1                          | -0.3V to +5.5V             |

| En2                          | -0.3V to +5.5V             |

| Continuous Power Dissipation | Internally Limited         |

|                              |                            |

Maximum Junction Temperature

$(T_{J\text{-MAX}})$  +150°C Storage Temperature Range -65°C to +150°C

ESD Rating (Note 2)

Human Body Model: 2 kV

Machine Model: 200V

#### **Operating Conditions** (Notes 1, 6)

### Thermal Properties (Note 4)

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )

Micro SMD Package 65°C/W Leadless Leadframe Package 49°C/W

**Electrical Characteristics** (Notes 6, 7) Limits in standard typeface are for  $T_J = +25^{\circ}C$ . Limits in **bold typeface** apply over the full operating junction temperature range  $(-40^{\circ}C \le T_J \le +125^{\circ}C)$ . Unless otherwise specified,  $V_{IN} = 2.5V$ .

| Symbol                  | Parameter                               | Conditions                                      | Min | Тур  | Max  | Units |

|-------------------------|-----------------------------------------|-------------------------------------------------|-----|------|------|-------|

| V <sub>IN</sub>         | Input Voltage                           | Continuent                                      | 2.5 | - 71 | 5.5  | V     |

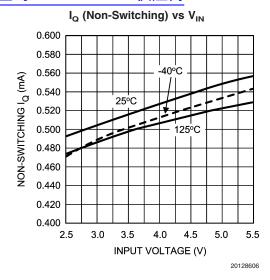

| I <sub>Q</sub>          | Non-Switching                           | Cntrl = 1.6V                                    |     | 0.5  | 1    | mA    |

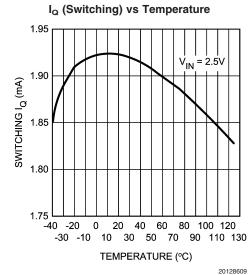

| Q                       | Switching                               | Fb = 0V, Sw Is Floating                         |     | 1.9  | 3    | mA    |

|                         | Shutdown                                | En1 = En2 = 0V                                  |     | 0.1  | 3    | μΑ    |

| $V_{Fb}$                | Feedback Voltage                        | Cntrl = 3.5V                                    | 0.5 | 0.55 | 0.6  | V     |

| I <sub>CL</sub>         | NMOS Power Switch                       | 16, Fb = 0V                                     | 250 | 400  | 650  |       |

|                         | Current Limit                           | 25, Fb = 0V                                     | 400 | 600  | 800  |       |

|                         |                                         | 35, Fb = 0V                                     | 450 | 750  | 1050 | mA    |

|                         |                                         | 44,FB = 0V                                      | 450 | 750  | 1050 |       |

| I <sub>Fb</sub>         | Feedback Pin Output                     | Fb = 0.25V, Cntrl = 1.6V                        |     | 64   | 500  | nA    |

|                         | Bias Current                            |                                                 |     | 04   | 300  | ПА    |

| F <sub>S</sub>          | Switching Frequency                     |                                                 | 0.8 | 1    | 1.2  | MHz   |

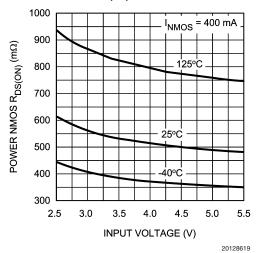

| R <sub>DS(ON)</sub>     | NMOS Power Switch                       | I <sub>Sw</sub> = 500 mA, (Note 8)              |     |      |      |       |

|                         | ON Resistance                           |                                                 |     | 0.55 | 1.1  | Ω     |

|                         | (Figure 1: N1)                          |                                                 |     |      |      |       |

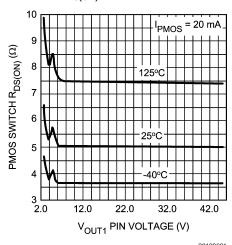

| R <sub>PDS(ON)</sub>    | PMOS ON Resistance                      | I <sub>PMOS</sub> = 20 mA, En1 = 0V, En2 = 1.5V |     |      |      |       |

|                         | Of V <sub>OUT1</sub> /V <sub>OUT2</sub> |                                                 |     | 5    | 10   | Ω     |

|                         | Switch (Figure 1: P1)                   |                                                 |     |      |      |       |

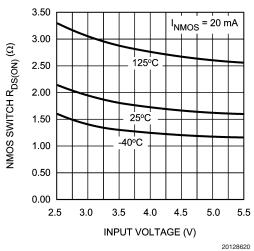

| R <sub>NDS(ON)</sub>    | NMOS ON Resistance                      | I <sub>NMOS</sub> = 20 mA, En1 = 1.5V, En2 = 0V |     |      |      |       |

|                         | Of V <sub>OUT2</sub> /Fb Switch         |                                                 |     | 2.5  | 5    | Ω     |

|                         | (Figure 1: N2)                          |                                                 |     |      |      |       |

| D <sub>MAX</sub>        | Maximum Duty Cycle                      | Fb = 0V                                         | 90  | 95   |      | %     |

| I <sub>CNTRL</sub>      | Cntrl Pin Bias Current                  | Cntrl = 2.5V                                    |     | 8    | 14   |       |

|                         | (Note 3)                                | Cntrl = 0V                                      |     | 0.1  |      | μΑ    |

| I <sub>Sw</sub>         | Sw Pin Leakage                          | Sw = 42V, En1 = En2 =0V                         |     | 0.01 | 5    |       |

|                         | Current (Note 3)                        |                                                 |     | 0.01 | 9    | μΑ    |

| I <sub>VOUT1(OFF)</sub> | V <sub>OUT1</sub> Pin Leakage           | V <sub>OUT1</sub> = 14V, En1 = En2 = 0V (16)    |     | 0.1  | 3    |       |

| 20(0.1)                 | Current (Note 3)                        | V <sub>OUT1</sub> = 23V, En1 = En2 = 0V (25)    |     | 0.1  | 3    | ^     |

|                         |                                         | V <sub>OUT1</sub> = 32V, En1 = En2 = 0V (35)    |     | 0.1  | 3    | μΑ    |

|                         |                                         | $V_{OUT1} = 42V, En1 = En2 = 0V (44)$           |     | 0.1  | 3    |       |

Electrical Characteristics (Notes 6, 7) Limits in standard typeface are for  $T_J = +25^{\circ}$ C. Limits in **bold** ip "此种结合图 如何,我可以可以证明的,我们就可以证明的。 Unless otherwise specified,  $V_{IN} = 2.5$ V. (Continued)

| Symbol                 | Parameter                                                                                                       | Conditions                                     | Min  | Тур  | Max  | Units |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|------|------|-------|--|

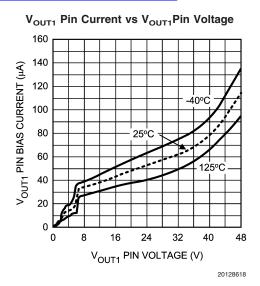

| I <sub>VOUT1(ON)</sub> | V <sub>OUT1</sub> Pin Bias                                                                                      | V <sub>OUT1</sub> = 14V, En1 = En1 = 1.5V (16) |      | 40   | 80   |       |  |

| 5511(ON)               | Current (Note 3)                                                                                                | $V_{OUT1} = 23V, En1 = En2 = 1.5V (25)$        |      | 50   | 100  |       |  |

|                        |                                                                                                                 | $V_{OUT1} = 32V, En1 = En2 = 1.5V (35)$        |      | 50   | 100  | μΑ    |  |

|                        |                                                                                                                 | V <sub>OUT1</sub> = 42V, En1 = En2 = 1.5V (44) |      | 85   | 140  |       |  |

| I <sub>VOUT2</sub>     | V <sub>OUT2</sub> Pin Leakage Fb = En1 = En2 = 0V, V <sub>OUT2</sub> = V <sub>OUT1</sub> = 42V Current (Note 3) |                                                |      | 0.1  | 3    | μΑ    |  |

| UVP                    | Under-Voltage                                                                                                   | On Threshold                                   |      | 2.4  | 2.5  | V     |  |

|                        | Protection                                                                                                      | Off Threshold                                  | 2.2  | 2.3  |      |       |  |

| OVP                    | Over-Voltage                                                                                                    | On Threshold (16)                              | 14.5 | 15.5 | 16.5 |       |  |

|                        | Protection (Note 5)                                                                                             | Off Threshold (16)                             | 14.0 | 15   | 16.0 |       |  |

|                        |                                                                                                                 | On Threshold (25)                              | 22.5 | 24   | 25.5 |       |  |

|                        |                                                                                                                 | Off Threshold (25)                             | 21.5 | 23   | 24.5 | V     |  |

|                        |                                                                                                                 | On Threshold (35)                              | 32.0 | 34   | 35.0 | V     |  |

|                        |                                                                                                                 | Off Threshold (35)                             | 31.0 | 33   | 34.0 |       |  |

|                        |                                                                                                                 | On Threshold (44)                              | 40.5 | 42   | 43.5 |       |  |

|                        |                                                                                                                 | Off Threshold (44)                             | 39.0 | 41   | 42.0 |       |  |

| V <sub>En1</sub>       | PMOS FET Switch and Device Enabling                                                                             | Off Threshold                                  |      | 0.8  | 0.3  | V     |  |

|                        | Threshold (Figure 1: P1)                                                                                        | On Threshold                                   | 1.4  | 0.8  |      | V     |  |

| V <sub>En2</sub>       | NMOS FET Switch and Device Enabling                                                                             | Off Threshold                                  |      | 0.8  | 0.3  | V     |  |

|                        | Threshold (Figure 1: N2)                                                                                        | On Threshold                                   | 1.4  | 0.8  |      | V     |  |

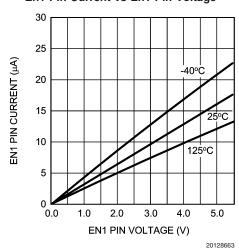

| I <sub>En1</sub>       | En1 Pin Bias Current                                                                                            | En1 = 2.5V                                     |      | 7    | 14   |       |  |

|                        | (Note 3)                                                                                                        | En1 = 0V                                       |      | 0.1  |      | μΑ    |  |

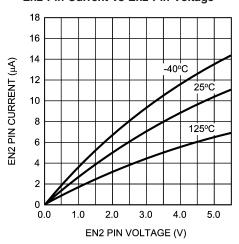

| I <sub>En2</sub>       | En2 Pin Bias Current                                                                                            | En2 = 2.5V                                     |      | 7    | 14   | 1 .   |  |

|                        | (Note 3)                                                                                                        | En2 = 0V                                       | 0    |      |      | μA    |  |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical characteristic specifications do not apply when operating the device outside of its rated operating conditions.

Note 2: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 3: Current flows into the pin.

Note 4: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(MAX)}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . See Thermal Properties for the thermal resistance. The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature. For more information on this topic, please refer to Application Note 1187(An1187): Leadless Leadframe Package (LLP) and Application Note 1112(AN1112) for microSMD chip scale package.

Note 5: The on threshold indicates that the LM3503 is no longer switching or regulating LED current, while the off threshold indicates normal operation.

Note 6: All voltages are with respect to the potential at the GND pin.

Note 7: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

Note 8: NMOS Power On Resistance measured at  $I_{SW}$ = 250mA for sixteen voltage version.

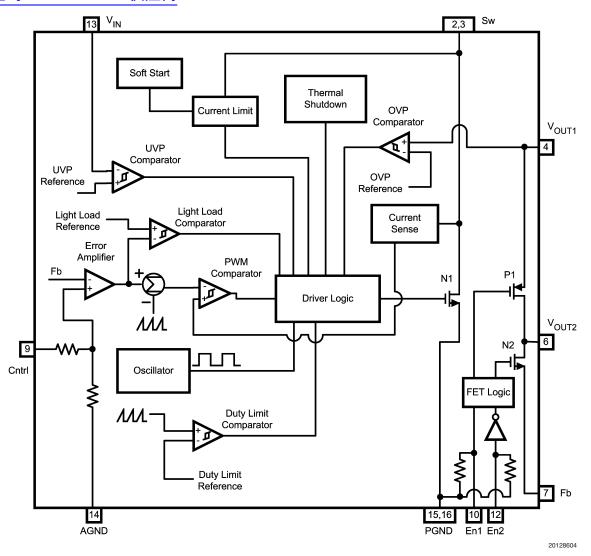

Block Diagram 查询"LM3503ITL-16"供应商

FIGURE 1. Block Diagram

#### **Detailed Description of Operation**

间"LTM-35/03-03-Lttilige"共成运动chronous current mode pulsewidth-modulation (PWM) control scheme to regulate the feedback voltage over specified load conditions. The DC/DC converter behaves as a controlled current source for white LED applications. The operation can best be understood by referring to the block diagram in Figure 1 for the following operational explanation. At the start of each cycle, the oscillator sets the driver logic and turns on the internal NMOS power device, N1, conducting current through the inductor and reverse biasing the external diode. The white LED current is supplied by the output capacitor when the internal NMOS power device, N1, is turned on. The sum of the error amplifier's output voltage and an internal voltage ramp are compared with the sensed power NMOS, N1, switch voltage. Once these voltages are equal, the PWM comparator will then reset the driver logic, thus turning off the internal NMOS power device, N1, and forward biasing the external diode. The inductor current then flows through the diode to the white LED load and output capacitor. The inductor current recharges the output capacitor and supplies the current for the white LED load. The oscillator then sets the driver logic again repeating the process. The output voltage of the error amplifier controls the current through the inductor. This voltage will increase for larger loads and decrease for smaller loads limiting the peak current in the inductor and minimizing EMI radiation. The duty limit comparator is always operational, it prevents the internal NMOS power switch, N1, from being on for more than one oscillator cycle and conducting large amounts of current. The light load comparator allows the LM3503 to properly regulate light/small white LED load currents, where regulation becomes difficult for the LM3503's primary control loop. Under light load conditions, the LM3503 will enter into a pulse skipping pulse-frequencymode (PFM) of operation where the operational frequency will vary with the load. As a result of PFM mode operation, the output voltage ripple magnitude will significantly in-

The LM3503 has two control pins, En1 and En2, used for selecting which segment of a single white LED string net-

work is active for dual display applications. En1 controls the main display (MAIN) segment of the single string white LED network between pins  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$ . En2 controls the sub display (SUB) segment of the single string white LED network between the  $V_{\rm OUT2}$  and Fb. If both  $V_{\rm En1}$  and  $V_{\rm En2}$  are  $\leq$  0.3V, the LM3503 will shutdown, for further description of the En1 and En2 operation, see Figure 3. During shutdown the output capacitor discharges through the string of white LEDs and feedback resistor to ground. The LED current can be dynamically controlled by a DC voltage on the Cntrl pin. When  $V_{\rm Cntrl}$  = 0V the white LED current may not be equal to zero because of offsets within the LM3503 internal circuitry. To guarantee zero white LED current the LM3503 must be in shutdown mode operation.

The LM3503 has dedicated protection circuitry active during normal operation to protect the integrated circuit (IC) and external components. Soft start circuitry is present in the LM3503 to allow for slowly increasing the current limit to its steady-state value to prevent undesired high inrush current during start up. Thermal shutdown circuitry turns off the internal NMOS power device, N1, when the internal semiconductor junction temperature reaches excessive levels. The LM3503 has a under-voltage protection (UVP) comparator that disables the internal NMOS power device when battery voltages are too low, thus preventing an on state where the internal NMOS power device conducts large amounts of current. The over-voltage protection (OVP) comparator prevents the output voltage from increasing beyond the protection limit when the white LED string network is removed or if there is a white LED failure. OVP allows for the use of low profile ceramic capacitors at the output. The current through the internal NMOS power device, N1, is monitored to prevent peak inductor currents from damaging the IC. If during a cycle (cycle=1/switching frequency) the peak inductor current exceeds the current limit for the LM3503, the internal NMOS power device will be turned off for the remaining duration of that cycle.

| En1  | En2  | Result (See Figure 1 and Figure 2)                            |   |

|------|------|---------------------------------------------------------------|---|

| 0.3V | 0.3V | [P1→OFF N2→OFF N1→OFF] or [MAIN→OFF SUB→OFF N1→OFF]           | х |

| 1.4V | 0.3V | [P1→OFF N2→ON N1→Switching] or [MAIN→ON SUB→OFF N1→Switching] |   |

| 0.3V | 1.4V | [P1→ON N2→OFF N1→Switching] or [MAIN→OFF SUB→ON N1→Switching] |   |

| 1.4V | 1.4V | [P1→OFF N2→OFF N1→Switching] or [MAIN→ON SUB→ON N1→Switching] |   |

20128605

FIGURE 2. Operational Characteristics Table

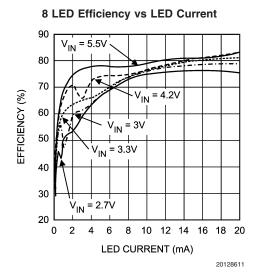

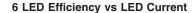

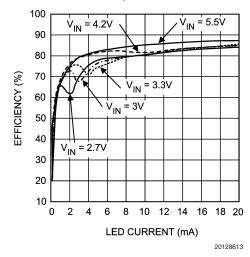

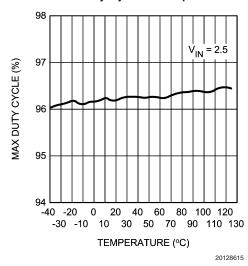

## Typical Performance Characteristics (See Typical Application Circuit: L=DO1608C-223 and D=查铂性区的设计上记识内容 [(V<sub>OUT</sub> - V<sub>Fb</sub>) \* I<sub>OUT</sub>] / [V<sub>IN</sub> \* I<sub>IN</sub>]. T<sub>A</sub> = +25°C, unless otherwise stated.)

$\rm I_{\rm Q}$  (Switching) vs  $\rm V_{\rm IN}$

4.5

4.0

INPUT VOLTAGE (V)

5.0

5.5

20128608

3.5

3.0

2.5

#### **Cntrl Pin Current vs Cntrl Pin Voltage**

#### En1 Pin Current vs En1 Pin Voltage

#### 4 LED Efficiency vs LED Current

#### Maximum Duty Cycle vs Temperature

En2 Pin Current vs En2 Pin Voltage

20128664

## Typical Performance Characteristics (See Typical Application Circuit: L=DO1608C-223 and D=查询性 NB503111=16。供应商 [(V<sub>OUT</sub> - V<sub>Fb</sub> ) \* I<sub>OUT</sub>] / [V<sub>IN</sub> \* I<sub>IN</sub>]. T<sub>A</sub> = +25°C, unless otherwise stated.) (Continued)

#### NMOS $R_{DS(ON)}$ (Figure 1: N2) vs $V_{IN}$

#### Feedback Voltage vs Cntrl Pin Voltage

#### Power NMOS R<sub>DS(ON)</sub> (Figure 1: N1) vs V<sub>IN</sub>

#### PMOS R<sub>DS(ON)</sub> (Figure 1: P1) vs V<sub>IN</sub>

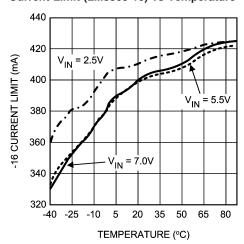

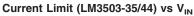

#### Current Limit (LM3503-16) vs Temperature

2012865

Typical Performance Characteristics (See Typical Application Circuit: L=DO1608C-223 and 頁"LD♥3503|3T Effloch供:应商 OUT/ PIN = [(VOUT - VFb ) \* IOUT] / [VIN \* IIN]. TA = +25°C, unless otherwise stated.) (Continued)

# 20128659

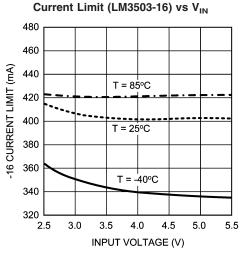

#### Current Limit (LM3503-25) vs VIN

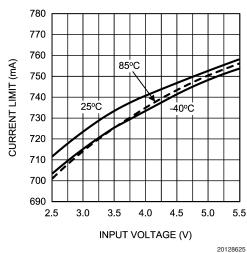

#### Current Limit (LM3503-25) vs Temperature

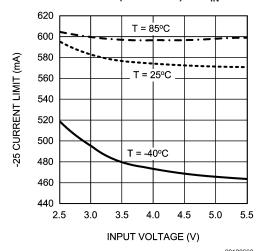

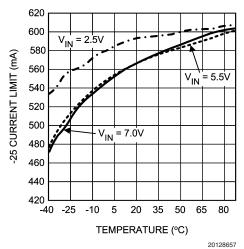

#### Current Limit (LM3503-35/44) vs Temperature

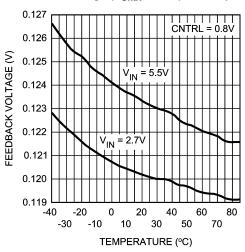

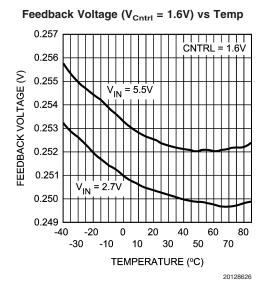

Feedback Voltage (V<sub>Cntrl</sub> = 0.8V) vs Temp

20128624

##

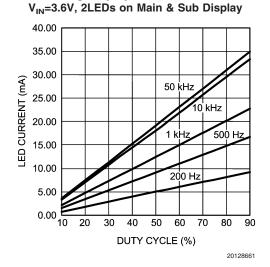

**Dimming Duty Cycle vs. LED Current**

#### **Application Information**

## LM3503ITL-16"供应商

#### WHITE LED CURRENT SETTING

The white LED current is controlled by a DC voltage at the Cntrl pin.

The relationship between the Cntrl pin voltage and Fb pin voltage can be computed with the following:

$$V_{FB} = (0.156) * (V_{Cntrl})$$

2012863

$V_{Cntrl}$ : Cntrl Pin Voltage. Voltage Range:  $0V \le V_{Cntrl} \le 3.5V$ .

V<sub>Fb</sub>: Feedback Pin Voltage.

#### LED CURRENT

The LED current is set using the following equation:

$$I_{LED} = \frac{V_{Fb}}{R1}$$

To determine the maximum output current capability of the device, it is best to estimate using equations on page 16 and the minimum peak current limit of the device (see electrical table). Note the current capability will be higher with less LEDs in the application.

#### WHITE LED DIMMING

FIGURE 3. If V<sub>OUT2</sub> is not used, En2 must be grounded

Aside from varying the DC voltage at the Cntrl pin, white LED dimming can be accomplished through the RC filtering of a PWM signal. The PWM signal frequency should be at least a decade greater than the RC filter bandwidth. *Figure 3* is how the LM3503 should be wired for PWM filtered white LED dimming functionality. When using PWM dimming, it is recommended to add 1-2ms delay between the Cntrl signal and the main Enable sginal (En1) to allow time for the output to discharge. This will prevent potential flickering especially if the Sub display is compose of 2 LEDs or less.

The equations below are guidelines for choosing the correct RC filter values in relation to the PWM signal frequency.

Equation #1:

$$F_{RC} = \frac{1}{2 * \pi * R * C}$$

Equation #2:

$$F_{PWM} > 10 * F_{RC}$$

F<sub>BC</sub>: RC Filter Bandwidth Cutoff Frequency.

F<sub>PWM</sub>: PWM Signal Frequency.R: Chosen Filter Resistor.C: Chosen Filter Capacitor.

For example, using the above equations to determine the proper RC values. Assume the following condition:  $V_{IN}=3.6V$ , C=0.01 $\mu$ F and F $_{PWM}=500$ Hz, then F $_{RC}=50$ Hz by relation to equation 2. By rearranging equation 1 to solve for R; R = 318.5K ohms (standard value, R = 316K).

#

The results are based on the 2LEDs on Main display and 2LEDs on Sub display

| Duty | 200Hz         | 500Hz        | 1KHz         | 10KHz        | 50KHz        | 100kHz       |

|------|---------------|--------------|--------------|--------------|--------------|--------------|

| (%)  | R = 787k ohms | R =316k ohms | R = 158kohms | R=16.2k ohms | R=3.16k ohms | R=1.62k ohms |

| 10   | 0.78mA        | 1.59mA       | 2.23mA       | 3.42mA       | 3.58mA       | 3.61mA       |

| 20   | 1.85mA        | 3.46mA       | 4.78mA       | 7.09mA       | 7.41mA       | 7.48mA       |

| 30   | 2.88mA        | 5.35mA       | 7.33mA       | 10.77mA      | 11.25mA      | 11.34mA      |

| 40   | 3.96mA        | 7.24mA       | 9.88mA       | 14.48mA      | 15.12mA      | 15.24mA      |

| 50   | 5.05mA        | 9.12mA       | 12.45mA      | 19.1mA       | 19.06mA      | 19.16mA      |

| 60   | 6.08mA        | 11.03mA      | 15.03mA      | 21.86mA      | 22.98mA      | 23.10mA      |

| 70   | 7.13mA        | 12.94mA      | 17.61mA      | 25.71mA      | 26.9mA       | 27.05mA      |

| 80   | 8.17mA        | 14.83mA      | 20.20mA      | 29.53mA      | 30.83mA      | 31.00mA      |

| 90   | 9.24mA        | 16.73mA      | 22.79mA      | 33.32mA      | 34.78mA      | 35.00mA      |

|      |               |              |              |              |              |              |

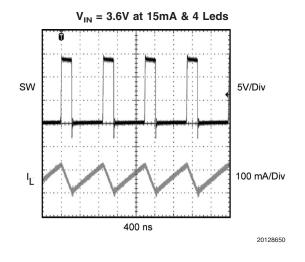

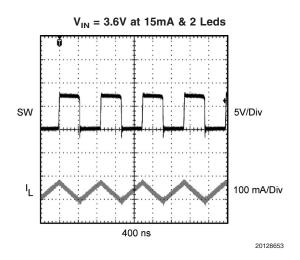

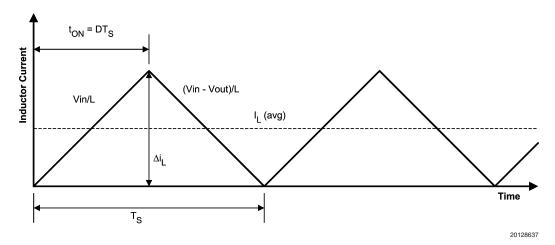

FIGURE 4. Inductor Current Waveform

#### CONTINUOUS AND DISCONTINUOUS MODES OF **OPERATION**

Since the LM3503 is a constant frequency pulse-widthmodulated step-up regulator, care must be taken to make sure the maximum duty cycle specification is not violated. The duty cycle equation depends on which mode of operation the LM3503 is in. The two operational modes of the LM3503 are continuous conduction mode (CCM) and discontinuous conduction mode (DCM). Continuous conduction mode refers to the mode of operation where during the switching cycle, the inductor current never goes to and stays at zero for any significant amount of time during the switching cycle. Discontinuous conduction mode refers to the mode of operation where during the switching cycle, the inductor current goes to and stays at zero for a significant amount of time during the switching cycle. Figure 4 illustrates the threshold between CCM and DCM operation. In Figure 4 the inductor current is right on the CCM/DCM operational threshold. Using this as a reference, a factor can be introduced to calculate when a particular application is in CCM or DCM operation. R is a CCM/DCM factor we can use to compute which mode of operation a particular application is in. If R is  $\geq$  1, then the application is operating in CCM. Conversely, if R is < 1, the application is operating in DCM. The R factor inequalities are a result of the components that make up the R factor. From Figure 4, the R factor is equal to the average inductor current, IL(avg), divided by half the inductor ripple current,  $\Delta i_1$ . Using Figure 4, the following equation can be used to compute R factor:

$$R = \frac{2 * I_L (avg)}{\Delta i_L}$$

$$I_{L} (avg) = \frac{[I_{OUT}]}{[(1-D) * Eff]}$$

$$\Delta i_L = \frac{[V_{IN} * D]}{[L * Fs]}$$

$$R = \frac{[2 * I_{OUT} * L * Fs * (V_{OUT})^2]}{[(V_{IN})^2 * Eff * (V_{OUT} - V_{IN})]}$$

$V_{IN}$ : Input Voltage. Output Voltage.  $V_{OUT}$ :

Eff: Efficiency of the LM3503.

## Application Information (Continued) 询"LM3503订品16"供应商。

I<sub>OUT</sub>: White LED Current/Load Current.L: Inductance Magnitude/Inductor Value.

D: Duty Cycle for CCM operation.  $\Delta i_L$ : Inductor Ripple Current.

I<sub>L</sub>(avg): Average Inductor Current.

For CCM operation, the duty cycle can be computed with:

$$D = \frac{t_{ON}}{T_{S}}$$

2012864

$$D = \frac{[V_{OUT} - V_{IN}]}{[V_{OUT}]}$$

2012864

D: Duty Cycle for CCM Operation.

$V_{OUT}$ : Output Voltage.  $V_{IN}$ : Input Voltage.

For DCM operation, the duty cycle can be computed with:

$$D = \frac{t_{ON}}{T_{S}}$$

$$D = \sqrt{\frac{[2 * I_{OUT} * L * (V_{OUT} - V_{IN}) * Fs]}{[(V_{IN})^2 * Eff]}}$$

20128645

D: Duty Cycle for DCM Operation.

$V_{OUT}$ : Output Voltage.  $V_{IN}$ : Input Voltage.

IOUT: White LED Current/Load Current.

Fs: Switching Frequency.

L: Inductor Value/Inductance Magnitude.

#### INDUCTOR SELECTION

In order to maintain inductance, an inductor used with the LM3503 should have a saturation current rating larger than the peak inductor current of the particular application. Inductors with low DCR values contribute decreased power losses and increased efficiency. The peak inductor current can be computed for both modes of operation: CCM and DCM.

The cycle-by-cycle peak inductor current for CCM operation can be computed with:

$$I_{\text{Peak}} \approx I_{\text{L}} \text{ (avg)} + \frac{\Delta i_{\text{L}}}{2}$$

$$I_{Peak} pprox rac{[I_{OUT}]}{[(1 - D) * Eff]} + rac{[V_{IN} * D]}{[2 * L * Fs]}$$

V<sub>IN</sub>: Input Voltage.

Eff: Efficiency of the LM3503. Fs: Switching Frequency.

I<sub>OUT</sub>: White LED Current/Load Current.L: Inductance Magnitude/Inductor Value.

D: Duty Cycle for CCM Operation.

$I_{PEAK}$ : Peak Inductor Current.  $\Delta i_L$ : Inductor Ripple Current.  $I_L(avg)$ : Average Inductor Current.

The cycle-by-cycle peak inductor current for DCM operation can be computed with:

$$I_{\text{Peak}} \approx \frac{[V_{\text{IN}} * D]}{[L * Fs]}$$

V<sub>IN</sub>: Input Voltage.

Fs: Switching Frequency.

L: Inductance Magnitude/Inductor Value.

D: Duty Cycle for DCM Operation.

I<sub>PEAK</sub>: Peak Inductor Current.

The minimum inductance magnitude/inductor value for the LM3503 can be calculated using the following, which is only valid when the duty cycle is > 0.5:

$$L > \frac{[V_{IN} * R_{DS(ON)} * ((D/D') - 1)]}{[1.562 * Fs]}$$

20128649

D: Duty Cycle.

D': 1-D.

R<sub>DS(ON)</sub>: NMOS Power Switch ON Resistance.

Fs: Switching Frequency.

$V_{\text{IN}}$ : Input Voltage.

L: Inductance Magnitude/Inductor Value.

This equation gives the value required to prevent subharmonic oscillations. The result of this equation and the inductor ripple currents should be accounted for when choosing an inductor value.

Some recommended Inductor manufactures included but are not limited to:

| Coilcraft | DO1608C-223 | www.coilcraft.com |

|-----------|-------------|-------------------|

|           | DT1608C-223 | www.concrant.com  |

#### **CAPACITOR SELECTION**

Multilayer ceramic capacitors are the best choice for use with the LM3503. Multilayer ceramic capacitors have the lowest equivalent series resistance (ESR). Applied voltage or DC bias, temperature, dielectric material type (X7R, X5R, Y5V, etc), and manufacturer component tolerance have an affect on the true or effective capacitance of a ceramic capacitor. Be aware of how your application will affect a particular ceramic capacitor by analyzing the aforementioned factors of your application. Before selecting a capacitor always consult the capacitor manufacturer's data curves to verify the effective or true capacitance of the capacitor in your application.

#### **INPUT CAPACITOR SELECTION**

The input capacitor serves as an energy reservoir for the inductor. In addition to acting as an energy reservoir for the inductor the input capacitor is necessary for the reduction in input voltage ripple and noise experienced by the LM3503. The reduction in input voltage ripple and noise helps ensure

### **Application Information** (Continued)

the \$\frac{13}{3503}\$ \frac{15}{3503}\$ \frac{15}{3503}\$

#### **OUTPUT CAPACITOR SELECTION**

The output capacitor serves as an energy reservoir for the white LED load when the internal power FET switch (*Figure 1*: N1) is on or conducting current. The requirements for the output capacitor must include worst case operation such as when the load opens up and the LM3503 operates in overvoltage protection (OVP) mode operation. A minimum capacitance of 0.5  $\mu$ F is required to ensure normal operation. Consult the capacitor manufacturer's data curves to verify whether the minimum capacitance requirement is going to be achieved for a particular application.

Some recommended capacitor manufacturers included but are not limited to:

| Taiyo-<br>Yuden | GMK212BJ105MD<br>(0805/35V)                                                             | www.t-yuden.com |

|-----------------|-----------------------------------------------------------------------------------------|-----------------|

| muRata          | GRM40-035X7R105K<br>(0805/50V)                                                          | www.murata.com  |

| TDK             | C3216X7R1H105KT<br>(1206/50V)<br>C3216X7R1C475K<br>(1206/16V)                           | www.tdktca.com  |

| AVX             | 08053D105MAT<br>(0805/25V)<br>08056D475KAT<br>(0805/6.3V)<br>1206ZD475MAT<br>(1206/10V) | www.avxcorp.com |

#### **DIODE SELECTION**

To maintain high efficiency it is recommended that the average current rating ( $\rm I_F$  or  $\rm I_O$ ) of the selected diode should be larger than the peak inductor current ( $\rm I_{Lpeak}$ ). At the minimum the average current rating of the diode should be larger than the maximum LED current. To maintain diode integrity the peak repetitive forward current ( $\rm I_{FRM}$ ) must be greater than or equal to the peak inductor current ( $\rm I_{Lpeak}$ ). Diodes with low forward voltage ratings ( $\rm V_F$ ) and low junction capacitance magnitudes ( $\rm C_J$  or  $\rm C_T$  or  $\rm C_D$ ) are conducive to high efficiency. The chosen diode must have a reverse breakdown voltage rating ( $\rm V_R$  and/or  $\rm V_{RRM}$ ) that is larger than the output voltage ( $\rm V_{OUT}$ ). No matter what type of diode is chosen, Schottky or not, certain selection criteria must be followed:

- 1.  $V_R$  and  $V_{RRM} > V_{OUT}$

- 2.  $I_F$  or  $I_O \ge I_{LOAD}$  or  $I_{OUT}$

- 3. I<sub>FRM</sub> ≥ I<sub>Lpeak</sub>

Some recommended diode manufacturers included but are not limited to:

| Vishay        | SS12(1A/20V) | www.vishay.com      |

|---------------|--------------|---------------------|

|               | SS14(1A/40V) |                     |

|               | SS16(1A/60V) |                     |

| On            | MBRM120E     | www.onsemi.com      |

| Semiconductor | (1A/20V)     |                     |

|               | MBRS1540T3   |                     |

|               | (1.5A/40V)   |                     |

|               | MBR240LT     |                     |

|               | (2A/40V)     |                     |

| Central       | CMSH1-40M    | www.centralsemi.com |

| Semiconductor | (1A/40V)     |                     |

#### SHUTDOWN AND START-UP

On startup, the LM3503 contains special circuitry that limits the peak inductor current which prevents large current spikes from loading the battery or power supply. The LM3503 is shutdown when both En1 and En2 signals are less than 0.3V. During shutdown the output voltage is a diode drop below the supply voltage. When shutdown, the softstart is reset to prevent inrush current at the next startup.

#### THERMAL SHUTDOWN

The LM3503 stops regulating when the internal semiconductor junction temperature reaches approximately 140°C. The internal thermal shutdown has approximately 20°C of hysteresis which results in the LM3503 turning back on when the internal semiconductor junction temperature reaches 120°C. When the thermal shutdown temperature is reached, the softstart is reset to prevent inrush current when the die temperature cools.

#### **UNDER VOLTAGE PROTECTION**

The LM3503 contains protection circuitry to prevent operation for low input supply voltages. When Vin drops below 2.3V, typically, the LM3503 will no longer regulate. In this mode, the output voltage will be one diode drop below Vin and the softstart will be reset. When Vin increases above 2.4V, typically, the device will begin regulating again.

#### **OVER VOLTAGE PROTECTION**

The LM3503 contains dedicated ciruitry for monitoring the output voltage. In the event that the LED network is disconnected from the LM3503, the output voltage will increase and be limited to 15.5V(typ.) for the 16V version, 24V(typ.) for the 25V version, 34V(typ.) for 35V version and 42V(typ.) for the 44V version. (see electrical table for more details). In the event that the network is reconnected regulation will resume at the appropriate output voltage.

#### LAYOUT CONSIDERATIONS

All components, except for the white LEDs, must be placed as close as possible to the LM3503. The die attach pad (DAP) must be soldered to the ground plane.

The input bypass capacitor  $C_{\rm IN}$ , as shown in the Typical Application Circuit,, must be placed close to the IC and connect between the  $V_{\rm IN}$  and Pgnd pins. This will reduce copper trace resistance which effects input voltage ripple of the IC. For additional input voltage filtering, a 100 nF bypass capacitor can be placed in parallel with  $C_{\rm IN}$  to shunt any high frequency noise to ground. The output capacitor,  $C_{\rm OUT}$ , must be placed close to the IC and be connected between the  $V_{\rm OUT1}$  and Pgnd pins. Any copper trace connections for the  $C_{\rm OUT}$  capacitor can increase the series resistance, which

| 1 | c | 7 |

|---|---|---|

| 1 | C | 3 |

| ı | L | ī |

| 1 | c | 7 |

|   | Z | Ì |

Application Information (Continued)

[ Application Information (Continued) ] [ Application (Conti rent setting resistor, R1, should be kept close to the Fb pin to minimize copper trace connections that can inject noise into the system. The ground connection for the current setting resistor network should connect directly to the Pgnd pin. The

Agnd pin should be tied directly to the Pgnd pin. Trace connections made to the inductor should be minimized to reduce power dissipation and increase overall efficiency while reducing EMI radiation. For more details regarding layout guidelines for switching regulators, refer to Applications Note AN-1149.

## Physical Dimensions inches (millimeters) unless otherwise noted 查询"LM3503ITL316"供应商 DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY В LAND PATTERN RECOMMENDATION C TOP SIDE COATING--ВИМР 1 0.5 BUMP A1 CORNER SILICON-|0.5 10X Ø 0.335 — + 0.005\$ C A\$ B\$ TLP10XXX (Rev D) TLP10: 10-Bump Thin Micro SMD Package X1 = 1.958 mm X2 = 2.135 mmX3 = 0.6 mm**NS Package Number TLP10** - (3.8 TYP) -ф (12X 0.5) $\dot{\Box}$ ( 2.6) ф DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN () FOR REFERENCE ONLY (0.1) (16X 0.6) RECOMMENDED LAND PATTERN **C** -□2.6±0.1 -0.8 MAX -PIN 1 ID-PIN 1 INDEX AREA (45° X0.25) <u>U U;U U</u> ╛ 16X 0.4±0.1 <u>n nih h</u> В A 4 ± 0 . 1 -SQA16A (Rev A) 16-Lead Thin Leadless Leadframe Package **NS Package Number SQA16A**

| Comtrol               |

|-----------------------|

|                       |

| <b>Brightness</b>     |

| with Analog           |

| with                  |

| <b>LED Driver</b>     |

| ED Dri                |

| Current               |

| Constant              |

| <b>Il-Display</b>     |

| $\boldsymbol{\omega}$ |

询"LM3503ITL-16"供应商

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

**Notes**

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

**National Semiconductor** Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer **Support Center** Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560