# LD120/121A 4½ Digit A/D Converter Set

# 查询"LD120"供应商

- 0.005% ±1 Count Accuracy

- ±200.0 mV and ±2.000 V Ranges

- Auto Zero

- Auto-Polarity

- Over and Under Range Outputs

#### BENEFITS

- High System Performance

- Single Resistor Programming

- · Nulls Out Offsets

- Single Reference

- · Easily Interfaced

#### **APPLICATIONS**

- High Accuracy Digital Voltmeters and Panel Meters

- Digital Scales and Thermometer

- μP Data Acquisition Systems

- Scientific Instrumentation

#### DESCRIPTION

The LD120 and LD121A form a precision 4 1/2 digit A/D converter system for use in display and microprocessor based data acquisition applications. Based on Siliconix's "Quantized Feedback" technique, intrinsic features include auto-polarity, auto-zero, and ratiometric operation. Except for a stable reference, no critical components are required to achieve rated performance. The technique used offers superior linearity, normal mode rejection, and stability due to the simultaneous integration of the unknown input and the reference voltages. Unlike other conversion techniques, the integrator output voltage never represents more than 100 counts. Thus, critical, high resolution performance is not required of either the integrator or the comparator.

The LD120 analog processor is fabricated with a unique PMOS/Bipolar process. It contains all the necessary amplifiers, MOSFET switches, and switch driver circuits for the system. The reference voltage input is fully buffered in

LD120 to eliminate the reference switch resistance as a source of error. All the amplifiers are internally compensated. The LD120 directly interfaces the LD121A digital processor with no additional active components required.

The LD121A synchronous processor contains all the digital circuitry for the quantized feedback system. Device outputs supply two overrange signals, underrange, sign and 4½ digits of multiplexed BCD data. (All outputs are TTL compatible). Overrange is also indicated by blinking digit strobes above 20,000 counts. An input is provided to inhibit this feature at user option. Microprocessor controlled operation is simplified by a start conversion input that allows conversion-on-command.

Both devices are supplied in space saving 300 mil dual-inline plastic packages. The LD120 has 16 pins and the LD121A has 18 pins.

#### PIN CONFIGURATION FUNCTIONAL BLOCK DIAGRAM **Dual-In-Line Package** 16 V+ BUFF IN 1 HI-Q GND 2 15 VIN 14 AZ IN M/Z 3 13 AZ FILTER U/D 4 12 AZ OUT COMP 5 11 INT OUT V- 6 ALOG GND 7 10 VREFIN **Dual-In-Line Package** 02 1 18 03 17 D D, 2 16 05 GND 4 15 V<sub>DO</sub> U/D 5 LD121A 13 SIGN M/Z 6 START 7 11 82 CLK 8 LD121A LD120 Synchronous Digital Processor Order Numbers: Analog Processor LD120CJ See Package 8 LD121ACJ Switch States are for a Logic "0" at U/D and M/Z Inputs. See Package 19

## -LD120/LD121A-

### ABSOLUTE MAXIMUM RATINGS

| VIN (Pin 15, 2 LD120) |          | $V- < V_{IN} < V+$              |

|-----------------------|----------|---------------------------------|

| INPUT (LD120)         |          | ±1 mA                           |

| V+ - V- (LD120)       |          |                                 |

| VSS ZNAMILDI 2100     | "(#) 成 离 | 20 V                            |

| Vss 查询"LP 120         | 一六四回\    | $^{\prime}$ DD to Vss $\pm$ 0.3 |

| VPEE CITE             |          |                                 |

## FLECTRICAL CHARACTERISTICS1

$T_A = 25^{\circ}C$

| n-vel               |                    | PARAMETER                                 | SYMBOL          | TEST CONDITIONS UNLESS OTHERWISE NOTED: V+ = 12 V, V- = V <sub>DD</sub> = -12 V, V <sub>SS</sub> = 5 V |                                                        | 2 V 800.5 LIMITS: Vm 0.005 |                |                                          | UNIT       |  |

|---------------------|--------------------|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------|----------------|------------------------------------------|------------|--|

|                     |                    |                                           | SYMBOL          |                                                                                                        |                                                        | MIN <sup>2</sup>           | ТҮРЗ           | MAX                                      | May        |  |

|                     | 1                  | int Fragmentage                           |                 | e/de//                                                                                                 | 2 V Scale                                              | -1                         | 1 ±1/4         | 1 1 1 1 1 1 1                            | Count      |  |

|                     | 1                  | Linearity 1939 MOMBERT 150                |                 | ence                                                                                                   | 200 mV Scale                                           | -2                         | ±1/2           | 2                                        |            |  |

| 4                   | İ                  | - Deth Acquisition                        | 4               |                                                                                                        | 2 V Scale                                              | district and               | 1/3            | 14 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |            |  |

| SYSTEM <sup>4</sup> |                    | Noise <sup>5</sup>                        |                 | f <sub>CLK</sub> = 163.84 kHz                                                                          | 200 mV Scale                                           | EL BOY                     | 1/2            | 2                                        |            |  |

| YST                 | ŀ                  | Normal Mode Rejection Ratio NMRR VREF = 6 |                 | V <sub>REF</sub> = 6.8 V                                                                               | f <sub>L</sub> = 50 or 60 Hz                           | e a selfant                | 40             | and solu                                 | dB         |  |

| S                   | 1                  | Power Supply Rejection Ratio              | PSRR            | EES .                                                                                                  |                                                        | ira filmor                 | 80             |                                          | 11/2/25    |  |

|                     | 1                  | Gain T.C.                                 |                 |                                                                                                        |                                                        |                            | 5              | 15                                       | ppm/°      |  |

|                     | İ                  | Zero Drift                                |                 | $C_{STRG} = 1 \mu F, R_{in} \le 100 k\Omega$                                                           |                                                        |                            | 1              | 5                                        | Count      |  |

|                     | 1                  | Analog Input Voltage                      | VANALOG         |                                                                                                        |                                                        | -5                         |                | 5                                        | V          |  |

| 0                   | =                  | Output Source Current                     |                 |                                                                                                        | /in = 2 V, Buff Out = 0 V                              |                            | -100           | -50                                      | μА         |  |

| 100                 | BUFFER             | Output Sink Current                       | ISINK           | $V_{in} = -2 V$ , Buff Out = 0 V                                                                       |                                                        | 400                        | 800            |                                          | ,,,,       |  |

| ō                   | 2                  | Input Current                             | IN              | $V_{in} = \pm$                                                                                         | 2.8 V                                                  |                            | 2              | Server and the                           | pA         |  |

| 1                   | INPUT              | Common Mode Rejection Ratio               | CMRR            |                                                                                                        | abuiter sourbeat                                       | and stated on a            | -72            | in and har                               | dB         |  |

| 1 5                 |                    | Input Current/Input Voltage High          | ЧH              | M/Z, U/D Inputs                                                                                        | V <sub>in</sub> = 2.0 V                                | A Landson                  | The American   | 20                                       | μΑ         |  |

| 1                   |                    | Input Current/Input Voltage Low           | one he wa       | Wi/Z, O/D imputs                                                                                       | V <sub>in</sub> = 0.8 V                                | -100                       | Plannac, se    | election dates                           | μΛ         |  |

| 0                   | Y.                 | Output Source Current                     | SOURCE          | ADMINISTRATE                                                                                           | group used offers                                      | shoot out 17 is            | -100           | france aug                               | ]A         |  |

| . 1                 | OFFER              | Output Sink Current                       | ISINK           | gun enudaco                                                                                            | au de utili dalla boso u                               | roll-transfer of           | 800            | District Control                         | μА         |  |

| i                   | 8                  | Offset Voltage                            | VOFFSET         | Vout                                                                                                   | = 0 V                                                  | -50                        | the matter out | 50                                       | mV         |  |

| A7 D                | AZ                 | Switch Resistance (on)9                   | 118140-1510     | VSTRG = -4 \                                                                                           | andre ad                                               | 6                          | 20             | kΩ                                       |            |  |

| 2 14                | ш                  | Reference Buffer Source Current           | SOURCE          | Vin (U/D IN) =                                                                                         | V <sub>in</sub> (U/D IN) = 0.8 V, V <sub>O</sub> = 0 V |                            |                | -400                                     | niause     |  |

| RE                  | 2                  | Reference Buffer Sink Current             | ISINK           | Vin (U/D IN) =                                                                                         | 2.0 V, V <sub>O</sub> = 2 V                            | id Innitite                | 100            | en (Williams)                            | μΑ         |  |

| 1                   | SUPPLY COMP GRATOR | Integrator Source Current <sup>10</sup>   | SOURCE          | V <sub>in</sub> (Int. IN) = -                                                                          | 100 mV, V <sub>O</sub> = 0 V                           | orit spreig                | -100           | ~50                                      | onno)      |  |

| 鱼                   |                    | Integrator Sink Current <sup>10</sup>     | ISINK           | V <sub>in</sub> (Int. IN) = 1                                                                          | I) = 100 mV, V <sub>O</sub> = 0 V 400 800              |                            |                | deviso                                   | antonan    |  |

| Z                   |                    | Output Swing                              | elgane trib     | R <sub>L</sub> = 10 k to 5 V<br>AZ FILTER IN = 100 mV<br>INTEGRATOR OUT = 0 V                          |                                                        | -10                        |                | 10                                       | S V        |  |

|                     |                    | Comparator Output Voltage                 | Vout            |                                                                                                        |                                                        | -5                         | g processor    | Zinnib Wall                              |            |  |

| 1 8                 |                    | Comparator Offset Voltage                 |                 |                                                                                                        |                                                        | -5                         | agus II Aseme  | 5                                        | mV         |  |

| 1                   |                    |                                           | VOFFSET<br>V+   |                                                                                                        |                                                        | 9                          | 12             | 15                                       |            |  |

| 1                   |                    | Positive Supply Voltage                   | V-              |                                                                                                        |                                                        | -15                        | -12            | -9                                       | V          |  |

| 1 6                 |                    | Negative Supply Voltage                   |                 |                                                                                                        | -10 -                                                  |                            | -12            | 3.5                                      | mA         |  |

| 1                   |                    | Positive Supply Current                   | 1+              |                                                                                                        |                                                        | AFFERRE                    | 300 ta         | 3.3                                      |            |  |

|                     |                    | Negative Supply Current                   | H-              |                                                                                                        |                                                        | -3.5                       |                |                                          |            |  |

| 1                   | NPUTS              | Input Voltage High                        | VINH            |                                                                                                        | put, Sign/UR/OR/                                       | 4                          |                | 0.5                                      | V          |  |

| 1                   |                    | Input Voltage Low                         | VINL            | Blink <sup>6</sup> , Start, CLK IN                                                                     |                                                        | Care Co                    | 170            | 300                                      | -          |  |

| 1 5                 | 힐                  | Input Current/Input Voltage High          | INH             | V <sub>in</sub> = 5 V (Sign/OR/UR <sup>6</sup> )                                                       |                                                        |                            | 170            | 300                                      | μА         |  |

| L                   |                    | Input Current/Input Voltage Low           | INL             | V <sub>in</sub> = 0 V (Start Convert, Clock)  Bit Lines, IOH = -40 #A                                  |                                                        | -400                       | -150           |                                          |            |  |

|                     | LS                 | Output Voltage High                       | VOH             | Sign/OR/UR,                                                                                            | I <sub>OH</sub> = -40 μA                               | 2.4                        |                | 0.0                                      | -          |  |

| 1                   |                    | Output Voltage Low                        | VOL             | Digit Strobes                                                                                          | I <sub>OL</sub> = 1.6 mA                               | LINE IN                    | Andrew K       | 0.6                                      | al comment |  |

| 1 3                 | 5                  | Output Voltage High                       | VOH             | M/Z                                                                                                    | I <sub>OH</sub> = -150 μA                              | 4                          |                | 2.0                                      | V          |  |

| 5                   | NAMIC OUTPUTS      | Output Voltage Low                        | VOL             | HARTE I                                                                                                | I <sub>OL</sub> = 0.8 mA                               |                            | 70 -0 C        | 0.6                                      |            |  |

| 5 6                 |                    | Output Voltage High                       | Voн             | U/D                                                                                                    | $I_{OH} = -0.5 \text{ mA}$                             | 4                          |                |                                          | 1          |  |

| DISTA DIGITAL       |                    | Output Voltage Low                        | VOL             | 11.566 103                                                                                             | I <sub>OL</sub> = 0.8 mA                               |                            |                | 0.6                                      |            |  |

| 5                   |                    | Start Convert <sup>7</sup>                | tp              | Line street Chi                                                                                        |                                                        | 20                         |                |                                          | μS         |  |

|                     |                    | Clock Frequency                           | fCLK            | 50% Duty Cycle                                                                                         |                                                        | 50                         |                | 250                                      | kHz        |  |

|                     | DX                 | Rep Rate (Strobes)                        |                 | f <sub>CLK</sub> -640                                                                                  |                                                        | 78                         |                | 470                                      | Hz         |  |

| 1                   | > -                | Positive Supply Voltage                   | VSS             | Range Over which                                                                                       |                                                        | 4.5                        | 5              | 5.5                                      | V          |  |

| 1                   |                    | Negative Supply Voltage                   | V <sub>DD</sub> | Functionality                                                                                          | s Guaranteed                                           | -13.2                      | -12            | -10.8                                    |            |  |

|                     |                    | Positive Supply Current <sup>8</sup>      | ISS             |                                                                                                        |                                                        |                            | 14             | 25                                       | mA.        |  |

| 0,                  | 31                 | Negative Supply Current                   | IDD             | AF2YO.                                                                                                 |                                                        | -25                        | -14            |                                          |            |  |

(See next page)

#### LD120/LD121A ELECTRICAL CHARACTERISTICS1 (Cont.) TEST CONDITIONS LIMITS UNLESS OTHERWISE NOTED: UNIT SYMBOL PARAMETER $V+ = 12 \text{ V}, V- = V_{DD} = -12 \text{ V}, V_{SS} = 5 \text{ V}$ MIN<sup>2</sup> түр3 MAX fCLK = 163.84 kHz, VREF = 6.8 V zero 查询"LD120"供应商 5 Count

$C_{STRG} = 1 \mu F, R_{in} \le 100 k\Omega$

#### NOTES:

- Refer to PROCESS OPTION FLOWCHART for additional information.

- 2. The algebraic convention whereby the most negative value is a minimum, and the most positive value is a maximum, is used in this data sheet.

- 3. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- System parameters not directly tested.

- Bit width over which reading is stable 95% of the time.

- 6. Pin characteristic only during D<sub>4</sub> strobe time.

- Minimum positive going pulse width to initiate a conversion.

- All outputs disconnected.

- VSTRG must be more positive than -4 V.

- Reference source impedance must be less than 10 k.

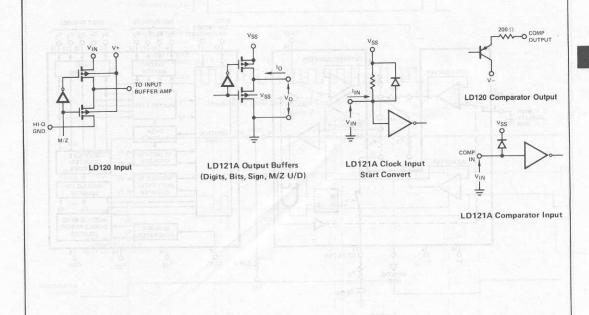

### INPUT/OUTPUT SCHEMATICS

#### FUCTIONAL SYSTEM OPERATION

Timing: The external oscillator is divided to generate a 2- $\phi$  clock on the synchronous digital chip. A time base generator divides the property into sampling intervals of 49,152 the property into sampling intervals of 49,152 the property into sampling intervals of 49,152 the property into sampling intervals.

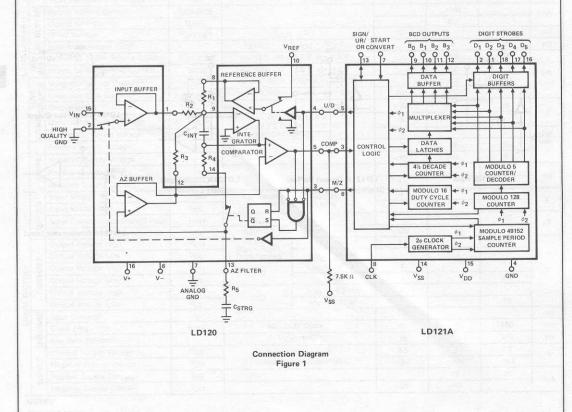

Auto-Zero Interval: The connection diagram in Figure 1 illustrates the system during the Auto-Zero interval. The input buffer is switched to reference ground and supplies a current equal to its offset voltage divided by R<sub>2</sub> to the integrator summing mode. The U/D buffer is toggled by the digital processor between V<sub>REF</sub> and ground with a 50% duty cycle. This results in a current flow equal to V<sub>REF</sub>/R<sub>1</sub> to the summing node half of the time. The AZ capacitor, C<sub>STRG</sub>, assumes a voltage, V<sub>STRG</sub>, that is equal to the average value of integrator output. The AZ buffer supplies a current to the summing node equal to the V<sub>STRG</sub> voltage divided by R<sub>3</sub>.

The system will reach an equilibrium when the sum of the DC currents into the summing node equal zero. At this time, the current through  $R_3$  equals  $-\frac{1}{2}$   $V_{REF}/R_1$  plus the small currents necessary to cancel the offset of the input buffer and integrator input bias current. Capacitor

CSTRG "stores" VSTRG when the AZ switch opens at the end of the Auto-Zero interval. The digital BCD counter is inactive during Auto-Zero. It is reset to zero during the last clock pulse of the Auto-Zero interval.

## THE U/D CONTROL DURING THE MEASURE INTERVAL

The U/D buffer is switched to  $V_{\mbox{REF}}$  when the U/D control is low. In this state the currents through  $R_1$  and  $R_3$  sum to  $\frac{1}{2}$   $V_{\mbox{REF}}/R_1$ . A high level on the U/D control connects the U/D buffer to ground. During this state the sum of the currents through  $R_1$  and  $R_3$  sum to  $-\frac{1}{2}$   $V_{\mbox{REF}}/R_1$ . In one clock cycle, a charge equal to  $V_{\mbox{REF}}/2R_1f_{\mbox{IN}}$  coulombs is either added or subtracted to the integrator capacitor. The BCD counter is decremented for each addition of this quantized charge and incremented for each subtraction of quantized charge.

#### THE MEASURE ALGORITHM

The input is connected to  $V_{IN}$  during the measure interval and supplies a current to the integrator equal to  $V_{IN}/R_2$ .

This causes the integrator output to move away from VSTRG. The digital processor attempts to keep the integrator control of the processor attempts to keep the integrator control of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the processor attempts to keep the integrator of the

# U/D DUTY CYCLE CONTROL DURING THE MEASURE INTERVAL

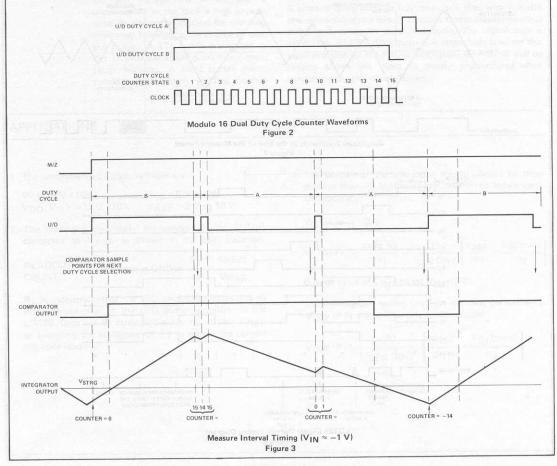

The digital processor contains a modulo 16 duty cycle counter that provides the U/D control output. This counter examines the state of the comparator once each 16 clock cycles during state 15. If the comparator is high, the U/D control will be high for one cycle and low for 15 cycles in the next 16 clock cycle period of the duty cycle counter. If the comparator output is low, the U/D control will be high for 15 cycles and low for one cycle in the next period of the duty cycle counter. Figure 2 illustrates these waveforms. The effect of these two duty cycles is to source or sink a net 14 charge parcels to CINT, thus driving the

integrator output toward V<sub>STRG</sub> and accumulating counts in the BCD counter in groups of 14 counts. This dual duty cycle control technique results in a fixed number of U/D control transitions, regardless of the value of V<sub>IN</sub>; therefore, these transitions cannot cause linearity error. The first few periods of the measure interval are illustrated in Figure 3 for a negative V<sub>IN</sub>.

### AUTO-ZERO OVERRIDE AT THE END OF MEASURE

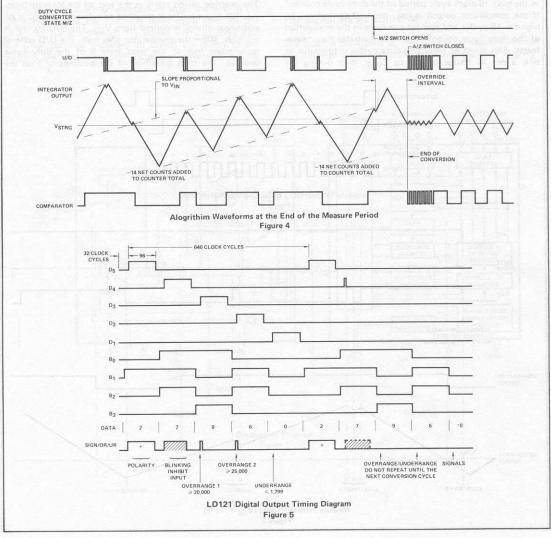

The BCD counter contents equal a multiple of 14 counts at the end of the measure interval. A residual voltage on C<sub>INT</sub> represents the remaining unresolved portion of the input voltage. This voltage is cancelled and the corresponding counts accumulated during a brief override period at the start of the AZ interval. Normal AZ interval action is inhibited until this residual count is resolved.

The override period starts at the end of the Measure Interval. The input buffer is switched to reference ground as no additional charge is desired from  $V_{\mbox{\scriptsize IN}}$ . The U/D control is set high. After the comparator goes high, the U/D control is switched low at the next state 8 of the duty cycle counter. The next transition of the comparator ends the

## FUNCTIONAL SYSTEM OPERATION (Cont.)

Figure 4 illustrates the events at the end of the measure interval. The slope of the dotted lines is proportional to the unknown current through  $R_2$ .

The self oscillation following the override period keeps V<sub>INT</sub> near V<sub>STRG</sub> until sync is achieved with the duty cycle counter. This feature eliminates large transients on C<sub>STRG</sub> and results in highly stable Auto-Zero loop characteristics.

#### DIGITAL INTERFACE FUNCTIONAL DESCRIPTION

BCD Outputs— (Pins 9, 10, 11 and 12): The output latch contents are time multiplexed in a digit serial, bit parallel fashion through 4 push-pull TTL compatible output buffers. A high level (sourcing current from  $V_{SS}$ ) indicates a one and a low level (sinking current to ground) indicates a zero.  $B_0$  is the least significant Bit. Figure 5 illustrates the timing relationship. All BCD outputs are valid during digit strobe time.

Digit Strobes—(Pins 1, 2, 16, 17 and 18): Figure 5 indicates the operation of these outputs. The strobes are TTL compatible. Only one strobe is high at one time. The strobe period is equal to 640 clock cycles with a 15% duty cycle. An inter-digit blanking period of 32 clock cycles permits easy interface with gas discharge displays. The strobe sequence is D<sub>5</sub> (MSD), D<sub>4</sub>, D<sub>3</sub>, D<sub>2</sub>, D<sub>1</sub> (LSD).

Sign/Overrange/Underrange (Pin 13): This pin operates as a TTL compatible output during  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_5$  strobe times and as an input during  $D_4$  strobe time. Figure 5 indicates the timing relationship. Information is presented to this output as follows:

At D<sub>5</sub> Time — Polarity is indicated by a high level for positive and a low level for negative. It is valid approximately 0.25 µsec after D<sub>5</sub> goes high until the end of each D<sub>5</sub> strobe.

At D<sub>4</sub> Time — The output buffer assumes a high im-

goes high until the end of each D5 strobe. The output buffer assumes a high impedance state. An input latch samples the voltage level imposed on this pin during D4 time. A high level will inhibit the overrange blinking (digit strobes are suppressed during zero interval). An internal pull down resistor will hold the pin voltage low if the pin is unconnected or the load is high impedance. An alternative method for selecting overrange blinking is the choice of output buffer. A TTL buffer connected to pin 13 provides a pullup inhibiting overrange blinking. A NPN buffer driver provides a pulldown yielding normal

overrange blinking.

At D<sub>3</sub> Time — If the count is equal to or greater than 20,000, a single positive going pulse will occur at the beginning of the first D<sub>3</sub> time after the end of conversion cycle. The pulse width equals one clock cycle. The overrange blinking is momentarily inhibited when overrange pulses are present to prevent the display blinking feature from interfering with the decoding of the overrange output.

At  $D_2$  Strobe— A second overrange pulse occurs at the beginning of the first  $D_2$  time, after the end of conversion, if the count is

equal or exceeds 25,000 counts.

At D<sub>1</sub> Strobe— A single pulse occurs at the beginning of the first D<sub>1</sub> time after the end of conversion, if the count is less than 1800 counts.

All overrange and underrange signals are one clock pulse wide. They occur only once per measure/zero cycle.

Start Conversion (Pin 7): A low level on this TTL compatible input holds the system in the zero mode continuously. A positive going pulse at least one clock time wide initiates one conversion cycle within 16 clock cycles after system has completed minimum auto zero cycle. The digital data is valid after 32,850 clock cycles. A static high level on this input provides normal cyclical operation. An internal pull up resistor allows this input to remain unconnected when conversion control is not desired.

#### **APPLICATIONS**

1. The recommended supply voltages are:

2. The reading is essentially the proportionality of V<sub>IN</sub> compared to V<sub>REF</sub> as shown in the gain equation:

$$\begin{array}{l} \text{READOUT} = (\text{V}_{IN} - \text{V}_{HI\text{-}Q} \text{ GND}) \bullet \begin{array}{l} \frac{R_1}{R_2} \bullet \begin{array}{l} 65,536 \\ \hline \text{V}_{REF} \end{array} \end{array}$$

$R_{1}$  is independent of the U/D switch resistance due to the incorporation of the U/D buffer amplifier in the LD120. Gain can be calibrated either by varying VREF or trimming the resistance of  $R_{1}$  to obtain the correct full scale reading.

The output of the integrator should always be more positive than -9 V (for VDD = -12 V) to obtain specified accuracy:

$$V_0$$

(min)  $> -9$  V 1150 asgot Installed ups off of

$$V_{O} \text{ (min)} = -\frac{V_{REF} R_{3}}{2R_{1}} - \frac{15}{f_{CLK} CINT} \left[ \frac{V_{REF}}{2R_{1}} + \frac{V_{IN} \text{ (max)}}{R_{2}} \right]$$

Change value of CINT to set VINT(P-P).

Large integrator swing provides the best performance.  $V_{INT}$  (P-P) = 6 to 8 volts is recommended.

$$V_{INT} (P-P) = \frac{30}{f_{CLK} C_{INT}} \left[ \frac{V_{REF}}{2R_1} + \frac{V_{IN} (max)}{R_2} \right]$$

## APPLICATIONS (Cont.)

4. Although any oscillator frequency from 50 kHz to 250 kHz can be used, frequencies that provide integer number of line frequency cycles per measure period provide national line noise rejection. These frequencies are:

$$f_{CLK} = \frac{32,768 \text{ FLINE}}{n}$$

, n = 8, 9, 10, ... 40

$f_{CLK}$  = 163,840 is popular since it provides both 50 and 60 Hz rejection.

- 5. The sampling rate =  $f_{CLK}/49,152$  cycles/sample.

- After a start conversion pulse, data is valid 32,850 clock pulses later and remains valid until at least 32,768 clock pulses after the next start pulse. During continuous cycle operation, data is assured valid when M/Z is high or 100 clock cycles after the one/zero transition of M/Z.

- Any capacitive coupling between U/D and Comp. is detrimental to proper algorithm operation. PC board layouts should not allow these traces to be adjacent.

- All power supplies should be capacitively bypassed to ground for maximum count stability.

- CINT and CSTRG should be selected for low leakage.

Silvered mica is recommended for CINT and mylar for CSTRG. Polypropylene capacitors also work well for both CSTRG and CINT.

- 10. For a given leakage into CSTRG of ISTRG:

$$\Delta V_{STRG} = \frac{\Delta t I_{AZ}}{C_{STRG}}$$

where  $\Delta t$  = a measure interval =  $\frac{2}{3} \times \frac{1}{\text{FSAMPLE}}$

$\Delta V_{STRG}$  will inject a  $\Delta I$  integrator of  $\Delta V_{STRG}/R_3$  Now a  $\Delta I$  integrator would have been equivalent to a  $\Delta V_{IN}/R_2$

So the equivalent input drift is

$$\Delta V_{IN} = \frac{1}{2} \times \frac{R_2}{R_3} \times \frac{2}{3} \times \frac{I_{STRG}}{F_{SAMPLE} \cdot C_{STRG}}$$

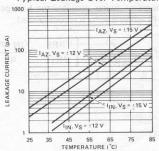

Typical Leakage Over Temperature

the ½ factor is provided by integrator action.

Example: We wish to see 1 count (0.1 mV of  $\Delta V_{IN}$  on the 2 V range) of drift for the circuit of Figure 7 with  $I_{STRG} = 100 \, pA \ @ \ 70^{\circ} \, C$ . What  $C_{STRG}$  is needed?

Answer:

$$C_{STRG} = \frac{R_2}{R_3} \times \frac{1}{3} \times \frac{I_{STRG}}{F_{SAMPLE} \cdot \Delta V_{IN}} = \frac{100K \Omega}{62K \Omega} \times \frac{1}{3} \times \frac{10^{-10} \text{ F}}{3 \text{ Hz} \times 10^{-4} \text{ V}}$$

=  $0.18 \mu F$  Minimum

Interfacing the LD120/LD121A to Microprocessors: A description of interfacing the LD120/LD121A to the 8080 μP is given in AN77-3. Some of the timing details warrant description here.

The end-of-conversion is determined by gating  $\overline{M/Z}$   $\cdot$   $\overline{U/D}$   $\cdot$   $\overline{COMP}$ . At this time, all BCD latches are updated with the contents of the latest conversion.

We recommend using the negative edge of M/Z to interrupt the processor. Next, test for a high D5 digit strobe (MSD). Once D5 is high load the BCD data from  $B_0-B_3$  lines and the polarity information from the SIGN/OR/UR line. Next delay 128 LD121A clock times (this assures that the D4 data is valid) then load  $B_0-B_3$  lines containing the D4 data. Next delay another 128 LD121A clock times (this assures that the D3 data is valid) then load  $B_0-B_3$  lines containing the D3 data. Repeat this process for D2 and finally the D1 (LSD) data load. In flowchart form (see Figure 6).

Flow Chart for 8080 Interface Figure 6

## APPLICATIONS (Cont.)

### CIRCUIT BENEFITS

- Overrange Blinking

- Overrange Billiking

Leakages and Comparator

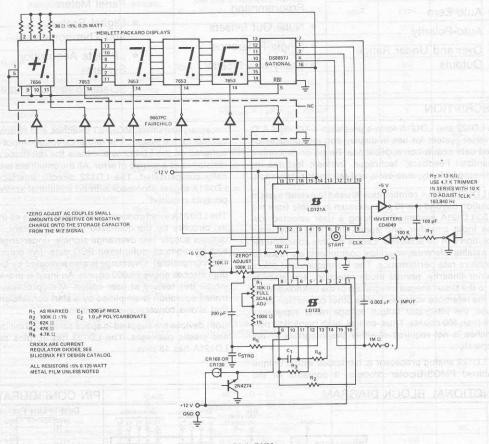

41/2 Digit DVM Figure 7