# Issue Date: Feb. 18, 2004

FEDL7029-03

# **ML7029**

### **Multifunction ADPCM CODEC**

#### **GENERAL DESCRIPTION**

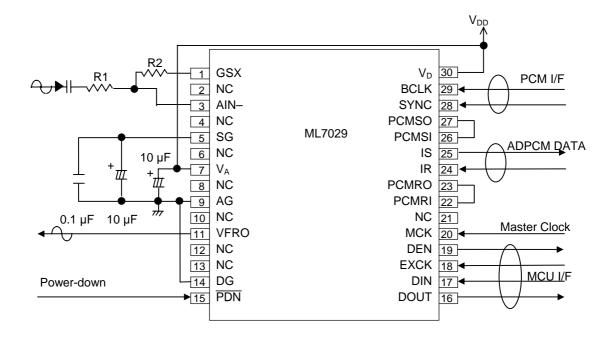

The ML7029 is a single channel ADPCM CODEC IC which performs mutual transcoding between the analog voice band signal and 32 kbps ADPCM serial data.

#### **FEATURES**

• Single 3 V Power Supply Operation (V<sub>DD</sub>: 2.7 to 3.6 V)

• ADPCM Algorithm: ITU-T G.726 (32 kbps, 24 kbps, 16 kbps)

Full-Duplex Transmit/Receive OperationTransmit/Receive Synchronous Mode Only

• PCM Data Format: μ-law

• Serial PCM/ADPCM Transmission Data Rate: 64 kbps to 2048 kbps (when SYNC = 8 kHz)

• Low Power Consumption

Operating Mode:  $18 \text{ mW Typ.} (V_{DD} = 3.0 \text{ V, SYNC} = 8 \text{ kHz})$ Power-Down Mode:  $0.03 \text{ mW Typ.} (V_{DD} = 3.0 \text{ V, SYNC} = 8 \text{ kHz})$ • Sampling Frequency: 6 kHz to 21 kHz selectable (However, there are

limitations to 16 kHz or higher frequencies)

• Master Clock Frequency: Sampling frequency × 1296

When SYNC = 8 kHz: 10.368 MHz

• Transmit/Receive Mute, Transmit/Receive Programmable Gain Control

- Side Tone Path with Programmable Attenuation (8-Step Level Adjustment)

- Serial MCU Interface Control

- Package:

30-pin plastic SSOP (SSOP30-P-56-0.65-K) (ML7029)

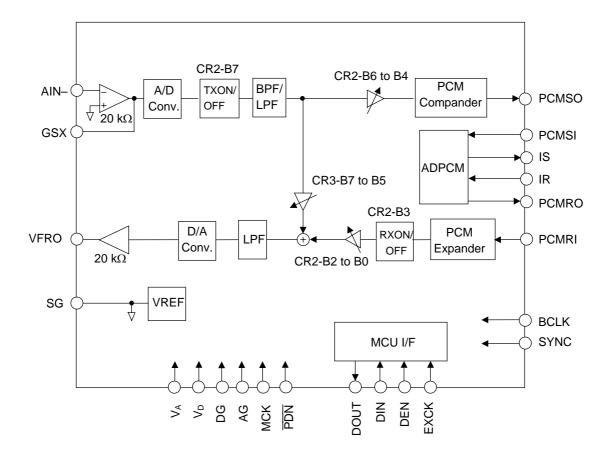

# **BLOCK DIAGRAM**

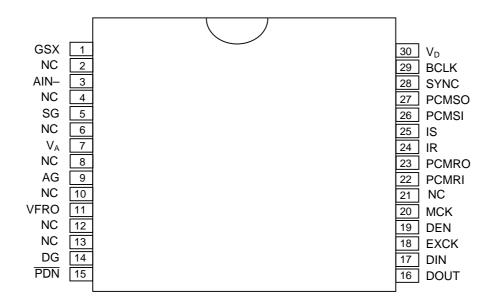

# PIN CONFIGURATION (TOP VIEW)

**NC: No Connection**

30-Pin Plastic SSOP

#### PIN FUNCTIONAL DESCRIPTIONS

#### AIN-, GEX

Transmit analog input and transmit level adjustment.

AIN— is connected to the inverting input of the transmit amplifier. GSX is connected to the transmit amplifier output. During power-down mode, the GSX output is a high impedance state.

### **VFRO**

Receive analog output. During power-down mode, the VFRO output is in a high impedance state.

#### SG

Analog signal ground.

The output voltage of this pin is approximately 1.4 V. Put 10  $\mu$ F plus 0.1  $\mu$ F (ceramic type) bypass capacitors between this pin and AG. During power-down, this output voltage is 0 V. This pin should be used via a buffer if used externally.

#### AG

Analog ground.

#### DG

Digital ground.

This ground is separated from the analog signal ground pin (AG). The DG pin must be kept as close as possible to AG on the PCB.

#### Va

Analog +3 V power supply.

#### $V_{D}$

Digital +3 V power supply.

This power supply is separated from the analog signal power supply pin  $(V_A)$ . The  $V_D$  pin must be kept as close as possible to  $V_A$  on the PCB.

### **PDN**

Power-down and reset control input.

A "0" level makes the IC enter a power-down state. At the same time, all control register data are reset to the initial state. Set this pin to "1" during normal operating mode. The power-down state is controlled by a logical OR with CR0-B5 of the control register. When using  $\overline{PDN}$  for power-down and reset control, set CR0-B5 to digital "0". The reset width (a "L" level period) should be 200 ns or more.

Be sure to reset the control registers by executing this power down to keep this pin to digital "0" level for 200 ns or longer after the power is turned on and  $V_{DD}$  exceeds 2.7 V.

#### **MCK**

Master clock input.

The frequency is 1296 times the SYNC signal. For example, it is 10.368 MHz when the SYNC signal is 8 kHz. The master clock signal may be asynchronous with BCLK and SYNC.

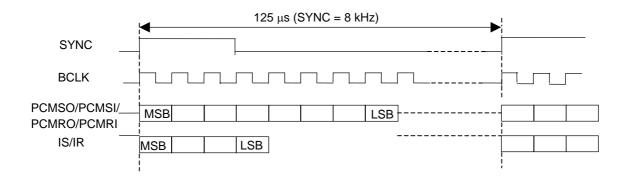

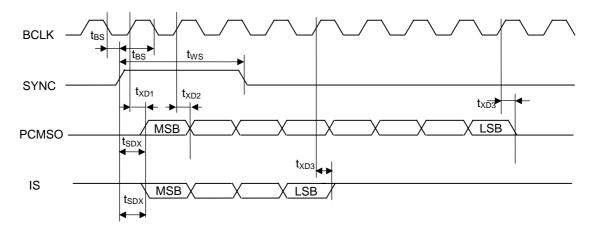

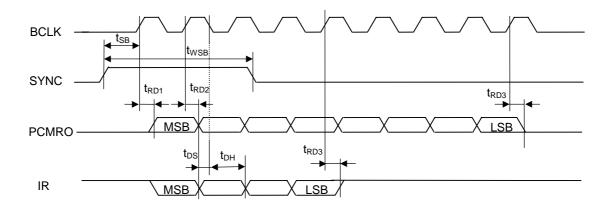

#### **PCMSO**

Transmit PCM data output.

PCM is output from MSB in synchronization with the rising edge of BCLK and XSYNC.

Refer to Figure 1. During power-down, the PCMSO output is at "L" level.

#### **PCMSI**

Transmit PCM data input.

This signal is converted to the transmit ADPCM data, PCM is shifted in synchronization with the falling edge of BCLK. Normally, this pin is connected to PCMSO. Refer to Figure 1.

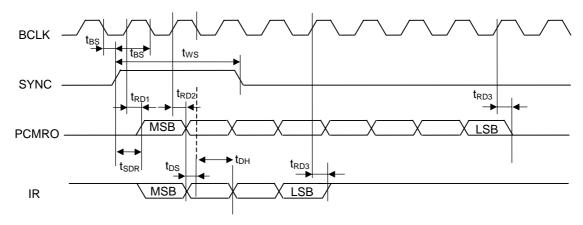

#### **PCMRO**

Receive PCM data output.

PCM is the output signal after ADPCM decoder processing. This signal is output serially from MSB in synchronization with the rising edge of BCLK and RSYNC. Refer to Figure 1.

During power-down, the PCMRO output is at "L" level.

#### **PCMRI**

Receive PCM data input.

PCM is shifted on the rising edge of the BCLK and input from MSB. Normally, this pin is connected to PCMRO. Refer to Figure 1.

#### IS

Transmit ADPCM signal output.

After having encoded PCM with ADPCM, the signal is output from MSB in synchronization with the rising edge of BCLK and XSYNC. Refer to Figure 1. This pin is at "H" level during power-down.

#### IR

Receive ADPCM signal input.

This input signal is shifted serially on the falling edge of BCLK and SYNC and input from MSB. Refer to Figure 1.

#### **BCLK**

Shift clock input for the PCM and ADPCM data.

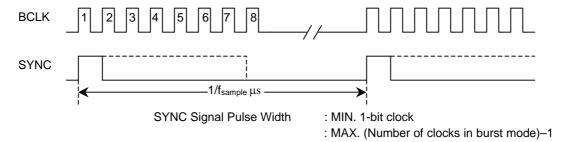

The frequency is set in the range of 8 to 256 times the SYNC frequency. Refer to Figure 1.

### **SYMC**

Sampling input for the PCM and ADPCM data. The frequency is 8 kHz or 11.025 kHz and is selected by the control register data CR3-B1.

Synchronize this signal with BCLK signal. SYNC is used to indicate the MSB of the PCM data stream. Refer to Figure 1.

Figure 1 PCM and ADPCM Interface Basic Timing

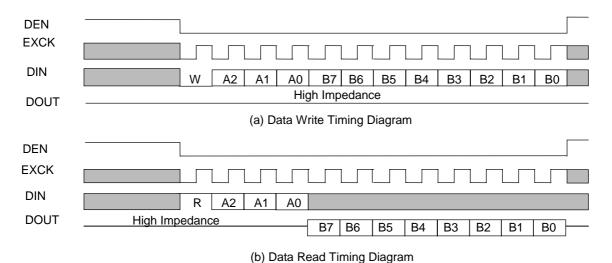

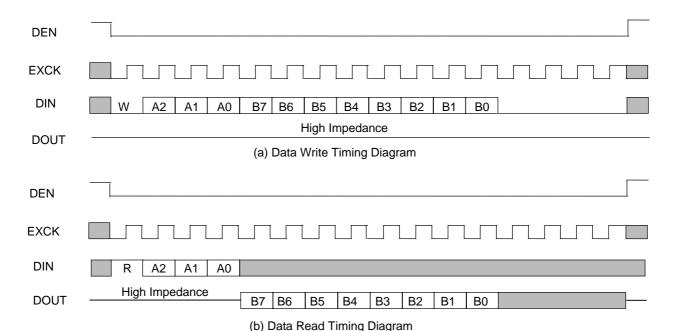

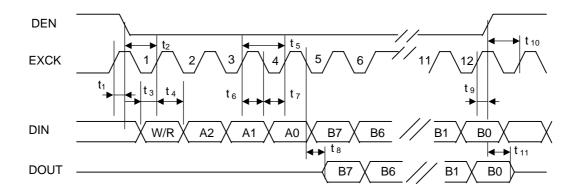

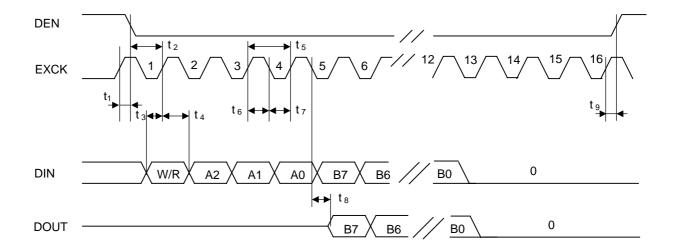

### DEN, EXCK, DIN, DOUT

Serial control ports for MCU interface.

Reading and writing data are performed by an external MCU through these pins. The 8-byte cotrol registers (CR0 to 7) are provided on the device.

DEN is the "Enable" control signal input, EXCK is the data shift clock input, DIN is the address and data input, and DOUT is the data output.

Figures 2-1 and 2-2 show the input/output timing diagram. During power-down, the DOUT output is in a high impedance state.

Figure 2-1 MCU Interface Input/Output Timing (DIN = 12 bits)

Figure 2-2 MCU Interface Input/Output Timing (DIN = 16 bits)

Table 1 shows the register map.

Table 1 Control Register Map

| Nama | Ad | ddre | SS |                    |                    | C                  | ontrol and  | Detect Da    | ta          |               |               | DAM |

|------|----|------|----|--------------------|--------------------|--------------------|-------------|--------------|-------------|---------------|---------------|-----|

| Name | A2 | Α1   | Α0 | B7                 | В6                 | B5                 | B4          | В3           | B2          | B1            | В0            | R/W |

| CR0  | 0  | 0    | 0  | _                  | _                  | PDN<br>ALL         | _           | _            |             |               | _             | R/W |

| CR1  | 0  | 0    | 1  | MODE 1             | MODE 0             | TX<br>RESET        | RX<br>RESET | TX<br>MUTE   | RX<br>MUTE  | 1             | RX<br>PAD     | R/W |

| CR2  | 0  | 1    | 0  | TX<br>ON/OFF       | TX<br>GAIN2        | TX<br>GAIN1        | TX<br>GAIN0 | RX<br>ON/OFF | RX<br>GAIN2 | RX<br>GAIN1   | RX<br>GAIN0   | R/W |

| CR3  | 0  | 1    | 1  | Side Tone<br>GAIN2 | Side Tone<br>GAIN1 | Side Tone<br>GAIN0 | _           | _            | _           | HPF<br>8k/11k | HPF<br>ON/OFF | R/W |

R/W: Read/Write enable

# ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol           | Condition    | Rating                  | Unit |

|-----------------------|------------------|--------------|-------------------------|------|

| Power Supply Voltage  | $V_{DD}$         |              | 3 to +5.0               | V    |

| Analog Input Voltage  | $V_{AIN}$        | _            | $-0.3$ to $V_{DD}$ +0.3 | V    |

| Digital Input Voltage | $V_{DIN}$        | _            | $-0.3$ to $V_{DD}$ +0.3 | V    |

| Storage Temperature   | T <sub>stg</sub> | <del>_</del> | -55 to +150             | °C   |

# RECOMMENDED OPERATION CONDITIONS

| Parameter                                          | Symbol            | Condition                     | Min.                 | Тур.           | Max.                 | Unit |

|----------------------------------------------------|-------------------|-------------------------------|----------------------|----------------|----------------------|------|

| Power Supply Voltage                               | $V_{DD}$          | Voltage must be fixed         | +2.7                 | 3.0            | +3.6                 | V    |

| Operating Temperature Range                        | Та                | _                             | -25                  | +25            | +70                  | °C   |

| Digital Input High Voltage                         | V <sub>IH</sub>   | Digital Input Pins            | $0.45 \times V_{DD}$ | _              | $V_{DD}$             | V    |

| Digital Input Low Voltage                          | VIL               | Digital Input Pins            | 0                    | _              | $0.16 \times V_{DD}$ | V    |

| Master Clock Frequency                             | f <sub>MCK1</sub> | MCK                           | 7.776                | 10.368         | 20.736               | MHz  |

| Master Clock Frequency<br>Accuracy                 | f <sub>MCK2</sub> | MCK                           | -0.01%               | SYNC ×<br>1296 | +0.01%               | MHz  |

| Bit Clock Duty                                     | f <sub>BCK</sub>  | BCLK                          | SYNC × 8             | 1              | SYNC × 256           | kHz  |

| Sampling Frequency (*1)                            | f <sub>SYNC</sub> | SYNC                          | 6.0                  | 8.0            | 16                   | kHz  |

| Master Clock Duty Ratio                            | D <sub>MCK</sub>  | MCK (≤20.736 MHz)             | 30                   | 50             | 70                   | %    |

| Clock Duty Ratio                                   | D <sub>CLK</sub>  | BCLK, EXCK                    | 30                   | 50             | 70                   | %    |

| Digital Input Rise Time                            | t <sub>ir</sub>   | Digital Input Pins            | _                    | _              | 50                   | ns   |

| Digital Input Fall Time                            | t <sub>if</sub>   | Digital Input Pins            | _                    | _              | 50                   | ns   |

| PCM Sync Signal Setting<br>Time (Continuous BCLK)  | t <sub>BS</sub>   | BCLK ↔ SYNC<br>(see Fig. 3-1) | 100                  | _              | _                    | ns   |

| PCM Sync Signal Setting<br>Time (Burst Mode Clock) | t <sub>SB</sub>   | BCLK ↔ SYNC<br>(see Fig. 3-2) | 0                    | _              | 20                   | μS   |

| SYNC Signal Width<br>(Continuous BCLK)             | t <sub>WS</sub>   | SYNC (see Fig. 3-1)           | 1BCLK                | _              | SYNC -1<br>BCLK      | μS   |

| SYNC Signal Width<br>(Burst Mode Clock)            | t <sub>WSB</sub>  | SYNC (see Fig. 3-2)           | 1BCLK                | _              | Burst<br>Clock –1    | μS   |

| PCM, ADPCM Setup Time                              | t <sub>DS</sub>   | _                             | 100                  | _              | _                    | ns   |

| PCM, ADPCM Hold Time                               | t <sub>DH</sub>   | _                             | 100                  | _              | _                    | ns   |

| Digital Output Load                                | $C_{DL}$          | Digital Output Pins           | _                    | _              | 100                  | pF   |

| Bypass Capacitors for SG                           | C <sub>SG</sub>   | SG to AG                      | 10+0.1               |                |                      | μF   |

<sup>\*1:</sup> Refer to the Appendix.

# **ELECTRICAL CHARACTERISTICS**

### **DC** Characteristics

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

| Parameter                                        | Symbol           | Condition                              | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|------------------|----------------------------------------|------|------|------|------|

| Power Supply Current                             | I <sub>DD1</sub> | Operating Mode No Signal               | _    | 6.0  | 12   | mA   |

| $(V_{DD} = 3.0 \text{ V, SYNC} = 8 \text{ kHz})$ | I <sub>DD2</sub> | Power Down Mode (Input pins are fixed) | _    | 0.01 | 0.1  | mA   |

| Input Leakage Current                            | I <sub>IH</sub>  | $V_I = V_{DD}$                         | _    | _    | 2.0  | μA   |

|                                                  | I <sub>IL</sub>  | $V_I = 0 V$                            | _    | _    | 0.5  | μA   |

| Output High Voltage                              | VoH              | I <sub>OH</sub> = 4 mA                 | 2.4  | _    | _    | V    |

| Output Low Voltage                               | V <sub>OL</sub>  | $I_{OL} = -4 \text{ mA}$               | _    | _    | 0.4  | V    |

| Input Capacitance                                | C <sub>IN</sub>  |                                        | _    | 5    | _    | pF   |

# **Analog Interface Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

|                         |                 | 1                                               | · DD — <b>—</b> |      | .u = _0 | <del>(0 . , 0 0)</del> |

|-------------------------|-----------------|-------------------------------------------------|-----------------|------|---------|------------------------|

| Parameter               | Symbol          | Condition                                       | Min.            | Тур. | Max.    | Unit                   |

| Input Resistance        | R <sub>IN</sub> | AIN-                                            | _               | 10   | _       | MΩ                     |

| Output Load Resistance  | R <sub>L</sub>  | GSX, VFRO                                       | 20              | _    | _       | kΩ                     |

| Output Load Capacitance | CL              | GSX, VFRO                                       | _               | _    | 100     | pF                     |

| Output Amplitude (*2)   | V <sub>O1</sub> | GSX, VFRO ( $R_L = 20 \text{ k}\Omega$ )        | _               | _    | 1.3     | $V_{PP}$               |

| Offset Voltage          | V <sub>OF</sub> | GSX, VFRO                                       | -100            | _    | +100    | mV                     |

| SG Output Voltage       | V <sub>SG</sub> | SG                                              | _               | 1.4  | _       | V                      |

| SG Output Resistance    | Rss             | SG                                              | _               | 40   | _       | kΩ                     |

| SG Warm-up Time         | T <sub>SG</sub> | SG↔AG 10+0.1μF<br>(Rise time to max. 90% level) | _               | 700  | _       | ms                     |

<sup>\*2:</sup>  $-7.7 \text{ dBm } (600\Omega) = 0 \text{ dBm0}, +3.17 \text{ dBm0} = 1.3 \text{ V}_{PP}$

# **AC Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

|                                         | 1                 | T                                    | (V <sub>DD</sub> = | = 2.7 to 3.0 | 6 V, Ta  | = –25 tc     | +70°C)   |

|-----------------------------------------|-------------------|--------------------------------------|--------------------|--------------|----------|--------------|----------|

| Parameter                               | Symbol            | Condition                            |                    | Min.         | Тур.     | Max.         | Unit     |

|                                         | _                 | Freg. (Hz)                           | Level (dBm0)       |              | 71       |              |          |

| Transmit Francisco                      | LB8T1             | 60                                   |                    | 30           | _        | _            | dB       |

| Transmit Frequency Response             | LB8T2             | 300                                  |                    | -0.5         | _        | 1.5          | dB       |

| SYNC = 8 kHz                            | LB8T3             | 1015                                 | 0                  | Re           | eference | <del>)</del> | dB       |

| BPF                                     | LB8T4             | 3400                                 |                    | -0.5         | _        | 1.0          | dB       |

|                                         | LB8T5             | 3970                                 |                    | 12           | _        | _            | dB       |

|                                         | LB11T1            | 60                                   |                    | 30           | _        | —            | dB       |

| Transmit Frequency                      | LB11T2            | 300                                  |                    | -0.5         |          | 1.5          | dB       |

| Response<br>SYNC = 11.025 kHz           | LB11T3            | 1400                                 | 0                  | Re           | dB       |              |          |

| BPF                                     | LB11T4            | 4690                                 |                    | -0.5         | _        | 1.0          | dB       |

|                                         | LB11T5            | 5470                                 |                    | 12           | _        | _            | dB       |

| Transmit Frequency                      | LL8T1             | 300                                  |                    | -0.5         | _        | 0.5          | dB       |

| Response                                | LL8T2             | 1015                                 | 0                  | Re           | eference | <del>.</del> | dB       |

| SYNC = 8 kHz                            | LL8T3             | 3400                                 | 0                  | -0.5         | _        | 1.0          | dB       |

| LPF                                     | LL8T4             | 3970                                 |                    | 12           | _        | _            | dB       |

| Transmit Frequency                      | LL11T1            | 300                                  |                    | -0.5         | _        | 0.5          | dB       |

| Response                                | LL11T2            | 1400                                 |                    | Re           | eference | <del>)</del> | dB       |

| SYNC = 11.025 kHz                       | LL11T3            | 4690                                 | 0                  | -0.5         | _        | 1.0          | dB       |

| LPF                                     | LL11T4            | 5470                                 |                    | 12           | _        | _            | dB       |

| Receive Frequency                       | LL8R1             | 300                                  |                    | -0.5         | _        | 0.5          | dB       |

| Response                                | LL8R2             | 1015                                 | _                  |              | eference | )            | dB       |

| SYNC = 8 kHz                            | LL8R3             | 3400                                 | 0                  | -0.5         | _        | 1.0          | dB       |

| LPF                                     | LL8R4             | 3970                                 |                    | 12           | _        |              | dB       |

| Dagoiya Fraguenay                       | LL11R1            | 300                                  |                    | -0.5         | _        | 0.5          | dB       |

| Receive Frequency<br>Response           | LL11R2            | 1400                                 |                    |              | eference |              | dB       |

| SYNC = 11.025 kHz                       | LL11R3            | 4690                                 | 0                  | -0.5         | I —      | 1.0          | dB       |

| LPF                                     | LL11R4            | 5470                                 |                    | 12           | _        | _            | dB       |

| Transmit S/N Ratio                      | SD8T1             | 0.1.0                                | 3                  | 35           | _        | _            | dB       |

| SYNC = 8 kHz (*3)                       | SD8T2             | f = 1015 Hz                          | -40                | 28           | _        | _            | dB       |

| Receive S/N Ratio                       | SD8R1             |                                      | 3                  | 35           |          |              | dB       |

| SYNC = 8 kHz (*3)                       | SD8R2             | f = 1015 Hz                          | -40                | 28           |          |              | dB       |

| Transmit S/N Ratio                      | SD16T1            |                                      | 3                  | 35           |          |              | dB       |

| SYNC = 16 kHz (*3)                      | SD16T2            | f = 1015 Hz                          | <del>-4</del> 0    | 28           |          |              | dB       |

| Receive S/N Ratio                       | SD16R1            |                                      | 3                  | 35           |          |              |          |

| SYNC = 16 kHz (*3)                      | SD16R2            | f = 1015 Hz                          | <del>-4</del> 0    | 28           |          | _            | dB<br>dB |

|                                         | <u> </u>          |                                      | 40<br>AIN- = SG    |              | _        | - 60         | dBm0pP   |

| Idle Channel Noise<br>SYNC = 8 kHz (*3) | N <sub>IDLT</sub> | _                                    |                    | _            | _        | -68          |          |

|                                         | N <sub>IDLR</sub> |                                      | (*4)               | _            | _        | -72          | dBm0pP   |

| Idle Channel Noise                      | N <sub>IDLT</sub> | _                                    | AIN- = SG          | _            | _        | -68          | dBm0pP   |

| SYNC = 16 kHz (*3)                      | N <sub>IDLR</sub> | 1015 11 (00)() 0)(110 - 0.111        | (*4)               |              | _        | -72          | dBm0pP   |

| Absolute Signal                         | A <sub>VT</sub>   | 1015 Hz(GSX) SYNC = 8 kHz            | 0                  | 0.285        | 0.320    | 0.359        | Vrms     |

| Amplitude (*5)                          | $A_{VR}$          | 1015 Hz(VFRO) SYNC = $8 \text{ kHz}$ | 0                  | 0.285        | 0.320    | 0.359        | Vrms     |

<sup>\*3:</sup> Use the P-message weighted filter

\*4: PCMRI input code "11111111" (μ-law)

\*5: 0.320 Vrms = 0 dBm0 = -7.7 dBm (600Ω)

# **Digital Interface**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -20 \text{ to } +70^{\circ}\text{C})$

| Parameter                                     | Symbol                              | Condition        | Reference            | Min. | Typ. | Max. | Unit |

|-----------------------------------------------|-------------------------------------|------------------|----------------------|------|------|------|------|

|                                               | t <sub>SDX</sub> , t <sub>SDR</sub> |                  |                      | 0    |      | 200  | ns   |

| Digital Input/Output Setting                  | t <sub>XD1</sub> , t <sub>RD1</sub> | 11 STTL : 100 pF | Fig. 3-1             | 0    | _    | 200  | ns   |

| Time                                          | $t_{XD2}, t_{RD2}$                  | 1LSTTL+100 pF    | Fig. 3-2             | 0    |      | 200  | ns   |

|                                               | t <sub>XD3</sub> , t <sub>RD3</sub> |                  |                      | 0    |      | 200  | ns   |

|                                               | t <sub>1</sub>                      |                  |                      | 50   | _    | _    | ns   |

|                                               | t <sub>2</sub>                      |                  |                      | 50   | _    | _    | ns   |

|                                               | t <sub>3</sub>                      |                  |                      | 50   | _    | _    | ns   |

|                                               | t <sub>4</sub>                      |                  |                      | 50   | _    | _    | ns   |

| 0 : 15 / 5: :: 11 //0 / /                     | t <sub>5</sub>                      |                  | Fig. 4-1<br>Fig. 4-2 | 100  |      | _    | ns   |

| Serial Port Digital Input/Output Setting Time | t <sub>6</sub>                      | $C_L=50 pF$      |                      | 50   | _    | _    | ns   |

| Cetting Time                                  | t <sub>7</sub>                      |                  | Fig. 4-2             | 50   | _    | _    | ns   |

|                                               | t <sub>8</sub>                      |                  |                      | 0    | _    | 50   | ns   |

|                                               | t <sub>9</sub>                      |                  |                      | 50   | _    | _    | ns   |

|                                               | t <sub>10</sub>                     |                  |                      | 50   |      | _    | ns   |

|                                               | t <sub>11</sub>                     |                  |                      | 0    |      | 50   | ns   |

| Shift Clock Frequency                         | f <sub>EXCK</sub>                   | EXCK             | EXCK                 |      | _    | 10   | MHz  |

# AC Characteristics (Programmable Gain Stages)

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

|               |                | , 55                                            |      | <u> </u> |      |      |

|---------------|----------------|-------------------------------------------------|------|----------|------|------|

| Parameter     | Symbol         | Condition                                       | Min. | Тур.     | Max. | Unit |

| Gain Accuracy | D <sub>G</sub> | All stages, to programmed value<br>SYNC = 8 kHz | -1   | 0        | +1   | dB   |

### **TIMING DIAGRAM**

# Transmit Side PCM/ADPCM Data Interface

### Receive Side PCM/ADPCM Data Interface

Figure 3-1 PCM/ADPCM Data Interface (Continuous BCLK)

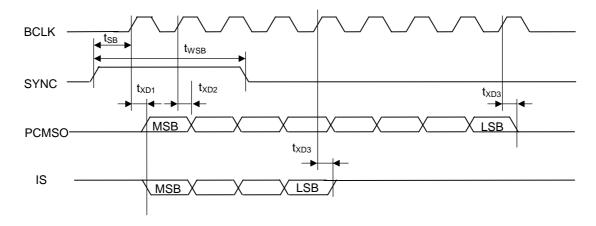

# Transmit Side PCM/ADPCM Data Interface

# **Receive Side PCM/ADPCM Data Interface**

Figure 3-2 PCM/ADPCM Data Interface (Burst Mode Clock)

# **Serial Port Data Transfer for MCU Interface**

Figure 4-1 Serial Control Port Interface (DIN = 12 bits)

Figure 4-2 Serial Control Port Interface (DIN = 16 bits)

#### **FUNCTIONAL DESCRIPTION**

### **Control Registers**

(1) CR0 (Basic operating mode setting)

|               | В7 | B6 | B5      | B4 | В3 | B2 | B1 | B0 |

|---------------|----|----|---------|----|----|----|----|----|

| CR0           | _  | _  | PDN ALL | _  | _  | _  | _  | _  |

| Initial Value | *  | *  | 0       | *  | *  | *  | *  | *  |

Note: Initial Value: Reset state by PDN (\*: Don't care)

B7, B6, B4 to B0: Not used (These pins are used to test the device. They should be set to "0" during normal operation.)

B5: Power-down (entire system); 0/Power-on, 1/Power-down

0 Red with the inverted external power-down signals.

When using this data, set the  $\overline{RDN}$  pin to "1".

(2) CR1 (ADPCM operating mode setting)

|               | В7    | В6    | B5       | B4       | В3      | B2      | B1 | В0     |

|---------------|-------|-------|----------|----------|---------|---------|----|--------|

| CR1           | MODE1 | MODE0 | TX RESET | RX RESET | TX MUTE | RX MUTE | 1  | RX PAD |

| Initial Value | 0     | 0     | 0        | 0        | 0       | 0       | *  | 0      |

B7, B6: ADPCM data compression algorithm select (output bit select);

(0, 0): 4-bit output (32 kbps)

(0, 1): 8-bit output (64 kbps)

(1, 0): 3-bit output (24 kbps)

(1, 1): 2-bit output (16 kbps)

Data rates in parentheses: when SYNC = 8 kHz

B5: ADPCM of transmit reset (specified by G.726); 1/Reset\*

B4: ADPCM of receive reset (specified by G.726); 1/ Reset\*

B3: ADPCM transmit data mute; 1/Mute

B2: ADPCM receive data mute; 1/Mute

B1: Not used (This pin is used to test the device. It should be set to "0" during normal operation.

B0: Receive side PAD; 1/inserted in the receive side voice path, 12 dB loss

0/no PAD

The transmit and receive sides cannnot be reset separately.

They must be reset at the same time.

<sup>\*</sup> The reset width should be  $1/f_{sample} \mu s$  or more.

# (3) CR2 (PCM CODEC operating mode setting and transmit/receive gain adjustment)

|               | В7        | В6       | B5       | B4       | В3           | B2       | B1       | В0       |

|---------------|-----------|----------|----------|----------|--------------|----------|----------|----------|

| CR2           | TX ON/OFF | TX GAIN2 | TX GAIN1 | TX GAIN0 | RX<br>ON/OFF | RX GAIN2 | RX GAIN1 | RX GAIN0 |

| Initial Value | 0         | 0        | 1        | 1        | 0            | 0        | 1        | 1        |

B7: Transmit PCM signal ON/OFF; 0/ON, 1/OFF

B6, B5, B4: Transmit signal gain adjustment, refer to Table 2.

B3: Receive PCM signal ON/OFF; 0/ON, 1/OFF

B2, B1, B0: Receive signal gain adjustment, refer to Table 2.

Table 2 Transmit/Receive Gain Setting (when SYNC = 8 kHz)

| B6 | B5 | B4 | Transmit Gain | B2 | B1 | В0 | Receive Gain |

|----|----|----|---------------|----|----|----|--------------|

| 0  | 0  | 0  | −6 dB         | 0  | 0  | 0  | −6 dB        |

| 0  | 0  | 1  | −4 dB         | 0  | 0  | 1  | –4 dB        |

| 0  | 1  | 0  | −2 dB         | 0  | 1  | 0  | −2 dB        |

| 0  | 1  | 1  | 0 dB          | 0  | 1  | 1  | 0 dB         |

| 1  | 0  | 0  | +2 dB         | 1  | 0  | 0  | +2 dB        |

| 1  | 0  | 1  | +4 dB         | 1  | 0  | 1  | +4 dB        |

| 1  | 1  | 0  | +6 dB         | 1  | 1  | 0  | +6 dB        |

| 1  | 1  | 1  | +8 dB         | 1  | 1  | 1  | +8 dB        |

### (4) CR3 (Side tone gain setting)

|               | В7                 | В6                 | B5                 | B4 | В3 | B2 | B1            | B0            |

|---------------|--------------------|--------------------|--------------------|----|----|----|---------------|---------------|

| CR3           | Side Tone<br>GAIN2 | Side Tone<br>GAIN1 | Side Tone<br>GAIN0 |    |    |    | HPF<br>8k/11k | HPF<br>ON/OFF |

| Initial Value | 0                  | 0                  | 0                  | *  | *  | *  | 0             | 0             |

B7, B6, B5: Side tone path gain setting. Refer to Table 3.

B4 to B2: Not used (These pins are used to test the device. They should be set to "0" during normal operation.)

Table 3 Side Tone Pash Gain Setting (when SYNC = 8 kHz)

| B7 | В6 | B5 | Side Tone Path Gain |

|----|----|----|---------------------|

| 0  | 0  | 0  | OFF                 |

| 0  | 0  | 1  | –21 dB              |

| 0  | 1  | 0  | –19 dB              |

| 0  | 1  | 1  | –17 dB              |

| 1  | 0  | 0  | −15 dB              |

| 1  | 0  | 1  | –13 dB              |

| 1  | 1  | 0  | –11 dB              |

| 1  | 1  | 1  | −9 dB               |

B1: Transmit HPF cut-off frequency select;

0/The cut-off frequency of the transmit HPF is the sampling frequency  $\times$  0.0275.

When SYNC = 8 kHz: 220 Hz, when SYNC = 11.025 kHz: 300 Hz.

The transmit frequency characteristics are not guaranteed when selecting SYNC = 11.025 kHz.

1/The cut-off frequency of the transmit HPF is the sampling frequency  $\times$  0.0200.

When SYNC = 8 kHz: 160 Hz, when SYNC = 11.025 kHz: 220 Hz.

The transmit frequency characteristics are not guaranteed when selecting SYNC = 8 kHz.

B0: Transmit HPF ON/OFF; 0/ON, 1/OFF

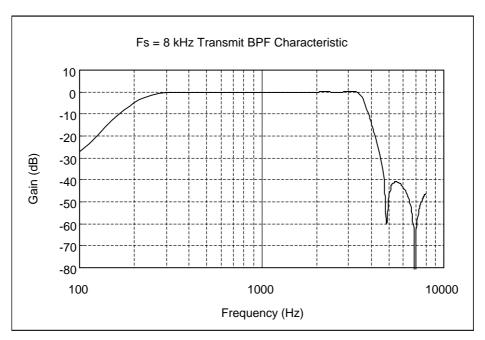

For the frequency characteristics, refer to Figures 9 to 12 in the Reference Data.

### **APPLICATION CIRCUIT**

### APPLICATION INFORMATION

#### **Burst Mode Clock**

This device can be operated by a burst mode clock (see below).

Figure 5 Example of Burst Mode Clock

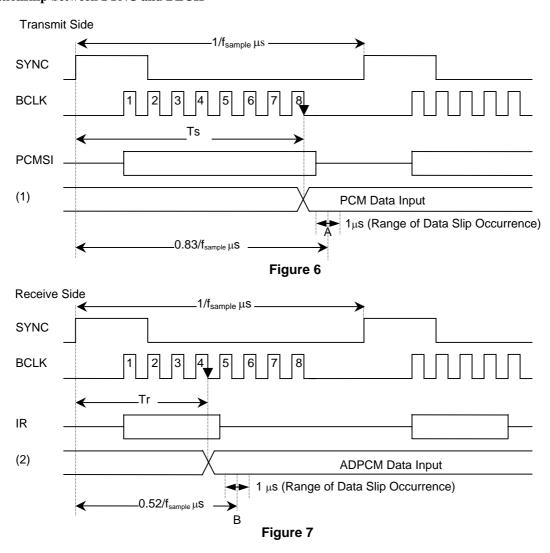

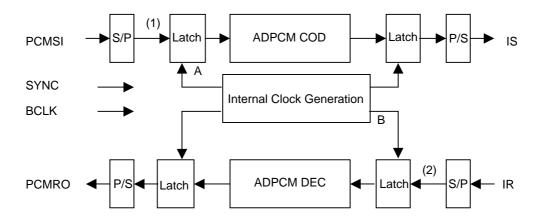

# Relationship between SYNC and BLCK

- (1): PCM data serial to parallel conversion output

- (2): ADPCM data serial to parallel conversion output

- A: (1) Data internal latch timing

- B: (2) Data internal latch timing

Figure 8

In this device, internal operating timing is generated according to the SYNC signal (see Figure 8). Therefore, a data slip may occur in the following timing when the PCM and ADPCM data is input.

- 1. When the PCM signal (PCMSI) is captured

If TS: PCM signal output (1) after serial/parallel conversion and A: internal latch timing in Figure 6 overlap, a

data slip occurs.

- 2. When the ADPCM signal (IR) is captured

If Tr: ADPCM signal output (2) after serial/parallel conversion and B: internal latch timing in Figure 7 overlap,

a data slip occurs.

The data slip occurs at the timing of 1 and 2 above. Therefore, taking internal clock jitters and IC internal delay into consideration, the timing of SYNC and BCLK signals should not be set up in the range of about 1  $\mu$ s from the timing A and B.

### REFERENCE DATA

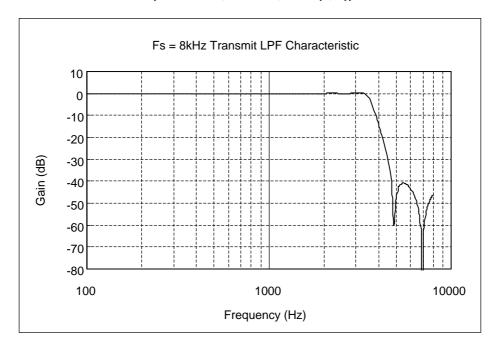

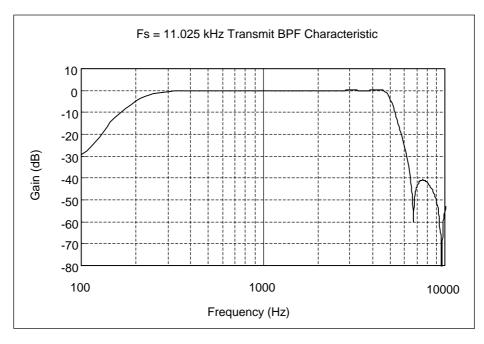

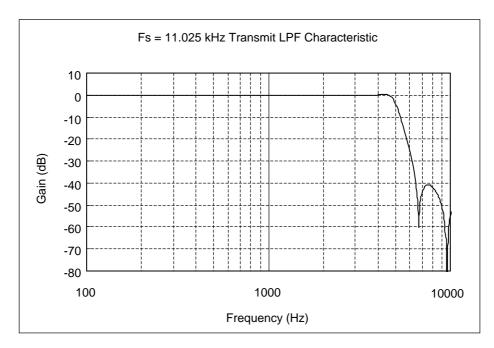

# **Transmit Frequency Characteristics**

Figure 9 Transmit Bandpass Filter Characteristic (Fs = 8 kHz, CR3-B1, B0 = (0, 0))

Figure 10 Transmit Lowpass Filter Characteristic (Fs = 8 kHz, CR3-B1, B0 = (0, 1))

Figure 11 Transmit Bandpass Filter Characteristic (Fs = 11.025 kHz, CR3-B1, B0 = (1, 0))

Figure 12 Transmit Lowpass Filter Characteristic (Fs = 11.025 kHz, CR3-B1, B0 = (1, 1))

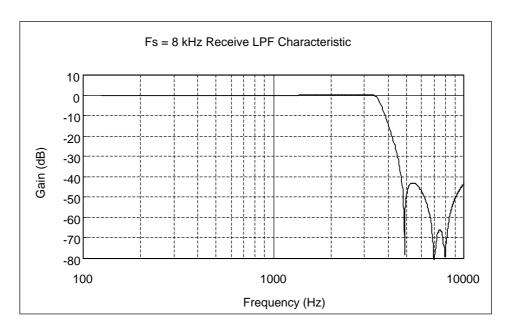

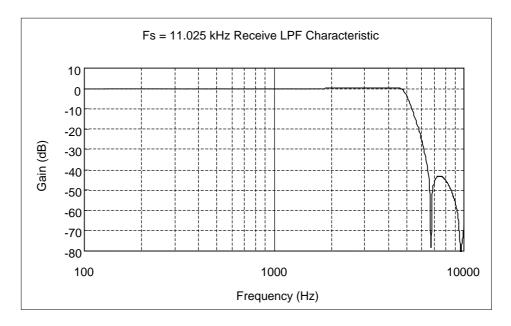

# **Receive Frequency Characteristics**

Figure 13 Receive Lowpass Filter Characteristic (Fs = 8 kHz, CR3-B1, B0 = (0, \*))

Figure 14 Receive Lowpass Filter Characteristic (Fs = 11.025 kHz, CR3-B1, B0 = (1, \*))

### **APPENDIX**

When the Sampling Frequency is 16 kHz or Higher:

This device enables the operation at 16 kHz or higher sampling frequencies under conditions below. However, be aware that the AC characteristics are not guaranteed under these conditions.

# Operating Conditions at Sampling Frequency = 19 kHz

|                                          |                   | T                     |                           |                |                      |      |

|------------------------------------------|-------------------|-----------------------|---------------------------|----------------|----------------------|------|

| Parameter                                | Symbol            | Condition             | Min.                      | Тур.           | Max.                 | Unit |

| Power Supply Voltage                     | $V_{DD}$          | Voltage must be fixed | 3.0                       | _              | 3.6                  | V    |

| Operating Temperature Range              | Ta                | _                     | -25                       | _              | +50                  | °C   |

| Digital Input High Voltage               | V <sub>IH</sub>   | Digital input pin     | 0.95 ×<br>V <sub>DD</sub> | _              | $V_{DD}$             | V    |

| Digital Input Low Voltage                | V <sub>IL</sub>   | Digital input pin     | 0                         |                | $0.05 \times V_{DD}$ | V    |

| Master Clock Frequency                   | f <sub>MCK1</sub> | MCK                   | _                         | 24.624         | _                    | MHz  |

| Master Clock Frequency Accuracy          | f <sub>MCK2</sub> | MCK                   | -0.01%                    | SYNC<br>× 1296 | +0.01                | MHz  |

| Sampling Frequency                       | f <sub>SYNC</sub> | SYNC                  | _                         | 19             | _                    | kHz  |

| Master Clock Duty Ratio                  | D <sub>MCK</sub>  | _                     | 40                        | _              | 70                   | %    |

| Transmit S/N Ratio (at 3 dBm0 input)     | SD19T1            | _                     |                           | 46.2           |                      | dB   |

| Transmit S/N Ratio (at –40 dBm0 input)   | SD19T2            | _                     |                           | 24.8           | l                    | dB   |

| Receive S/N Ratio<br>(at 3 dBm0 input)   | SD19R1            | _                     | _                         | 45.4           | _                    | dB   |

| Receive S/N Ratio<br>(at –40 dBm0 input) | SD19R2            | _                     |                           | 38.0           |                      | dB   |

# Operating Conditions at Sampling Frequency = 21 kHz

| Parameter                                | Symbol            | Condition             | Min.                      | Тур.           | Max.                      | Unit |

|------------------------------------------|-------------------|-----------------------|---------------------------|----------------|---------------------------|------|

| Power Supply Voltage                     | $V_{DD}$          | Voltage must be fixed | 3.3                       | _              | 3.6                       | V    |

| Operating Temperature Range              | Та                | _                     | -25                       | _              | +50                       | °C   |

| Digital Input High Voltage               | V <sub>IH</sub>   | Digital input pin     | 0.95 ×<br>V <sub>DD</sub> | _              | $V_{DD}$                  | V    |

| Digital Input Low Voltage                | V <sub>IL</sub>   | Digital input pin     | 0                         |                | 0.05 ×<br>V <sub>DD</sub> | V    |

| Master Clock Frequency                   | f <sub>MCK1</sub> | MCK                   | _                         | 27.216         | _                         | MHz  |

| Master Clock Frequency Accuracy          | f <sub>MCK2</sub> | MCK                   | -0.01%                    | SYNC<br>× 1296 | +0.01                     | MHz  |

| Sampling Frequency                       | f <sub>SYNC</sub> | SYNC                  | _                         | 21             | _                         | kHz  |

| Master Clock Duty Ratio                  | D <sub>MCK</sub>  | _                     | 40                        | _              | 70                        | %    |

| Transmit S/N Ratio (at 3 dBm0 input)     | SD19T1            | _                     |                           | 46.1           | _                         | dB   |

| Transmit S/N Ratio (at –40 dBm0 input)   | SD19T2            | _                     |                           | 20.2           |                           | dB   |

| Receive S/N Ratio<br>(at 3 dBm0 input)   | SD19R1            | _                     |                           | 44.8           | _                         | dB   |

| Receive S/N Ratio<br>(at –40 dBm0 input) | SD19R2            | _                     |                           | 37.8           | _                         | dB   |

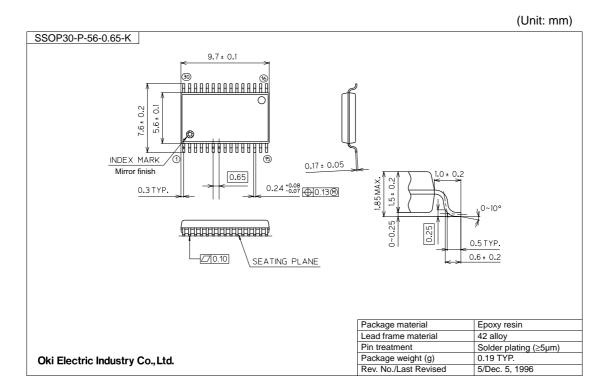

#### PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

|              | Date         | Page                |                    |                                                              |  |

|--------------|--------------|---------------------|--------------------|--------------------------------------------------------------|--|

| Document No. |              | Previous<br>Edition | Current<br>Edition | Description                                                  |  |

| FEDL7029-02  | Nov. 2001    | I – –               |                    | Final edition 2                                              |  |

|              |              | _                   | -                  | Final edition 3                                              |  |

| FEDL7029-03  | Feb.18, 2004 | 9                   | 9                  | Changed "Symbol" of Setup Time and Hold Time for PCM/ ADPCM. |  |

#### **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by Oki, authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace

- Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2004 Oki Electric Industry Co., Ltd.