DISC.C

# Single-Chip, Multiband 3G Femtocell

## Transceiver

# ADF4602

#### Rev. 0

df.dzsc.com

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No iterense is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tractements are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009 Analog Devices, Inc. All rights reserved.

## TABLE OF CONTENTS

| Features 1                                    |

|-----------------------------------------------|

| Applications1                                 |

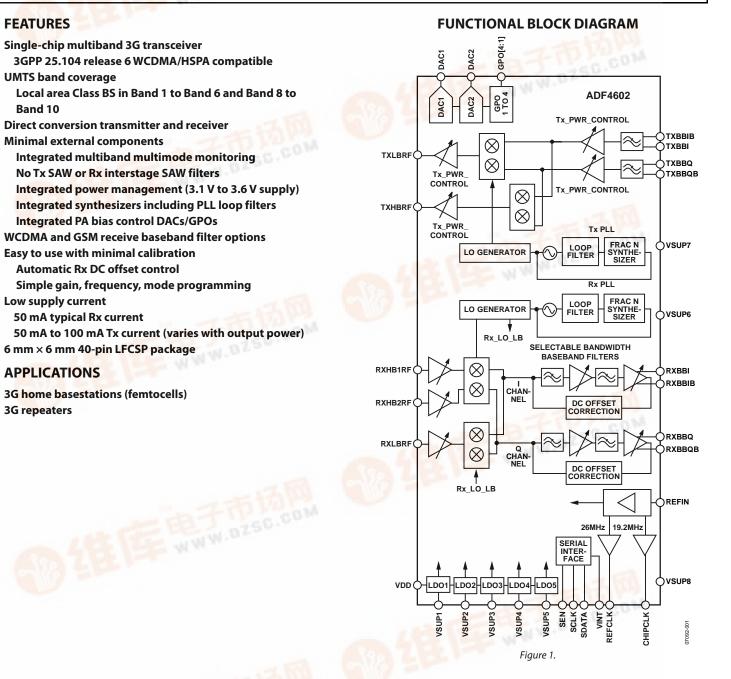

| Functional Block Diagram1                     |

| Revision History 2                            |

| General Description                           |

| Specifications 4                              |

| Timing Characteristics                        |

| Absolute Maximum Ratings9                     |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions10 |

| Typical Performance Characteristics12         |

| Theory of Operation17                         |

| Transmitter Description17                     |

| DACs                                          |

| General Purpose Outputs18                     |

| Receiver Description                  | 18 |

|---------------------------------------|----|

| Power Management                      | 21 |

| Frequency Synthesis                   | 22 |

| Serial Port Interface (SPI)           | 23 |

| Operation and Timing                  |    |

| Registers                             | 24 |

| Register Map                          | 24 |

| Register Description                  | 25 |

| Software Initialization Procedure     | 29 |

| Initialization Sequence               | 29 |

| Applications Information              |    |

| Interfacing the ADF4602 to the AD9863 |    |

| Outline Dimensions                    | 33 |

| Ordering Guide                        | 33 |

#### **REVISION HISTORY**

10/09—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The ADF4602 is a 3G transceiver integrated circuit (IC) offering unparalleled integration and feature set. The IC is ideally suited to high performance 3G femtocells providing cellular fixed mobile converged (FMC) services. With only a handful of external components, a full multiband transceiver is implemented.

UMTS Band 1 through Band 6 and Band 8 through Band 10 are supported in a single device.

The receiver is based on a direct conversion architecture. This architecture is the ideal choice for highly integrated wideband CDMA (WCDMA) receivers, reducing the bill of materials by fully integrating all interstage filtering. The front end includes three high performance, single-ended low noise amplifiers (LNAs), allowing the device to support tri-band applications. The single-ended input structure eases interface and reduces the matching components required for small footprint single-ended duplexers. The excellent device linearity achieves good performance with a large range of SAW and ceramic filter duplexers.

The integrated receive baseband filters offer selectable bandwidth, enabling the device to receive both WCDMA and GSM-EDGE radio signals. The selectable bandwidth filter, coupled with the multiband LNA input structure, allows GSM-EDGE signals to be monitored as part of a UMTS home basestation.

The transmitter uses an innovative direct conversion modulator that achieves high modulation accuracy with exceptionally low noise, eliminating the need for external transmit SAW filters.

The fully integrated phase lock loops (PLLs) provide high performance and low power fractional-N frequency synthesis for both receive and transmit sections. Special precautions have been taken to provide the isolation demanded by frequency division duplex (FDD) systems. All VCO and loop filter components are fully integrated.

The ADF4602 also contains on-chip low dropout voltage regulators (LDOs) to deliver regulated supply voltages to the functions on chip, with an input voltage of between 3.1 V and 3.6 V.

The IC is controlled via a standard 3-wire serial interface with advanced internal features allowing simple software programming. Comprehensive power-down modes are included to minimize power consumption in normal use.

## **SPECIFICATIONS**

$V_{DD}$  = 3.1 V to 3.6 V, GND = 0 V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical specifications are at  $V_{DD}$  = 3.3 V and  $T_A$  = 25°C, 26 MHz reference input level = 0.7 V p-p.

| Parameter                       | Min   | Тур  | Max   | Unit   | Test Conditions                                 |

|---------------------------------|-------|------|-------|--------|-------------------------------------------------|

| REFERENCE SECTION               |       |      |       |        |                                                 |

| Reference Input                 |       |      |       |        |                                                 |

| Reference Input Frequency       |       | 26   |       | MHz    |                                                 |

| Reference Input Amplitude       | 0.1   | 0.7  | 2.0   | V р-р  | Single-ended operation, dc-coupled <sup>1</sup> |

| REFCLK Output (26 MHz)          |       |      |       |        |                                                 |

| Output Load Capacitance         |       | 10   | 40    | pF     |                                                 |

| Output Swing                    |       | 1.5  |       | V р-р  | 10 pF load                                      |

| Output Slew Rate                |       | 200  |       | V/µs   | 10 pF load                                      |

| Output Duty Cycle Variation     |       | 2    |       | %      | Input duty cycle = 50%                          |

| CHIPCLK Output (19.2 MHz)       |       |      |       |        |                                                 |

| Output Load Capacitance         |       | 10   | 40    | pF     |                                                 |

| Frequency Multiplication Ratio  | 48/65 |      | 48/65 | N/A    |                                                 |

| Output Swing                    |       | 1.5  |       | V р-р  | 10 pF load                                      |

| Output Duty Cycle Variation     |       | 2    |       | %      | Input duty cycle = 50%                          |

| Output Jitter                   |       | 36   |       | ps rms |                                                 |

| Lock Time                       |       | 50   |       | μs     |                                                 |

| TRANSMIT SECTION                |       |      |       |        |                                                 |

| I/Q Input                       |       |      |       |        |                                                 |

| Input Resistance                |       | 100  |       | kΩ     | Single-ended                                    |

| Input Capacitance               |       | 2    |       | pF     | Single-ended                                    |

| Differential Peak Input Voltage |       | 500  | 550   | mV pd  |                                                 |

| Input Common-Mode Voltage       | 1.05  | 1.2  | 1.4   | V      |                                                 |

| Baseband Filter 3 dB Bandwidth  |       | 4.0  |       | MHz    |                                                 |

| TX Gain Control                 |       |      |       |        |                                                 |

| Maximum Gain                    |       | 5    |       | dB     | 1 V p-p differential baseband input             |

| Gain Control Range              |       | 60   |       | dB     |                                                 |

| Gain Control Resolution         |       | 1/32 |       | dB     | Average of LSB steps                            |

| Gain Control Accuracy           |       | 1.0  |       | dB     | Any 1 dB step                                   |

|                                 |       | 10   |       | dB     | Any 10 dB step                                  |

| Gain Settling Time              |       | 1    |       | μs     | Pout within 0.1 dB of final value               |

| RF Specifications (High Band)   |       |      |       |        |                                                 |

| Carrier Frequency               | 1710  |      | 2170  | MHz    |                                                 |

| Output Impedance                |       | 50   |       | Ω      |                                                 |

| Output Power (Pout)             |       | -8   |       | dBm    | TM1 signal 64 DPCH                              |

| Output Noise Spectral Density   |       | -155 |       | dBc/Hz | 40 MHz offset                                   |

|                                 |       | -161 |       | dBc/Hz | 80 MHz offset                                   |

|                                 |       | -161 |       | dBc/Hz | 95 MHz offset                                   |

|                                 |       | -163 |       | dBc/Hz | 190 MHz offset                                  |

| Carrier Leakage                 |       | -35  |       | dBc    | $P_{OUT} = -8 \text{ dBm}$                      |

| FDD EVM                         |       | 5    |       | %      | $P_{OUT} = -8 \text{ dBm}$                      |

| FDD ACLR                        |       | 55   |       | dB     | $\pm 5$ MHz, P <sub>OUT</sub> = $-8$ dBm        |

|                                 |       | 70   |       | dB     | $\pm 10 \text{ MHz}, P_{OUT} = -8 \text{ dBm}$  |

### 查询"ADF4602"供应商

| Parameter                        | Min  | Тур  | Мах  | Unit    | Test Conditions                                        |

|----------------------------------|------|------|------|---------|--------------------------------------------------------|

| RF Specifications (Low Band)     |      |      |      |         |                                                        |

| Carrier Frequency                | 824  |      | 960  | MHz     |                                                        |

| Output Impedance                 |      | 50   |      | Ω       |                                                        |

| Output Power (Pout)              |      | -6   |      | dBm     | TM1 signal 64 DPCH                                     |

| Output Noise Spectral Density    |      | -158 |      | dBc/Hz  | 45 MHz offset                                          |

| Carrier Leakage                  |      | -35  |      | dBc     | $P_{OUT} = -6 \text{ dBm}$                             |

| FDD EVM                          |      | 5    |      | %       | $P_{OUT} = -6 \text{ dBm}$                             |

| FDD ACLR                         |      | 55   |      | dB      | $\pm 5 \text{ MHz}, P_{OUT} = -6 \text{ dBm}$          |

| I DD ACEN                        |      | 70   |      | dB      | $\pm 10 \text{ MHz}, P_{00T} = -6 \text{ dBm}$         |

| ECEIVE SECTION                   |      | 70   |      | ub      | ±10 Mil2, F001 = -0 dBill                              |

| Baseband I/Q Output              |      |      |      |         |                                                        |

| Output Common Mode Voltage       | 1.15 | 1.2  | 1.35 | v       | Mode 1                                                 |

| Output Common Mode Voltage       |      |      |      |         |                                                        |

|                                  | 1.35 | 1.4  | 1.55 | V       | Mode 2                                                 |

| Differential Output Range        |      | 4    |      | V p-p d |                                                        |

| Output DC Offset                 |      | ±5   |      | mV      | WCDMA HPF mode                                         |

|                                  |      | ±100 |      | mV      | GSM servo loop mode                                    |

| Quadrature Gain Error            |      | 0.3  | 0.7  | dB      |                                                        |

| Quadrature Phase Error           |      | 1    |      | °rms    |                                                        |

| In-Band Gain Ripple              |      | 0.2  |      | dB      |                                                        |

| Low-Pass Filter Rejection        |      |      |      |         |                                                        |

| WCDMA (Seventh Order)            |      | 30   |      | dB      | @2.7 MHz                                               |

|                                  |      | 45   |      | dB      | @3.5 MHz                                               |

|                                  |      | 84   |      | dB      | @5.9 MHz                                               |

|                                  |      | 110  |      | dB      | @10 MHz                                                |

| WCDMA (Fifth Order)              |      | 14   |      | dB      | @2.7 MHz                                               |

|                                  |      | 31   |      | dB      | @3.5 MHz                                               |

|                                  |      | 55   |      | dB      | @5.9 MHz                                               |

|                                  |      | 80   |      | dB      | @10 MHz                                                |

| GSM                              |      | 12   |      | dB      | @200 kHz                                               |

| Com                              |      | 47   |      | dB      | @400 kHz                                               |

|                                  |      | 90   |      | dB      | @800 kHz                                               |

| Differential Group Delay         |      | 50   |      | ЧD      | (0000 KHZ                                              |

| WCDMA                            |      | 250  |      |         | 1.92 MHz band                                          |

| GSM                              |      | 200  |      | ns      | 100 kHz band                                           |

|                                  |      | 200  |      | ns      |                                                        |

| Receiver Gain Control            |      | 100  |      | 10      |                                                        |

| Maximum Voltage Gain             |      | 102  |      | dB      | WCDMA mode                                             |

| Gain Control Range               |      | 90   |      | dB      |                                                        |

| Gain Control Resolution          |      | 1    |      | dB      |                                                        |

| Gain Control Step Error          |      | ±1   |      | dB      | 1 dB step                                              |

|                                  |      | ±2   |      | dB      | 10 dB step                                             |

| RF Specifications (High Band)    | 1710 |      | 2170 |         |                                                        |

| Input Frequency                  | 1710 | 50   | 2170 | MHz     |                                                        |

| Input Impedance                  |      | 50   |      | Ω       |                                                        |

| Input Return Loss                |      | -20  |      | dB      |                                                        |

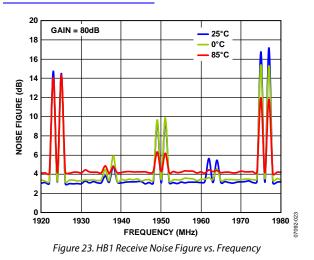

| Noise Figure                     |      | 4.0  |      | dB      | TX power of -8 dBm, spur-free measurement <sup>2</sup> |

| Maximum Input Power <sup>3</sup> |      |      | -20  | dBm     | Maximum LNA gain                                       |

|                                  |      |      | -2   | dBm     | Minimum LNA gain                                       |

| Input IP3                        |      | -7   |      | dBm     | ±10 MHz and ±20 MHz Offset, 59 dB gain                 |

|                                  |      | 0    |      |         | 85 MHz and 190 MHz Offset, 59 dB gain                  |

| Input IP2                        |      | 53   |      | dBm     | 80 MHz offset                                          |

|                                  |      | 65   |      | dBm     | 190 MHz offset                                         |

| EVM                              |      | 8    |      | %       | –60 dBm input                                          |

| Parameter                                         | Min                   | Тур  | Max  | Unit | Test Conditions                                            |

|---------------------------------------------------|-----------------------|------|------|------|------------------------------------------------------------|

| RF Specifications (Low Band)                      |                       |      |      |      |                                                            |

| Input Frequency                                   | 824                   |      | 960  | MHz  |                                                            |

| Input Impedance                                   |                       | 50   |      | Ω    |                                                            |

| Input Return Loss                                 |                       | -20  |      | dB   |                                                            |

| Noise Figure                                      |                       | 4.0  |      | dB   | 80 dB gain, TX power of –8 dBm                             |

| Maximum Input Power <sup>3</sup>                  |                       |      | -20  | dBm  | Maximum LNA gain                                           |

| ·                                                 |                       |      | -2   | dBm  | Minimum LNA gain                                           |

| Input IP3                                         |                       | 2    |      | dBm  | ±10 MHz and ±20 MHz offset, 59 dB gain                     |

| ·                                                 |                       | 5    |      | dBm  | 45 MHz and 90 MHz offset, 59 dB gain                       |

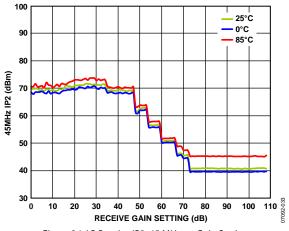

| Input IP2                                         |                       | 40   |      | dBm  | 45 MHz offset                                              |

| EVM                                               |                       | 7    |      | %    | –60 dBm input                                              |

| Synthesizer Section                               |                       |      |      | /-   |                                                            |

| Channel Resolution                                |                       | 50   |      | kHz  |                                                            |

| Lock Time <sup>3</sup>                            |                       |      | 200  | μs   |                                                            |

| DAC/GPO CONTROL                                   |                       |      | 200  | μ.,  |                                                            |

| DACI                                              |                       |      |      |      |                                                            |

| Resolution                                        |                       | 5    |      | bits |                                                            |

| Output Range                                      | 2.3                   | 5    | 3.15 | V    | V <sub>DD</sub> > 3.15 V                                   |

| Absolute Accuracy                                 | 2.5                   | ±50  | 5.15 | mV   | Any code, $V_{DD} > 3.2 V$                                 |

| Output LSB Step                                   |                       | 25   |      | mV   | Any code, vbb > 5.2 v                                      |

| Output Capacitive Load                            |                       | 25   | 1    | nF   |                                                            |

| Output Current                                    | -10                   |      | +10  | mA   |                                                            |

| Output Impedance                                  | -10                   | 1    | +10  | Ω    |                                                            |

| DAC2                                              |                       | I    |      | 12   |                                                            |

| Resolution                                        |                       | C    |      | bits |                                                            |

|                                                   |                       | 6    | 2.05 |      |                                                            |

| Output Range                                      | 0                     |      | 2.85 | V    | No load                                                    |

| DNL                                               |                       | ±0.5 |      | LSB  |                                                            |

| INL                                               |                       | ±1.0 |      | LSB  | No load                                                    |

| Output Capacitive Load                            | _                     |      | 1    | nF   |                                                            |

| Output Current                                    | -5                    | _    | +5   | mA   |                                                            |

| Output Impedance                                  |                       | 5    |      | Ω    |                                                            |

| GPO1 to GPO4                                      |                       |      | -    |      |                                                            |

| Output Current                                    |                       |      | 2    | mA   | GPO1, GPO2, GPO3                                           |

|                                                   |                       |      | 10   | mA   | GPO4                                                       |

| Output High Voltage                               | 2.6                   |      |      | V    | Maximum output current                                     |

| Output Low Voltage                                |                       |      | 0.2  | V    | Maximum output current                                     |

| Switching Time                                    |                       | 1    |      | μs   | 5 pF load                                                  |

| LOGIC INPUTS                                      |                       |      |      |      |                                                            |

| Input High Voltage, V <sub>INH</sub>              | 1.2                   |      | 2.1  | V    | 1.8 V readback mode <sup>4</sup>                           |

| Input High Voltage, V <sub>INH</sub>              | 1.2                   |      | 3.3  | V    | 2.8 V readback mode⁴                                       |

| Input Low Voltage, VINL                           |                       |      | 0.6  | V    |                                                            |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub> |                       |      | ±1   | μΑ   |                                                            |

| Input Capacitance, C <sub>IN</sub>                |                       |      | 10   | pF   |                                                            |

| LOGIC OUTPUTS (SDATA)                             |                       |      |      |      |                                                            |

| Output High Voltage, V <sub>он</sub>              | V <sub>x</sub> - 0.45 | 5    |      | V    | $V_X = VINT \text{ or } VSUP8, I_{OH} = 500 \ \mu\text{A}$ |

| Output Low Voltage, $V_{OL}$                      |                       |      | 0.45 | V    | $I_{OL} = 500 \ \mu A$                                     |

| CLKout Rise/Fall                                  |                       |      | 5    | ns   |                                                            |

| CLK <sub>out</sub> Load                           |                       |      | 10   | pF   |                                                            |

| TEMPERATURE RANGE (T <sub>A</sub> )               | 0                     |      | 85   | °C   |                                                            |

#### 查询"ADF4602"供应商

| Parameter                    | Min | Тур | Мах | Unit | Test Conditions                                                                                |

|------------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------|

| POWER SUPPLIES               |     | ·   |     |      |                                                                                                |

| Voltage Supply               |     |     |     |      |                                                                                                |

| VDD                          | 3.1 | 3.3 | 3.6 | V    | Main supply input                                                                              |

| VSUP1                        |     | 2.6 |     | V    | Output from internal LDO1, 10 mA rating, supply for RX VCO                                     |

| VSUP2                        |     | 2.8 |     | V    | Output from Internal LDO2, 30 mA rating,<br>supply for RX baseband and RX down-<br>converter   |

| VSUP3                        |     | 1.9 |     | V    | Output from internal LDO3, 10 mA rating, supply for RX LNAs                                    |

| VSUP4                        |     | 2.6 |     | V    | Output from internal LDO4, 10 mA rating, supply for TX VCO                                     |

| VSUP5                        |     | 2.8 |     | V    | Output from internal LDO5, 100 mA rating supply for TX modulator, TX baseband, PA control DACs |

| VSUP6                        |     | 1.9 |     | V    | Supply input for RX synthesizer, connect to VSUP3                                              |

| VSUP7                        |     | 1.9 |     | V    | Supply input for TX synthesizer, connect to VSUP3                                              |

| VSUP8                        |     | 2.8 |     | V    | Supply input for reference section, connect to VSUP2                                           |

| VINT                         | 1.6 | 1.8 | 2.0 | V    | Supply input for serial interface control logic                                                |

| CURRENT CONSUMPTION          |     |     |     |      |                                                                                                |

| Transmit Current Consumption |     |     |     |      | $V_{\text{DD}}{=}3.6\text{V},$ output is matched into 50 $\Omega$                              |

| –8 dBm Output Level          |     | 100 |     | mA   | $F_{RF} = 2170 \text{ MHz}$                                                                    |

| –28 dBm Output Level         |     | 50  |     | mA   | $F_{RF} = 2170 \text{ MHz}$                                                                    |

| Receive Current Consumption  |     | 50  |     | mA   |                                                                                                |

<sup>1</sup> The reference frequency should be dc coupled to the REFIN pin. It is ac-coupled internally.

<sup>2</sup> The noise figure measurement does not include spurious due to harmonics of the 26 MHz reference frequency. Spurs appear at integer multiples of the reference frequency (every 26 MHz), degrading the receive sensitivity by about 6 dB.

<sup>3</sup> Guaranteed by design, not production tested.

<sup>4</sup> Bit sif\_vsup8 in Register 2 controls whether 1.8 V readback mode or 2.8 V readback mode is selected. See the Serial Port Interface (SPI) section for more details.

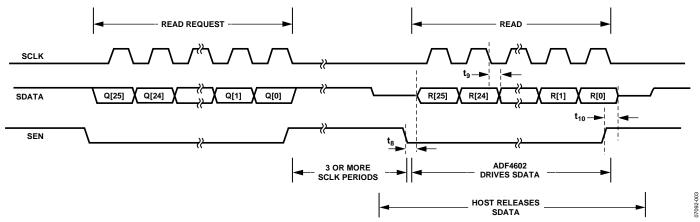

### **TIMING CHARACTERISTICS**

$V_{DD}$  = 3.1 V to 3.6 V, VGND = 0 V,  $T_A$  = 25°C, unless otherwise noted. Guaranteed by design but not production tested.

| Table 2.              |                                               |        |                             |  |  |  |

|-----------------------|-----------------------------------------------|--------|-----------------------------|--|--|--|

| Parameter             | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> | Unit   | Test Conditions/Comments    |  |  |  |

| t1                    | 62                                            | ns min | SEN high to write time      |  |  |  |

| <b>t</b> <sub>2</sub> | 10                                            | ns min | SEN to SCLK setup time      |  |  |  |

| t <sub>3</sub>        | 10                                            | ns min | SDATA to SCLK setup time    |  |  |  |

| t4                    | 10                                            | ns min | SDATA to SCLK hold time     |  |  |  |

| t <sub>5</sub>        | 31                                            | ns min | SCLK high duration          |  |  |  |

| t <sub>6</sub>        | 31                                            | ns min | SCLK low duration           |  |  |  |

| t7                    | 10                                            | ns min | SEN to SCLK hold time       |  |  |  |

| t <sub>8</sub>        | 20                                            | ns max | SEN to SDATA valid delay    |  |  |  |

| t9                    | 20                                            | ns max | SCLK to SDATA valid delay   |  |  |  |

| t <sub>10</sub>       | 20                                            | ns max | SEN to SDATA disabled delay |  |  |  |

Figure 3. Serial Interface Read/Write Diagram

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                          | Rating                |

|----------------------------------------------------|-----------------------|

| VDD to GND                                         | –0.3 V to +4 V        |

| VSUP1, VSUP2 to GND                                | –0.3 V to +3.6 V      |

| VSUP4, VSUP5, VSUP6, VSUP7,<br>VSUP8, VSUP9 to GND | –0.3 V to +3.6 V      |

| VSUP3 to GND                                       | –0.3 V to +2.0 V      |

| VINT to GND                                        | –0.3 V to +2.0 V      |

| Analog I/O Voltage to GND                          | –0.3 V to VDD + 0.3 V |

| Digital I/O Voltage to GND                         | –0.3 V to VDD + 0.3 V |

| Operating Temperature Range                        |                       |

| Commercial (B Version)                             | 0°C to +85°C          |

| Storage Temperature Range                          | −65°C to +125°C       |

| Maximum Junction Temperature                       | 150°C                 |

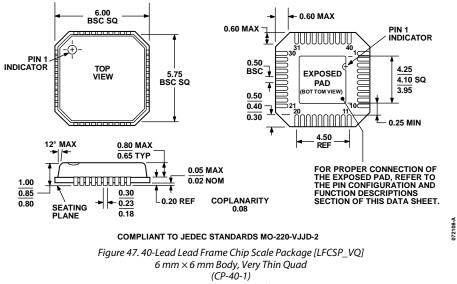

| LFCSP $\theta_{JA}$ Thermal Impedance              | 32°C/W                |

| Reflow Soldering                                   |                       |

| Peak Temperature                                   | 240°C                 |

| Time at Peak Temperature                           | 40 sec                |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device is a high performance RF integrated circuit with an ESD rating of <2 kV, and it is ESD sensitive. Proper precautions should be taken for handling and assembly.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

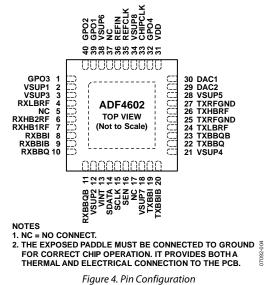

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic           | Function                                                                                                                                               |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GPO3               | General Purpose Output 3. Digital output. This is used for external switch or PA control.                                                              |

| 2       | VSUP1 <sup>1</sup> | Output from LDO 1. Supply for receive VCO. Nominal value of 2.6 V. 100 nF decoupling to ground is required.                                            |

| 3       | VSUP3 <sup>1</sup> | Output from LDO 3. Supply for receive LNA. Nominal value of 1.9 V. 100 nF decoupling to ground is required.                                            |

| 4       | RXLBRF             | Receive Low Band LNA Input.                                                                                                                            |

| 5       | NC                 | No Connect. Do not connect to this pin.                                                                                                                |

| 6       | RXHB2RF            | Receive Second High Band LNA Input. Should be used for Band 2.                                                                                         |

| 7       | RXHB1RF            | Receive First High Band LNA Input. Should be used for Band 1.                                                                                          |

| 8       | RXBBI              | Receive Baseband I Output.                                                                                                                             |

| 9       | RXBBIB             | Complementary Receive Baseband I Output.                                                                                                               |

| 10      | RXBBQ              | Receive Baseband Q Output.                                                                                                                             |

| 11      | RXBBQB             | Complementary Receive Baseband Q Output.                                                                                                               |

| 12      | VSUP2 <sup>1</sup> | Output from LDO 2. Supply for receive downconverter and baseband. Nominal value of 2.8 V. 100 nF decoupling to ground is required.                     |

| 13      | VINT               | Serial Port Supply Input. 1.8 V should be applied to this pin.                                                                                         |

| 14      | SDATA              | Serial Port Data Pin. This can be an input or output.                                                                                                  |

| 15      | SCLK               | Serial Clock Input.                                                                                                                                    |

| 16      | SEN                | Serial Port Enable Input.                                                                                                                              |

| 17      | NC                 | No Connect. Do not connect to this pin.                                                                                                                |

| 18      | VSUP7 <sup>1</sup> | Transmit Synthesizer Supply Input. Connect to VSUP3 and decouple with 100 nF to ground.                                                                |

| 19      | TXBBI              | Transmit Baseband I Input.                                                                                                                             |

| 20      | TXBBIB             | Complementary TX Baseband I Input.                                                                                                                     |

| 21      | VSUP4 <sup>1</sup> | Output from LDO4. Supply for transmit VCO. Nominal value of 2.8 V. 100 nF decoupling to GND is required.                                               |

| 22      | TXBBQ              | Transmit Baseband Q Input.                                                                                                                             |

| 23      | TXBBQB             | Complementary TX Baseband Q Input.                                                                                                                     |

| 24      | TXLBRF             | Low Band Transmit RF Output. This can output in the range of 824 MHz to 960 MHz.                                                                       |

| 25      | TXRFGND            | Transmit RF Ground. Connect this pin to ground.                                                                                                        |

| 26      | TXHBRF             | High Band Transmit RF Output. This can output in the range of 1710 MHz to 2170 MHz.                                                                    |

| 27      | TXRFGND            | Transmit RF Ground. Connect this pin to ground.                                                                                                        |

| 28      | VSUP5 <sup>1</sup> | Output from LDO 5. Supply for transmit modulator, baseband, power detector, and DACs. Nominal value of 2.8 V. 100 nF decoupling to ground is required. |

| 29      | DAC2               | Output from DAC2.                                                                                                                                      |

| 30      | DAC1               | Output from DAC1.                                                                                                                                      |

### 查询"ADF4602"供应商

| Pin No. | Mnemonic           | Function                                                                                                                                                 |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | VDD                | Main Supply Input.                                                                                                                                       |

| 32      | GPO4               | Digital Output. This is used for switch or PA control.                                                                                                   |

| 33      | CHIPCLK            | Chip Clock Output.                                                                                                                                       |

| 34      | VSUP8 <sup>1</sup> | Reference Clock Supply Input. Connect to VSUP2, and decouple to ground with 100 nF.                                                                      |

| 35      | REFCLK             | Reference Clock Output.                                                                                                                                  |

| 36      | REFIN              | Reference Clock Input. The reference is ac-coupled internally.                                                                                           |

| 37      | NC                 | No Connect. Do not connect to this pin.                                                                                                                  |

| 38      | VSUP6 <sup>1</sup> | Receive Synthesizer Supply Input. Connect to VSUP3 and decouple to ground with 100 nF.                                                                   |

| 39      | GPO1               | Digital Output. This is used for switch or PA control.                                                                                                   |

| 40      | GPO2               | Digital Output. This is used for switch or PA control.                                                                                                   |

|         | EPAD               | Exposed Paddle Under Chip. This must be connected to ground for correct chip operation. It provides both a thermal and electrical connection to the PCB. |

<sup>1</sup>Y5V capacitors are not recommended for use with these pins. X7R, X5R, C0G or a similar type of capacitor should be used.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

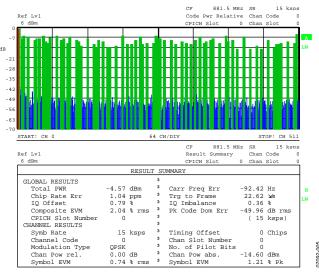

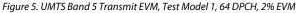

Figure 6. UMTS Band 1 Transmit EVM, Test Model 5, 2.5% EVM

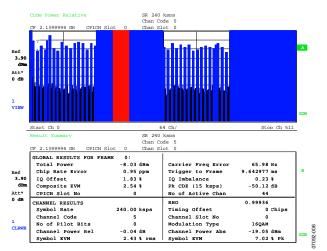

Figure 7.Transmit EVM vs. TXPWR\_SET (dBm), Measured Across 10 DUTS, Four Calibration Points Applied

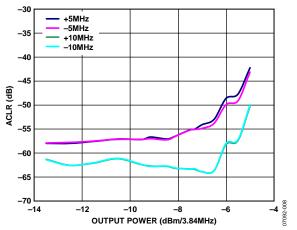

Figure 8. TXHBRF Transmit ACLR vs. Output Power, Test Model 1 Signal, 10.54 dB PAR, 217 MHz

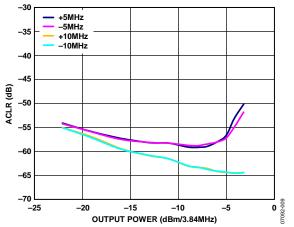

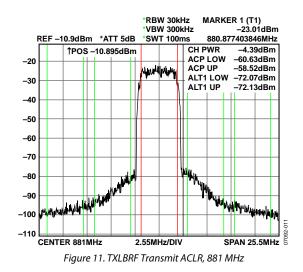

Figure 9. TXLBRF Transmit ACLR vs. Output Power, Test Model 1 Signal, 10.54 dB PAR, 881 MHz

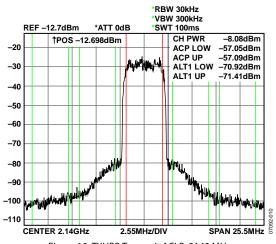

Figure 10. TXHBR Transmit ACLR, 2140 MHz

### ADF4602

#### 查询"ADF4602"供应商

-51 0°C 5MHz HIGH 0°C 5MHz LOW 25°C 5MHZ HIGH 25°C 5MHz LOW -53 85°C 5MHz HIGH 85°C 5MHz LOW -55 5MHz ACLR (dB) -57 -59 -61 -63 -65 2110 2120 2140 2150 2160 2130 2170 FREQUENCY (MHz)

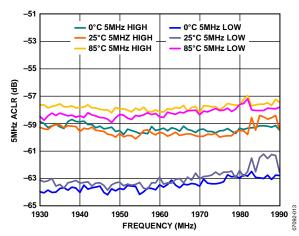

Figure 12. Transmit ACLR vs. Frequency and Temperature (Band 1), Transmit Output Power = -8 dBm

Figure 13. Transmit ACLR vs. Frequency and Temperature (Band 2), Transmit Output Power = -8 dBm

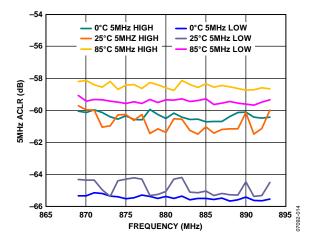

Figure 14. Transmit ACLR vs. Frequency and Temperature (Band 5), Transmit Output Power = -7 dBm

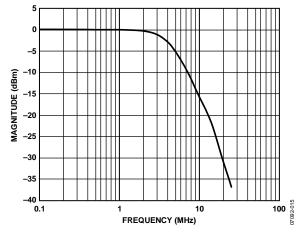

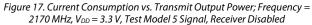

Figure 15. Transmit Baseband Filter Response

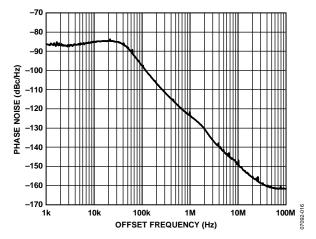

Figure 16. Transmit Synthesizer Phase Noise

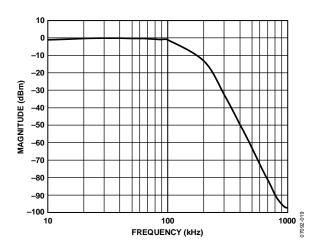

Figure 18. Receive WCDMA Baseband Filter Response

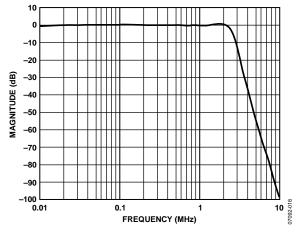

Figure 19. Receive GSM Baseband Filter Response

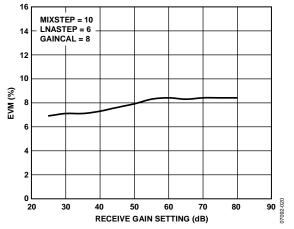

Figure 20. Receive EVM vs. Gain; 2.84 MHz QPSK Modulated Input Signal, WCDMA Receive Baseband Filter

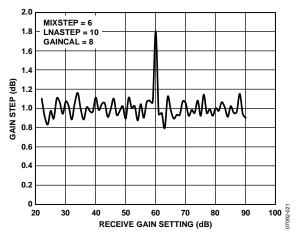

Figure 21. Receive Gain Step Error vs. Gain Setting, 1 dB Steps, Measurement was taken by injecting known signal level and measuring the gain through the device. The gain was then stepped through all settings in 1 dB steps, and the gain step change measured in each case.

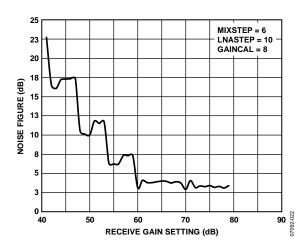

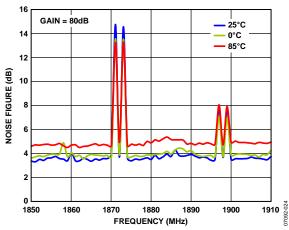

Figure 22. Receiver Noise Figure vs. Gain. Rx Frequency = 1955 MHz

## ADF4602

#### 查询"ADF4602"供应商

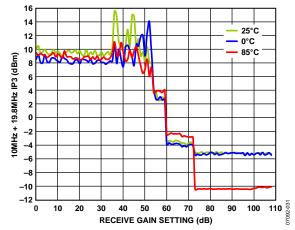

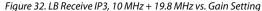

Figure 25. LB Receive Noise Figure vs. Frequency

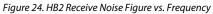

Figure 26. Receive Sensitivity vs. Frequency (See the Receive Sensitivity Section for More Details)

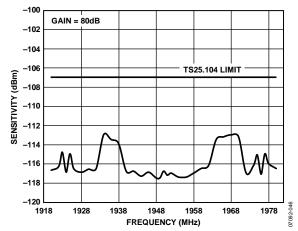

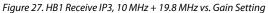

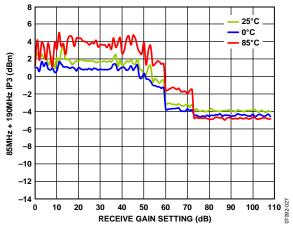

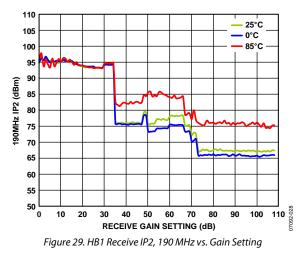

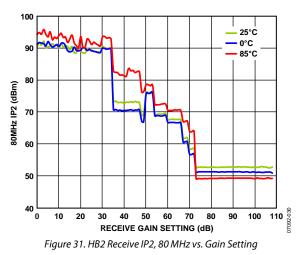

Figure 28. HB1 Receive IP3, 85 MHz + 190 MHz vs. Gain Setting

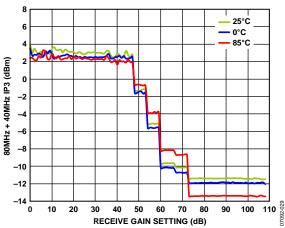

Figure 30. HB2 Receive IP3, 80 MHz + 40 MHz vs. Gain Setting

#### THEORY OF OPERATION **TRANSMITTER DESCRIPTION** TESTI, SWAP\_I тхвы с TXBBIB INTEGRATED BALUN LB ONLY DIVIDER ξ Σ ÷2 ÷2 ΤΧ Ουτρυτ DIVIDER AND QUAD GEN -90 DEGREES тхв TXBBQ O TXBBQB PF 11 TESTQ, SWAP\_Q GAIN CONTROL 7092-034 TXPWR\_SET[11:0] Figure 35. Transmitter Block Diagram

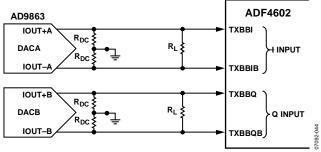

The ADF4602 contains a highly innovative low noise variable gain direct conversion transmitter architecture, that removes the need for external transmit SAW filters. The direct conversion architecture significantly reduces the risk of transmit harmonics across all bands due to the simplified nature of the frequency plan. See Figure 35 for a block diagram.

#### I/Q Baseband

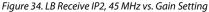

The baseband interface for the I and Q channels is a differential, dc-coupled input, supporting a wide range of input commonmode voltages ( $V_{CM}$ ). The allowable input common-mode range is 1.05 V to 1.4 V. The maximum signal swing allowed is 550 mV peak differential. This corresponds to a 1.1 V peak-to-peak differential on either the I or Q channel. Figure 36 shows a graphical definition of peak differential voltage and  $V_{CM}$ .

The baseband input signals pass through a second order Butterworth filter prior to the quadrature modulator. The cutoff frequency is 4 MHz. This gives some rejection of the DAC images. The filter also helps to suppress any spurious signals that might be coupled to the baseband terminals on the PCB.

For ease of PCB routing between the ADF4602 and the transmit DAC, the I and Q differential inputs can be internally swapped. For user test purposes, the I and Q inputs can also be internally shorted together and a dc offset applied. This produces a large carrier at the RF output, which is useful for signal path integrity testing.

Figure 36. Transmit Baseband Input Signals

#### I/Q Modulator

The I/Q modulator converts the transmit baseband input signals to RF. Calibration techniques are used to maintain accurate IQ balance and phase across frequency and environmental conditions, thus ensuring that 3GPP carrier leakage and EVM and ACLR requirements are met with good margin under all conditions. The on-chip calibrations are carried out during the transmit PLL lock time specified and are self-contained, requiring no additional input from the user.

The modulator has an 80 dB gain control range, programmable in 1/32 of a decibel step. The 12-bit word txpwr\_set[11:0] in Register 28 controls the transmit output power. The setting is referenced to a full-scale (500 mV peak differential) sine wave signal applied to the transmit baseband inputs. To calculate the output power when a WCDMA modulated signal with a certain peak-to-average ratio is applied, Equation 1 should be used.

Output Power (dBm/3.84 MHz) = txpwr(dBm) - PAR(dB) (1)

where txpwr(dBm) is the txpwr\_set[11:0] value converted to dBm, and *PAR* is the peak-to-average ratio of the WCDMA signal. For example, if an output power of -8 dBm is required for a WCDMA signal with a peak-to-average ratio of 10 dB

txpwr(dBm) = -8 dBm + 10 dB = +2 dBm

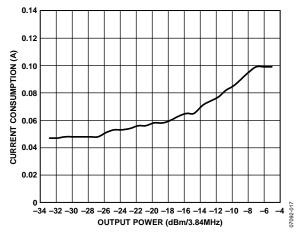

The current consumption of the modulator scales with output power. When the TX power is backed off from maximum, the transceiver benefits from lower power dissipation.

#### VCO Output

The TX VCO output is fed to a tuned buffer stage and then to the quadrature generation circuitry. The tuned buffer ensures that minimum current and LO related noise is generated in the VCO transport. This action is transparent to the user. The quadrature generator creates the highly accurate phased signals required to drive the modulator and also acts as a divide-by-2. In low band, an additional divide-by-2 is used in the VCO transport path, which is bypassed in high band. This is done to minimize the VCO tuning range required to cover all the bands.

The phase accuracy of the signals is important in ensuring good modulation quality and accurate output power. An on-chip calibration ensures that the phased signals are exactly 90° out of phase. This calibration runs each time the frequency is changed or if the txpwr\_set[11:0] word is written to. If the temperature of the device changes, this calibration should be updated. To run the calibration, the user should simply write to the txpwr\_set[11:0] word for each five degree change in temperature, or update the value regularly (every few seconds) between WCDMA frames or timeslots. This ensures that good EVM and accurate output power are maintained as the temperature of the device changes.

#### **TX Output Baluns**

The baseband input, modulator, and all associated circuitry are fully differential to maintain high signal integrity and noise immunity. However, a differential output is not optimal for the user because most power amplifiers (PAs) are singled-ended. This situation would normally require additional external matching components or a differential to single-ended SAW filter structure. With the ADF4602, the SAW filter is not necessary, and the required low loss balun is fully integrated, converting the differential internal signals to a single-ended 50  $\Omega$  output, thus allowing easy interfacing to the PA.

The high band output is available at the TXHBRF pin, and the low band output is available at the TXLBRF pin. These are directly connected to a 50  $\Omega$  load, if necessary, and do not require ac-coupling.

#### DACS

The ADF4602 integrates two DACs that are designed to interface to an external PA to control reference or bias nodes within the PA. If this function is not required, the DACs are used for any general purpose or powered down if not required.

DAC1 is a 5-bit voltage output DAC. The output range is from 2.3 V to 3.15 V (for  $V_{DD}$  > 3.15 V). The DAC1 output stage is supplied directly from VDD, with the capability to supply 10 mA of current to within 50 mV of  $V_{DD}$ . For high accuracy, the DAC reference is supplied from LDO5, which is internally trimmed to 25 mV accuracy. The DAC1 output is set by the PADAC1[4:0] word.

DAC2 is a 6-bit voltage output DAC with a range from 0 V to 2.8 V. LDO5 supplies both the reference voltage and full-scale output voltage for DAC2. The output voltage is set by the padac2\_ow[5:0] word. The dacgpo\_owen bit must also be set high if control of DAC2 is required.

Both DACS are powered down by writing the code, 0x0, to the respective control register.

#### **GENERAL PURPOSE OUTPUTS**

Four general-purpose outputs (GPOs) are provided on the ADF4602. These are used to control PA bias modes or, more commonly, the GPOs are used to control external RF front-end switches in the transmit/receive path. The GPOs are simple 3 V digital output drivers. GPO1 to GPO3 are capable of supplying a maximum current of 2 mA, whereas GPO4 can supply up to 10 mA.

For operation of the GPOs, Bit dacgpo\_owen must be set to 1. The GPOs are then controlled via the gpo\_ow[3:0] word.

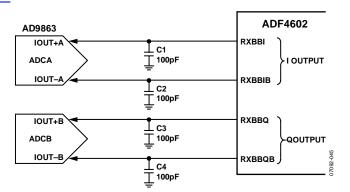

#### **RECEIVER DESCRIPTION**

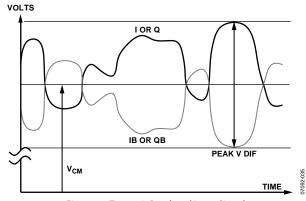

The ADF4602 contains a fully integrated direct conversion receiver designed for multiband WCDMA femtocell applications. High performance, low power consumption, and minimal external components are the key features of the design. Figure 37 shows a block diagram of the receiver, which consists of three LNA blocks for multiband operation, high linearity I/Q mixers, advanced baseband channel filtering, and a DC offset compensation circuit.

#### 查询"ADF4602"供应商

## ADF4602

Figure 37. Receiver Block Diagram

#### LNAs

The ADF4602 contains three tunable RF front ends suitable for all major 3GPP frequency bands. Two are suitable for high band operation in the region 1700 MHz to 2170 MHz. One is suitable for operation from 824 MHz to 960 MHz. Thus, the three integrated LNAs offer the designer the opportunity to create multiband and regional specific variants with no additional components.

LNA power control and internal band switching is fully controlled by the serial interface.

The ADF4602 LNAs are designed for 50  $\Omega$  single-ended inputs, thus further simplifying the front-end design and providing easy matching with minimal components. Typically, a two-component match is required: a series and shunt inductor. Within the LNA, the signal is converted to a differential path for signal processing in subsequent blocks within the receive signal chain.

Interstage RF filtering is fully integrated, ensuring that external out-of-band blockers are suitably attenuated prior to the mixer stages. The LNA characteristic is designed to provide additional filtering at the transmitter frequency offset.

The LNAs are enabled by programming bits rxbs[1:0] in Register 1. LNA input HB1 should be used for UMTS Band 1 operation, and HB2 should be used for UMTS Band 2 operation.

#### Mixers

High linearity quadrature mixer circuits are used to convert the RF signal to baseband in-phase and quadrature components. Although not shown in Figure 37, two mixer sections exist: one optimized for the high band LNA outputs and one optimized for the low band. The high band and low band mixer outputs are combined and then driven directly into the first stage of the baseband low-pass filter, which also acts to reduce the level of the largest blocking signals, prior to baseband amplification. Quadrature drive is provided to the mixers from the receiver synthesizer section by the VCO transport system, which includes a programmable divider, so that the same VCO is used for both high and low bands. Excellent 90° quadrature phase and amplitude match are achieved by careful design and layout of the mixers and VCO transport circuits.

#### **Baseband Section**

The ADF4602 baseband section is a distributed gain and filter function designed to provide a maximum of 54 dB gain with 60 dB gain control range. Through careful design, pass band ripple, group delay, signal loss, and power consumption are kept to a minimum. Filter calibration is performed during the manufacturing process, resulting in a high degree of accuracy and ease of use.

Three baseband filters are available on the ADF4602, as shown in Table 5. Bits rxbw\_toggle[2:0] are used to select the mode of operation. The seventh order WCDMA filter with 1.92 MHz cutoff ensures that good attenuation of the adjacent channel should be used to meet blocking/adjacent channel selection specifications in femtocell applications. The GSM filter has a 100 kHz cut-off and is intended for use as a monitoring receiver in a home base station. The fifth order WCDMA filter provides less attenuation of the adjacent channel, so it should not be used in femtocell applications.

The I and Q channels can be internally swapped, thus allowing optimum PCB routing between radio and analog baseband. This is achieved using the swapi and swapq bits.

#### Table 5. Receive Baseband Filter Modes

| Mode                | Filter Cutoff Frequency (fc) |

|---------------------|------------------------------|

| Seventh Order WCDMA | 1.92 MHz                     |

| Fifth Order WCDMA   | 1.92 MHz                     |

| GSM                 | 100 kHz                      |

The receive baseband outputs have a programmable common mode voltage of 1.2 V or 1.4 V, selectable via the vcmsel bit in Register 15.

#### **Gain Control**

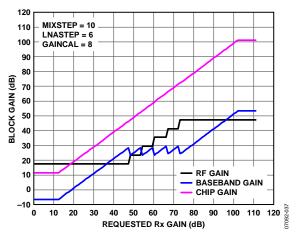

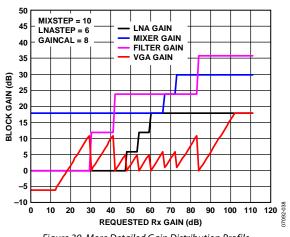

Gain control is distributed throughout the receive signal chain as shown in Figure 39. The RF front end contains 30 dB of control range: 18 dB in the LNA and 12 dB in the mixer transconductance stage. The two baseband active filter stages each provide 18 dB of gain control range in 6 dB steps. Filter characteristics (ripple and group delay) are best conserved if the active filter stages have equal gain. This results in a total of 36 dB gain control in  $4 \times 12$  dB steps for the filter stage. The variable gain amplifier (VGA) implements 24 dB of gain controllable in 1 dB steps. The base gain of the mixer is 18 dB, and the base gain of the VGA is -6 dB. This gives a total of 102 dB gain with 90 dB of gain control range.

The base gain of the mixer stage is 18 dB in WCDMA mode and 27 dB in GSM mode.

| Table 6. Receive Gain | <b>Control</b> in | WCDMA mode |

|-----------------------|-------------------|------------|

|-----------------------|-------------------|------------|

| Gain Control                                       | Control Steps                                                                          |

|----------------------------------------------------|----------------------------------------------------------------------------------------|

| 0 dB to +18 dB                                     | 3 × 6 dB steps                                                                         |

| +18 dB to +30 dB (WCDMA)<br>+27 dB to +39 dB (GSM) | 2 × 6 dB steps                                                                         |

| 0 dB to +36 dB                                     | $3 \times 12$ dB steps                                                                 |

| –6 dB to +18 dB                                    | 24 × 1 dB steps                                                                        |

|                                                    | 0 dB to +18 dB<br>+18 dB to +30 dB (WCDMA)<br>+27 dB to +39 dB (GSM)<br>0 dB to +36 dB |

To simplify programming and to ensure optimum receiver performance and dynamic range, the user simply programs the total desired receive gain in dB via the rx\_gain[6:0] bits in Register 11. The ADF4602 then decodes the gain setting and automatically distributes the gain between the various blocks. To allow some flexibility, predefined user inputs control the gain threshold points at which the LNA and mixer gain steps occur.

Bit settings mixstep[3:0] and lnastep[3:0] control the mixer and LNA gain threshold steps, respectively. An Excel spreadsheet detailing the receive gain decode system is available from Analog Devices, Inc., on request. Figure 38 shows an example gain distribution profile.

Figure 38. Gain Distribution Between RF and Baseband Blocks for Default Settina

In addition, a gain calibration setting in Register 15 (gaincal[4:0]) is used to account for losses in the RF front end.

The total gain in the ADF4602 is given by

$$ReceiveGain = rxgain[6:0] - gaincal[4:0] + X$$

(2)

where X = 8 in WCDMA filter mode, and X = 17 in GSM filter mode. Rxgain[6:0] is the receive gain programmed in Register 11. Gaincal[4:0] is the gain calibration setting in Register 15, and is calculated using the following formula:

$$gaincal[4:0] = 8 - front\_end\_losses$$

(3)

where front\_end\_losses is the loss in the receive path due to duplexers/switches. This is useful for referencing the programmed gain to the antenna and accounting for any losses in the path.

For example, if the total receive front-end loss is 2 dB, the user should program gaincal[4:0] to 6 dB. If the user then requestes 80 dB of gain by programming rxgain[6:0] to 80 dB, the ADF4602 uses Equation 4 to give

$$ReceiveGain = 80 - 6 + 8 = 82 \text{ dB}$$

(4)

82 dB is the receive gain used internally by the ADF4602.

## ADF4602

#### 查询"ADF4602"供应商

#### **DC Offset Compensation**

Due to the very high proportion of the total system gain assigned to the analog baseband function, compensating for dc offsets is an inherent part of any direct conversion solution. DC offsets are characterized as falling into two categories: static or slow varying and time varying

The ADF4602 architecture has been designed to reduce the amount of time varying dc offsets. The device also includes a dc offset control system. The control system consists of ADCs at the baseband output to digitize dc offsets: a digital signal processing block where the characteristics of the loop are programmed for customization of the loops transfer function, and trim DACs that are used to introduce the error term back into the signal path. The offset control transfer function can either be programmed to act as a servo loop that is automatically triggered by a gain change or as a high-pass filter (HPF) with an automatic fast settling mode that is also triggered by a gain change. Parameters of the servo loop, high-pass filter, and fast settling mode are set by the initial ADF4602 programming. In operation, the dc offset control system is fully automatic and does not require any external programming. Recommended default programming conditions for the dc offset compensation loop are shown in the Register Description section.

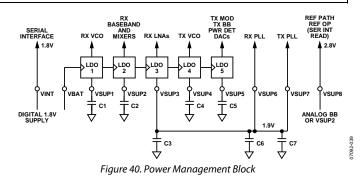

#### **POWER MANAGEMENT**

The ADF4602 contains integrated power management requiring two external power supplies: 3.3 V VDD and 1.8 V VINT. Figure 40 shows a block diagram.

VDD supplies the five integrated low drop-out regulators (LDOs), VSUP1 to VSUP5, that are used to supply the vast majority of the internal circuitry. VSUP6, VSUP7, and VSUP8 supply the receive PLL, transmit PLL, and reference block, respectively. These nodes require external connections to ensure good supply isolation and ensure a minimum level of interference between the PLL/reference blocks and the rest of the transceiver. VSUP6 and VSUP7 should be connected to VSUP3, whereas VSUP8 should be connected to VSUP2.

Each node, VSUP1 to VSUP8, should be externally decoupled to ground with a 0.1  $\mu$ F capacitor. Y5V capacitors are not recommended for use here. X7R, X5R, C0G, or a similar type of capacitor should be used.

VINT supplies the serial interface enabling register data preservation with minimum current consumption during power-down. This should be supplied with 1.8 V externally.

The five LDOs are individually powered up/down via bits ldoen[4:0] in Register 1. Table 7 summarizes the supply strategy.

Note that the reference path (VSUP8) supply is supplied from an external source or the internal VSUP2. The external supply option may be convenient so that the entire reference path can be shut down by collapsing a single supply.

VSUP8 can also be programmed to supply the voltage used for serial interface readback. See the Serial Port Interface (SPI) section for more information.

| Pin   | Connection        | Usage                                                                                  | Volts |

|-------|-------------------|----------------------------------------------------------------------------------------|-------|

| VINT  | External          | Serial interface control logic                                                         | 1.8 V |

| VDD   | External          | Main device supply,<br>DAC1                                                            | 3.3 V |

| VSUP1 | Internal LDO1     | Receive VCO                                                                            | 2.6 V |

| VSUP2 | Internal LDO2     | Receive baseband and down-converter                                                    | 2.8 V |

| VSUP3 | Internal LDO3     | Receive LNAs                                                                           | 1.9 V |

| VSUP4 | Internal LDO4     | Transmit VCO                                                                           | 2.6 V |

| VSUP5 | Internal LDO5     | Transmit baseband,<br>modulator, DAC2, and<br>GPOs                                     | 2.8 V |

| VSUP6 | Connect to VSUP3  | Receive synthesizer                                                                    | 1.9 V |

| VSUP7 | Connect to VSUP3  | Transmit synthesizer                                                                   | 1.9 V |

| VSUP8 | VSUP2 or external | Reference path,<br>reference buffer outputs;<br>Optional: serial interface<br>readback | 2.8 V |

#### Table 7. Power Management Strategy

#### **FREQUENCY SYNTHESIS**

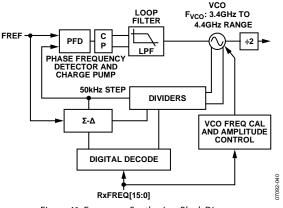

The ADF4602 contains two fully integrated programmable frequency synthesizers for generation of transmit and receive local oscillator (LO) signals. The design uses a fractional-N architecture for low noise and fast lock-time. The fractional-N functionality is implemented with a third order  $\Sigma$ - $\Delta$  modulator. Figure 41 shows a block diagram of the synthesizer architecture.

Figure 41. Frequency Synthesizer Block Diagram

All necessary components are fully integrated for both transmit and receive synthesizers, including loop filters, VCOs, and tank components. The VCOs run at 2× the high band frequency and 4× the low band frequency. The dividers are external to the synthesizer loop. This minimizes VCO leakage power at the desired frequency and tuning range requirements of the VCO. The VCOs use a multiband structure to cover the wide frequency range required.

The design incorporates both frequency and amplitude calibration to ensure that the oscillator is always operating with its optimum performance. The calibrations occur during the 200  $\mu s$  PLL lock time and are fully self contained, requiring no user inputs.

The charge pump and loop filter are internally trimmed to remove variations associated with manufacture and frequency. This process is fully automated.

To aid simplified programming, the ADF4602 contains a frequency decode table for the synthesizers, meaning the programmer is not concerned with the internal operation of the counters and fractional-N system. Frequency step sizes of 50 kHz are possible with both transmit and receive synthesizers. The programming words rxfreq[15:0] and txfreq[15:0] set the frequency in 50 kHz steps from 0 MHz to 3276.75 MHz. Note that the synthesizers do not cover this full range. The frequency range for each synthesizer in high and low bands is given in the Specifications section.

When the high band is enabled, the programmed frequency is equal to the LO frequency. For low band operation, the programmed frequency should be set to  $2\times$  the desired LO frequency.

The transmit and receive synthesizers are enabled by setting Bit txsynthen and Bit rxsynthen in Register 1, respectively.

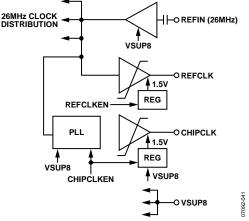

#### **Reference Path**

The ADF4602 requires a 26 MHz reference frequency input. A VCTCXO is used to provide this. The reference input is accoupled internally, so external ac coupling is not necessary.

The 26 MHz reference is internally buffered and distributed to the respective blocks, such as the synthesizer PFD inputs. Figure 42 shows a block diagram.

The ADF4602 provides two buffered outputs: a buffered version of the 26 MHz reference on Pin REFCLK and a 19.2 MHz WCDMA chip clock on Pin CHIPCLK. The 19.2 MHz chip clock is a multiple of the 3.84 MHz chip rate used in WCDMA. Thus, it can be used to clock ADCs/DACs elsewhere in the system. The chip clock is generated by an integrated PLL and contains no user settings.

Both outputs are slew rate limited and produce low swing digital outputs. The buffers contain their own 1.5 V regulator circuits to improve isolation and minimize unwanted supply noise. The 26 MHz and 19.2 MHz buffer outputs are enabled or disabled by programming Bit refclken and Bit chipclken (Register 1).

Figure 42. Reference Path Block Diagram

All reference sections are powered from VSUP8, which can safely be removed from the chip in isolation, to enter a low current power-down mode. Calibration data is not lost, but the reference frequency ceases to exist. As soon as VSUP8 is reapplied, oscillation begins. This is visible at the buffer outputs, as long as they were previously enabled.

### **SERIAL PORT INTERFACE (SPI)**

The ADF4602 contains internal registers that are used to configure the device. The three-wire serial port interface provides read and write access to the internal registers. For write, read requests, and read operations, 26-bit transfers are used. The MSB of all words are transferred first.

#### Format

Figure 43 shows the format of the register write. This consists of a 5-bit address and 16-bit data words. The exception is register A1 = 00000, where the lower data byte is used as an 8-bit subaddress. In total, this creates 31 16-bit registers and 256 8-bit registers. The 31 16 bit registers are referred to in the text as "Register 31" for example, while the 256 8-bit sub registers are referred to as "Register 0.144".

OP is a 2-bit code specifying the type of operation being performed (see Table 8 for more information). The chip select code, CS, is a 3-bit field indicating which device on the bus is being programmed. For the ADF4602, CS should be set to 001 (D2, D1, D0).

#### Table 8. SPI Operation Code

| OP[1] | OP[0] | Operation | Description                                                                                        |

|-------|-------|-----------|----------------------------------------------------------------------------------------------------|

| 0     | 0     | Write     | Normal register write.                                                                             |

| 0     | 1     | Set       | Register bits corresponding to 1s<br>in the data word are set. Other<br>bits are not modified.     |

| 1     | 0     | Clear     | Register bits corresponding to 1s<br>in the data word are cleared.<br>Other bits are not modified. |

| 1     | 1     | Read      | Register read request.                                                                             |

The read request format has the same address structure as the write format but does not contain a data field. Padding is used to maintain the 26-bit word length.

The readback format is the same as the word format during a write. Again, padding is used to maintain the 26-bit word length.

#### Table 9. SPI Chip Select Code

| CS[2]           | CS[1]   | CS[0] | Device   |

|-----------------|---------|-------|----------|

| 0               | 0       | 1     | ADF4602  |

| All other permu | tations |       | Reserved |

#### **OPERATION AND TIMING**

SCLK, SDATA, and SEN are used to transfer data into the ADF4602 registers. Data is clocked into the register, MSB, first on the rising edge of each SCLK. The data is transferred to the selected register address on the rising edge of SEN. See Figure 2 and Figure 3 for timing information.

#### Read

Figure 3 shows a read operation. First, a read request is written by the host to the ADF4602. SEN must remain high for at least three SCLK periods between the read request operation and the following read operation. The host must release the SDATA line during this period. The ADF4602 takes control of SDATA, and the read operation commences when the host device drives SEN low.

The SDATA output voltage during readback is set to 1.8 V or 2.8 V. Bit sif\_vsup8 (Register 2) controls this. A 0 in this bit configures the device to use the 1.8 V VINT supply, whereas a 1 configures the 2.8 V VSUP8 supply. After power-up or after a soft reset, the ADF4602 defaults to 2.8 V readback mode.

| ODEDATION                                   |    |    |    |                 |                    |      |    |   |                |                       |   | BI         | r PO        | sı | тіс                   | N  |             |                    |         |           |             |   |             |             |             |   |             |             |   | 1 |

|---------------------------------------------|----|----|----|-----------------|--------------------|------|----|---|----------------|-----------------------|---|------------|-------------|----|-----------------------|----|-------------|--------------------|---------|-----------|-------------|---|-------------|-------------|-------------|---|-------------|-------------|---|---|

| OPERATION                                   | 25 | 24 | 23 | 22              | 21                 | 20   | 19 | 1 | 8 17           | 16                    | 1 | 5 14       | 13          | 1  | 2                     | 11 | 10          | 9                  | 8       |           | 7           | 6 | 5           | 4           |             | 3 | 2           | 1           | 0 | 1 |

| WRITE<br>REGISTER 1 TO 31<br>W[25:0]        |    |    |    |                 |                    |      |    | _ | DATA<br>[15:0] |                       |   |            |             |    |                       |    |             |                    |         | DD<br>A1[ |             |   |             |             | OP<br>1:0   |   |             | CS<br>[2:0] | I |   |

| WRITE<br>REGISTER 0<br>W[25:0]              |    |    |    | DA<br>D[7       |                    |      |    |   |                |                       | S | UBAI<br>A2 | DR<br>[7:0] |    | s                     |    |             |                    |         | DD<br>I = |             |   |             | OP<br>[1:0] |             |   | CS<br>[2:0] |             |   |   |

| READ REQUEST<br>REGISTER 1 TO 31<br>Q[25:0] |    |    |    | M PAI<br>[15:0] | I PADDING<br>15:0] |      |    |   |                |                       |   |            | DD<br>A1[   |    |                       |    | OP<br>[1:0] |                    |         |           | CS<br>[2:0] | I |             |             |             |   |             |             |   |   |

| READ REQUEST<br>REGISTER 0<br>Q[25:0]       |    | RA | ND | ом<br>Р[7       |                    | DDIN | IG |   |                |                       | S | UBAI<br>A2 | DR<br>[7:0] |    | s                     |    |             | ADDRESS<br>A1[4:0] |         |           |             |   |             | OP<br>[1:0] |             |   |             | CS<br>[2:0] | I |   |

| READ<br>REGISTER 1 TO 31<br>Q[25:0]         |    |    |    |                 |                    |      |    | _ | DATA<br>[15:0] |                       |   |            |             |    | ADDRESS<br>A1[4:0]    |    |             |                    |         |           | OP = 11     |   |             |             | CS<br>[2:0] | I |             |             |   |   |

| READ<br>REGISTER 0<br>Q[25:0]               |    |    |    | DA<br>D[7       |                    |      |    |   |                | SUBADDRESS<br>A2[7:0] |   |            |             |    | ADDRESS<br>A1 = 00000 |    |             |                    | OP = 11 |           |             |   | CS<br>[2:0] |             |             |   |             |             |   |   |

Figure 43. SPI Register Write Format

# REGISTERS

**REGISTER MAP**

|    |     |     |      |              |               |     |    | GENERA     | L USER | REGISTER | RS   |      |               |      |               |                |                      |     |

|----|-----|-----|------|--------------|---------------|-----|----|------------|--------|----------|------|------|---------------|------|---------------|----------------|----------------------|-----|

| A1 | D15 | D14 | D13  | D12          | D11           | D10 | D9 | D8         | D7     | D6       | D5   | D4   | D3            | D2   | D1            | D0             | DEFAULT <sup>1</sup> | R/W |

| 1  |     |     | rxen | refclk<br>en | chipclk<br>en |     |    | Idoen[4:0] | 1      |          | txen | txbs | txsynth<br>en | rxbs | [1:0]         | rxsynth<br>en  | 0x2FFD               | w   |

| 2  |     |     |      |              |               |     |    |            |        |          |      |      |               |      | sif_<br>vsup8 | reset_<br>soft | 0x0002               | w   |

|    |     |        |         |     |        |       |        | RECEIVE | ER USER   | REGISTER | RS      |    |             |        |         |        |                      |     |

|----|-----|--------|---------|-----|--------|-------|--------|---------|-----------|----------|---------|----|-------------|--------|---------|--------|----------------------|-----|

| A1 | D15 | D14    | D13     | D12 | D11    | D10   | D9     | D8      | D7        | D6       | D5      | D4 | D3          | D2     | D1      | D0     | DEFAULT <sup>1</sup> | R/W |

| 10 |     |        |         |     |        |       |        | rxfreq  | [15:0]    |          |         |    |             |        |         |        | 0x9858               | w   |

| 11 |     |        |         |     |        |       |        |         |           |          |         | r  | xgain[6:0   | ]      |         |        | 0x0000               | w   |

| 12 |     | rfskip | o[3:0]  |     |        | sdme  | n[3:0] |         |           | mixste   | ep[3:0] |    |             | Inaste | ep[3:0] |        | 0x0FA6               | w   |

| 13 |     | osadc  | 2x[3:0] |     |        | nper  | 2[3:0] |         |           | nper     | 1[3:0]  |    |             | nper   | 0[3:0]  |        | 0x103E               | w   |

| 14 |     | nint3  | 8[3:0]  |     |        | nint2 | 2[3:0] |         |           | nint     | [3:0]   |    |             | nint(  | 0[3:0]  |        | 0xEE53               | w   |

| 15 |     |        |         |     | vcmsel | swapq | swapi  |         | rxbw[2:0] |          |         | ç  | jaincal[4:0 | )]     |         | sdmosr | 0x0890               | w   |

#### TRANSMITTER USER REGISTERS

| A1 | D15             | D14 | D13   | D12      | D11    | D10           | D9       | D8     | D7             | D6    | D5 | D4    | D3       | D2         | D1 | D0             | DEFAULT <sup>1</sup> | R/W |

|----|-----------------|-----|-------|----------|--------|---------------|----------|--------|----------------|-------|----|-------|----------|------------|----|----------------|----------------------|-----|

| 21 |                 |     |       | test_l/s | swap_l | test_Q/s      | swap_Q   |        | lanksel<br>:0] | cmmod |    |       | vcm_sat_ | thres[5:0] |    |                | 0x001F               | w   |