**DVB-T Demodulator**

## **CXD1968AR**

## **Description**

The CXD1968AR is a 4th generation product in a successful family of DVB-T channel decoders that conforms to the ETSI (EN) 300-744 standard and demonstrates exceptional performance in the current industry regional receiver specifications including Nordig 1.0.2 and IEC (MBRAI) requirements.

This state of the art demodulator provides a fully flexible interface compatible with a wide variety of RF tuner solutions from today's common High IF or Low IF architectures to future direct conversion ZIF systems. It offers options to address the cost/performance balance for a range of DVB-T applications from digital only to digital/analog hybrid systems. Advanced algorithms deliver optimal performance for each system configuration, while options to clock from a variety of tuner sources help to minimize system cost.

The highest technical performance is achieved through the implementation of advanced algorithms in synchronization and channel estimation, which result in robust decoding for challenging reception environments such as SFN's and portable reception. It also features an internal auto-acquisition controller that simplifies host software during scanning, and completely eliminates host software intervention during channel acquisition and recovery.

In summary, the CXD1968AR is a highly integrated DVB-T channel decoder that provides Sony's highest performance, most flexible configuration and design simplification for today's digital terrestrial receiver designs.

#### Applications:

- Digital terrestrial set top boxes

- Digital terrestrial PVRs and recordable DVD players

- Portable DVB-T receivers

- Terrestrial IDTV with digital only or hybrid tuner support

- ◆ PC-TV receiver modules

- DVB-T test equipment

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

- 1 - E06905-PS

#### **Features**

- ◆ Fully complies with the ETSI EN 300-744 standard for DVB-T. Operates with all guard intervals, code rates and hierarchical modes

- ◆ Performance designed to Nordig Unified 1.0.2, EBook, DTG, IEC 62002-1/2 and EICTA (MBRAI), and all existing regional DTT specifications

- ◆ Smart auto acquisition controller for minimal host software intervention

- ◆ Operates from low cost tuner reference clock (4 to 20MHz) or standard 20.48MHz crystal for 6, 7 and 8MHz channels

- ◆ High and Low IF input frequency mode compatibility. High IF operation with all common SAW filter frequencies

- ◆ Silicon tuner Zero IF interface support with DC offset, I/Q amplitude correction and I/Q phase imbalance correction

- ◆ Impulse noise cancellation algorithm compliant with DTG and IEC (MBRAI) specification requirements

- ◆ Optimized for SFN channels with pre-cursive or post-cursive echoes, inside or outside guard interval

- ◆ Advanced channel corrector for low multipath channel loss and enhanced time varying channel performance

- ◆ Dual high performance differential 10-bit ADCs

- ◆ Digital filtering for improved ACI protection

- ◆ Digital carrier recovery with ±857kHz carrier offset recovery range including up to 3×±1/6MHz transmitter offset

- ◆ Common Phase Error (CPE) correction

- ◆ Special features for fast 2K and 8K acquisition, including fast symbol number detection, automatic mode and guard detection

- ◆ Configurable parallel and serial MPEG2-TS interface with smoothing buffer

- ♦ Fast I<sup>2</sup>C compatible bus interface provides access to channel SNR, individual carrier SNR, constellation data and TPS data including cell identification bits

- ◆ Very Low operating power consumption (140mW typ.)

- ♦ Standby mode including "Ultra Low" shutdown mode which stops all activity including crystal oscillator to reduce interference with analog TV and multi-tuner input systems

- ◆ Quiet I<sup>2</sup>C output configuration for tuner control

- ◆ PWM outputs for external AGC control

- ◆ 5V tolerant inputs and outputs

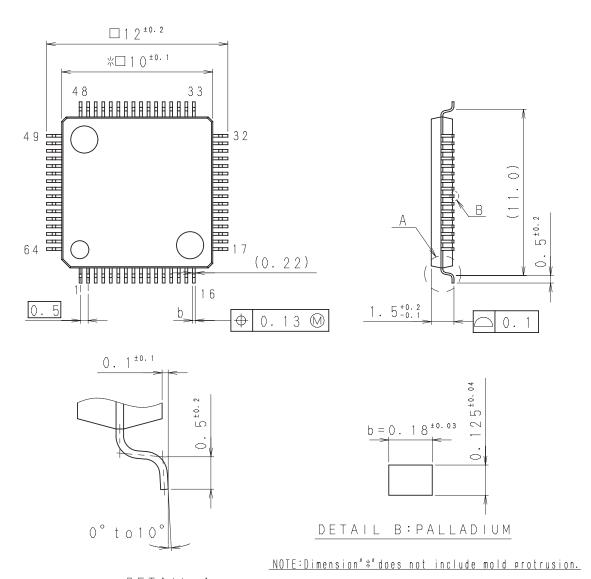

- ♦ 64-pin LQFP package

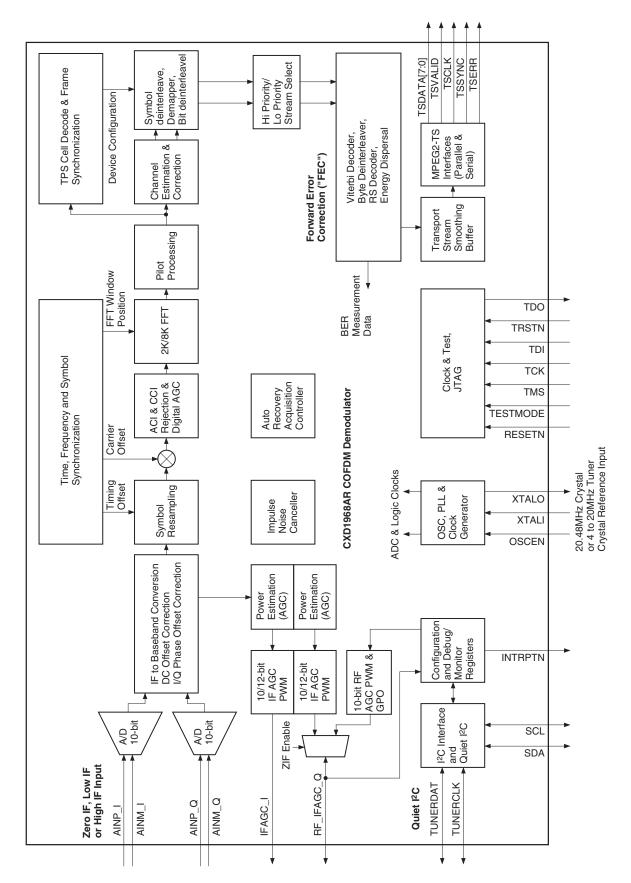

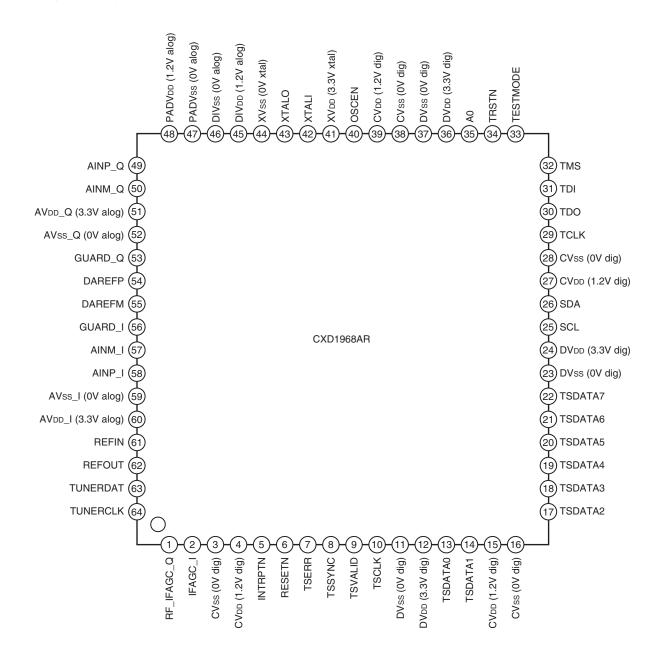

## 1. Block Diagram

Fig. 1. Block Diagram

## 2. Functional Description

The block diagram of the CXD1968AR is shown in Fig. 1.

#### ◆ Improvements over CXD1976R and CXD1973Q

The CXD1968AR incorporates some enhanced functionality over the CXD1976R. The following improvements offer performance benefits, system cost savings and simplify control of the device:

#### 1. Auto-recovery/acquisition controller

This easy to use hardware controller eliminates the processing load on the host processor software during acquisition and will reacquire the channel if the transport stream is lost. The demodulator registers are initialized by host software after power up/reset, then the controller is enabled. The controller automatically acquires the channel selected by the tuner, and continuously monitors for loss of TS or TPS lock and reacquires the channel if necessary. This functionality also reduces host software overhead for zapping, as the host processor need only write a new channel frequency to the tuner – the demodulator will automatically acquire the new channel. The controller can also reduce host processor overhead during channel scanning. Conventional host control of the demodulator is also possible by disabling the controller.

#### 2. Operation from a low cost tuner crystal reference

The CXD1968AR can be clocked from a standard 20.48MHz crystal (as in the CXD1976R) or from a tuner generated clock output, typically 4MHz, but can be in the range 4MHz to 20MHz by suitable programming of the PLL registers.

#### 3. Impulse noise cancellation

This block compensates for the effects of impulse noise detected in the incoming signal using a proprietary algorithm.

#### 4. Zero IF tuner interface

The CXD1968AR includes an optional Zero IF tuner interface to allow use of low cost silicon tuners. This interface includes several new blocks to handle typical signal impairments caused by the Zero IF tuning process:

#### I/Q amplitude imbalance correction (AGC)

Mismatches in the I and Q tuner signal paths can cause distortion of the I/Q signal. Dual AGC power estimation blocks individually monitor the I and Q input channels after the ADCs, and drive dual AGC amplifier PWM control outputs, allowing independent control of I and Q channel amplitudes in the tuner baseband amplifiers. The AGC gains of the I and Q channels can be read via I<sup>2</sup>C.

## I/Q phase quadrature imbalance correction (QIC)

Mismatches in the I/Q quadrature in the tuner local oscillator and signal paths can cause a uniform phase distortion of the I/Q signal across the band. This type of frequency independent I/Q phase imbalance can be corrected by this block. The detected I/Q phase imbalance can be read via I<sup>2</sup>C.

#### DC offset correction

DC offsets in the input signal are estimated and removed by this block. The detected DC offset can be read via I<sup>2</sup>C.

## 查询"CXD1968AR"供应商

## 5. improved ACI rejection

The Channel Selection Filter (CSF) provides additional rejection of adjacent channel interference, particularly in ZIF mode where there is reduced folding of ACI signals in-band during the ADC sampling process. This can reduce the complexity of the Zero IF tuner baseband filters.

### 6. Improved performance with echoes outside guard interval

The CXD1968AR includes improvements to allow pre-cursive or post-cursive echoes outside the guard interval, to meet the latest DTT specifications. This type of channel can occur in SFN networks.

#### 7. Improved time varying channel performance

Performance has been improved in doppler channels to meet the latest DTT specifications. The symbol synchronization algorithm has also been improved to handle "birth-death" echo fading that is more likely in portable reception applications.

#### 8. Improved reading of reserved TPS data

There are now separate "odd" and "even" banks of registers that latch the reserved TPS data including Cell-ID occurring on odd and even TPS frames. The length of the valid TPS data can also be read to determine whether Cell-ID and DVB-H signaling is present.

#### 9. Standby power saving mode

The standby power has been reduced further. The design can enter and exit standby mode by I<sup>2</sup>C control. The crystal or clock input is kept running in this mode.

#### 10. Shutdown power saving mode

This is a very low power mode, where the crystal oscillator or clock input is stopped by the host processor setting the OSCEN input signal to logic 0. This prevents any clock/oscillator interference affecting analog TV reception.

## 查询"CXD1968AR"供应商 ◆ COFDM Demodulator Core

The main processing functions are;

#### 10-bit ADC

#### IF Input Mode

Input to the CXD1968AR is a differential IF signal centered at either 4.57MHz or nominally 36.167MHz. The exact IF frequency can be set via the ITB\_FREQ\_1 and ITB\_FREQ\_2 registers. An integrated 10-bit A/D converter clocked at 20.48MHz is used to sample the IF signal. Input amplitude is nominally 1V peak-to-peak differential, but can also be set to 0.7V, 1.5V, or 2V peak-to-peak differential using I<sup>2</sup>C registers.

#### Zero IF (ZIF) Input Mode

The I channel uses the same ADC described above for IF input signals. A second 10-bit ADC is used for the Q channel input. Both ADCs sample at 20.48MHz. Input amplitude is nominally 1V peak-to-peak differential, but can also be set to 0.7V, 1.5V, or 2V peak-to-peak differential using I<sup>2</sup>C registers.

#### **Power Estimation (AGC)**

#### IF Mode

This block monitors the signal level at the output of the ADC and provides a Pulse Width Modulated (PWM) control signal to drive an external (analog) variable gain amplifier (VGA) in the tuner IF stage. This circuit operates as an automatic gain control loop and is normally configured to maximize ADC dynamic range determined by a fixed AGC target value. The enhanced AGC system modifies the AGC gain according to the characteristics of the received channel in order to better cope with interferers. The AGC output voltage is generated as a PWM signal and requires a simple external single pole RC filter to interface with the AGC system. The AGC gain value applied to the external amplifier can be read via a register to assist software RF AGC algorithms.

#### Zero IF (ZIF) Input Mode

In ZIF input mode, both the I and Q channels are monitored independently, each driving a separate PWM control signal (IFAGC\_I, RF\_IFAGC\_Q) to allow separate tuner AGC amplifiers to correct for I/Q amplitude imbalances. Other features are similar to IF-mode AGC described above.

## **Automatic Gain Control – External RF**

This block provides an additional Pulse Width Modulated (PWM) control signal (RF\_IFAGC\_Q) to drive the variable gain amplifier (VGA) in the tuner RF stage. The output value is set by an I<sup>2</sup>C register. This feature is only available in IF input mode. In ZIF mode this pin is used by the Q channel AGC PWM output.

#### General-purpose I/O Port

The RF AGC pin can be configured to generate a logic level signal in place of the PWM output. This may be used for SAW switching, test output or other user-defined purpose. Alternatively this pin can be programed as a digital input, readable by I<sup>2</sup>C. The above features are only available in IF input mode. In ZIF mode this pin is used by the Q channel AGC PWM output.

## IF to Baseband Conversion (ITB)

This block translates the received digitized IF signal to complex baseband. Subsequent processing is performed on the complex baseband samples. This block is not used in ZIF input mode.

## 查询"CXD1968AR"供应商

#### Symbol Resampling (ITP)

This block resamples the complex baseband data to compensate for errors between the transmitter clock and ADC sampling clock frequency thus ensuring the FFT block receives the correct number of samples per OFDM symbol. An all-digital resampling technique is used which eliminates the cost and stability issues associated with internal or external VCXOs. The timing offset can be read from an I<sup>2</sup>C register allowing external monitoring or control.

### Frequency Synchronization Loop (CRL)

The frequency synchronization loop compensates for intentional transmitter carrier frequency offsets and tuner local oscillator frequency error inherent in the RF to IF conversion process. An all-digital AFC technique estimates the frequency shift using the pilots in the OFDM signal and derotates the I/Q constellation before the FFT process. Frequency offset information can be read from an I²C register. This information may be extracted during a channel scan and subsequently applied to the tuning when pre-selecting (zapping) a channel. The offset range can be programed to allow faster acquisition to broadcast channels even beyond  $3 \times \pm 166 \text{kHz}$  transmitter offset. Scanning under software control is simplified using the extended acquisition range.

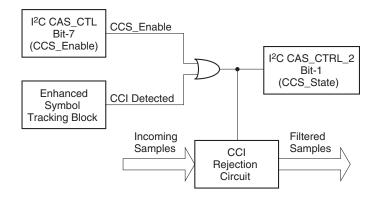

#### ACI and CCI Rejection and Digital AGC (CSF + CAS)

These blocks filter any residual adjacent channel interference such as NICAM energy leaking through the edges of the SAW filter. The CCI filter can optionally cancel co-channel interference such as vision carrier of an analog TV signal. Digital AGC is also performed to restore a consistent signal after filtering. The CCI filter is automatically applied in the presence of analog co-channel interference, resulting in optimum performance for the received channel. The CSF block provides extra adjacent channel rejection, particularly in ZIF mode where there is reduced folding in-band of ACI signals.

#### **COFDM Symbol Synchronization Block (SYR)**

This block acquires and tracks the position of the FFT sampling window within the OFDM symbol, to allow the FFT to recover the useful carriers including pilot tones with minimal ISI. This block can be programed to perform a fast detection of the guard time interval and mode without using TPS, reducing acquisition time. Alternatively a specific mode and guard configuration can be programed also reducing acquisition times for known channels.

The CXD1968AR utilizes a new tracking algorithm which improves symbol tracking in multipath channels, particularly beneficial for reception of SFN broadcasts where there can be echoes outside the guard interval. The algorithm permits acquisition and tracking of pre-cursive and post-cursive echo delays inside and outside the guard interval, and also automatically tracks the "birth" and "death" of echoes occurring at different delays, even if the delay of the main echo path changes. The tracker contains automatic CCI detection and filter selection further optimizing channel reception.

#### **FFT Processor**

This block performs a 2048 or 8192 point FFT on the derotated I/Q samples.

#### Pilot Processing and Common Phase Error (CPE) Correction (SCR and PPM)

This block corrects for the phase slope and common phase error present on the carriers due to the FFT trigger point being chosen to minimize ISI. A fast acquisition mode can be programed to allow the device to start outputting transport stream data before a full superframe has been received.

#### **Channel Estimation**

This block estimates a time varying channel frequency response using the pilot carriers embedded in every COFDM symbol. This estimate is then interpolated in the frequency domain and used to correct each of the individual OFDM carriers in the CHC block. This block also estimates the signal and noise power for each carrier, which is used as a reliability estimate to weight the soft decisions of each bit fed to the Viterbi decoder. This feature helps to improve PAL CCI performance where vision and sound carriers can distort nearby COFDM carriers.

## 查询"CXD1968AR"供应商

#### **Channel Correction (CHC)**

This block uses the estimated channel frequency response to equalize the carriers against frequency selective attenuation in the channel.

#### TPS Cell Decode and Frame Synchronization (TPS)

The Transmission Parameter Signaling (TPS) pilots convey information used to configure the receiver and delimit the COFDM frame boundaries. This block decodes the TPS pilot carriers and generates frame synchronization signals. All the TPS information (shown below) is readable via I<sup>2</sup>C registers.

- ◆ Length indicator Needed to read Cell-ID and reserved TPS bits

- ◆ Frame number within superframe (0-3)

- ◆ Constellation (QPSK, 16QAM, 64QAM)

- lacktriangle Hierarchy information (non-hierarchical,  $\alpha$  = 1,  $\alpha$  = 2,  $\alpha$  = 4)

- ◆ High priority stream code rates (1/2, 2/3, 3/4, 5/6, 7/8)

- ◆ Low priority stream code rates (1/2, 2/3, 3/4, 5/6, 7/8)

- ◆ Guard interval (1/32, 1/16, 1/8, 1/4)

- ◆ Transmission mode (2K, 8K)

- ♦ All TPS bits reserved for future use (S40-S53), such as Cell ID and DVB-H indicator bits

#### Symbol Deinterleaver (SDI)

The transmitter interleaves the QAM symbols to ensure that a given QAM symbol is mapped to a different carrier in each COFDM symbol, to avoid a succession of errors at the Viterbi decoder input due to frequency selective attenuation involving several adjacent carriers. The symbol deinterleaver deinterleaves the corrected carriers from the channel estimation and correction blocks together with the reliability information.

#### Symbol Demapper (DMP)

The demapper processes the complex symbols and reliability information issued from the symbol deinterleaver, generating weighted soft decision information for each bit.

### Bit Deinterleaver (BDI)

Depending upon the QAM level used, the transmitter splits up the input data bits into 2, 4 or 6 streams which are then interleaved to ensure that consecutive input data bits are not mapped to the same QAM symbol. The bit deinterleaver reverses this process by deinterleaving the soft decision information for each bit from the Symbol Demapper. In hierarchical mode, this block outputs a high priority and low priority bit stream. In non-hierarchical mode, a single bit stream is output.

### Low/High Priority Stream Select

For hierarchical transmissions, this block selects (via an I<sup>2</sup>C register) either the high priority or low priority transport stream for processing by the remainder of the decoder as shown in Fig. 2.

SONY

## 查询"CXD1968AR"供应商

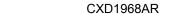

#### ◆ Forward Error Corrector (FEC)

Fig. 2. FEC Block Diagram (Viterbi decoder to transport stream output only)

#### Viterbi Decoder (VIT)

The Viterbi decoder uses the weighted soft decision data to perform a maximum likelihood estimation of each received bit. All code rates in the ETSI (EN) 300 744 standard are supported. Bit error rates at the input and output of this decoder can be monitored via the I<sup>2</sup>C bus. The serial bit stream output of the decoder is converted into byte wide format by a serial to parallel converter before it is passed to the byte deinterleaver.

#### **Sync Byte Lock Detection**

This block detects the MPEG2-TS sync bytes or inverted sync bytes at the output of the Viterbi decoder in order to ensure correct synchronization of the byte deinterleaving and correct identification of the inverted sync bytes.

#### **Byte Deinterleaver**

This block implements standard DVB compatible Forney type convolutional deinterleaving (I = 12, N = 204, M = 17, where M = N/I). Burst errors are split up across multiple MPEG2-TS packets, which increases the probability of successful Reed-Solomon error correction.

#### **Reed-Solomon Decoder**

This block is a DVB compatible (255,239) Reed-Solomon decoder implementing the standard DVB shortened (204,188) code using a (GF generation polynomial  $p(x) = x^8 + x^4 + x^3 + x^2 + 1$ ) to correct up to t = 8 erroneous bytes per MPEG2-TS packet. R/S decoding errors occurring when more than 8 bytes are in error are used to calculate error statistics, and are also signaled on the MPEG2-TS interface TSERR signal.

#### **Transport Stream Lock Detection and Sync Byte Inversion**

This block detects the MPEG2-TS sync bytes and inverted sync bytes after correction by the R/S decoder in order to provide a more resilient lock detection mechanism which is called Transport Stream Lock in this document. Operation is similar to the sync byte lock detection block described above. This block also detects the inverted sync bytes, which are then inverted by the energy dispersal block.

### **Energy Dispersal**

The error-corrected bytes are derandomized with a 15-stage PRBS (Pseudo Random Binary Sequence) generator, with polynomial  $1 + X^{14} + X^{15}$  and start-up sequence "100101010000000". Sync bytes are not derandomized, and when an inverted sync byte is detected, every 8th packet, the PRBS resets to the start-up sequence and the sync byte is reinverted. The derandomized data is output through the TSDATA pins, along with a data clock and synchronization signal.

#### 查询"CXD1968AR"供应商

#### **♦ MPEG2-TS Baseband Interface**

This block provides parallel and serial MPEG2-TS outputs. Due to the guard intervals and redundancy in the received COFDM signal, the MPEG2-TS output data can be bursty. MPEG2-TS packets can cross COFDM symbol boundaries resulting in periodic gaps between successive bytes in an MPEG2-TS packet. For this reason, the parallel and serial MPEG2-TS interfaces allow several different configurations of the TSCLOCK, TSERR, TSSYNC and TSVALID signals as described below. This block also smoothes the TS output in the time domain. This enables the serial interface to output data at the average rate rather than the peak rate and also reduces jitter on the PCR embedded in the TS.

#### **Transport Stream Smoothing**

When enabled, the transport stream smoothing function can operate in one of two modes:

- ◆ Automatic Mode, where the degree of smoothing is determined by reading the TPS data embedded in the DVB ensemble.

- ◆ Manual Mode, where the degree of smoothing is set by programming an I<sup>2</sup>C register. In manual mode the quality of the smoothing depends on how the I<sup>2</sup>C register is programed.

The effect of the transport stream smoothing function is different in parallel and serial modes:

- ◆ Parallel Mode: The frequency of the TSCLK output is almost the same as the data rate; there will be few gaps in the transport stream output (signaled by either TSVALID going inactive or a gated TSCLK see below). These gaps will never be within the 188 valid data bytes in a packet. This is because TSCLK is slightly fast, because allowances have to be made for timing offsets between the transmitter and receiver.

- ◆ Serial Mode: The frequency of the TSCLK output is fixed at 41MHz (40.96MHz if a 20.48MHz crystal is used), irrespective of the data rate. The valid data outputs are spread evenly, but there will be gaps output (signaled by either TSVALID going inactive or a gated TSCLK see below). These gaps will never be within a byte.

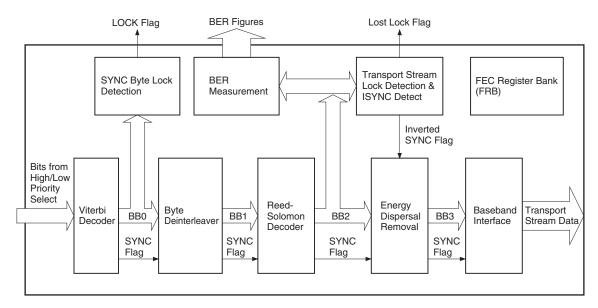

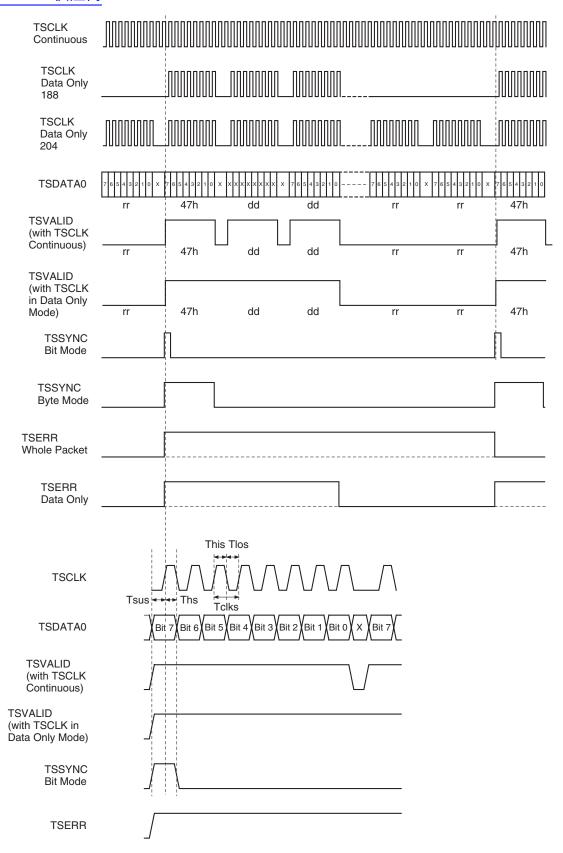

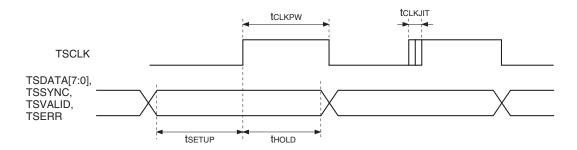

#### **Parallel Output Mode**

Fig. 3 illustrates the relationship between the CXD1968AR MPEG2 transport stream interface signals. The transport stream clock (TSCLK) can be programed for the external device to sample on the rising or falling edge (only rising edge sampling is shown here). The interface supports a number of additional signals, which indicate the integrity of the output data. Once the demodulator has achieved lock to the MPEG2 sync byte, the transport stream interface is activated. Fig. 3 shows a complete MPEG2 packet consisting of a sync byte (47h) data bytes (dd) and Reed-Solomon bytes (rr). Note that all the interface control signals have individual programmable polarity; active high signals are shown in the diagram.

**TSCLK** has two operating modes selected via I<sup>2</sup>C:

- ◆ Continuous Mode, where the clock runs continuously during all 204 bytes of each packet, and during gaps between bytes, thus requiring the external device to use TSVALID to validate the 188 data and sync bytes.

- ◆ Data Only Mode, where the clock is activated only for each of the valid data bytes and remains inactive at all other times. There are two further sub-modes in TSCLK Data Only Mode selected via I²C:

- 188 Mode, where TSCLK is active for the first 188 bytes in the TS packet.

- 204 Mode, where TSCLK is active for all 204 bytes in the TS packet.

**TSDATA[7:0]** is the byte wide MPEG2-TS data with programmable MSB/LSB ordering. The default is TSDATA7 being the MSB.

**TSVALID** identifies the data portion of transport stream packet (excludes R/S bytes). TSVALID has two operating modes depending on the TSCLK operating mode:

- ◆ TSCLK in Continuous Mode: TSVALID is set active for 1 TSCLK for each of the 188 data and sync bytes.

- ◆ TSCLK in Data Only Mode: TSVALID is set active during the 188 byte data portion of packet and inactive during the 16 Reed-Solomon bytes.

TSSYNC is set active during the MPEG2 sync byte and reset inactive for the remainder of the packet.

**TSERR** is only set active if the transport stream packet error flag is set within the MPEG2 TS. This signal indicates that the Reed-Solomon decoder was unable to correct all errors in the packet. There are 2 programmable modes for this signal:

- ◆ Whole Packet Mode: Active during the entire 204-byte packet.

- ◆ Data Only Mode: Active during the 188-byte data portion of packet and inactive during the 16 Reed-Solomon bytes.

<sup>\*</sup> Gaps will not appear within the 188 valid data bytes (dd) in parallel mode if TS smoothing is enabled.

Fig. 3. MPEG2 Transport Stream Output Configurations (Parallel Mode)

## 查询"CXD1968AR"供应商

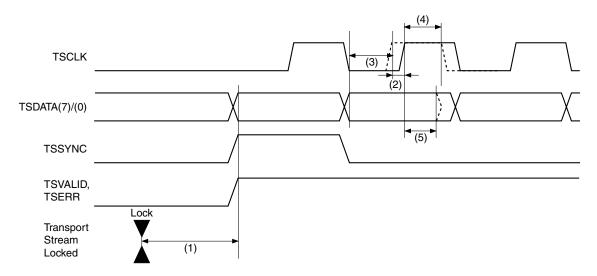

#### Seriai Output Mode

Fig. 4 illustrates the relationship between the CXD1968AR MPEG2 transport stream outputs when programed into serial output via I<sup>2</sup>C. The TSCLK can be programed for the external device to sample on the rising or falling edge (only rising edge sampling is shown here). The interface supports a number of additional signals, which indicate the integrity of the output data. Once the demodulator has achieved lock to the MPEG2 sync byte, the transport stream interface is activated. Data bits are shifted out on TSDATA0 or TSDATA7 (selectable via I<sup>2</sup>C), starting with the sync byte (47h). The remaining TSDATA signals are held inactive to reduce noise. The data bit order can be programed as MSB first or LSB first via an I<sup>2</sup>C register.

The frequency of the TSCLK output is 41MHz (40.96MHz if a 20.48MHz crystal is used) provided transport stream smoothing is enabled. It is recommended that the serial interface is only used with transport stream smoothing enabled.

Fig. 4 shows a complete MPEG2 packet consisting of a sync byte (47h) data bytes (dd) and Reed-Solomon bytes (rr). Note that all the interface control signals have individual programmable polarity; active high signals are shown in the diagram.

**TSCLK** has two operating modes and polarity selected via I<sup>2</sup>C. The operating modes are:

- ◆ Continuous Mode, where the clock runs continuously at a rate of 1 cycle per bit for all 204 bytes of each packet and during the gaps between bytes thus requiring the external device to use TSVALID to validate the 188 data and sync bytes. There are never any gaps between successive bits of the same byte.

- ◆ Data Only Mode, where the clock is activated only for 8 pulses on each byte output for each of the valid data bytes, and remains inactive at all other times. There are never any gaps between successive bits of the same byte. There are two further sub-modes in TSCLK Data Only Mode selected via I²C:

- 188 Mode, where TSCLK is active for the first 188 bytes in the TS packet.

- 204 Mode, where TSCLK is active for all 204 bytes in the TS packet.

Serial data can be output from either **TSDATA0** or **TSDATA7** under the control of I<sup>2</sup>C. MSB/LSB ordering is also selectable via I<sup>2</sup>C.

**TSVALID** identifies the data portion of transport stream packet (excludes R/S bytes). TSVALID has two operating modes selected depending on the TSCLK operating mode:

- ◆ TSCLK in Continuous Mode: TSVALID is set active for 8 TSCLK periods for each of the 188 data and sync bytes.

- ◆ TSCLK in Data Only Mode: TSVALID is set active during the 188 byte data portion of packet and inactive during the 16 Reed-Solomon bytes.

**TSSYNC** identifies the first byte in the transport stream packet and has two operating modes selectable by I<sup>2</sup>C:

- ◆ Byte Mode, where TSSYNC is set active for the first byte of the transport stream packet and reset inactive for the remainder of the packet.

- ◆ Bit Mode, where TSSYNC is set active for the first bit of the MPEG2 sync byte and reset inactive for the remainder of the packet.

**TSERR** is only set active if the transport stream packet error flag is set in the MPEG2 TS. This signal indicates that the Reed-Solomon decoder was unable to correct all errors in the packet. There are 2 programmable modes for this signal:

- ♦ Whole Packet Mode: Active during the entire 204-byte packet.

- ◆ Data Only Mode: Active during the 188-byte data portion of packet and inactive during the 16 Reed-Solomon bytes.

## 查询"CXD1968AR"供应商

Fig. 4. MPEG2 Transport Stream Output Configurations (Serial Mode)

## 查询"CXD1968AR"供应商

#### ◆ interrupts

The INTRPTN pin can be switched active low on the occurrence of one or more of the following conditions:

- · Receipt of a TPS block

- Received TPS parameter change

- Receipt of a TPS block with a bad BCH check

- · Change of AGC lock status

- TPS receive frame error

- Completion of FFT processing of the current symbol

- Occurrence of MPEG2 transport stream lock

- Loss of MPEG2 transport stream lock

- Occurrence of FEC (sync byte) lock

- Occurrence of errored second

- Occurrence of severely errored second

- Occurrence of more than 8-byte errors in transport stream packet (rejected codeword)

- TS smoothing circuit under/overflow

Separate interrupt enable and status bits for each interrupt are provided. An interrupt condition can be latched without generating INTRPTN to allow interrupt polling.

#### ◆ Diagnostic Interface

There is a diagnostic interface, which enables the following to be read using the I2C interface:

- Mean signal-to-noise ratio across all carriers

- Signal-to-noise ratio on each carrier

- Real and imaginary components of each carrier after channel correction

- Real and imaginary components of the channel estimate for each carrier

- Estimated noise power for each carrier

#### **♦ BER Measurement**

The CXD1968AR FEC includes comprehensive signal quality measurement logic. The current estimated Bit Error Rate (BER) of the received signal at various points in the receiver and a measure of the long-term signal quality are both available via I<sup>2</sup>C registers. It is also possible for a highly accurate BER to be measured, with a transmitted sequence of NULL MPEG2 packets in accordance with ETSI TR 101 290 v1.2.1. The measurements available are;

- 1. Pre-Viterbi decoder BER (can be measured with real live MPEG2 datastreams)

- 2. Post-Viterbi BER can be measured in two ways:

- Using live MPEG2 datastreams. This is an exact measurement provided each transport stream packet contains no more than 8-byte errors, and is an estimated measurement if the packet contains 8 or more errors.

- Using MPEG2 NULL packets. This is an exact measurement based on comparison between the

received packet and a stored MPEG2-TS NULL packet, and allows more than 8-byte errors in the

received packet to occur without introducing inaccuracies in the BER measurement.

- 3. Post R/S decoder BER (requires MPEG2-TS NULL packets to be sent)

- 4. Number of rejected codewords per second (R/S decoder errors due to more than 8-byte errors occurring)

- 5. Interrupt on occurrence of errored second (ES, at least one rejected codeword/second)

- 6. **Interrupt on occurrence of severely errored second** (SES, n or more rejected codewords in a second where n is a programmable threshold)

## 查询"CXD1968AR"供应商

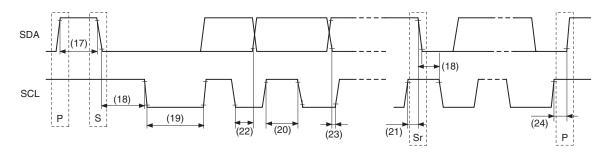

## **◆ Tuner Control Interface**

The Quiet I<sup>2</sup>C Module contained within the CXD1968AR allows the simple connection of slow I<sup>2</sup>C slave(s) to a 400kHz master by providing the necessary logic to guarantee all of the timing parameters for the slower device. If the slave is slower than 400kHz then it can use the slave acknowledge mechanism of holding the clock low between high phases. The Quiet I<sup>2</sup>C Module does not provide for multi-master arbitration.

In order to satisfy the tuner's requirement that the bus is normally quiet, the slave interface may be enabled or disabled.

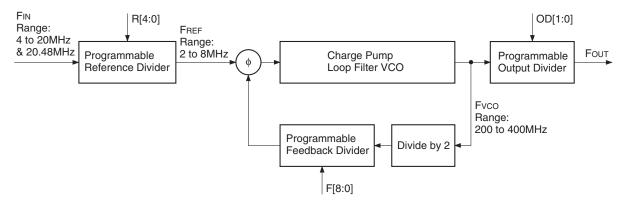

#### **♦ PLL Operation**

Internal clock signals are derived from an all-digital PLL. The functionality of this circuit has been extended to allow operation with an optional external clock signal. A typical application could be to use a 4MHz clock provided by the RF tuner, permitting the removal of the 20.48MHz crystal and components.

The following diagram illustrates the configuration used to generate the internal clock signals when a 20.48MHz crystal is present.

In this example the clock source Fin is obtained from the crystal oscillator, running at a nominal 20.480MHz.

- ◆ The reference divider R[4:0] is set to ÷5 which in combination with the fixed ÷2 results in FREF of 2.048MHz.

- ◆ The feedback divider F[8:0] is set to ÷80 which in combination with the fixed ÷2 results in the VCO, Fvco running at 327.68MHz (not accessible to the user).

- ◆ The output frequency Fou⊤ is divided by 4, OD[1:0] to give an 81.92MHz clock to the clock divider logic in the demodulator core.

Refer to the registers PLL\_FODR (0xA7) and PLL\_F (0xA8) for detailed programming information and a table of register settings for the supported external clock and crystal frequency combinations. The application note EAN-0066 provides programming examples.

Note) The internal clock frequency of 20.48MHz can change to 20.50MHz for some clock configurations. This will require alternative values of ITB\_FREQ and TRL\_NOM\_RATE.

## 查询"CXD1968AR"供应商 ◆ JTAG Test interface

#### **Test Mode**

The JTAG interface consists of five test pins available on the CXD1968AR. These are used only for embedded test and should be inactive for normal device operation. These pins are;

| TRSTN | Pin 34 |

|-------|--------|

| TDO   | Pin 30 |

| TDI   | Pin 31 |

| TMS   | Pin 32 |

| TCK   | Pin 29 |

The JTAG interface conforms to the "IEEE 1149.1 Joint Test Action Group (JTAG)" standard. The following instructions are available:

| Instruction    | Code |

|----------------|------|

| BYPASS         | 1111 |

| EXTEST         | 0000 |

| SAMPLE/PRELOAD | 0001 |

#### **Normal Device Operation**

The input functions of this group have very weak internal pull-ups present on the pins. This is primarily to ensure that these pins cannot be left floating, a condition which could cause the device to draw excessive current.

Under circumstances that may be influenced by board layout and supply power-up effects, the JTAG circuit can be inadvertently activated in parallel with the normal operation of the demodulator. This results in the main I<sup>2</sup>C bus locking.

This condition is readily identified but cannot be resolved without either a hardware reset or power-down. Once the main I<sup>2</sup>C bus has locked it is not possible to communicate with the chip, hence only an external reset will permit resumption of normal operation.

If JTAG functionality is not required, the interface should be disabled to ensure this mode cannot be initiated. This is implemented by forcing the test block into permanent reset. The TRSTN and TCK inputs should be grounded.

For users who wish to implement the JTAG test mode in their equipment, it will be unacceptable to permanently ground the TRSTN and TCK inputs. It is suggested that these inputs are pulled to ground by an external resistor. A pull-down value of  $10k\Omega$  is recommended, however the choice of value will depend upon the driver circuit and speed of operation. This is illustrated in the application circuit in section 4.

## 查询"CXD1968AR"供应商

#### 3. Description of Operation

This section describes the operation of the CXD1968AR DVB-T COFDM demodulator IC and how to make use of these features when operating the device. It does not give a detailed description of the enhanced modes of operation, users should refer to the separate engineering application notes for additional information about these configurations and uses.

The following descriptions apply to the CXD1968AR used with a tuner providing a High IF signal at a nominal frequency of 36.1667MHz. Contact Sony for configuration recommendations when operating with Low IF (4.5MHz) or Zero IF at the e-mail support address CXD1968 support@eu.sony.com

EAN-0065 and EAN-0066 are intended to assist users familiar with its predecessor the CXD1976R, and intend to make the transition to the CXD1968AR.

Engineering Application Notes are available for download to registered users from the Sony Technical Library http://www.sonybiz.net/semiconductor.

#### **♦** Processor Interface

The CXD1968AR must be configured by a host controller, which is required for initialization and to monitor its performance by writing and reading the CXD1968AR internal registers. The CXD1968AR controller interface is a serial interface which corresponds to the I<sup>2</sup>C standard. The I<sup>2</sup>C interface supports access at bit rates up to 400kbit/s.

The I2C uses an 8-bit address:

- The first 6 significant bits relate to the device type and are fixed at 110110.

- A single external address pin A0 is provided so that 2 different I<sup>2</sup>C slave address locations can be used. This permits multiple front-end configurations, for instance PVR application.

- The least significant bit is set to "1" for a write and "0" for a read.

| Address pin | CXD1968AR I <sup>2</sup> C address |           |  |  |

|-------------|------------------------------------|-----------|--|--|

| A0          | Binary Hexadecimal                 |           |  |  |

| 0           | 1101 100 R/W                       | D8h + R/W |  |  |

| 1           | 1101 101 R/W                       | DAh + R/W |  |  |

Examples used in this document assume an I2C address of 0xD8.

Reference to 0xD8 indicates a write instruction and to 0xD9 indicates a read instruction.

#### **Multibyte Reads**

Some registers contain fields more than 8 bits which are each accommodated across two or three registers. It is therefore possible for the field value to change in the time between two reads from the register pair. When a "1" is written to the freeze bit in the PIR\_CTL register (whether it was previously "0" or not), the field values are latched and the multibyte value can be read without fear of reading a corrupt value. With the freeze bit set to "0" the data within the fields changes dynamically.

## 查询"CXD1968AR"供应商

#### ◆ Tuner Quiet i<sup>2</sup>C interface

The tuner I<sup>2</sup>C interface allows the I<sup>2</sup>C interface to the tuner to be isolated from the host I<sup>2</sup>C interface to the rest of the system. This uses on-chip switching.

When an I<sup>2</sup>C master wants to send data to the tuner, it must first enable the slave interface before sending the data. To enable the tuner Quiet I<sup>2</sup>C interface the enable\_quiet\_I<sup>2</sup>C bit must be set in the TUNER\_CTRL5 register (bit 7 at register address 0xAF).

The normal sequence of operation is;

- 1. Set the enable\_quiet\_I2C bit in TUNER\_CTRL5.

- 2. Send/Receive the tuner I<sup>2</sup>C address and data as if it were being accessed directly by the host controller.

- 3. Reset the enable guiet I2C bit in TUNER CTRL5.

Example: 0xD8 0xAF 0x80 ; enable quiet I2C bus

0xC0 0xAA 0xBB... ; read/write any number of messages

; to tuner @ address 0xC0 for example

0xD8 0xAF 0x00 ; disable quiet I<sup>2</sup>C bus

#### Reset

There are three types of reset. A hard reset is initiated at power up; cold and warm resets are initiated by programming the RST\_REG register (below). With cold and warm resets, the host controller determines the type of reset and which parts of the CXD1968AR are to be reset.

#### **Hard Reset**

A hard reset is applied to all the CXD1968AR logic. A hard reset is initiated at power up by driving the RESETN pin low for more than 28ns. When the CXD1968AR is powered up, it must be hard reset. Whenever a hard reset occurs, the PLL will be out of tune. It must not drive logic until it has tuned. This is prevented by the reset to any PLL clocked logic being held in reset after a hard reset. The host controller must configure then enable the PLL output and release this reset after the PLL has tuned. The PLL output is enabled by setting the PLL\_op\_enable bit in the PLL\_CONTROL register. The reset is released when the host controller resets the "hard" bit of the RST\_REG register. The PLL tunes in 500µs.

#### **Cold Reset**

A cold reset is initiated by setting the cold bit in the RST\_REG register, and resets any modules that are selected by the RST\_REG register, including their I<sup>2</sup>C registers.

#### **Warm Reset**

A warm reset is initiated by setting the warm bit in the RST\_REG register, and resets any modules that are selected by the RST\_REG register, excluding their I<sup>2</sup>C registers.

## 查询"CXD1968AR"供应商

## ◆ COFDM Demodulator Configuration

While there are many registers which can be programed to configure the COFDM demodulator, there are only a few which must be programed to setup the interface to the tuner. The following must be configured:

- Configure clock, PLL and ADC

- Set ITB frequency for chosen IF frequency

- · Set TRL nominal rate for current channel bandwidth

- IF AGC sense if required

- Input spectrum inversion if required

## Clock, PLL and ADC Configuration

This means setting the clock mode for operation using the internal oscillator (crystal) or from an external clock source (tuner). PLL divider settings according to the oscillator or clock frequency. The ADC powers-up in dual channel mode (defaults to ZIF input), for IF mode the unused Q channel is then turned-off.

A description has been given in section 2, PLL Operation, with reference to the application note EAN-0066 which includes code samples. Standard operation is described here with a 20.48MHz crystal.

Example: 0xD8 0xA7 0x6A ; PLL comparison frequency and input divider

0xD8 0xA8 0x50 ; set PLL feedback divider

0xD8 0xBA 0x43 ; enable clocking from the crystal

0xD8 0xB9 0xB2 ; power down ADC Q

#### Signal IF Frequency

The ADC input IF frequency is programed via the ITB\_FREQ\_1, 2 registers. These make up a 14-bit value – ITB frequency (IF-To-Baseband). This value is calculated using the following formula:

$$ITBFREQ = \frac{-1 \times F_{IF}}{F_{ADC}} \times 16384$$

If the IF is being undersampled (as will be the case with a High IF signal input) then FIF is the subsampled IF, thus for a 36.1667MHz IF a derived value of 4.79MHz should be used in the equation  $(2 \times 20.480MHz - 36.1667MHz = 4.79MHz)$ :

| IF mode | IF [MHz] | Fif [MHz] | FADC [MHz] | ITBFREQ       |

|---------|----------|-----------|------------|---------------|

| Low     | 4.57     | 4.57      | 20.48      | -3657 (31B7h) |

| High    | 36.00    | 4.96      | 20.48      | -3968 (3080h) |

| High    | 36.125   | 4.835     | 20.48      | -3868 (30E4h) |

| High    | 36.1667  | 4.7933    | 20.48      | -3835 (3105h) |

| High    | 36.1667  | 4.8333    | 20.50      | -3863 (30E9h) |

| High    | 36.00    | 5.00      | 20.50      | -3996 (3064h) |

Example: 0xD8 0x0C 0x05 ; write ITBFREQ in two bytes for 0xD8 0x0D 0x31 ; 36.1667MHz IF and 20.48MHz clock

It is important that the ITB frequency should be calculated using the correct ADC clock frequency.

Note) The spectrum invert bit in register ITB\_CTL 0x0B may need to be set for Low IF operation, this may also depend upon the tuner.

#### **Channel Bandwidth**

The channel bandwidth is set indirectly by programming the TRL\_NOMINALRATE\_0, 1, 2 registers. TRLNOMINALRATE has changed from a 16-bit number on the CXD1976R to a 24-bit number on the CXD1968AR. These registers set the nominal rate of the sample timing NCO. TRL nominal rate is the ratio of the FFT time sample clock to the (fixed) ADC clock frequency. The following formula should be used to determine the TRLNOMINALRATE value:

$$TRLNOMINALRATE = \frac{16 \times ChanBW}{F_{ADC} \times 7} \times (2^{24})$$

Note that the maximum allowable value of this register is 16777215 and the minimum is 11184811. Some common settings are given below, calculated for 20.48MHz and 20.5MHz clocks:

| Channel bandwidth | FADC = 20.48MHz    | FADC = 20.5MHz     |

|-------------------|--------------------|--------------------|

| 8MHz              | 14979657 (E49249h) | 14965043 (E45933h) |

| 7MHz              | 13107200 (C80000h) | 13094412 (C7CE0Ch) |

| 6MHz              | 11234743 (AB6DB7h) | 11223782 (AB42E6h) |

Example: 0xD8 0x65 0x49 ; write TRL\_NOMINALRATE in three bytes

0xD8 0x1B 0x92 ; for 8MHz RF channel 0xD8 0x1C 0xE4 ; and 20.480MHz clock

Note) Error in the calculation of TRLNOMINALRATE more than 50ppm may compromise acquisition of 8K transmissions.

#### **Using Other IF Input Frequencies**

IF signals outside the range 4.50MHz to 4.57MHz and 36.000MHz to 36.1667MHz are not recommended.

### **IF AGC Sense**

The IF AGC sense is programed by setting the AGC\_neg bit in the AGC\_CTL register. When set the AGC level output decreases when a larger signal is required, otherwise the AGC level output increases when a larger signal is required.

Most tuners will not require this bit setting, so the register may not need to be programed.

#### **Spectrum Inversion**

The spectrum can be inverted to allow a reversed frequency spectrum from the tuner by setting the ITB invert spectrum bit in the ITB\_CTL register.

This may be required for operation with dual-conversion and Low IF architecture tuners.

## 查询"CXD1968AR"供应商

## ◆ Forward Error Corrector Configuration

Operation of the FEC block can be optimized by overriding some of the default register values. The following should be configured:

- Viterbi auto-reset

- Sync detect

- TS output mode

#### Viterbi Block

The disable bit in the AUTO\_RESET register should be reset to optimize acquisition (the default value does not give optimum performance).

Example: 0xD8 0xB1 0x00 ; enable Viterbi auto-reset

#### **FEC Block**

The SET\_SYNC\_DETECT register should be set to 0x67 for optimum performance (the default value of 0xD6 does not give optimum performance).

Example: 0xD8 0x86 0x67 ; set sync detect

#### **Transport Stream Outputs**

Also, in order to obtain a watchable picture after TS lock, the transport stream outputs must be enabled (normally these are tri-stated on power-up) by clearing bit 1 of FEC\_PARAMS register. The following lines enable the most commonly used parallel TS output format:

Example: 0xD8 0x80 0x18 ; enable parallel mode

0xD8 0x81 0xF4 ; preferred TS configuration

## 查询"CXD1968AR"供应商

## **◆ COFDM Signal Acquisition**

There are three stages in acquiring and locking to a COFDM signal. First, the COFDM demodulator must acquire the signal; then the FEC must synchronize to the Viterbi decoder output; finally, the FEC must synchronize to the transport stream.

The CXD1968AR contains a new auto-recover algorithm. This is a hardware implementation which automatically reacquires an interrupted signal without intervention from the host controller. After the initial setup this minimizes the load on the host processor.

The recommended method of operating the demodulator is to;

- 1. Configure the clocks and registers as described in the application note EAN-0066 and explained above.

- 2. Enable the core which will result in an acquired channel if present.

- 3. Set the auto-recover enable bit for automatic acquisition on any channel change.

This uses the default acquisition mode and will acquire the channel regardless of the DVB-T mode.

#### **Default Acquisition**

In this mode, nothing need be known about the transmission parameters (except the channel bandwidth). The COFDM demodulator tries all the guard intervals in the two modes (2K and 8K) and then waits until it has received a whole super-frame before decoding the TPS data and configuring itself to receive that particular COFDM signal. Signaled TPS data in the stream is valid for the NEXT super-frame so the decoder may have to wait for 5 frames – 1 symbol (= 339 symbols) before it can use the received transmission parameters.

Typical acquisition times for this mode: 125ms (2K) / 500ms (8K).

#### **Settings for Faster Acquisition**

There are several short cuts that can be taken to speed up acquisition. These depend on how the control registers are programed. It is not generally recommended that the user overrides the default settings unless the host processor has sufficient resources available.

#### **Transport Stream Locking**

FEC lock occurs at the input of the Reed-Solomon decoder when the number of sync bytes (47h) measured exceeds a certain value in the SET\_SYNC\_DETECT register. Transport Stream (TS) lock occurs at the output of the Reed-Solomon decoder, and uses the same mechanism as FEC lock.

The SET\_SYNC\_DETECT register can be used to adjust the criteria for gaining/losing lock. The higher the number of bytes required to gain lock, the harder it is to acquire lock, but, once acquired, the chip should be less likely to lose lock. Lock can be lost either by counting the number of missed sync bytes (Decrement mode) or one missed sync byte can lose lock straight away (Reset mode). Reset and decrement modes are independently settable for TS lock and FEC lock.

Example: 0xD8 0x86 0x67 ; recommended configuration

#### Reacquisition

It may be necessary to reacquire a COFDM signal, for example if the user were to select a different RF channel, because of reception problems with a poorly sited set-top aerial or to simplify channel scanning. It is recommended to use the auto-recovery algorithm and default acquisition settings to minimize host processor overhead.

The auto-recovery block has two modes of operation, scanning and zapping.

Scanning mode will tell the auto-recovery state machine to attempt only 1 acquisition when enabled, after which it falls back to an idle state. The status can read by the host processor, ie. TPS and/or TS lock at the end of acquisition. Note that ready bits will indicate if the status readings are valid, ie. the process has completed.

Zapping or channel change mode, also to be used during static operation to automatically recover a lost signal. In this mode the auto-recovery state machine will continuously monitor the demodulator status and reacquire when TPS/TS lock is lost. It is not necessary to read the status as it will continue to operate until disabled.

## 查询"CXD1968AR"供应商

#### ◆ Transport Stream Outputs

Transport stream data is output on the TSDATA outputs; it is clocked by the TSCLK output. The TSSYNC output is active during the first byte of a TS packet. The TSVALID output can be used to indicate valid data. The TSERR output indicates a TS packet containing uncorrected errors. The TSLOCK output is set active high when a valid transport stream is locked on to.

#### **Enabling/Disabling the Transport Stream Output**

The transport stream outputs are enabled by setting the Tri\_State\_Outputs bit in the FEC\_PARAMS register.

#### Serial/Parallel Data Output Selection

The default transport stream output mode is parallel. A serial output can be selected by resetting the TS parallel sel bit in the FEC PARAMS register.

#### **Other Transport Stream Output Format Options**

The default output format is as below:

- ◆ In parallel mode, the MSB is output on the TSDATA7 pin, the LSB on TSDATA0. In serial mode, the MSB is output first and the LSB last all on TSDATA0.

- ◆ Data should be sampled on the rising edge of TSCLK.

- ◆ TSVALID, TSSYNC and TSERR are all active high.

- ◆ TSVALID active high indicates a valid data.

- ◆ TSERR is active for the first 188 bytes if that packet contains an uncorrected error.

- ◆ TSCLK is gated so that edges occur when TSVALID is active.

The following options are available and can be selected by programming the FEC\_PARAMS and BB\_PARAMS registers:

- ◆ In parallel mode, the MSB can be output on TSDATA0 and the LSB on TSDATA7, and in serial mode the LSB can be output first and the MSB last by setting the Output\_Sel\_MSB bit in the FEC\_PARAMS register.

- In serial mode, data can be output on TSDATA7 by setting the Ser\_data-on\_MSB bit in the FEC\_PARAMS register.

- ◆ TSVALID, TSSYNC and TSERR can all be set active low by resetting the TSvalid\_active\_high, TSsync\_active\_high and TSerr\_active\_high bits respectively in the BB\_PARAMS register.

- ◆ In parallel mode, the TSVALID output can be set to be active only during the first byte of a packet by setting the TSvalid\_pulse bit in the BB\_PARAMS register.

- ♦ TSERR can be set to be active only during the first byte (or bit in serial mode) by setting the TSerr\_pulse bit in the BB\_PARAMS register. If this bit is reset, then TSERR can be set to be active until the start of the next non errored TS packet by setting the TSerr full bit in the BB\_PARAMS register.

- ◆ TSCLK can be set to be active continuously by setting the TSclk full bit in the BB PARAMS register.

## 查询"CXD1968AR"供应商

## **Transport Stream Smoothing**

COFDM demodulation is naturally bursty. The demodulator operates on whole symbols of data at a time. A whole symbol must be stored before FFT processing can begin. Transformed data is read out of the FFT block as fast as possible into the following circuitry, resulting in a bursty TS. This bursty TS output can be smoothed by the on-chip TS smoothing buffer.

The TS smoothing buffer is enabled by setting the ENABLE bit in the SMOOTH\_CTRL register. The smoothing buffer can operate in an automatic or manual mode.

#### **Automatic Mode**

In automatic mode, the smoothing buffer applies the correct degree of smoothing for the COFDM signal being demodulated. Automatic mode is set by setting the DATA\_PERIOD\_AUTO bit in the SMOOTH\_CTRL register. The channel bandwidth must also be programed into the SMOOTH\_CTRL register using the CHANNEL\_WIDTH bits.

Example: 0xD8 0xB4 0x03 ; enable automatic mode for 8MHz channel

#### **Manual Mode**

In manual mode, the degree of smoothing must be programed into the SMOOTH\_DP1, 0 registers. The SMOOTH\_DP0 register bits represent the fractional number of clock periods per TS word. A read from the SMOOTH\_DP0 register returns the current value of the fractional part of the data period value.

A read from SMOOTH\_DP0 also causes the current value of the integer part of the data period value to be stored in a holding register, which can be accessed by reading from SMOOTH\_DP1. For this reason it is recommended that SMOOTH\_DP0 and SMOOTH\_DP1 are read as a pair of registers, SMOOTH\_DP0 first, followed by SMOOTH\_DP1.

Writing to SMOOTH\_DP0 only has an effect when the DATA\_PERIOD\_AUTO bit of the SMOOTH\_CTRL register is set to "0". In this case, writing to SMOOTH\_DP0 has the effect of storing the 8-bit value in a holding register. Writing to SMOOTH\_DP1 then has the effect of transferring data from the holding register to the SMOOTH\_DP0 register proper. As with read accesses, it is recommended that write accesses to SMOOTH\_DP0 and SMOOTH\_DP1 are performed in pairs, SMOOTH\_DP0 first, followed by SMOOTH\_DP1.

The SMOOTH\_DP0 register bits represent the integer number of clock periods per TS word. A read from the SMOOTH\_DP1 register returns the integer part of the data period value previously stored in a holding register when a read from the SMOOTH\_DP0 register occurred (see SMOOTH\_DP0 above).

Writing to SMOOTH\_DP1 only has an effect when the DATA\_PERIOD\_AUTO bit of the SMOOTH\_CTRL register is set to "0". In this case, writing to SMOOTH\_DP1 has the expected effect of updating the SMOOTH\_DP1 register value, and has the additional effect of transferring data from a holding register (updated during a SMOOTH\_DP0 write operation) into the SMOOTH\_DP0 register (see SMOOTH\_DP0 above).

#### Monitoring the Smoothing Buffer Status

The status of the smoothing buffer can be monitored by reading the SMOOTH STAT register.

The UNDERFLOW flag is set when an underflow condition has been detected. An underflow condition is where data is requested but cannot be provided because the read FIFO is empty. Note that when data is requested but cannot be provided because the next TS word is a sync and at the same time the SRAM FIFO does not contain a complete TS packet, this is part of the smoothing circuit's normal operation and is not classed as an underflow condition. Write a "1" to this bit location to clear this bit. Writing a "0" to this bit has no effect.

The OVERFLOW flag is set when an overflow condition has been detected. Write a "1" to this bit location to clear this bit. Writing a "0" to this bit has no effect.

Example: 0xD8 0xB5 0x03 ; to clear smoothing buffer status flags

## 查询"CXD1968AR"供应商

**◆ AGC**

There are two AGC outputs from the CXD1968AR – one for the RF tuner stages and one for the IF tuner stages. These generate PWM outputs that need to be integrated off-chip to provide an analog control signal to drive an external variable gain amplifier (analog VGA) in the tuner. Each integrator is implemented with a simple external single pole RC filter, values selected to give a cutoff frequency of 400Hz, removing the high frequency components.

#### **RF AGC**

The RF AGC outputs a PWM value via the RF AGC pin, which has been programed into the RF\_IFAGC\_CTRL0 and RF\_IFAGCQ\_PWM registers (renamed to cover the new ZIF AGC modes). The RF AGC pin is enabled by setting the RF AGC EN bit in the RF AGC CTRL0 register.

The RF AGC pin may alternatively be used as a logic I/O pin, see below.

#### **IF AGC**

The IF AGC outputs a PWM value via the IF AGC pin. The AGC setting can be generated automatically or manually overridden.

#### **Automatic Gain Control**

The CXD1968AR contains an internal AGC block, which monitors the signal level at the output of the ADC and provides a Pulse Width Modulated (PWM) control signal to implement an automatic gain control loop. The AGC is capable of tracking out 60Hz AM interference with the specified time constant, and large changes in input level. A 40dB input swing can be corrected in 20ms (irrespective of QAM/QPSK modulation scheme).

The IF AGC automatic mode is enabled by resetting the AGC Set bit in the AGC\_CTL register. The sense of the output is controlled by the AGC Neg bit in the same register.

## **Manual Gain Control**

The AGC loop can be set manually using the AGC Set bit in the AGC\_CTL register and entering a value of 0 to 1023 in the AGC Manual field in this register.

#### **RF AGC GPO**

The RF AGC pin may be configured to generate a fixed logic "0" or "1" output level (3.3V) where the RF AGC variable output function is not required. A typical application is to switch a dual bandwidth SAW filter or other circuit function in software.

If the RF AGC output pin is to be used for this kind of application, the integrating RC filter is not required. This example generates a logic "1" or 3.3V level at this output.

Example: 0xD8 0xB2 0x07 ; set RF AGC output pin High

#### **RF AGC GPI**

The RF AGC pin may be configured as a logic input (3.3V logic but 5V tolerant) where the RF AGC variable output function is not required. This may be used to sense operation of an external circuit.

#### **Status Monitoring**

#### **Transport Stream Lock**

This flag indicates that a valid MPEG2 transport stream is available at the CXD1968AR TSDATA outputs. Transport stream lock can be determined from reading the FEC\_STATUS register, or from the INTERRUPT\_SOURCE register. This bit is set in both registers whenever the Reed-Solomon FEC block has locked and a valid MPEG2 transport stream is now ready for output. Should the transport stream lose lock, then a TS lost lock flag bit is set in the FEC\_PARAMS and INTERRUPT\_SOURCE registers.

#### **FEC Lock**

FEC lock indicates that the Reed-Solomon FEC block has a coded MPEG2 transport stream at its input, which it is trying to decode. FEC lock can be determined from reading the FEC\_STATUS register.

#### **AGC Lock**

The AGC lock flag in the COR\_STAT register can be used to check that the input signal level is not varying and is not too high or too low (a high-level signal will cause distortion problems, and a low-level signal will suffer from quantization noise).

#### **Core State Machine**

The COFDM demodulator contains a state machine, which can be used to gain information as to why the CXD1968AR has not locked on to an incoming OFDM signal. The core has the following states:

| 0000 | State machine not forced |

|------|--------------------------|

| 0001 | WAIT_TRL                 |

| 0010 | WAIT_AGC                 |

| 0011 | WAIT_SYR                 |

| 0100 | WAIT_PPM                 |

| 0101 | WAIT_TPS                 |

| 0110 | MONITOR _TPS             |

| State 0: IDLE        | Core is disabled.                                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| State 1: WAIT_ TRL   | Core is calculating a value to be used later.                                                                                    |

| State 2: WAIT_AGC    | Core is waiting for input signal levels to stabilize to an acceptable value before attempting to demodulate the incoming signal. |

| State 3: WAIT_SYR    | AGC has locked, waiting for the core to determine the guard interval and its position.                                           |

| State 4: WAIT_PPM    | Waiting for the pilot processing module to find the pilot carriers.                                                              |

| State 5: WAIT_TPS    | Waiting for the core's TPS decoder to acquire frame sync (which determines the symbol number).                                   |

| State 6: MONITOR_TPS | Signal ready to be fed to the Viterbi decoder, continue to monitor the TPS data for parameter changes.                           |

## 查询"CXD1968AR"供应商 Performance Monitoring

#### Pre-Viterbi BER

Pre-Viterbi BER readings are available from the VIT\_BER register. The sampling period is adjustable in the VIT\_CTRL register.

#### Reed-Solomon BER

Pre- or Post-Reed-Solomon BER can be either measured or estimated using the BER\_ESTIMATE register. In measurement mode, NULL packets must be used. In estimate mode, any data can be used. Estimation mode assumes that all post Viterbi errors are corrected by the Reed-Solomon decoder. Measurement mode is selected by setting the Measurement\_Sel bit in the FEC\_PARAMS register. Readings should be taken whenever the NEW\_BER bit is set. If too many errors have been recorded during the specified measurement period, then the BERCNT\_Overflow bit will be set. Should this occur, the reading should be discarded and a lower measurement period selected. The measurement period is set using the BER\_PERIOD register.

#### **Uncorrected Errors**

#### Errored Second

This indicates that the Reed-Solomon FEC block could not correct all the errors found in one or more 204-byte packets received during the last second. This is because >8 errors were found in the packet. Errored second can be determined from reading the FEC\_STATUS register, or from the INTERRUPT\_SOURCE register.

#### Severely Errored Second

This indicates that the Reed-Solomon FEC block has been unable to correct the errors found in N or more 204-byte packets received during the last second. This is because >8 errors were found in each of the packets.

N is set using the LT\_QLTY\_THRESHOLD register. Typically, this can be used to set a threshold value with regard to picture degradation, depending on the quality of service required. Severely errored second can be determined from reading the FEC\_STATUS register, or from the INTERRUPT\_SOURCE register.

#### Codeword Reject Count

This indicates the number of rejected codewords (MPEG-2 packets) in one second. This is recognized to be a particularly useful measurement as it is more closely aligned to receiver picture failure than BER.

#### Signal-to-Noise Estimate

The CHC\_SNR register can be used to obtain an estimate of the signal-to-noise ratio of the received signal either for each carrier individually or as a mean across the channel.

If the mean bit in the SNR\_CARRIER\_2 register is set, then a mean value across the channel can be read from the CHC\_SNR register.

If the mean bit in the SNR\_CARRIER\_2 register is reset then the carrier number can be selected by programming the SNR carrier number bits in the SNR\_CARRIER\_1, 2 registers and after at most one symbol the SNR for that carrier can be read from the CHC\_SNR register (the host controller must wait for one symbol to be sure that the data is ready).

A higher value indicates a lower operating SNR. The estimated value is independent of the channel response, and accurate to about  $\pm 1$ dB. The value in this register (N) can be converted to an approximate dB value using the following empirical formula:

$$SNR[dB] = \frac{CHC\_SNR}{8}$$

## 查询"CXD1968AR"供应商

#### interrupts

These can be used to quickly ascertain the status of the chip. This can be done in one of two ways:

- 1. Regularly polling the interrupt flags over the I<sup>2</sup>C bus.

- 2. Using the INT pin to raise a hardware interrupt, then getting the host controller to read the interrupt flags to determine the type of interrupt.

The interrupts are of two basic types:

- High-level interrupts: the flags for these are contained in the interrupt status register (INTERRUPT\_SOURCE).

- 2. OFDM core interrupts: the flags for these are contained in the core interrupt status register (COR\_INTSTAT).

#### **High-level Interrupts**

These interrupts relate to the key stages in acquiring transport stream lock. Interrupt flags are available for the following events:

- 0. COFDM demodulator interrupt (poll the COR\_INTSTAT register to find out why)

- 1. Transport stream lock

- 2. Transport stream lost lock

- 3. Reserved

- 4. Errored second detected

- 5. Severely errored second detected

- 6. Codeword rejected (>8 errors in current packet)

- 7. Transport stream smoothing under/over flow

To clear each interrupt, write a "1" to the corresponding bit in the INTERRUPT\_SOURCE register after the interrupt has occurred.

#### **COFDM Demodulator Interrupts**

COFDM demodulator interrupt flags are available for the following events:

- 0. AGC lock change (AGC gained lock/AGC lost lock)

- 1. End of symbol (from Symbol Recovery block)

- 2. FFT done: FFT processing complete on current symbol

- 3. Receipt of a TPS block

- 4. Change of TPS parameters

- 5. TPS block has a bad BCH checksum.

#### Enabling Core Interrupts

Interrupts are enabled using the COR\_INTEN register. To enable any core interrupt, the INTEN Global bit in the COR\_INTEN register must be set. Each individual interrupt is then enabled by setting the appropriate bit in the COR\_INTEN register.

#### Low-power Standby Mode

This mode reduces the nominal power consumption of the CXD1968AR in IF mode from 140mW to 10mW.

To obtain maximum benefit it is necessary in software to;

- ◆ Disable PLL and stop internal clocks

- ◆ Power-down the ADC

Recovery from low-power standby mode can be achieved by cold reset to all blocks.

Example: 0xD8 0xA9 0x41 ; power-down PLL and stop clock

0xD8 0xB9 0x01 ; power-down ADC

#### **Ultra Low-power Shutdown Mode**

This mode reduces the nominal power consumption of the CXD1968AR in IF mode from 140mW to < 1mW.

This mode is entered through external control of OSCEN (Pin 40). Grounding this pin will stop the crystal oscillator and all on-chip activity.

The CXD1968AR should be reset when resuming from shutdown mode.

## 查询"CXD1968AR"供应商

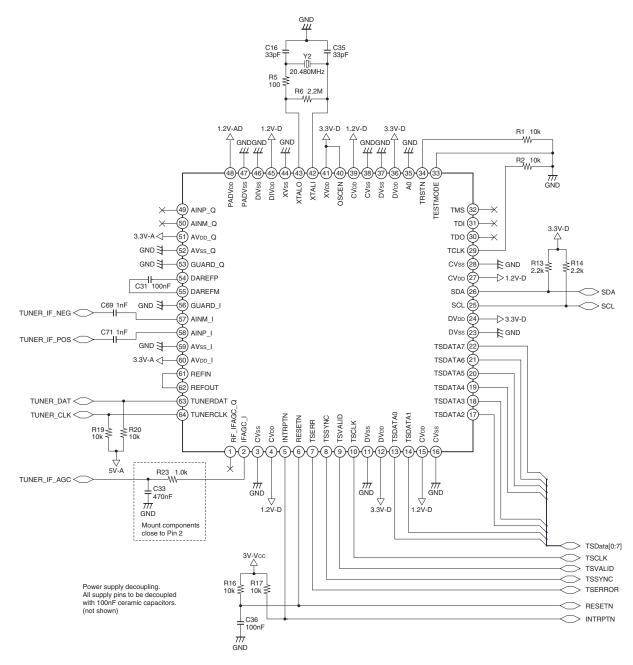

## 4. Application Circuit

Note) For High IF or Low IF mode, use PIN 57, 58 (AINM\_I, AINP\_I) as the ADC input. And, PIN 49, 50, which are unused, should be kept open.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

Fig. 5. Application and Test Measurement Schematic for IF Mode of Operation

## 查询"CXD1968AR"供应商

## 5. Design Guidelines

This section describes the application of the CXD1968AR DVB-T COFDM demodulator IC.

The schematic contained within the previous section should be used to assist with following descriptions.

Refer to the separate engineering application notes for additional information about specific configurations and uses. EAN-0065 is intended to assist users familiar with the CXD1976R in making the transition to the CXD1968AR.

#### **Circuit Configurations**

The CXD1968AR has the capability to operate with High IF, Low IF and Zero IF conventional or silicon tuners. The application described in this section is for a conventional High IF tuner.

## **ADC Input**

The ADC input of the CXD1968AR is directly compatible with differential sources. Where the tuner can supply only a single-ended IF signal, a balun is recommended to maximize the dynamic range of the IF strip.

The ADC input has a high impedance input (>  $1k\Omega$ ). The tuner output impedance is normally low (<  $100\Omega$ ) and it is not necessary to match to the ADC. The differential inputs are self-biasing and our recommendation is to AC couple the input signals with 1nF or larger capacitors.

Note) For High IF or Low IF mode, use PIN 57, 58 (AINM\_I, AINP\_I) as the ADC input.

## **ADC Reference Components**

The ADC reference voltage at Pins 61 and 62 (connected together) should be decoupled with 100nF multilayer capacitor for optimum performance.

#### **AGC**

The CXD1968AR generates an IF AGC output. This signal is a digital PWM format requiring an integrating RC filter to provide a variable DC control voltage for the tuner or IF circuit.

A second AGC output can be generated for RF gain control. The output signal is also PWM format, but may be configured as a fixed logic level output for general-purpose control functions. When used as an AGC output, an integrating RC filter is required. This pin may alternatively be used as a logic input at a nominal 3.3V but is 5V compliant.

The application values for the PWM integrating filter of  $1000\Omega$  and 470nF are chosen to give a 0.5ms time constant which approximates to a 400Hz cutoff frequency. For the IF AGC loop, this value is chosen as a compromise between suppressing the PWM high-frequency components and permitting the AGC loop to track 50/60Hz AM interference which may be present on the received signal. Typically the AGC response time to a step input, as might occur changing channel, is 20ms. If the filter values are modified perhaps to achieve faster channel acquisition, then note the possible impact on AM rejection.

#### **Clock and Crystal Oscillator**

The oscillator cell will operate with an external crystal or use an external clock, this is configured at startup by register settings described in the application note EAN-0066. If using an external clock, this must be present before programming can be applied.

Performance with an external clock may be compromised if the quality of the reference signal is poor.

## 查询"CXD1968AR"供应商

The JTAG facility can be utilized, but refer to section 2 of this datasheet for information on how to configure the connections.

It may be necessary to apply pull-down resistors to these pins:

TCK Pin 29 TRSTN Pin 34

#### **Power Supply Sequencing**

During the power-up sequence of the 1.2V and 3.3V supplies, it is important to ensure that the 1.2V supply is not applied before the 3.3V supply. Failure to do this could result in latch up and the CXD1968AR will not function correctly.

During power-down the 3.3V supply should not fall below the 1.2V supply, as both decay.

Both conditions can be met by deriving the 1.2V supply from the 3.3V supply.

If this configuration is not utilized or the timing cannot be guaranteed, it is possible to prevent supply latchup by adding a Schottcky diode between the supplies. Connect the diode with anode to 1.2V supply and cathode to 3.3V supply. This is only appropriate when both analog and digital 3.3V supplies are derived from the same regulator. The diode used must be a Schottcky type for low forward voltage drop, ie. 0.4V or less. This solution is applicable to both power-up and power-down conditions.

#### Reset

Note the hardware reset requirements outlined in section 3. As has been stated, when the CXD1968AR is powered up, it must be hard reset. This can be achieved simply by using an external RC circuit with time constant of around 1ms, values of  $10k\Omega$  and 100nF are employed in the recommended application. Alternatively this function may be provided by a specific device or host controller and the timing will be dependant upon supply rise time.

## Pull-ups

The following pins should be used with pull-up resistors:

SDA

Pin 26

SCL

Pin 25

QSDA

Pin 63

QSCLK

Pin 64

INTRPTN

Pin 5 (if used)

A nominal value of  $10k\Omega$  is used with the CXD1968AR but other values are permissible dependant upon the interface requirement. The maximum loading is stated in the DC Electrical Characteristics, a value of less than  $1000\Omega$  is not advisable.

## 查询"CXD1968AR"供应商 Printed Board Layout

Board layout recommendation for CXD1968AR.

#### **Supply and Ground**

The CXD1968AR uses three supplies:

| 1.2V digital | for core processing |

|--------------|---------------------|

| 3.3V digital | for clock and I/O   |

| 3.3V analog  | for ADC             |

All supplies should be decoupled close to the supply pins.

A single ground plane is recommended. However in some situations a split analog/digital ground plane can offer improved immunity from digital noise. Which option yields better performance will depend upon the application, ie. location of supplies and interference sources.

These rules should be adhered to, minimizing the risk of performance degradation:

- ◆ The supplies may be tracked-in (2-layer board) or assigned to a specific power-plane (multilayer). With either form it is essential to provide a low-impedance ground return to the source of the supply. A continuous ground plane is preferred as a starting point.

- ◆ The quiet analog section resides at one corner of the device, Pins 47 to 62. The supply to this section should feed into and return (via ground) without crossing over the digital section of board.

- ◆ The digital section should avoid a ground return path through the analog section. Failure to ensure this may compromise performance of the demodulator.

If it is not possible to ensure uninterrupted ground return paths back to each supply source, it may be necessary to partition the ground plane to force digital supply ground return currents to avoid the analog section. It is also advisable to link analog and digital grounds in the area directly below the CXD1968AR.

## **ESD**

Other constraints include immunity from ESD. The instantaneous energy presented by any electrical impulse should avoid passing close to or through the CXD1968AR. Similarly any connection to the CXD1968AR should not be susceptible to or protected against ESD pickup. For circuit connections that may travel outside of the immediate vicinity around the CXD1968AR, it is recommended that low-value series resistors are employed to limit charge transfer. A typical value would be 47 to  $100\Omega$ .

### **ADC Input**

The signal connections to the ADC input should be of similar length and routed together. Failure to do so may compromise the common mode rejection properties of the differential input circuit. Low-impedance drive to the ADC will minimize the risk of spurious pickup.

The connection between tuner IF output and the CXD1968AR ADC input should be routed over continuous analog ground plane.

## **ADC Reference Components**

As for the ADC input connection, the capacitor between DAREFP and DAREFM should be positioned above continuous analog ground plane.

#### **AGC**