### LP38859

# 3A Fast-Response High-Accuracy LDO Linear Regulator with Soft-Start

### **General Description**

The LP38859 is a high current, fast response regulator which can maintain output voltage regulation with extremely low input to output voltage drop. Fabricated on a CMOS process, the device operates from two input voltages:  $V_{\rm BIAS}$  provides voltage to drive the gate of the N-MOS power transistor, while  $V_{\rm IN}$  is the input voltage which supplies power to the load. The use of an external bias rail allows the part to operate from ultra low  $V_{\rm IN}$  voltages. Unlike bipolar regulators, the CMOS architecture consumes extremely low quiescent current at any output load current. The use of an N-MOS power transistor results in wide bandwidth, yet minimum external capacitance is required to maintain loop stability.

The fast transient response of this device makes it suitable for use in powering DSP, Microcontroller Core voltages and Switch Mode Power Supply post regulators. The LP38859 is available in TO-220 and TO-263 5-Lead packages.

**Dropout Voltage:** 240 mV (typical) at 3A load current. **Low Ground Pin Current:** 14 mA (typical) at 3A load current.

Soft-Start: Programmable Soft-Start time.

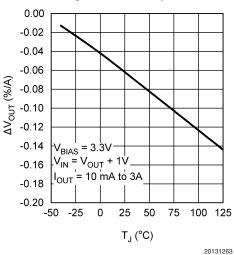

**Precision Output Voltage:**  $\pm 1.0\%$  for  $T_J = 25^{\circ}C$  and  $\pm 2.0\%$  for  $0^{\circ}C \le T_J \le +125^{\circ}C$ , across all line and load conditions

### **Features**

- Standard V<sub>OUT</sub> values of 0.8V and 1.2V

- Stable with 10µF Ceramic capacitors

- Dropout voltage of 240 mV (typical) at 3A load current

- Precision Output Voltage across all line and load conditions:

- $\pm 1.0\% \text{ V}_{OUT} \text{ for T}_{J} = 25^{\circ}\text{C}$

- $\pm 2.0\%$  V<sub>OUT</sub> for 0°C ≤ T<sub>J</sub> ≤  $\pm 125$ °C

- $\pm 3.0\%$  V<sub>OUT</sub> for -40°C ≤ T<sub>J</sub> ≤ +125°C

- Over-Temperature and Over-Current protection

- Available in 5 lead TO-220 and TO-263 packages

- Custom V<sub>OUT</sub> values between 0.8V and 1.2V are available

- -40°C to +125°C Operating Temperature Range

### **Applications**

- ASIC Power Supplies In:

- Desktops, Notebooks, and Graphics Cards, Servers

- Gaming Set Top Boxes, Printers and Copiers

- Server Core and I/O Supplies

- DSP and FPGA Power Supplies

- SMPS Post-Regulator

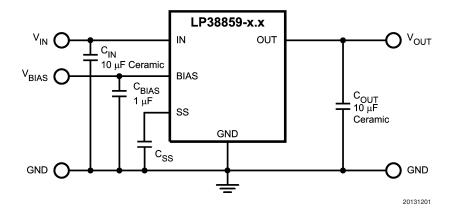

### **Typical Application Circuit**

## Ordering Information 9"LP38859T-0.8"供应商

| V <sub>OUT</sub> * | Order Number  | Package Type | Package Drawing | Supplied As          |

|--------------------|---------------|--------------|-----------------|----------------------|

| 0.8V               | LP38859S-0.8  | TO263-5      | TS5B            | Rail of 45           |

|                    | LP38859SX-0.8 | TO263-5      | TS5B            | Tape and Reel of 500 |

|                    | LP38859T-0.8  | TO220-5      | T05D            | Rail of 45           |

| 1.2V               | LP38859S-1.2  | TO263-5      | TS5B            | Rail of 45           |

|                    | LP38859SX-1.2 | TO263-5      | TS5B            | Tape and Reel of 500 |

|                    | LP38859T-1.2  | TO220-5      | T05D            | Rail of 45           |

<sup>\*</sup> For custom V<sub>OUT</sub> values between 0.8V and 1.2V please contact the National Semiconductor Sales Office.

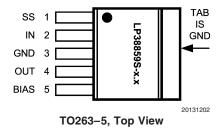

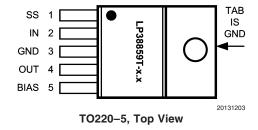

### **Connection Diagrams**

### **Pin Descriptions**

### TO220-5 and TO263-5 Packages

| Pin # | Pin Symbol | Pin Description                                                                             |

|-------|------------|---------------------------------------------------------------------------------------------|

| 1     | SS         | Soft-Start capacitor connection. Used to slow the rise time of V <sub>OUT</sub> at turn-on. |

| 2     | IN         | The unregulated voltage input pin.                                                          |

| 3     | GND        | Ground                                                                                      |

| 4     | OUT        | The regulated output voltage pin.                                                           |

| 5     | BIAS       | The supply for the internal control and reference circuitry.                                |

|       |            | The TAB is a thermal connection that is physically attached to the backside of              |

| TAB   | TAB        | the die, and used as a thermal heat-sink connection. See the Application                    |

|       |            | Information section for details.                                                            |

### **Absolute Maximum Ratings** (Note 1)

If mitary/Acrospace - specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Storage Temperature Range -65°C to +150°C

Lead Temperature

Soldering, 5 seconds 260°C

**ESD Rating**

$\begin{array}{lll} \mbox{Human Body Model (Note 2)} & \pm 2 \mbox{ kV} \\ \mbox{Power Dissipation (Note 3)} & \mbox{Internally Limited} \\ \mbox{V}_{\mbox{IN}} & \mbox{Supply Voltage (Survival)} & -0.3 \mbox{V to } +6.0 \mbox{V} \end{array}$

$V_{\text{BIAS}}$  Supply Voltage (Survival) -0.3V to +6.0V  $V_{\text{SS}}$  SoftStart Voltage (Survival) -0.3V to +6.0V  $V_{OUT}$  Voltage (Survival) -0.3V to +6.0V  $I_{OUT}$  Current (Survival) Internally Limited Junction Temperature  $-40^{\circ}\mathrm{C}$  to  $+150^{\circ}\mathrm{C}$

### Operating Ratings(Note 1)

$\begin{array}{lll} \text{V}_{\text{IN}} & \text{Supply Voltage} & (\text{V}_{\text{OUT}} + \text{V}_{\text{DO}}) \text{ to V}_{\text{BIAS}} \\ \text{V}_{\text{BIAS}} & \text{Supply Voltage} & 3.0 \text{V to } 5.5 \text{V} \\ \text{I}_{\text{OUT}} & 0 \text{ mA to } 3.0 \text{A} \\ \text{Junction Temperature} & -40 ^{\circ} \text{C to } +125 ^{\circ} \text{C} \end{array}$

Range(Note 3)

**Electrical Characteristics** Unless otherwise specified:  $V_{IN} = V_{OUT(NOM)} + 1V$ ,  $V_{BIAS} = 3.0V$ ,  $I_{OUT} = 10$  mA,  $C_{IN} = C_{OUT} = 10$   $\mu$ F,  $C_{BIAS} = 1$   $\mu$ F,  $C_{SS} = open$ . Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in **boldface type** apply over the junction temperature  $(T_J)$  range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only.

| Symbol                           | Parameter                                                                  | Conditions                                                                                                                                                                                             | MIN                 | TYP        | MAX                 | Units |

|----------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|---------------------|-------|

| $V_OUT$                          | V <sub>OUT</sub> Accuracy                                                  | $\begin{split} &V_{OUT(NOM)} + 1V \leq V_{IN} \leq V_{BIAS}, \\ &3.0V \leq V_{BIAS} \leq 5.5V, \\ &10 \text{ mA} \leq I_{OUT} \leq 3A \end{split}$                                                     | -1.0<br>-3.0        | 0.0        | 1.0<br><b>3.0</b>   | %     |

|                                  |                                                                            | $\begin{split} & V_{OUT(NOM)} + 1V \leq V_{IN} \leq V_{BIAS}, \\ & 3.0V \leq V_{BIAS} \leq 5.5V, \\ & 10 \text{ mA} \leq I_{OUT} \leq 3.0A, \\ & 0^{\circ}C \leq T_{J} \leq +125^{\circ}C \end{split}$ | -2.0                | 0.0        | 2.0                 |       |

| $\Delta V_{OUT}/\Delta V_{IN}$   | Line Regulation, V <sub>IN</sub> (Note 4)                                  | $V_{OUT(NOM)} + 1V \le V_{IN} \le V_{BIAS}$                                                                                                                                                            | -                   | 0.04       | -                   | %/V   |

| $\Delta V_{OUT}/\Delta V_{BIAS}$ | Line Regulation, V <sub>BIAS</sub> (Note 4)                                | $3.0V \le V_{BIAS} \le 5.5V$                                                                                                                                                                           | -                   | 0.10       | -                   | %/V   |

| $\Delta V_{OUT}/\Delta I_{OUT}$  | Output Voltage Load Regulation (Note 5)                                    | 10 mA ≤ I <sub>OUT</sub> ≤ 3.0A                                                                                                                                                                        | -                   | 0.2        | -                   | %/A   |

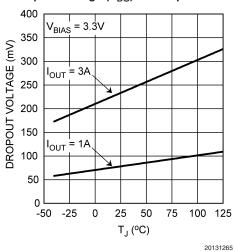

| $V_{DO}$                         | Dropout Voltage (Note 6)                                                   | I <sub>OUT</sub> = 3.0A                                                                                                                                                                                | -                   | 240        | 300<br><b>450</b>   | mV    |

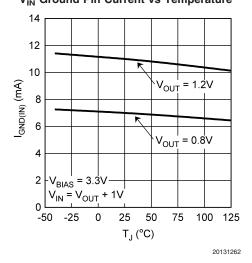

| I <sub>GND(IN)</sub>             | Quiescent Current Drawn from V <sub>IN</sub> Supply                        | LP38859-0.8<br>10 mA ≤ I <sub>OUT</sub> ≤ 3.0A                                                                                                                                                         | -                   | 7.0        | 8.5<br><b>9.0</b>   | mA.   |

|                                  |                                                                            | LP38859-1.2<br>10 mA $\leq$ I <sub>OUT</sub> $\leq$ 3.0A                                                                                                                                               |                     | 11         | 12<br><b>15</b>     | IIIA  |

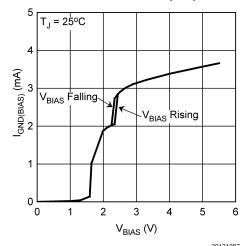

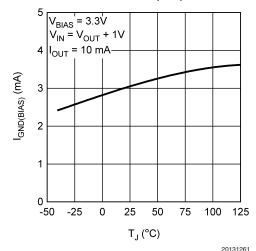

| I <sub>GND(BIAS)</sub>           | Quiescent Current Drawn from V <sub>BIAS</sub> Supply                      | 10 mA ≤ I <sub>OUT</sub> ≤ 3.0A                                                                                                                                                                        | -                   | 3.0        | 3.8<br><b>4.5</b>   | mA    |

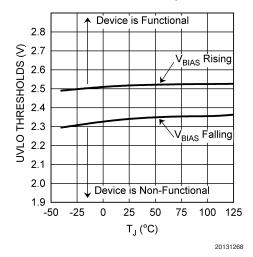

| UVLO                             | Under-Voltage Lock-Out<br>Threshold                                        | V <sub>BIAS</sub> rising until device is functional                                                                                                                                                    | 2.20<br><b>2.00</b> | 2.45       | 2.70<br><b>2.90</b> | V     |

| UVLO <sub>(HYS)</sub>            | Under-Voltage Lock-Out<br>Hysteresis                                       | V <sub>BIAS</sub> falling from UVLO<br>threshold until device is<br>non-functional                                                                                                                     | 60<br><b>50</b>     | 150        | 300<br><b>350</b>   | mV    |

| I <sub>sc</sub>                  | Output Short-Circuit Current                                               | $V_{IN} = V_{OUT(NOM)} + 1V,$<br>$V_{BIAS} = 3.0V, V_{OUT} = 0.0V$                                                                                                                                     | -                   | 6.2        | -                   | А     |

| Soft-Start                       |                                                                            |                                                                                                                                                                                                        |                     |            |                     |       |

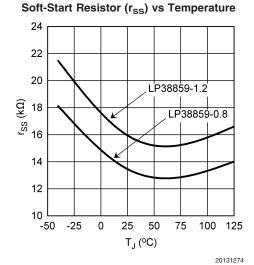

| r <sub>SS</sub>                  | Soft-Start internal resistance                                             | LP38859-0.8                                                                                                                                                                                            | 11.0                | 13.5       | 16.0                | kΩ    |

|                                  | 0.000                                                                      | LP38859-1.2                                                                                                                                                                                            | 13.5                | 16.0       | 18.5                |       |

| t <sub>ss</sub>                  | Soft-Start time<br>t <sub>SS</sub> = C <sub>SS</sub> x r <sub>SS</sub> x 5 | LP38859-0.8, $C_{SS} = 10 \text{ nF}$<br>LP38859-1.2, $C_{SS} = 10 \text{ nF}$                                                                                                                         | -                   | 675<br>800 | -                   | μs    |

| Symbol                | Parameter                                             | Conditions                                    | MIN | TYP | MAX | Units     |

|-----------------------|-------------------------------------------------------|-----------------------------------------------|-----|-----|-----|-----------|

| AC Paramete           | ers                                                   | ,                                             | •   |     |     |           |

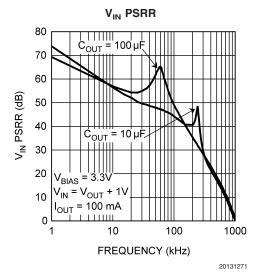

| PSRR                  | Ripple Rejection for V <sub>IN</sub> Input<br>Voltage | $V_{IN} = V_{OUT(NOM)} + 1V,$<br>f = 120 Hz   | -   | 80  | -   |           |

| $(V_{IN})$            |                                                       | $V_{IN} = V_{OUT(NOM)} + 1V,$<br>f = 1 kHz    | -   | 65  | -   | dB        |

| PSRR                  | Ripple Rejection for V <sub>BIAS</sub><br>Voltage     | $V_{BIAS} = V_{OUT(NOM)} + 3V,$<br>f = 120 Hz | -   | 58  | -   | - ив      |

| $(V_{BIAS})$          |                                                       | $V_{BIAS} = V_{OUT(NOM)} + 3V,$<br>f = 1 kHz  | -   | 58  | -   |           |

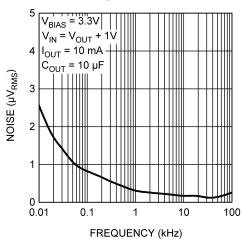

|                       | Output Noise Density                                  | f = 120 Hz                                    | -   | 1   | -   | μV/√Hz    |

| $e_n$                 | Output Noise Voltage                                  | BW = 10 Hz - 100 kHz                          | -   | 150 | -   | \/ (***** |

|                       | V <sub>OUT</sub> = 1.8V                               | BW = 300 Hz - 300 kHz                         | -   | 90  | -   | μV (rms)  |

| hermal Par            | ameters                                               |                                               |     | •   |     |           |

| T <sub>SD</sub>       | Thermal Shutdown Junction Temperature                 |                                               | -   | 160 | -   | - °C      |

| T <sub>SD(HYS)</sub>  | Thermal Shutdown Hysteresis                           |                                               | -   | 10  | -   |           |

| $\theta_{J-A}$        | Thermal Resistance, Junction to Ambient(Note 3)       | TO220-5                                       | -   | 60  | -   | °C/W      |

|                       |                                                       | TO263-5                                       | -   | 60  | -   |           |

| $\theta_{\text{J-C}}$ | Thermal Resistance, Junction to                       | TO220-5                                       | -   | 3   | -   | ] C/W     |

|                       | Case(Note 3)                                          | TO263-5                                       | -   | 3   | -   | 1         |

**Note 1:** Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics.

Note 2: The human body model is a 100 pF capacitor discharged through a 1.5k resistor into each pin. Test method is per JESD22-A114. The HBM rating for device pin 1 (SS) is ±1.5 kV.

**Note 3:** Device power dissipation must be de-rated based on device power dissipation ( $P_D$ ), ambient temperature ( $T_A$ ), and package junction to ambient thermal resistance ( $\theta_{JA}$ ). Additional heat-sinking may be required to ensure that the device junction temperature ( $T_J$ ) does not exceed the maximum operating rating. See the Application Information section for details.

Note 4: Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

Note 5: Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from no load to full load.

Note 6: Dropout voltage is defined the as input to output voltage differential (V<sub>IN</sub> - V<sub>OUT</sub>) where the input voltage is low enough to cause the output voltage to drop no more than 2% from the nominal value.

# Typical Performance Characteristics Unless otherwise specified: $T_J = 25\,^{\circ}\text{C}, \ V_{\text{IN}} = V_{\text{OUT(NOM)}} + 1V, V_{\text{Ba}}$ மு. இ. இ. இ. Ceramic, $C_{\text{BIAS}} = 1\,\mu\text{F}$ Ceramic, $C_{\text{SS}} = \text{open}$ .

### $V_{BIAS}$ Ground Pin Current ( $I_{GND(BIAS)}$ ) vs $V_{BIAS}$

### V<sub>IN</sub> Ground Pin Current vs Temperature

### Dropout Voltage (V<sub>DO</sub>) vs Temperature

### $V_{\text{BIAS}}$ Ground Pin Current ( $I_{\text{GND(BIAS)}}$ ) vs Temperature

### **Load Regulation vs Temperature**

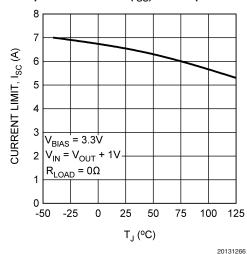

### Output Current Limit (I<sub>SC</sub>) vs Temperature

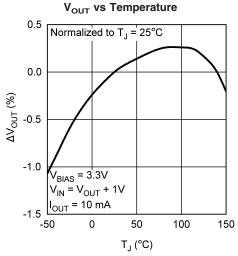

Typical Performance Characteristics Unless otherwise specified:  $T_J = 25^{\circ}C$ ,  $V_{IN} = V_{OUT(NOM)} + 1V$ , 即以及 0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,0.8中间,

### 20131267

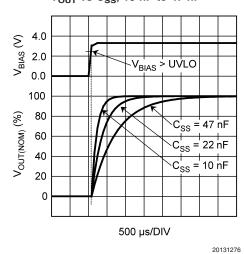

### $m V_{OUT}$ vs $m C_{SS}$ , 10 nF to 47 nF

### **UVLO Thresholds vs Temperature**

### Soft-Start $r_{SS}$ Variation vs Temperature

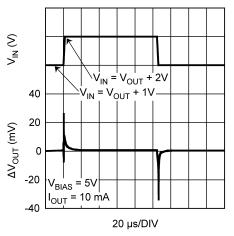

### **VIN Line Transient Response**

20131277

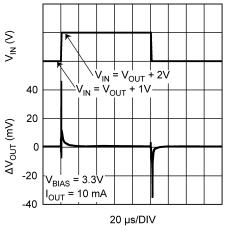

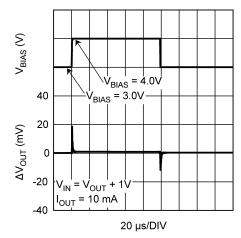

# Typical Performance Characteristics Unless otherwise specified: $T_J = 25^{\circ}C$ , $V_{IN} = V_{OUT(NOM)} + 1V$ , $V_{BI}$ இழும் இது தூற்-ஒது " நட்கு $I_{IJ} = 10~\mu F$ Ceramic, $C_{BIAS} = 1~\mu F$ Ceramic, $C_{SS} = open$ . (Continued)

20131278

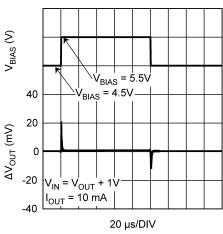

### **V<sub>BIAS</sub>** Line Transient Response

20131279

### **V<sub>BIAS</sub>** Line Transient Response

20131280

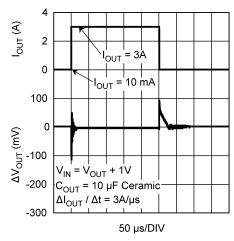

### Load Transient Response, $C_{OUT} = 10 \mu F$ Ceramic

20131281

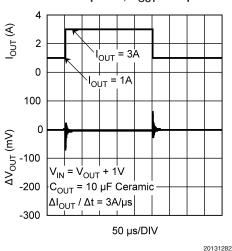

### Load Transient Response, $C_{OUT}$ = 10 $\mu F$ Ceramic

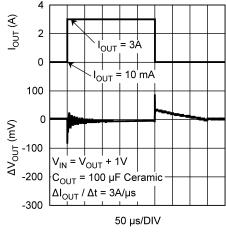

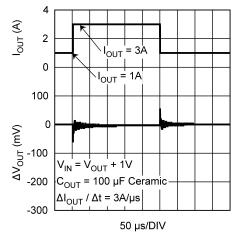

Load Transient Response,  $C_{OUT}$  = 100  $\mu F$  Ceramic

20131283

Typical Performance Characteristics Unless otherwise specified:  $T_J = 25^{\circ}C$ ,  $V_{IN} = V_{OUT(NOM)} + 1V$ , 可以及多数的 $V_T$  的。 $V_{IN} = V_{OUT} = 10$   $V_{OUT} = 10$   $V_{O$

### Load Transient Response, $C_{OUT}$ = 100 $\mu F$ Ceramic

20131284

20131286

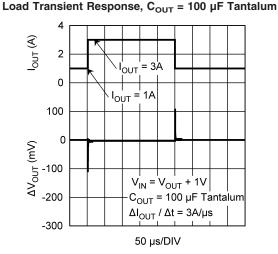

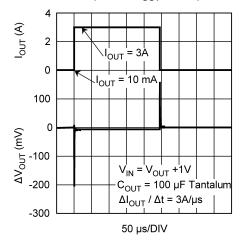

Load Transient Response, C<sub>OUT</sub> = 100 μF Tantalum

20131285

# V<sub>BIAS</sub> PSRR 80 70 C<sub>OUT</sub> = 100 μF 60 40 C<sub>OUT</sub> = 10 μF 10 V<sub>BIAS</sub> = 3.3V V<sub>IN</sub> = V<sub>OUT</sub> + 1V I<sub>OUT</sub> = 100 mA 0 1 10 100 1000 FREQUENCY (kHz)

20131270

20131269

# 图lock Diagram 查询"LP38859T-0.8"供应商 LP38859-x.x BIAS Under-Voltage Lock-Out Thermal Shut Down YREF VREF VREF VREF Z0131205

### **Application Information**

旬"LP38859T-0.8"供应商

To assure regulator stability, input and output capacitors are required as shown in the Typical Application Circuit.

### **Output Capacitor**

A minimum output capacitance of 10  $\mu$ F, ceramic, is required for stability. The amount of output capacitance can be increased without limit. The output capacitor must be located less than 1 cm from the output pin of the IC and returned to the device ground pin with a clean analog ground.

Only high quality ceramic types such as X5R or X7R should be used, as the Z5U and Y5F types do not provide sufficient capacitance over temperature.

Tantalum capacitors will also provide stable operation across the entire operating temperature range. However, the effects of ESR may provide variations in the output voltage during fast load transients. Using the minimum recommended 10  $\mu\text{F}$  ceramic capacitor at the output will allow unlimited capacitance, Tantalum and/or Aluminum, to be added in parallel.

### **Input Capacitor**

The input capacitor must be at least 10  $\mu$ F, but can be increased without limit. It's purpose is to provide a low source impedance for the regulator input. A ceramic capacitor, X5R or X7R, is recommended.

Tantalum capacitors may also be used at the input pin. There is no specific ESR limitation on the input capacitor (the lower, the better).

Aluminum electrolytic capacitors can be used, but are not recommended as their ESR increases very quickly at cold temperatures. They are not recommended for any application where the ambient temperature falls below 0°C.

### **Bias Capacitor**

The capacitor on the bias pin must be at least 1 µF, and can be any good quality capacitor (ceramic is recommended).

### INPUT VOLTAGE

The input voltage  $(V_{IN})$  is the high current external voltage rail that will be regulated down to a lower voltage, which is applied to the load. The input voltage must be at least  $V_{OUT} + V_{DO}$ , and no higher than whatever values is used for  $V_{BIAS}$ .

### **BIAS VOLTAGE**

The bias voltage ( $V_{\rm BIAS}$ ) is a low current external voltage rail required to bias the control circuitry and provide gate drive for the N-FET pass transistor. The bias voltage must be in the range of 3.0V to 5.5V to ensure proper operation of the device.

### **UNDER VOLTAGE LOCKOUT**

The bias voltage is monitored by a circuit which prevents the device from functioning when the bias voltage is below the Under-Voltage Lock-Out (UVLO) threshold of approximately 2.45V.

As the bias voltage rises above the UVLO threshold the device control circuitry becomes active. There is approximately 150 mV of hysteresis built into the UVLO threshold to provide noise immunity.

When the bias voltage is between the UVLO threshold and the Minimum Operating Rating value of 3.0V the device will be functional, but the operating parameters will not be within the guaranteed limits.

### **SUPPLY SEQUENCING**

There is no requirement for the order that  $V_{\text{IN}}$  or  $V_{\text{BIAS}}$  are applied or removed.

One practical limitation is that the Soft-Start circuit starts charging  $C_{\rm SS}$  when  $V_{\rm BIAS}$  rises above the UVLO threshold. If the application of  $V_{\rm IN}$  is delayed beyond this point the benefits of Soft-Start will be compromised.

In any case, the output voltage cannot be guaranteed until both  $V_{\rm IN}$  and  $V_{\rm BIAS}$  are within the range of guaranteed operating values.

If used in a dual-supply system where the regulator output load is returned to a negative supply, the output pin must be diode clamped to ground. A Schottky diode is recommended for this diode clamp.

### **REVERSE VOLTAGE**

A reverse voltage condition will exist when the voltage at the output pin is higher than the voltage at the input pin. Typically this will happen when  $V_{\rm IN}$  is abruptly taken low and  $C_{\rm OUT}$  continues to hold a sufficient charge such that the input to output voltage becomes reversed.

The NMOS pass element, by design, contains no body diode. This means that, as long as the gate of the pass element is not driven, there will not be any reverse current flow through the pass element during a reverse voltage event. The gate of the pass element is not driven when  $V_{\rm BIAS}$  is below the UVLO threshold.

When  $V_{BIAS}$  is above the UVLO threshold the control circuitry is active and will attempt to regulate the output voltage. Since the input voltage is less than the output voltage the control circuit will drive the gate of the pass element to the full  $V_{BIAS}$  potential when the output voltage begins to fall. In this condition, reverse current will flow from the output pin to the input pin , limited only by the  $R_{DS(ON)}$  of the pass element and the output to input voltage differential. This condition is outside the guaranteed operating range and should be avoided.

### **SOFT-START**

The LP38859 incorporates a Soft-Start function that reduces the start-up current surge into the output capacitor ( $C_{OUT}$ ) by allowing  $V_{OUT}$  to rise slowly to the final value. This is accomplished by controlling  $V_{REF}$  at the SS pin. The soft-start timing capacitor ( $C_{SS}$ ) is internally held to ground until  $V_{BIAS}$  rises above the Under-Voltage Lock-Out threshold (ULVO).

$V_{REF}$  will rise at an RC rate defined by the internal resistance of the SS pin ( $r_{SS}$ ), and the external capacitor connected to the SS pin. This allows the output voltage to rise in a controlled manner until steady-state regulation is achieved. Typically, five time constants are recommended to assure that the output voltage is sufficiently close to the final steady-state value. During the soft-start time the output current can rise to the built-in current limit.

Soft-Start Time =

$$C_{SS} \times r_{SS} \times 5$$

(1)

### Application Information (Continued)

Since  $\Gamma_{OUT}$  rise will be exponentian not linear, the in-rush current will peak during the first time constant  $(\tau)$ , and  $V_{OUT}$  will require four additional time constants  $(4\tau)$  to reach the final value  $(5\tau)$ .

After achieving normal operation, should  $V_{\rm BIAS}$  fall below the ULVO threshold the device output will be disabled and the Soft-Start capacitor ( $C_{\rm SS}$ ) discharge circuit will become active. The  $C_{\rm SS}$  discharge circuit will remain active until  $V_{\rm BIAS}$  falls to 500 mV (typical). When  $V_{\rm BIAS}$  falls below 500 mV (typical), the  $C_{\rm SS}$  discharge circuit will cease to function due to a lack of sufficient biasing to the control circuitry.

Since  $V_{REF}$  appears on the SS pin, any leakage through  $C_{SS}$  will cause  $V_{REF}$  to fall, and thus affect  $V_{OUT}$ . A leakage of 50 nA (about 10 M $\Omega$ ) through  $C_{SS}$  will cause  $V_{OUT}$  to be approximately 0.1% lower than nominal, while a leakage of 500 nA (about 1 M $\Omega$ ) will cause  $V_{OUT}$  to be approximately 1% lower than nominal. Typical ceramic capacitors will have a factor of 10X difference in leakage between 25°C and 85°C, so the maximum ambient temperature must be included in the capacitor selection process.

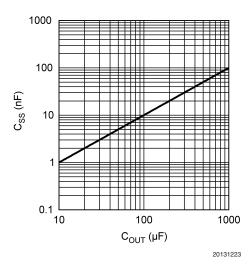

Typical  $C_{SS}$  values will be in the range of 1 nF to 100 nF, providing typical Soft-Start times in the range of 70  $\mu$ s to 7 ms (5 $\tau$ ). Values less than 1 nF can be used, but the Soft-Start effect will be minimal. Values larger than 100 nF will provide soft-start, but may not be fully discharged if  $V_{BIAS}$  falls from the UVLVO threshold to less than 500 mV in less than 100  $\mu$ s.

Figure 1 shows the relationship between the  $C_{\text{OUT}}$  value and a typical  $C_{\text{SS}}$  value.

FIGURE 1. Typical  $C_{SS}$  vs  $C_{OUT}$  Values

The  $C_{SS}$  capacitor must be connected to a clean ground path back to the device ground pin. No components, other than  $C_{SS}$ , should be connected to the SS pin, as there could be adverse effects to  $V_{OUT}$ .

If the Soft-Start function is not needed the SS pin should be left open, although some minimal capacitance value is always recommended.

### POWER DISSIPATION AND HEAT-SINKING

Additional copper area for heat-sinking may be required depending on the maximum device dissipation ( $P_D$ ) and the maximum anticipated ambient temperature ( $T_A$ ) for the de-

vice. Under all possible conditions, the junction temperature must be within the range specified under operating conditions.

The total power dissipation of the device is the sum of three different points of dissipation in the device.

The first part is the power that is dissipated in the NMOS pass element, and can be determined with the formula:

$$P_{D(PASS)} = (V_{IN} - V_{OUT}) \times I_{OUT}$$

(2)

The second part is the power that is dissipated in the bias and control circuitry, and can be determined with the formula:

$$P_{D(B|AS)} = V_{B|AS} \times I_{GND(B|AS)}$$

(3)

where  $I_{\rm GND(BIAS)}$  is the portion of the operating ground current of the device that is related to  $V_{\rm BIAS}.$

The third part is the power that is dissipated in portions of the output stage circuitry, and can be determined with the formula:

$$P_{D(IN)} = V_{IN} \times I_{GND(IN)}$$

(4)

where  $I_{GND(IN)}$  is the portion of the operating ground current of the device that is related to  $V_{IN}$ .

The total power dissipation is then:

$$P_{D} = P_{D(PASS)} + P_{D(BIAS)} + P_{D(IN)}$$

(5)

The maximum allowable junction temperature rise  $(\Delta T_J)$  depends on the maximum anticipated ambient temperature  $(T_A)$  for the application, and the maximum allowable operating junction temperature  $(T_{J(MAX)})$ .

$$\Delta T_{J} = T_{J(MAX)} - T_{A(MAX)}$$

(6)

The maximum allowable value for junction to ambient Thermal Resistance,  $\theta_{JA}$ , can be calculated using the formula:

$$\theta_{JA} \le \frac{\Delta T_J}{P_D}$$

(7)

### Heat-Sinking The TO-220 Package

The TO220-5 package has a  $\theta_{JA}$  rating of  $60^{\circ}\text{C/W}$  and a  $\theta_{JC}$  rating of  $3^{\circ}\text{C/W}$ . These ratings are for the package only, no additional heat-sinking, and with no airflow. If the needed  $\theta_{JA}$ , as calculated above, is greater than or equal to  $60^{\circ}\text{C/W}$  then no additional heat-sinking is required since the package can safely dissipate the heat and not exceed the operating  $T_{J(MAX)}$ . If the needed  $\theta_{JA}$  is less than  $60^{\circ}\text{C/W}$  then additional heat-sinking is needed.

The thermal resistance of a TO-220 package can be reduced by attaching it to a heat sink or a copper plane on a PC board. If a copper plane is to be used, the values of  $\theta_{JA}$  will be same as shown in next section for TO-263 package.

The heat-sink to be used in the application should have a heat-sink to ambient thermal resistance,  $\theta_{\text{HA}}$ :

### Application Information (Continued)

旬"LP38859T-0.8"供应商

$$\theta_{HA} \le \theta_{JA} - (\theta_{CH} + \theta_{JC})$$

(8)

where  $\theta_{JA}$  is the required total thermal resistance from the junction to the ambient air,  $\theta_{CH}$  is the thermal resistance from the case to the surface of the heart-sink, and  $\theta_{JC}$  is the thermal resistance from the junction to the surface of the case.

For this equation,  $\theta_{JC}$  is about 3°C/W for a TO-220 package. The value for  $\theta_{CH}$  depends on method of attachment, insulator, etc.  $\theta_{CH}$  varies between 1.5°C/W to 2.5°C/W. Consult the heat-sink manufacturer datasheet for details and recommendations.

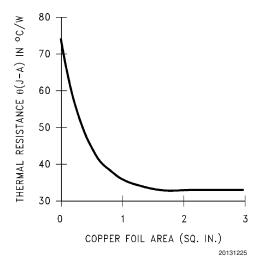

### Heat-Sinking The TO-263 Package

The TO-263 package has a  $\theta_{JA}$  rating of 60°C/W, and a  $\theta_{JC}$  rating of 3°C/W. These ratings are for the package only, no additional heat-sinking, and with no airflow.

The TO-263 package uses the copper plane on the PCB as a heat-sink. The tab of this package is soldered to the copper plane for heat sinking. shows a curve for the  $\theta_{\rm JA}$  of TO-263 package for different copper area sizes, using a typical PCB with 1 ounce copper and no solder mask over the copper area for heat-sinking.

FIGURE 2.  $\theta_{JA}$  vs Copper (1 Ounce) Area for the TO-263 package

Figure 2 shows that increasing the copper area beyond 1 square inch produces very little improvement. The minimum value for  $\theta_{JA}$  for the TO-263 package mounted to a PCB is 32°C/W.

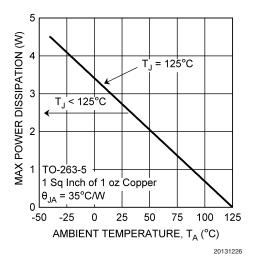

Figure 3 shows the maximum allowable power dissipation for TO-263 packages for different ambient temperatures, assuming  $\theta_{JA}$  is 35°C/W and the maximum junction temperature is 125°C.

FIGURE 3. Maximum power dissipation vs ambient temperature for the TO-263 package

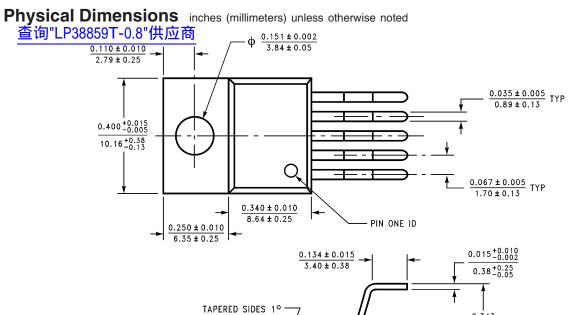

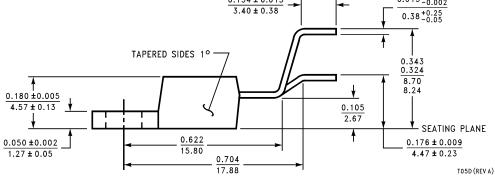

TO-220 5-Lead, Stagger Bend Package (TO220-5) NS Package Number TO5D

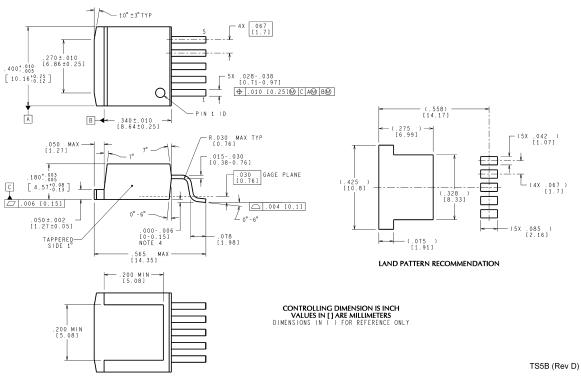

TO-263 5-Lead, Molded, Surface Mount Package (TO263-5) NS Package Number TS5B

|       | tart                                               |   |

|-------|----------------------------------------------------|---|

| (     |                                                    |   |

| (     | S                                                  |   |

|       | WITP                                               |   |

|       | High-Accuracy LDO Linear Requiator with Soft+Start | • |

| (     | ž                                                  | , |

| -     | _inear                                             |   |

| •     | _<br>_                                             |   |

|       | בַּ                                                |   |

|       | Iracv                                              | • |

| •     | Accu                                               |   |

| -     |                                                    | ) |

| •     | se F                                               |   |

|       | <b>Fast-Response F</b>                             | - |

| [<br> | <b>Fast-F</b>                                      |   |

**Notes**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

**National Semiconductor** Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor **Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560