### FEATURES

- 12-bit resolution

- 1.0 and 1.5MHz throughput rates

- Small 44-pin Leaded Chip Carrier

- Single +5V supply

- Low power, 75 and 200mW maximum

- · Low power "standby" mode

- Outstanding dynamic performance

- No missing codes over temperature

- · Built-in sample-and-hold

- · Optional two-channel input multiplexer

- Ideal for both time and frequency-domain applications

DZSC.COM

#### **GENERAL DESCRIPTION**

The ADS-230 and ADS-231 are 12-bit, high speed CMOS sampling analog-to-digital converters capable of minimum sampling rates of 1.0 and 1.5MHz, respectively. Both models feature excellent dynamic performance including a typical SNR of 72dB for the ADS-230 and 70dB for the ADS-231.

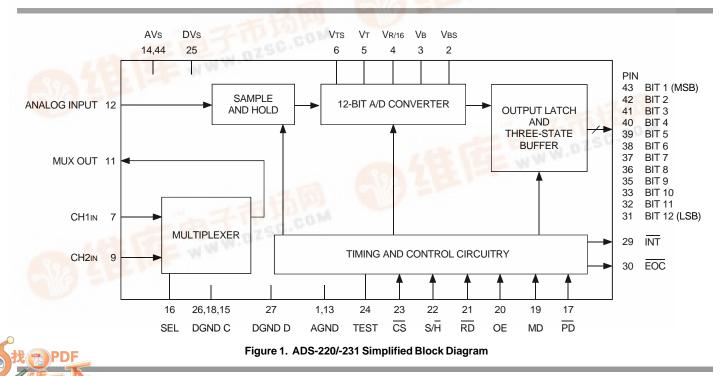

The ADS-230 and ADS-231 are packaged in a small 44-pin plastic Leaded Chip Carrier (LCC). Each model contains a fast-settling sample/hold amplifier, a multipass (three-step flash) A/D converter, timing and control logic, three-state outputs, a two-channel multiplexer, and digital error correction circuitry. Digital input and output levels are TTL.

Requiring only a single +5V supply, the ADS-230 typically dissipates only 60mW and the ADS-231 only 170mW. Both models offer a low-power "standby" mode resulting in typical power dissipations of  $100\mu$ W and  $250\mu$ W, respectively. The units offer a maximum unipolar input range of 0 to +5V. The exact value of the input range is determined by an externally applied reference voltage. Both models operate over the extended –40 to +85°C temperature range.

# ADS-230/ADS-231 Low-Power, 12-Bit, 1.0/1.5MHz Sampling A/D Converter

### **INPUT/OUTPUT CONNECTIONS**

| PIN | FUNCTION     | PIN | FUNCTION     |

|-----|--------------|-----|--------------|

| 1   | AGND         | 44  | AVs          |

| 2   | VBS          | 43  | BIT 1 (MSB)  |

| 3   | Vв           | 42  | BIT 2        |

| 4   | VR/16        | 41  | BIT 3        |

| 5   | Vτ           | 40  | BIT 4        |

| 6   | VTS          | 39  | BIT 5        |

| 7   | CH1IN        | 38  | BIT 6        |

| 8   | NC           | 37  | BIT 7        |

| 9   | CH2IN        | 36  | BIT 8        |

| 10  | NC           | 35  | BIT 9        |

| 11  | MUX OUT      | 34  | NC           |

| 12  | ANALOG INPUT | 33  | BIT 10       |

| 13  | AGND         | 32  | BIT 11       |

| 14  | AVs          | 31  | BIT 12 (LSB) |

| 15  | DGND C       | 30  | EOC          |

| 16  | SEL          | 29  | INT          |

| 17  | PD           | 28  | NC           |

| 18  | DGND C       | 27  | DGND D       |

| 19  | MD           | 26  | DGND C       |

| 20  | OE           | 25  | DVs          |

| 21  | RD           | 24  | TEST         |

| 22  | S/H          | 23  | CS           |

DATEL, Inc., Mansfield, MA 02048 (U.S.A.) • Tel: (508) 339-3000, (800) 233-2765 Fax: (508) 339-6356 • Email: sales@datel.com • Internet: www.datel.com

## ABS在词语和AXANU供在A育NGS

| PARAMETERS                       | LIMITS          | UNITS |

|----------------------------------|-----------------|-------|

| Supply Voltages                  |                 |       |

| (Vs = AVs = DVs)                 | -0.3 to +6      | V     |

| Input or Output Voltage, any pin | -0.3 to Vs +0.3 | V     |

| Input Current, any pin ①         | 25              | mA    |

| Total Package Input Current, ①   | 50              | mA    |

| Power Dissipation, 2             | 875             | mW    |

| ESD Susceptibilty, 3             | 2000            | V     |

| Soldering, Infrared, 15 seconds  | +300            | °C    |

### PHYSICAL/ENVIRONMENTAL

| PARAMETERS                           | MIN.                               | TYP. | MAX. | UNITS   |

|--------------------------------------|------------------------------------|------|------|---------|

| <b>Operating Temp. Range</b> TA = TJ | -40                                |      | +85  | °C      |

| Thermal Impedance, θja               | _                                  | 55   | _    | °C/Watt |

| Maximum Junction Temp. TJMAX         | _                                  | _    | +150 | °C      |

| Storage Temperature Range            | -65                                | _    | +150 | °C      |

| PackageType                          | 44-pin Plastic Leaded Chip Carrier |      |      |         |

### FUNCTIONAL SPECIFICATIONS

(The following specifications apply for TA = TJ = 25°C, DVs = AVs = 5.0V, VTs = +4.096V, VBs = AGND, Rs = 25ohms and Fs = 1.0/1.5MHz for the ADS-230/231 respectively, unless otherwise specified.)

|                                                    |       | ADS-230 |          |       | ADS-231 |          |       |  |

|----------------------------------------------------|-------|---------|----------|-------|---------|----------|-------|--|

|                                                    | +25°C | -40 te  | o +85°C  | +25°C | -40 1   | to +85°C |       |  |

| ANALOG INPUT                                       | TYP.  | MIN.    | MAX.     | TYP.  | MIN.    | MAX.     | UNITS |  |

| Input Voltage Range (Pins 7, 9, 12)                | _     | -0.05   | AVs+0.05 | _     | -0.05   | AVs+0.05 | V     |  |

| Input Leakage Current                              | 0.1   | _       | 3        | 0.1   | _       | 3        | μΑ    |  |

| Input Capacitance                                  | 25    | _       | _        | 25    | _       | _        | pF    |  |

| MUX On/Off-Channel Leakage                         | 0.1   | _       | 3        | 0.1   | _       | 3        | μA    |  |

| MUX Input Capacitance                              | 7     | _       | _        | 7     | _       |          | pF    |  |

| MUX Off-Channel Isolation                          |       |         |          |       |         |          |       |  |

| Fın = 100kHz, –0dB                                 | 92    | -       | -        | 92    | —       | -        | dB    |  |

| REFERENCE INPUT                                    |       |         | •        |       |         |          |       |  |

| Reference Input + (Pin 6), VTS                     | _     | _       | AVs      | _     | _       | AVs      | V     |  |

| Reference Input – (Pin 2), VBS                     | _     | 0       | _        | _     | 0       | _        | V     |  |

| Reference Resistance                               | 750   | 500     | 1000     | 750   | 500     | 1000     | Ohms  |  |

| DIGITAL INPUT                                      |       |         |          |       | 1       |          | 1     |  |

| Logic Levels                                       |       |         |          |       |         |          |       |  |

| Logic "1", Vs = 5.5V                               | _     | 2       | _        | _     | 2       | _        | V     |  |

| Logic "0", Vs = 4.5V                               | _     | _       | 0.8      | _     | _       | 0.8      | V     |  |

| Logic Loading "1"                                  | 0.1   | _       | 1        | 0.1   | _       | 1        | μΑ    |  |

| Logic Loading "0"                                  | 0.1   | _       | 1        | 0.1   | _       | 1        | μA    |  |

| Digital Input Capacitance                          | 4     | _       | _        | 4     | _       | _        | pF    |  |

| S/Ă Pulse Width ④, ts/H                            | —     | 5       | 550      | -     | 5       | 400      | ns    |  |

| STATIC PERFORMANCE                                 |       |         |          |       |         |          |       |  |

| Resolution                                         |       | 12      |          |       | 12      |          | Bits  |  |

| Integral Nonlinearity                              | ±0.4  | _       | ±1.5     | ±0.4  | _       | ±1.5     | LSB   |  |

| Differential Nonlinearity Error                    | ±0.4  | _       | ±0.95    | ±0.4  | _       | ±0.95    | LSB   |  |

| No Missing Codes                                   | _     | 12      | —        | _     | 12      | _        | Bits  |  |

| Offset Error                                       | ±0.3  | —       | ±2.0     | ±0.3  | _       | ±2.0     | LSB   |  |

| Gain Error                                         | ±0.2  | —       | ±1.5     | ±0.3  | —       | ±1.5     | LSB   |  |

| Power Supply Sensitivity, (±10%)                   | —     | _       | ±1.0     | -     | -       | ±0.75    | LSB   |  |

| DYNAMIC PERFORMANCE (5)                            |       |         | -        | -     | -       |          | -     |  |

| Total Harmonic Distortion (-0dB)                   |       |         |          |       |         |          |       |  |

| Fin = 100kHz 6                                     | -82   | —       | -70      | -80   | _       | -70      | dB    |  |

| Signal-to-Noise Ratio                              |       |         |          |       |         |          |       |  |

| (wo/distortion, –0dB) FIN = 100kHz                 | 72    | 69.5    | -        | 70    | 67.5    | -        | dB    |  |

| Signal-to-Noise Ratio 🕖                            |       |         |          |       |         |          |       |  |

| (& distortion, –0dB) FIN = 100kHz                  | 71    | 68      | -        | 70    | 67      | —        | dB    |  |

| Two-Tone Intermodulation Distortion                |       |         |          |       |         |          |       |  |

| FIN = 102.3, 102.7kHz, (-0dB)                      | -80   | —       | -        | -80   | -       | —        | dB    |  |

| Aperature Delay Time, (tAD)<br>A/D Conversion Rate | 20    | —       | _        | 20    | —       | —        | ns    |  |

|                                                    | _     | 1       | _        | _     | 1.5     | _        | MHz   |  |

|                                        | ADS-230 |              |      | ADS-231 |              |      |       |

|----------------------------------------|---------|--------------|------|---------|--------------|------|-------|

|                                        | +25°C   | –40 to +85°C |      | +25°C   | –40 to +85°C |      | 1     |

| TIMING                                 | TYP.    | MIN.         | MAX. | TYP.    | MIN.         | MAX. | UNITS |

| Conversion Time, tCONV                 | 740     | 600          | 980  | 580     | 510          | 660  | ns    |

| Time for Conversion to Start, tEOC     | 95      | 60           | 125  | 90      | 60           | 125  | ns    |

| Access Time, tacc (CL = 100pF)         | 10      | _            | 20   | 10      | —            | 20   | ns    |

| Three-State Control Time, t1H, t0H     |         |              |      |         |              |      |       |

| RL = 1k, CL = 10pF                     | 25      | _            | 40   | 25      | _            | 40   | ns    |

| Delay Time, RD Low to INT High         |         |              |      |         |              |      |       |

| tINTH, CL = 100pF                      | 35      | _            | 60   | 35      | _            | 60   | ns    |

| Delay Time, EOC High to INT Low        |         |              |      |         |              |      |       |

| tINTL, CL = 100pF                      | 25      | 35           | 10   | 25      | 35           | 10   | ns    |

| EOC High to Data Valid, tupdate        | 5       | —            | 15   | 5       | —            | 15   | ns    |

| MUX Address Setup Time, tms            | _       | 50           | -    | _       | 50           | _    | ns    |

| MUX Address Hold Time, tMH             | _       | 50           | _    | _       | 50           | _    | ns    |

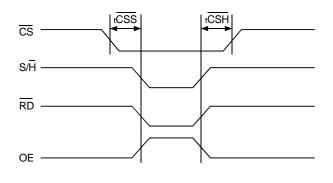

| CS Setup Time, toss                    | —       | 20           | _    | —       | 20           | —    | ns    |

| CS Hold Time, tcsh                     | —       | 20           | _    | —       | 20           | —    | ns    |

| Wake-up Time, twu                      |         |              |      |         |              |      |       |

| PD High to First S/H Low               | 1       | —            | -    | 1       | —            | —    | μs    |

| DIGITAL OUTPUT                         |         |              |      | -       |              |      |       |

| Logic Levels                           |         |              |      |         |              |      |       |

| Logic "1" (Vs = 4.5V)                  | _       | 2.4          | _    | _       | 2.4          | _    | V     |

| Logic "0", $(Vs = 4.5V)$               | _       | _            | 0.4  | _       | _            | 0.4  | V     |

| Logic Loading "1"                      | _       | _            | -360 | _       | _            | -360 | μA    |

| Logic Loading "0"                      | _       | _            | 1.6  | _       | _            | 1.6  | mA    |

| Three-State Output Leakage             | 0.1     | _            | 3    | 0.1     | _            | 3    | μA    |

| Three-State Output Capacitance         | 5       | —            | _    | 5       | —            | _    | pF    |

| Output Coding                          | Binary  |              |      | Binary  |              |      |       |

| POWER REQUIREMENTS                     |         |              |      |         |              |      |       |

| Power Supply Range                     |         |              |      |         |              |      |       |

| +5V Supply, Vs = AVs = DVs             | _       | 4.5          | 5.5  | _       | 4.75         | 5.25 | V     |

| Power Supply Current                   |         |              |      |         |              |      |       |

| DVs Supply Current, DIs                | 2       | —            | 3    | 2       | _            | 3    | mA    |

| AVs Supply Current, Als                | 10      | _            | 12   | 32      | _            | 37   | mA    |

| Standby Current (Als +Dls, PD = 0) (8) | 20      | _            | _    | 50      | _            | _    | μA    |

|                                        | 1       | 1            | 75   |         | 1            | 200  | mW    |

#### Footnotes:

0 When the input voltage at any pin exceeds the power supply rails (below GND or Above Vs) the input current must be limited to  $\pm 25 mA$  or less. The package input current limits to two the number of pins that can meet this constant.

- ② In most cases, the maximum derated power dissipation will be reached only during fault conditions.

- ③ This is the ESD rating for the human body model, with a 100pF capacitor discharged through a 1.5 kilohm resistor. The ESD rating for the machine model is 200V.

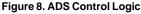

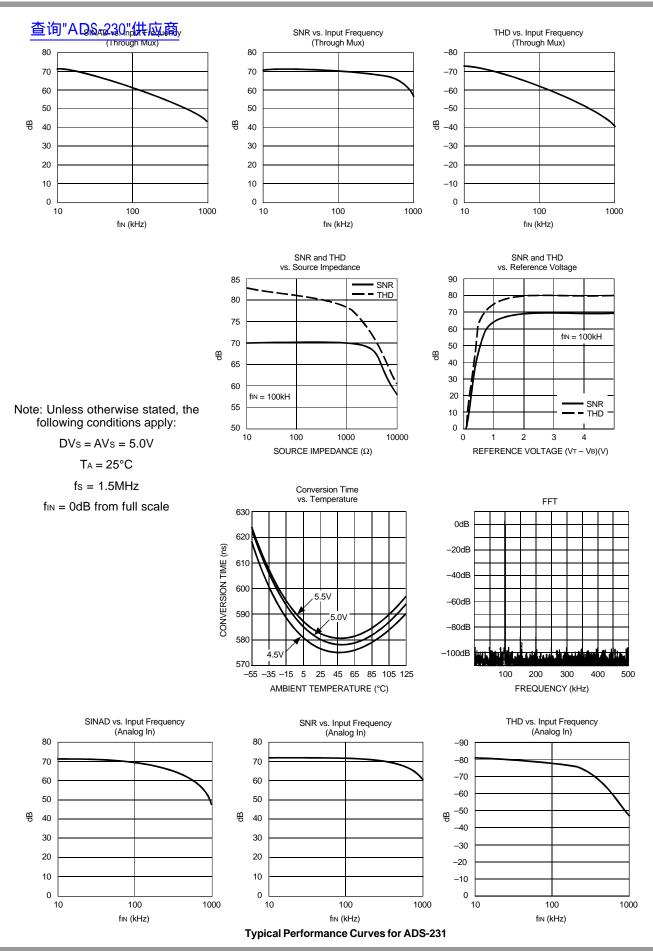

④ For best performance, the rising edge of the S/H pulse must not be near either the falling or rising edge of EOC. The recommended values of ts/H are: ADS-230: 5ns<ts/H<40ns, or 150ns<ts/H<550ns ADS-231: 5ns<ts/H<40ns, or 150ns<ts/H<400ns</p> ⑤ The MUX inputs CH1IN and CH2IN are not used during dynamic testing of these models. The internal multiplexer adds harmonic distortion at high input frequencies. See the Typical Performance Curves for THD with and without the MUX.

<sup>®</sup> The contributions from the first nine harmonics are used in the calculation of THD.

⑦ Effective bits is equal to:

6.02

## ADS-230/ADS-231

| 查询"ADS-230"供应商     | PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                      |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVs, DVs           | These are the analog and digital power supply input pins. They should all be connected to the same voltage source. Both AVs pins should be bypassed to AGND and the DVs pin to DGNDD. Bypass using a $0.1\mu$ F ceramic capacitor in parallel with a $10\mu$ F tantalum capacitor.                    |

| AGND, DGNDC, DGNDD | These are the analog and digital ground pins. All of the ground pins should be returned to the same potential and connected to a stable, noise-free system ground. AGND is the analog ground. DGNDC is the ground for the digital control lines. DGNDD is the digital ground for the output data bus. |

| BIT 1 – BIT 12     | These are the three-state data output pins. Output is enabled by $\overline{RD}$ , $\overline{CS}$ , and OE.                                                                                                                                                                                          |

| CH1ın, CH2ın       | These are the analog input pins to the internal input multiplexer.                                                                                                                                                                                                                                    |

| MUX OUT            | This is the output of the internal multiplexer,                                                                                                                                                                                                                                                       |

| ANALOG INPUT       | This is the direct input to the sampling A to D converter.                                                                                                                                                                                                                                            |

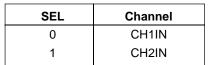

| SEL                | This is <u>the multiplexer channel select pin</u> . The input is selected based on the state of SEL when EOC transitions low. A low selects channel one and a high selects channel two. See Table 1.                                                                                                  |

| MD                 | Connect to DGNDC                                                                                                                                                                                                                                                                                      |

| TEST               | Connect to DVs.                                                                                                                                                                                                                                                                                       |

| CS                 | This is the $\overline{\text{Chip Select}}$ control input. When low, this pin enables the $\overline{\text{RD}}$ , S/H and OE inputs. This pin can be tied low.                                                                                                                                       |

| ĪNT                | This is the Interrupt output pin. When using the Interrupt Interface Mode, this output goes low when a conversion is completed and indicates that the data is available in the output latches. This output is always high when RD is held low. Refer to the Timing Diagrams.                          |

| EOC                | This is the End of Conversion output pin. $\overline{\text{EOC}}$ is low during a conversion.                                                                                                                                                                                                         |

| RD                 | This is the Read control input pin. When $\overline{RD}$ and $\overline{CS}$ are low, the $\overline{INT}$ output is reset and, if EOC is high, data appears on the data bus. This pin can be tied low.                                                                                               |

| OE                 | This is the Output Enable control input pin. The data outpu <u>t p</u> ins ar <u>e i</u> n the high impedance state when OE is low. Data appears when OE is high and CS and RD are both low. This pin can be tied high.                                                                               |

| S/H                | This is the Sample and Hold control input pin. When $\overline{\text{CS}}$ is low a new conversion is initiated by the falling edge of this input.                                                                                                                                                    |

| PD                 | This is the Power Down control input pin. This pin is held high for normal operation. When the input is low, the A to D converter goes into power standby mode.                                                                                                                                       |

| VR/16              | Bypass this pin to AGND using a 0.1µF ceramic capacitor.                                                                                                                                                                                                                                              |

| VT, VB             | These are the positive (top) and negative (bottom) voltage reference force input pins, respectively.                                                                                                                                                                                                  |

| VTS, VBS           | These are the positive (top) and negative (bottom) voltage reference sense pins, respectively.                                                                                                                                                                                                        |

## T在海NADE-NOT 供应商

#### The Analog Input

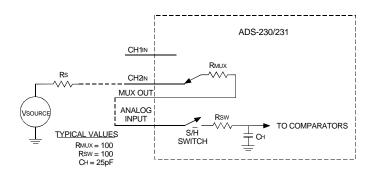

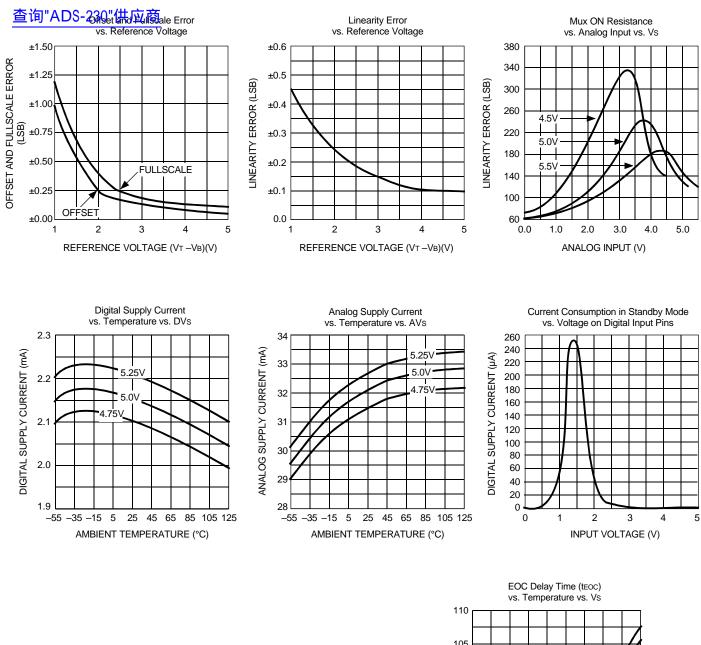

For maximum performance, the source impedance driving the input of the ADS-230/-231 should be as low as possible. A source impedance of less than 100 ohms is recommended. See the Typical Performance Curves.

If the signal source has high output impedance, the output should be buffered with an op-amp capable of driving a switched 25pF/100ohm load. Any ringing or instability of the op-amp during the sampling period can cause conversion errors.

Using a high-speed buffer also improves the THD performance when using the internal MUX. The MUX onresistance is non-linear over the range of the input voltage; this causes the RC time constant of the equivalent circuit shown in Figure 2 to vary with input voltage. This results in harmonic distortion with increasing frequency. Inserting a buffer between the MUX OUT and ANALOG INPUT terminals will eliminate the loading on RMUX and significantly reduce THD.

The analog input of the ADS-230/-231 can be modeled as shown in Figure 2. The S/H switch is closed during the sample period, and open during hold. The hold capacitor (CH) has to be charged to the input voltage by the source within the sample period. The source impedance (Rs) will directly effect the charge time. If Rs is too large, the voltage across CH will not settle to within  $\frac{1}{2}$  LSB's of the source voltage before conversion begins. This will result in conversion errors.

The combination of Rs, RMUX, Rsw and CH form a low-pass filter. Therefore, minimizing Rs will increase the frequency response of the converter.

The settling time to n bits is:

tsettle = (Rs + RMUX + Rsw) \* CH \* n \* In(2)

The bandwidth of the input circuit is:

F (-3dB) = 1/[2 \* 3.14 \* (Rs + RMUX + Rsw) \* CH]

#### **Internal Multiplexer**

Both the ADS-230 and ADS-231 have an internal multiplexer that is controlled by the logic level on the SEL pin when EOC goes low. See the timing diagrams. The MUX setup and hold times can be determined from the following:

$\begin{array}{l} tMS({\sf wrt}\;{\sf S}/{\sf H}) = tMS - tEOC\;({\sf min}) \\ tMS({\sf wrt}\;{\sf S}/{\sf H}) = 50-60 \\ tMS({\sf wrt}\;{\sf S}/{\sf H}) = -10ns \\ tMH({\sf wrt}\;{\sf S}/{\sf H}) = tMH + tEOC\;({\sf max}) \\ tMH({\sf wrt}\;{\sf S}/{\sf H}) = 50\;+125 \\ tMH({\sf wrt}\;{\sf S}/{\sf H}) = 175ns \end{array}$

Note that the -10ns indicates that data on SEL must be valid within 10ns of the S/ $\overline{H}$  pulse going low in order to meet the setup time requirements. SEL must be valid for the length of time determined by the following equation:

$(t_{MS} + t_{EOC(max)}) - (t_{MS} - t_{EOC(min)}) = 185ns$

Table 1 shows the coding for MUX channel selection.

The output of the MUX is available at the MUX OUT pin. This output allows the user to perform additional signal processing, such as buffering, filtering or gain, before the signal is brought to the ANALOG INPUT pin. If signal processing is not required connect the MUX OUT pin directly to the ANALOG INPUT pin.

Table 1. Internal Multiplexer Programming

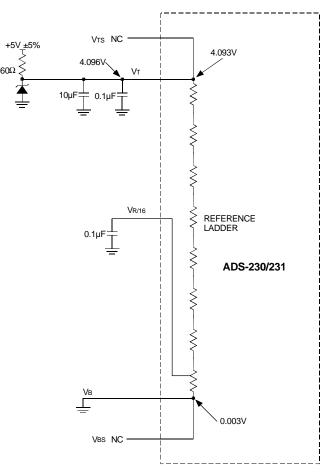

Figure 3. Reference Force Input Only

## ADS-230/ADS-231

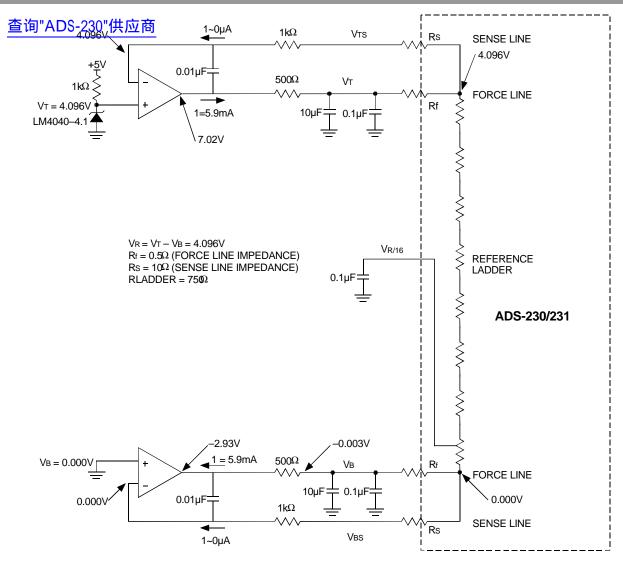

Figure 4. Ladder Reference Force and Sense Inputs

#### **Reference Inputs**

Reference voltages are applied to the fully differential V<sub>T</sub> and V<sub>B</sub> reference input pins. The resistance of the reference ladder network is typically 750 ohms. Additional parasitic resistances are added by the package leads, wire bonds, conductor traces, etc. These parasitic resistances can introduce voltage drops causing gain and offset errors as large as 6 LSB's at the 12-bit level. These IR drops can be compensated for by sensing the reference voltages at the V<sub>Ts</sub> and V<sub>Bs</sub> reference sense pins and forcing the reference voltage an exact value as shown in Figure 4.

Since there is essentially zero current flowing through the sense line there is negligible voltage drop to the inverting input of the op-amp. The voltage at the inverting input of the op-amp, therefore, accurately represents the voltage at the top or bottom of the reference ladder network. The opamp drives the force input and forces the voltages at the ends of the reference ladder network to equal the voltage at the op-amps non-inverting input, plus or minus the opamps input offset voltage. When using this reference configuration with a low offset voltage op-amp, gain and offset errors below 0.5 LSB are readily obtainable.

The 0.1 and 10µF capacitors on the force inputs provide high frequency decoupling of the reference ladder network. The 500 $\Omega$  force resistors isolate the op-amp from the large capacitive load. The 0.01µF and 1k $\Omega$  network ensures stability at high frequencies. The VR/16 output should be bypassed to analog ground with a 0.1µF ceramic capacitor. All bypass capacitors should be located as close to the pins as possible to minimize noise on the reference ladder.

If the ADS-230/-231 is used in a frequency domain application then the circuit shown in Figure 3 maybe used. This circuit will introduce several LSB's of gain and offset error, but the dynamic performance will be unaffected.

The reference inputs are fully differential and define the fullscale range of the input signal. The maximum range can be up to 5 volts, or when required any span within the 0 to 5V limit may be used. When using lower voltage spans the noise performance will degrade. See the Typical Performance Curves.

## т 🍙 润 "ADS-230" 供应商

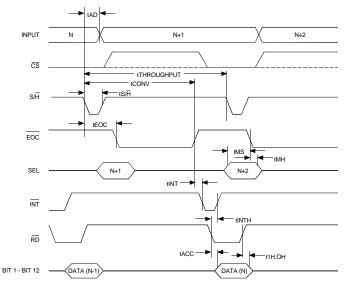

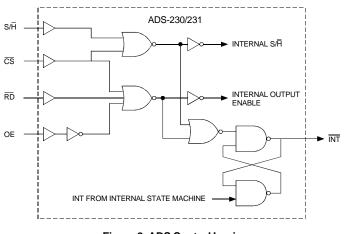

The ADS-230/-231 has two modes of operation as shown in Figure 5, 6, 7 and 8.

In the Interrupt Interface mode, as shown in Figure 5, the falling edge of  $S/\overline{H}$  holds the input voltage and initiates a conversion when  $\overline{CS}$  is held low. At the end of conversion, the  $\overline{EOC}$  output goes high and the  $\overline{INT}$  output goes low,

indicating that the conversion results are latched and may be read by pulling  $\overline{\text{RD}}$  low. The falling edge of  $\overline{\text{RD}}$  resets the  $\overline{\text{INT}}$  line.

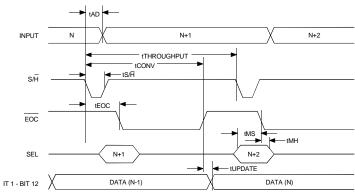

The High Speed Interface mode is shown in Figure 6. In this mode the output data is always present, and the  $\overline{\text{INT}}$  to  $\overline{\text{RD}}$  delay is eliminated.

The control logic decoding section is shown in Figure 8.

Figure 5. Interrupt Interface Timing (MD = 0, OE = 1)

Figure 6. High-speed Interface Timing (MD = 0, OE = 1,  $\overline{CS}$  = 0,  $\overline{RD}$  = 0)

Figure 7. CS Setup & Hold Timing for S/H, RD and OE

## Powe查询ph DS-230"供应商

The ADS-230 and ADS-231 are designed to operate off a single +5V supply. To guarantee proper operation of the converters, only one power supply should be used. If separate analog and digital supplies are used, then the converter must be powered up with the analog supply. The absolute maximum ratings states that all inputs must be between GND –300mV and VS +300mV. When the converter power supply is turned off the maximum input becomes  $\pm$ 300mV, which in turn requires that the devices connected to the converter have power removed before power to the converter is removed.

There are two analog pins AVs and one digital supply pin DVs. This allows for separate bypassing of the analog and digital sections of the circuit. Both AVs pins should be bypassed to ground with  $0.1\mu$ F ceramic capacitors. At least one of the AVs pins should be bypassed with a  $10\mu$ F tantalum capacitor. The DVs input should be bypassed with a  $0.1\mu$ F ceramic capacitor in parallel with a  $10\mu$ F tantalum capacitor. All bypass capacitor should be located as close to the converter as possible.

There are two analog ground pins (AGND), three digital ground pins for the control inputs (DGNDC), and one digital ground pin for the data output lines (DGNDD). Separating the analog section from the digital sections reduces digital

interference in the analog circuitry thereby improving the dynamic performance of the converter. When driving a high capacitance digital data bus buffering the output data lines maybe necessary to minimize the DVs and DGND current spikes generated each conversion to charge the data bus capacitance.

These large current spikes will couple back to the analog circuitry increasing the converter noise level. Separating the digital outputs from the digital inputs reduces the possibility of ground bounce from the data lines causing jitter on the S/H input. The digital ground planes should be tied together at the digital ground pins. The analog ground plane should be tied to the DGNDD ground plane at the ground return strap for the power supply.

#### S/H Input

The clock source driving the S/H input must be free of jitter. For best performance, a crystal oscillator is recommended. For the ADS-230 and ADS-231, a 1.0 and 1.5Mhz square wave will provide a good signal for the respective S/H inputs. In both cases, as long as the duty cycle is near 50%, the S/H pulse widths fall under the maximum allowed. When operating the ADS-230 below 910kHz or the ADS-231 below 1.25MHz, the S/H pulse widths must be less than half the respective sample periods.

## ADS-230/ADS-231

**Typical Performance Curves for ADS-230**

DVs = AVs = 5.0V

(c) 100 105 100 4.75V 95 5.25V 90 85 -55 -35 -15 5 25 45 65 85 105 125

AMBIENT TEMPERATURE (°C)

Typical Performance Curves, ADS-230/-231

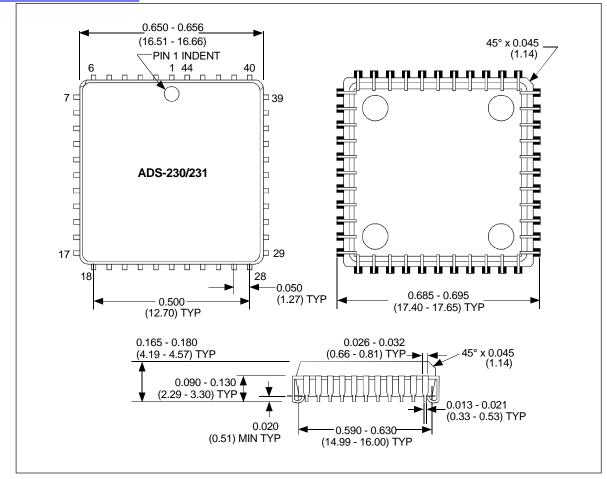

MECHANICAL DIMENSIONS INCHES (mm)

#### **ORDERING INFORMATION**

| Model   | Throughput Rate | <b>Operating Temperature Range</b> |

|---------|-----------------|------------------------------------|

| ADS-230 | 1.0MHz          | -40°C to +85°C                     |

| ADS-231 | 1.5MHz          | -40°C to +85°C                     |

DS-0301 03/97

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 Tel: (508) 339-3000 (800) 233-2765 Fax: (508) 339-6356 Internet: www.datel.com Email: sales@datel.com Data sheet fax back: (508) 261-2857

DATEL (UK) LTD. Tadley, England Tel: (01256)-880444 DATEL S.A.R.L. Montigny Le Bretonneux, France Tel: 01-34-60-01-01 DATEL GmbH Munchen, Germany Tel: 89-544334-0 DATEL KK Tokyo, Japan Tel: 3-3779-1031, Osaka Tel: 6-354-2025

DATEL makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice. The DATEL logo is a registered DATEL, Inc. trademark.