# F100155 Quad Multiplexer/Latch

### **General Description**

The F100155 contains four transparent latches, each of which can accept and store data from two sources. When both Enable  $(\overline{E}_n)$  inputs are LOW, the data that appears at an output is controlled by the Select  $(S_n)$  inputs, as shown in the Operating Mode table. In addition to routing data from either  $D_0$  or  $D_1$ , the Select inputs can force the outputs LOW for the case where the latch is transparent (both Enables are LOW) and can steer a HIGH signal from either  $D_0$  or  $D_1$  to an output. The Select inputs can be tied together for applications requiring only that data be steered from eight

ther  $D_0$  or  $D_1$ . A positive-going signal on either Enable input latches the outputs. A HIGH signal on the Master Reset (MR) input overrides all the other inputs and forces the Q outputs LOW. All inputs have 50 k $\Omega$  pulldown resistors.

Refer to the F100355 datasheet for:

PCC packaging

Lower power

Military versions

Extended voltage specs (-4.2V to -5.7V)

Ordering Code: See Section 8

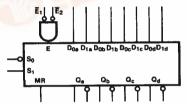

## **Logic Symbol**

TL/F/9860-3

| Pin Names                         | Description                |

|-----------------------------------|----------------------------|

| Ē₁, Ē₂                            | Enable Inputs (Active LOW) |

| $\overline{S}_0, S_1$             | Select Inputs              |

| MR                                | Master Reset               |

| D <sub>na</sub> -D <sub>nd</sub>  | Data Inputs                |

| Qa-Qd                             | Data Outputs               |

| $\overline{Q}_a - \overline{Q}_d$ | Complementary Data Outputs |

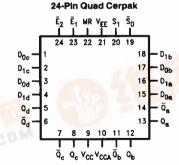

# **Connection Diagrams**

TL/F/9860-1

TL/F/9860-2

3-125

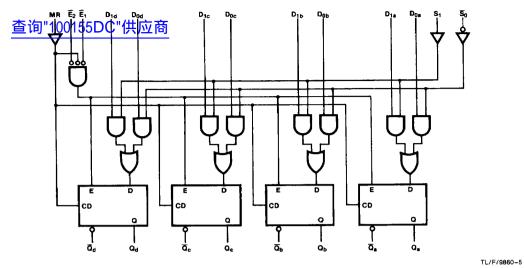

# **Logic Diagram**

#### **Operating Mode Table**

|                | Con | trois          |      | Outputs                                              |

|----------------|-----|----------------|------|------------------------------------------------------|

| Ē <sub>1</sub> | Ē₂  | S <sub>1</sub> | Ī\$₀ | Qn                                                   |

| н              | х   | х              | X    | Latched*                                             |

| X              | н   | X              | x    | Latched*                                             |

| L              | L   | L              | L    | D <sub>0x</sub>                                      |

| L              | L   | H              | L    | D <sub>0x</sub><br>D <sub>0x</sub> + D <sub>1x</sub> |

| L              | L   | L              | н    | L                                                    |

| L              | L   | Н              | н    | D <sub>1x</sub>                                      |

\*Stores data present before E went HIGH

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

# **Truth Table**

|    |                |                | Input | s              |                 |                 | Out  | puts |

|----|----------------|----------------|-------|----------------|-----------------|-----------------|------|------|

| MR | Ē <sub>1</sub> | Ē <sub>2</sub> | Sı    | S <sub>0</sub> | D <sub>1x</sub> | D <sub>0x</sub> | Qx   | Qx   |

| Н  | Х              | Х              | Х     | Х              | Х               | Х               | Н    | L    |

| L  | L              | L              | Н     | Н              | н               | Х               | L    | - н  |

| L  | L              | L              | Н     | Н              | L               | Х               | Н    | ᅵᅵ   |

| L  | L              | L              | L     | L              | ×               | н               | L    | Н    |

| L  | L              | L              | L     | L              | Х               | L               | н    | L    |

| L  | L              | L              | L     | Н              | X               | Х               | H    | L    |

| L  | L              | L              | Н     | L              | Н               | X               | L    | н    |

| L  | L              | L              | н     | L              | ×               | Н               | L    | Н    |

| L  | L              | L              | н     | L              | L               | L               | н    | ٦    |

| L  | Н              | Х              | Х     | Х              | Х               | X               | Late | hed* |

| L  | Х              | H_             | Х     | Х              | Х               | X               | Late | hed* |

### Absolute Maximum Ratings

Above which the useful life may be impaired. (Note 1)

If Military/Aerospace specified devices are required, please compact if National Semiconductor Sales Office/Distributors for availability and specifications.

-65°C to +150°C Storage Temperature

Maximum Junction Temperature (T<sub>J</sub>) + 150°C Case Temperature under Bias (T<sub>C</sub>) 0°C to +85°C VEE Pin Potential to Ground Pin -7.0V to +0.5VInput Voltage (DC)  $V_{FF}$  to +0.5VOutput Current (DC Output HIGH) -50 mA Operating Range (Note 2) -- 5.0V to -- 4.2V

#### DC Electrical Characteristics

$V_{EE} = -4.5V$ ,  $V_{CC} = V_{CCA} = GND$ ,  $T_{C} = 0^{\circ}C$  to  $+85^{\circ}C$  (Note 3)

| Symbol           | Parameter           | Min   | Тур                                   | Max    | Units  | Condition                               | s (Note 4)   |  |

|------------------|---------------------|-------|---------------------------------------|--------|--------|-----------------------------------------|--------------|--|

| $V_{OH}$         | Output HIGH Voltage | -1025 | -955                                  | -880   | m∨     | V <sub>IN</sub> = V <sub>IH</sub> (Max) | Loading with |  |

| V <sub>OL</sub>  | Output LOW Voltage  | -1810 | - 1705                                | - 1620 | ] '''' | or V <sub>IL (Min)</sub>                | 50Ω to -2.0V |  |

| V <sub>OHC</sub> | Output HIGH Voltage | 1035  |                                       |        | mV     | V <sub>IN</sub> = V <sub>IH(Min)</sub>  | Loading with |  |

| Volc             | Output LOW Voltage  |       |                                       | -1610  | ] '''* | or V <sub>IL (Max)</sub>                | 50Ω to -2.0V |  |

| V <sub>IH</sub>  | Input HIGH Voltage  | -1165 | · · · · · · · · · · · · · · · · · · · | - 880  | mV     | Guaranteed HIGH Signal for All Inputs   |              |  |

| V <sub>IL</sub>  | Input LOW Voltage   | -1810 |                                       | 1475   | mV     | Guaranteed LOW<br>for All Inputs        | Signal       |  |

| I <sub>IL</sub>  | Input LOW Current   | 0.50  |                                       |        | μА     | V <sub>IN</sub> = V <sub>IL</sub> (Min) |              |  |

#### **DC Electrical Characteristics**

$V_{EE} = -4.2V$ ,  $V_{CC} = V_{CCA} = GND$ ,  $T_{C} = 0^{\circ}C$  to  $+85^{\circ}C$  (Note 3)

| Symbol           | Parameter           | Min   | Тур | Max    | Units  | Condition                               | s (Note 4)   |

|------------------|---------------------|-------|-----|--------|--------|-----------------------------------------|--------------|

| V <sub>OH</sub>  | Output HIGH Voltage | -1020 |     | -870   | mV     | V <sub>IN</sub> = V <sub>IH (Max)</sub> | Loading with |

| VOL              | Output LOW Voltage  | 1810  |     | - 1605 | ] ",,* | or V <sub>IL (Min)</sub>                | 50Ω to -2.0V |

| V <sub>OHC</sub> | Output HIGH Voltage | -1030 |     |        | mV     | $V_{IN} = V_{IH (Min)}$                 | Loading with |

| Volc             | Output LOW Voltage  |       |     | -1595  | 1111   | or V <sub>IL (Max)</sub>                | 50Ω to -2.0V |

| VIH              | Input HIGH Voltage  | -1150 |     | -870   | mV     | Guaranteed HIGH<br>for All Inputs       | Signal       |

| V <sub>IL</sub>  | Input LOW Voltage   | -1810 |     | -1475  | mV     | Guaranteed LOW for All Inputs           | Signal       |

| Iμ               | Input LOW Current   | 0.50  |     |        | μΑ     | $V_{IN} = V_{IL (Min)}$                 |              |

### **DC Electrical Characteristics**

$V_{EE} = -4.8V$ ,  $V_{CC} = V_{CCA} = GND$ ,  $T_{C} = 0^{\circ}C$  to  $+85^{\circ}C$  (Note 3)

| Symbol           | Parameter           | Min    | Тур | Max   | Units | Condition                               | s (Note 4)   |  |

|------------------|---------------------|--------|-----|-------|-------|-----------------------------------------|--------------|--|

| VoH              | Output HIGH Voltage | - 1035 |     | -880  | mV    | V <sub>IN</sub> = V <sub>IH (Max)</sub> | Loading with |  |

| V <sub>OL</sub>  | Output LOW Voltage  | -1830  |     | 1620  | ""•   | or V <sub>IL (Min)</sub>                | 50Ω to -2.0V |  |

| V <sub>OHC</sub> | Output HIGH Voltage | - 1045 |     |       | mV    | V <sub>IN</sub> = V <sub>IH (Min)</sub> | Loading with |  |

| V <sub>OLC</sub> | Output LOW Voltage  |        |     | -1610 |       | or V <sub>IL (Max)</sub>                | 50Ω to -2.0V |  |

| V <sub>IH</sub>  | Input HIGH Voltage  | -1165  |     | -880  | mV    | Guaranteed HIGH Signal for All Inputs   |              |  |

| V <sub>IL</sub>  | Input LOW Voltage   | -1830  |     | -1490 | mV    | Guaranteed LOW for All Inputs           | Signal       |  |

| IIL              | Input LOW Current   | 0.50   |     |       | μΑ    | VIN = VIL (Min)                         |              |  |

Note 1: Absolute maximum ratings are those values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Parametric values specified at -4.2V to -4.8V.

Note 3: The specified limits represent the "worst case" value for the parameter. Since these "worst case" values normally occur at the temperature extremes, additional noise immunity and guard banding can be achieved by decreasing the allowable system operating ranges.

Note 4: Conditions for testing shown in the tables are chosen to guarantee operation under "worst case" conditions.

# **DC Electrical Characteristics**

$V_{\text{EE}} = -4.2 \text{V}$  to -4.8 V unless otherwise specified,  $V_{\text{CC}} = V_{\text{CCA}} = \text{GND}$ ,  $T_{\text{C}} = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$

| Symbol " | 100155 <b>口和地快</b> 放商                       | Min  | Тур | Max                      | Units | Conditions                             |

|----------|---------------------------------------------|------|-----|--------------------------|-------|----------------------------------------|

| IIH      | input HiGH Current So, S1 E1, E2 Dna-Dnd MR |      |     | 220<br>350<br>340<br>430 | μΑ    | V <sub>IN</sub> = V <sub>IH (Max</sub> |

| lee      | Power Supply Current                        | -133 | 95  | -66                      | mA    | Inputs Open                            |

# Ceramic Dual-In-Line Package AC Electrical Characteristic $V_{\text{EE}}=-4.2 V$ to -4.8 V, $V_{\text{CC}}=V_{\text{CCA}}=\text{GND}$

| O                                    | Parameter                                                                                      | T <sub>C</sub> =     | o.c  | $T_C = +25^{\circ}C$ |      | T <sub>C</sub> = +85°C |      | Units | Conditions        |  |

|--------------------------------------|------------------------------------------------------------------------------------------------|----------------------|------|----------------------|------|------------------------|------|-------|-------------------|--|

| Symbol                               | Parameter                                                                                      | Min                  | Max  | Min                  | Max  | Min                    | Max  | J     | Conditions        |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>D <sub>na</sub> -D <sub>nd</sub> to Output<br>(Transparent Mode)          | 0.50                 | 1.90 | 0.60                 | 1.85 | 0.50                   | 1.90 | ns    |                   |  |

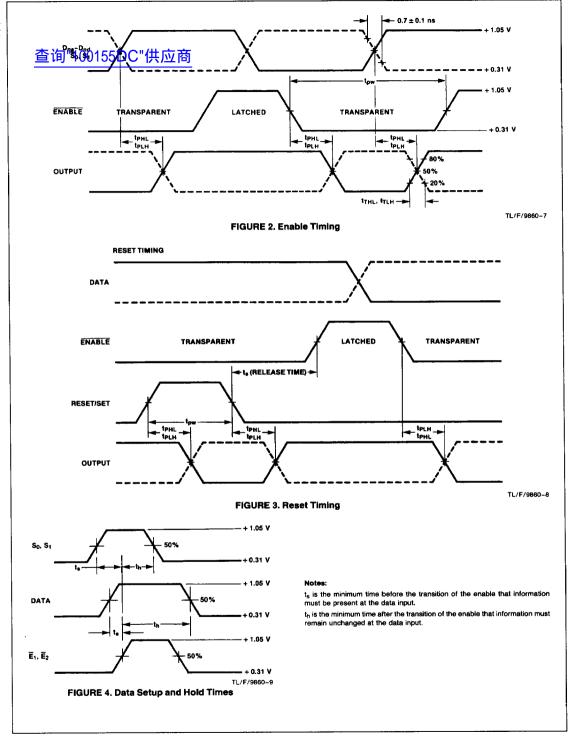

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay \$\overline{S}_0 S_1\$ to Output (Transparent Mode)                          | 1.50                 | 3.50 | 1.50                 | 3.40 | 1.50                   | 3.50 | ns    | Figures 1 and 2   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay  E <sub>1</sub> , E <sub>2</sub> to Output                                   | 0.90                 | 2.50 | 1.00                 | 2.40 | 1.00                   | 2.50 | ns    |                   |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>MR to Output                                                              | 0.90                 | 3.00 | 0.90                 | 2.90 | 0.90                   | 3.00 | ns    | Figures 1 and 3   |  |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition Time<br>20% to 80%, 80% to 20%                                                      | 0.60                 | 2.30 | 0.60                 | 2.20 | 0.45                   | 2.30 | ns    | Figures 1 and 2   |  |

| ts                                   | Setup Time  D <sub>na</sub> -D <sub>nd</sub> S <sub>0</sub> , S <sub>1</sub> MR (Release Time) | 0.90<br>2.40<br>1.50 |      | 0.90<br>2.40<br>1.50 |      | 0.90<br>2.70<br>1.50   |      | ns    | Figure 4 Figure 3 |  |

| t <sub>H</sub>                       | Hold Time  D <sub>na</sub> -D <sub>nd</sub> S <sub>0</sub> , S <sub>1</sub>                    | 0.40<br>-0.70        | -    | 0.40<br>-0.70        |      | 0.40<br>0.70           |      | ns    | Figure 4          |  |

| t <sub>pw</sub> (L)                  | Pulse Width LOW E <sub>1</sub> , E <sub>2</sub>                                                | 2.00                 |      | 2.00                 |      | 2.00                   |      | ns    | Figure 2          |  |

| t <sub>pw</sub> (H)                  | Pulse Width HIGH MR                                                                            | 2.00                 |      | 2.00                 |      | 2.00                   |      | ns    | Figure 3          |  |

# Cerpak AC Electrical Characteristics $V_{\text{EE}} = -4.2 \text{V to } -4.8 \text{V}, V_{\text{CC}} = V_{\text{CCA}} = \text{GND}$

| 0                                    | Parameter                                                                         | T <sub>C</sub> = 0°C |      | T <sub>C</sub> = +25°C |      | $T_C = +85^{\circ}C$ |      | Units | Conditions      |

|--------------------------------------|-----------------------------------------------------------------------------------|----------------------|------|------------------------|------|----------------------|------|-------|-----------------|

| Symbol                               |                                                                                   | Min                  | Max  | Min                    | Max  | Min                  | Max  |       |                 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay D <sub>na</sub> -D <sub>nd</sub> to Output (Transparent Mode)   | 0.50                 | 1.70 | 0.60                   | 1.65 | 0.50                 | 1.70 | ns    | (               |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay \$\overline{S}_1\$, \$S_1\$ to Output (Transparent Mode)        | 1.50                 | 3.30 | 1.50                   | 3.20 | 1.50                 | 3.30 | ns    | Figures 1 and 2 |

| t <sub>PLH</sub>                     | Propagation Delay $\overline{\mathbb{E}}_1$ , $\overline{\mathbb{E}}_2$ to Output | 0.90                 | 2.30 | 1.00                   | 2.20 | 1.00                 | 2.30 | ns    |                 |

TL/F/9860-6

# Cerpak AC Electrical Characteristics $V_{EE} = -4.2 V$ to -4.8 V, $V_{CC} = V_{CCA} = GND$ (Continued)

| Symbol                               | 查询 <b>"</b> 400495DC"                                                       | ## # <del>**</del>   | ос   | T <sub>C</sub> = +25°C |      | T <sub>C</sub> = +85°C |      | Units    | Conditions        |  |

|--------------------------------------|-----------------------------------------------------------------------------|----------------------|------|------------------------|------|------------------------|------|----------|-------------------|--|

| Cymbol                               | 旦时 100193000                                                                | 六四回                  | Max  | Min                    | Max  | Min                    | Max  | - Cilita |                   |  |

| t <sub>PLH</sub>                     | Propagation Delay<br>MR to Output                                           | 0.90                 | 2.80 | 0.90                   | 2.70 | 0.90                   | 2.80 | ns       | Figures 1 and 3   |  |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition Time<br>20% to 80%, 80% to 20%                                   | 0.60                 | 2.20 | 0.60                   | 2.10 | 0.45                   | 2.20 | ns       | Figures 1 and 2   |  |

| ts                                   | Setup Time  D <sub>na</sub> -D <sub>nd</sub> S 0, S 1  MR (Release Time)    | 0.80<br>2.30<br>1.40 |      | 0.80<br>2.30<br>1.40   |      | 0.80<br>2.60<br>1.40   |      | ns       | Figure 4 Figure 3 |  |

| tH                                   | Hold Time  D <sub>na</sub> -D <sub>nd</sub> S <sub>0</sub> , S <sub>1</sub> | 0.30<br>0.80         |      | 0.30<br>0.80           |      | 0.30<br>0.80           |      | ns       | Figure 4          |  |

| t <sub>pw</sub> (L)                  | Pulse Width LOW E1, E2                                                      | 2.00                 |      | 2.00                   |      | 2.00                   |      | ns       | Figure 2          |  |

| t <sub>pw</sub> (H)                  | Pulse Width HIGH MR                                                         | 2.00                 |      | 2.00                   |      | 2.00                   |      | ns       | Figure 3          |  |

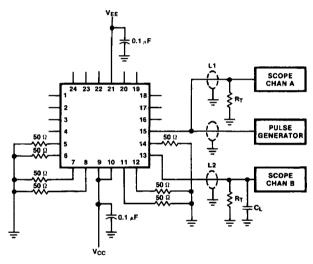

FIGURE 1. AC Test Circuit

#### Notes:

$V_{CC}$ ,  $V_{CCA} = +2V$ ,  $V_{EE} = -2.5V$ L1 and L2 = equal length  $50\Omega$  impedance lines  $R_T = 50\Omega$  terminator internal to scope Decoupling 0.1 μF from GND to V<sub>CC</sub> and V<sub>EE</sub> All unused outputs are loaded with 500 to GND C<sub>L</sub> = Fixture and stray capacitance ≤ 3 pF

Pin numbers shown are for flatpak; for DIP see logic symbol