# DRIVER/AMPLIFIER CIRCUIT C4069

### For Serial/Current Output Type MOS Linear Image Sensors

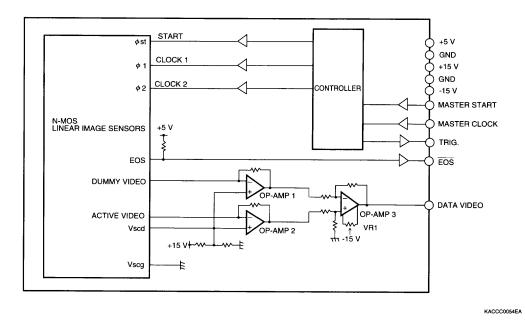

The C4069 is a high-speed driver/amplifier circuit designed specifically for use with Hamamatsu serial/current output type MOS linear image sensors (S3901, S3904, S3902, S3903). The C4069 driver/amplifier circuit includes a generator for a start pulse and two-phase clock pulses used to drive a MOS linear image sensor and a signal processing circuit used to read out the video signal in the current-voltage conversion mode. The signal inputs required are only a master start pulse, a master clock pulse,  $\pm 5V$  and  $\pm 15V$ .

In addition, the C4091 pulse generator is available, which supplies the C4069 with a master start pulse and a master clock pulse.

#### **FEATURES**

- Structure allows easy cooling and optical alignment of MOS image sensor

- Simple operation: only a master start pulse, a master clock pulse, +5V and ±15V required

- High-speed operation (2MHz Max.)

- No adjustment

#### **DESCRIPTIONS OF TERMINALS**

|        | Terminals        | Symbols                                              | Descriptions                                                                                                                                                                                                                                                     |

|--------|------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input  | Supply Voltage   | V <sub>d</sub> (+5)<br>V <sub>a</sub> (+15)<br>(-15) | +5 Vdc, 70 mA<br>+15 Vdc, 30 mA<br>-15 Vdc, 30 mA                                                                                                                                                                                                                |

|        | Master Start φms | St.                                                  | CMOS logic compatible. Positive logic. For initializing the circuit and the MOS shift register.                                                                                                                                                                  |

|        | Master Clock     | CLK                                                  | CMOS logic compatible. The maximum frequency is 12 MHz. For synchronizing the circuit and the MOS shift register.                                                                                                                                                |

| Output | Data Video       | Video                                                | Positive output. This is the voltage output produced after the current-voltage conversion of the MOS video signal and the differential amplification with respect to the dummy video line. It is obtained synchronized with the positive transition of $\phi$ 2. |

|        | Sample-and-hold  | Trig.                                                | CMOS logic compatible. Positive logic. This output can be used as the trigger signal for the sample-and-hold or A/D conversion.                                                                                                                                  |

|        | End of Scan      | EOS                                                  | CMOS logic compatible. Negative logic. This is the end-of-scan signal of the MOS shift register and it is obtained synchronized with $\phi 2$ right after the last element is scanned.                                                                           |

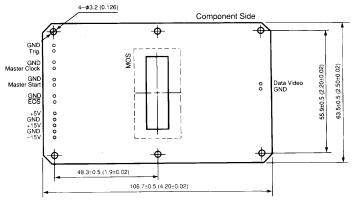

Figure 1: Dimensional Outline and Terminals

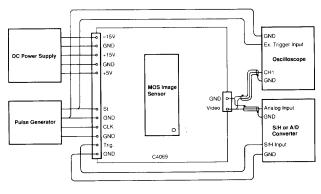

Figure 2: Wiring Example

Dimensions in mm (inches)

## 查询"C4069"供应商 Diagram

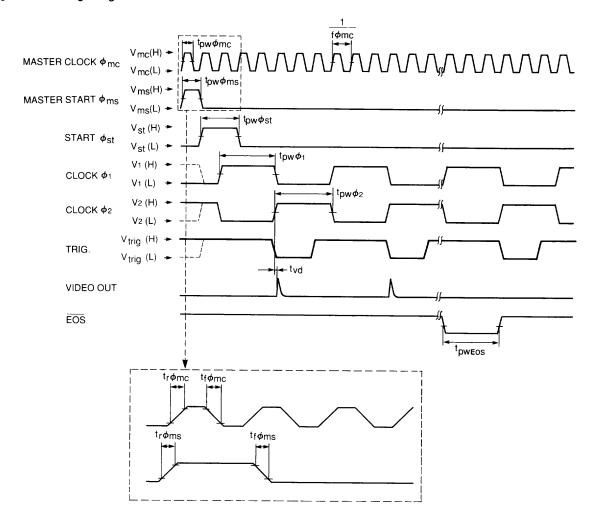

Figure 4: Timing Diagram