# **Product Description**

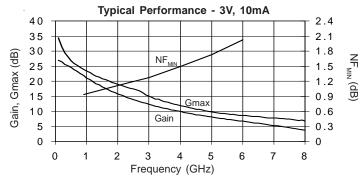

Sirenza Microdevices' SGA-8343 is a high performance Silicon Germanium Heterostructure Bipolar Transistor (SiGe HBT) designed for operation from DC to 6 GHz. The SGA-8343 is optimized for 3V operation but can be biased at 2V for low-voltage battery operated systems. The device provides high gain, low NF, and excellent linearity at a low cost. It can be operated at very low bias currents in applications where high linearity is not required.

The matte tin finish on Sirenza's lead-free package utilizes a post annealing process to mitigate tin whisker formation and is RoHS compliant per EU Directive 2002/95. This package is also manufactured with green molding compounds that contain no antimony trioxide nor halogenated fire retardants.

SGA-8343 SGA-8343Z

Low Noise, High Gain SiGe HBT

## **Product Features**

- Now Available in Lead Free, RoHS Compliant, & Green Packaging

- DC-6 GHz Operation

- 0.9 dB NF<sub>MIN</sub> @ 0.9 GHz

- 24 dB Gmax @ 0.9 GHz

- |G<sub>OPT</sub>|=0.10 @ 0.9 GHz

- OIP3 = +28 dBm, P1dB = +9 dBm

- Low Cost, High Performance, Versatility

# **Applications**

- · Analog and Digital Wireless Systems

- 3G, Cellular, PCS, RFID

- Fixed Wireless, Pager Systems

- Driver Stage for Low Power Applications

- Oscillators

| Symbol            | Device Characteristics                            | Test Conditions V <sub>cE</sub> =3V, I <sub>co</sub> =10mA, 25°C (unless otherwise noted) | Test Frequency                | Units | Min. | Тур.                 | Max. |

|-------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------|-------|------|----------------------|------|

| $G_{MAX}$         | Maximum Available Gain                            | $Z_S = Z_S^*, Z_L = Z_L^*$                                                                | 0.9 GHz<br>1.9 GHz<br>2.4 GHz | dB    |      | 23.9<br>19.3<br>17.7 |      |

| NF                | Minimum Noise Figure                              | Z <sub>s</sub> =Gamma <sub>OPT</sub> , Z <sub>l</sub> =Z <sub>l</sub> *                   | 0.9 GHz<br>1.9 GHz<br>2.4 GHz | dB    |      | 0.94<br>1.10<br>1.18 |      |

| S <sub>21</sub>   | Insertion Gain <sup>[1]</sup>                     | $Z_s = Z_L = 50 \text{ Ohms}$                                                             | 0.9 GHz                       | dB    | 21.0 | 22.0                 | 23.0 |

| NF                | Noise Figure <sup>[2]</sup>                       | LNA Application<br>Circuit Board                                                          | 1.9 GHz                       | dB    |      | 1.40                 | 1.75 |

| Gain              | Gain <sup>[2]</sup>                               | LNA Application<br>Circuit Board                                                          | 1.9 GHz                       | dB    | 15.5 | 16.5                 | 17.5 |

| OIP <sub>3</sub>  | Output Third Order Intercept Point <sup>[2]</sup> | LNA Application<br>Circuit Board                                                          | 1.9 GHz                       | dBm   | 25.8 | 27.8                 |      |

| P <sub>1dB</sub>  | Output 1dB Compression Point <sup>[2]</sup>       | LNA Application<br>Circuit Board                                                          | 1.9 GHz                       | dBm   | 7.5  | 9.0                  |      |

| h <sub>FE</sub>   | DC Current Gain                                   |                                                                                           |                               |       | 120  | 180                  | 300  |

| BV <sub>CEO</sub> | Collector-Emitter Breakdown Voltage               |                                                                                           |                               | V     | 5.7  | 6.0                  |      |

| Rth               | Thermal Resistance                                | junction-to-lead                                                                          |                               | °C/W  |      | 200                  |      |

| V <sub>CE</sub>   | Operating Voltage                                 | collector-emitter                                                                         |                               | V     |      |                      | 4.0  |

| I <sub>CE</sub>   | Operating Current                                 | collector-emitter                                                                         |                               | mA    |      |                      | 50   |

|                   |                                                   |                                                                                           |                               |       |      |                      |      |

<sup>[1] 100%</sup> tested - Insertion gain tested using a 50 ohm contact board (no matching circuitry) during final production test.

The information provided herein is believed to be reliable at press time. Sirenza Microdevices assumes no responsibility for inaccuracies or omissions. Sirenza Microdevices assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. Sirenza Microdevices does not authorize or warrant any Sirenza Microdevices does not authorize or warrant any Sirenza Microdevices and/or systems.

Copyright 2003 Sirenza Microdevices, Inc. All worldwide rights reserved.

<sup>[2]</sup> Sample tested - Samples pulled from each wafer/package lot. Sample test specifications are based on statistical data from sample test measurements. The test fixture is an engineering application circuit board (parts are pressed down on the circuit board). The application circuit represents a trade-off between the optimal noise match and input return loss.

## **Junction Temperature Calculation**

MTTF is inversely proportional to the device junction temperature. For junction temperature and MTTF considerations the device operating conditions should also satisfy the following expression:

$$P_{DC} < (T_J - T_L) / R_{TH}$$

where:

$P_{DC} = I_{CE} * V_{CE} (W)$   $T_{J} = Junction Temperature (C)$  $T_L^J$  = Lead Temperature (pin 2) (C)  $R_{TH}$  = Thermal Resistance (C/W)

## **Biasing Details**

The SGA-8343 should be biased through a dropping resistor or with active bias circuitry to prevent thermal runaway and combat Beta variation. For passive biasing it is recommended that the voltage drop be at least 20% of  $V_{\rm CE}$ . A voltage divider from collector-to-base is preferred over a simple series resistor. The effect of Beta variation can be minimized by bleeding  $\sim 10^*I_R$  through the shunt resistor.

## **Absolute Maximum Ratings**

|                   | _                                                                                                                  |                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Symbol            | Value                                                                                                              | Unit                                                                |

| I <sub>CE</sub>   | 72                                                                                                                 | mA                                                                  |

| l <sub>B</sub>    | 1                                                                                                                  | mA                                                                  |

| V <sub>CE</sub>   | 5                                                                                                                  | V                                                                   |

| V <sub>CB</sub>   | 12                                                                                                                 | V                                                                   |

| V <sub>EB</sub>   | 4.5                                                                                                                | V                                                                   |

| $P_{\mathbb{N}}$  | 5                                                                                                                  | dBm                                                                 |

| T <sub>stor</sub> | -40 to +150                                                                                                        | С                                                                   |

| P <sub>DISS</sub> | 350                                                                                                                | mW                                                                  |

| T <sub>J</sub>    | +150                                                                                                               | С                                                                   |

|                   | I <sub>CE</sub> I <sub>B</sub> V <sub>CE</sub> V <sub>CB</sub> V <sub>CB</sub> T <sub>stor</sub> P <sub>DISS</sub> | CE   72   T2   T2   T2   T3   T4   T4   T5   T5   T5   T5   T5   T5 |

Operation of this device beyond any one of these limits may cause permanent damage. For reliable continuous operation, the device voltage and current must not exceed the maximum operating values specified in the table on page 1.

# Typical Performance - Engineering Application Circuits (See App Note AN-044)

| Freq<br>(GHz) | Vs<br>(V) | V <sub>CE</sub> (V) | I <sub>cq</sub><br>(mA) | NF<br>(dB) | Gain<br>(dB) |     | OIP3 <sup>[3]</sup> (dBm) | S11<br>(dB) | S22<br>(dB) | Comments        |

|---------------|-----------|---------------------|-------------------------|------------|--------------|-----|---------------------------|-------------|-------------|-----------------|

| 0.90          | 5.0       | 3.0                 | 12                      | 1.25       | 18.2         | 9   | 27.3                      | -16         | -18         | series feedback |

| 1.575         | 3.3       | 2.7                 | 10                      | 1.25       | 15.7         | 6.8 | 26.5                      | -10         | -25         | see AN-061      |

| 1.90          | 5.0       | 3.0                 | 12                      | 1.4        | 16.5         | 9   | 27.8                      | -9          | -24         |                 |

| 2.40          | 3.3       | 2.7                 | 10                      | 1.6        | 14.4         | 9   | 27.5                      | -13         | -24         |                 |

<sup>[3]</sup> P<sub>OUT</sub>= 0 dBm per tone, 1MHz tone spacing

Refer to the application note for additional RF data, PCB layouts, BOMs, biasing instructions, and other key issues to be considered. For the latest application note please visit our site at www.sirenza.com.

# Peak RF Performance Under Optimum Matching Conditions

| Freq<br>(GHz) | V <sub>CE</sub><br>(V) | l <sub>cq</sub><br>(mA) | NF <sub>MIN</sub> <sup>[4]</sup><br>(dB) | Gmax<br>(dB) | P1dB <sup>[5]</sup><br>(dBm) | OIP3 <sup>[6]</sup><br>(dBm) |                     |

|---------------|------------------------|-------------------------|------------------------------------------|--------------|------------------------------|------------------------------|---------------------|

| 0.00          | 2                      | 10                      | 0.90                                     | 23.7         | 10                           | 25                           | · c                 |

| 0.90          | 3                      | 10                      | 0.94                                     | 23.9         | 13                           | 29                           |                     |

| 1.00          | 2                      | 10                      | 1.05                                     | 19.1         | 10                           | 25                           | B ←                 |

| 1.90          | 3                      | 10                      | 1.10                                     | 19.3         | 13                           | 29                           | Z <sub>LOPT</sub>   |

| 2.40          | 2                      | 10                      | 1.15                                     | 17.4         | 10                           | 25                           |                     |

| 2.40          | 3                      | 10                      | 1.18                                     | 17.7         | 13                           | 29                           | Z <sub>SOPT</sub> E |

Note: Optimum NF, P1dB, and OIP3 performance cannot be achieved simultaneously.

$<sup>\</sup>begin{array}{l} ^{[4]} \ Z_{S} = \Gamma_{\text{OPT}}, \ Z_{L} = Z_{L}^{*}, \ \text{The input matching circuit losses have been de-emebedded.} \\ ^{[5]} \ Z_{S} = Z_{\text{SOPT}}, \ Z_{L} = Z_{\text{LOPT}}, \ \text{where } Z_{\text{SOPT}} \ \text{and } Z_{\text{LOPT}} \ \text{have been tuned for max P1dB (current allowed to drive-up with constant V}_{\text{CE}}) \\ ^{[6]} \ Z_{S} = Z_{\text{SOPT}}, \ Z_{L} = Z_{\text{LOPT}}, \ \text{where } Z_{\text{SOPT}} \ \text{and } Z_{\text{LOPT}} \ \text{have been tuned for max OIP3} \\ \end{array}$

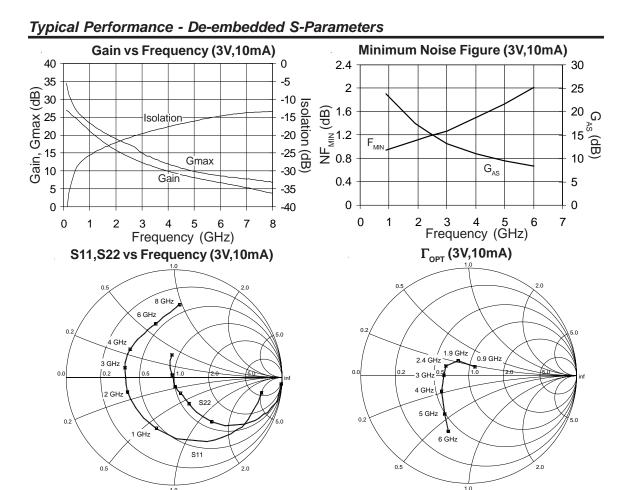

Note: S-parameters are de-embedded to the device leads with  $Z_s = Z_L = 50\Omega$ . The device was mounted on a 0.010" PCB with plated-thru holes close to pins 2 and 4. De-embedded s-parameters can be downloaded from our website (www.sirenza.com).

# Typical Performance - Noise Parameters - 3V,10mA

| Frequency<br>(GHz) | NF <sub>MIN</sub> <sup>[7]</sup><br>(dB) | Γ <sub>οΡΤ</sub><br>Mag ∠ Ang | r <sub>n</sub> (Ω) | Gmax<br>(dB) |

|--------------------|------------------------------------------|-------------------------------|--------------------|--------------|

| 0.9                | 0.94                                     | 0.10 ∠ 55                     | 0.11               | 23.88        |

| 1.9                | 1.1                                      | 0.17 ∠ 125                    | 0.10               | 19.33        |

| 2.4                | 1.18                                     | 0.23 ∠ 157                    | 0.09               | 17.66        |

| 3                  | 1.27                                     | 0.23 ∠ 179                    | 0.09               | 15.01        |

| 4                  | 1.5                                      | 0.29 ∠ -150                   | 0.12               | 11.94        |

| 5                  | 1.73                                     | 0.42 ∠ -122                   | 0.18               | 9.84         |

| 6                  | 2.02                                     | 0.55 ∠ -110                   | 0.24               | 8.62         |

$<sup>^{[7]}</sup>$   $Z_s = \Gamma_{OPT}$ ,  $Z_s = Z_t^*$ ,  $NF_{MIN}$  is a noise parameter for which the input matching circuit losses have been de-emebedded. The noise parameters were measured using a Maury Microwave Automated Tuner System. The device was mounted on a 0.010" PCB with plated-thru holes close to pins 2 and 4.

### Caution: ESD sensitive

Appropriate precautions in handling, packaging and testing devices must be observed.

# **Pin Description**

| Pin # | Function  | Description                                                                |  |

|-------|-----------|----------------------------------------------------------------------------|--|

| 1     | Base      | RF Input / Base Bias                                                       |  |

| 2     | Emitter   | Connection to ground. Use multiple via holes to reduce emitter inductance. |  |

| 3     | Collector | RF Output / Collector Bias                                                 |  |

| 4     | Emitter   | Same as Pin 2                                                              |  |

# **MARKING**

# **Part Number Ordering Information**

| Part Number | Reel Size | Devices/Reel |

|-------------|-----------|--------------|

| SGA-8343    | 7"        | 3000         |

| SGA-8343Z   | 7"        | 3000         |

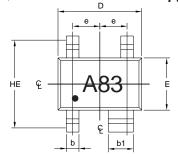

# Part Symbolization

The part will be symbolized with the "A83" or "A83Z" designator and a dot signifying pin 1 on the top surface of the package.

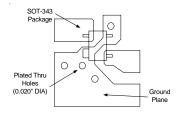

# **Recommended PCB Layout**

Use multiple plated-through vias holes located close to the package pins to ensure a good RF ground connection to a continuous groundplane on the backside of the board.

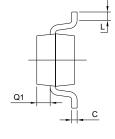

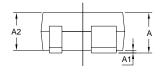

# **Package Dimensions**

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONS ARE INCLUSIVE OF PLATING.

3. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH

6. METAL BURR.

4. ALL SPECIFICATIONS COMPLY TO EIAJ SC70.

5. DIE IS FACING UP FOR MOLD AND FACING DOWN

- FOR TRIM/FORM. ie :REVERSE TRIM/FORM.

6. PACKAGE SURFACE TO BE MIRROR FINISH.

| SYMBOL | MIN  | MAX  |

|--------|------|------|

| E      | 1.15 | 1.35 |

| D      | 1.85 | 2.25 |

| HE     | 1.80 | 2.40 |

| Α      | 0.80 | 1.10 |

| A2     | 0.80 | 1.00 |

| A1     | 0.00 | 0.10 |

| Q1     | 0.10 | 0.40 |

| е      | 0.65 | BSC  |

| b      | 0.25 | 0.40 |

| b1     | 0.55 | 0.70 |

| С      | 0.10 | 0.18 |

| L      | 0.10 | 0.30 |

|        |      |      |

Phone: (800) SMI-MMIC