| LTR                                                                                      |                                                             |                      |                             |                             |                                                                                                                                                                                                                  |                                                      |              |          | REVIS   | IONS         |              |                    |                         |                    |                     |                  |                              |           |            |   |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|-----------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|----------|---------|--------------|--------------|--------------------|-------------------------|--------------------|---------------------|------------------|------------------------------|-----------|------------|---|

|                                                                                          |                                                             |                      | ,                           |                             | [                                                                                                                                                                                                                | DESCF                                                | RIPTIC       | N        |         |              |              |                    | D/                      | ATE (Y             | /R-MO-              | DA)              |                              | APP       | ROVE       | ) |

| A <u>查</u> 论                                                                             | t <sub>BI</sub>                                             | oc, a<br>Al<br>Isiti | nd to<br>so d<br>vity       | APS·<br>lelet<br>par        | 斯典爾arameters t <sub>BAA</sub> , t <sub>BDA</sub> ,<br>ps. Deleted parameters t <sub>CDR</sub> and<br>leted electrostatic discharged<br>paragraph from drawing. Editorial<br>ughout.                              |                                                      |              |          |         |              | 1989 NOV 08  |                    |                         |                    | М.7                 | A. Fr            | ye                           |           |            |   |

| В                                                                                        | Add                                                         | l foo                | tnot                        | type<br>e 3<br>hang         | to t                                                                                                                                                                                                             | able                                                 | Ι,           | para     |         |              |              |                    | 1                       | 991                | JULY                | 23               | М. А                         | M.A. Frye |            |   |

| C                                                                                        | 617<br>thr<br>Rea                                           | 72 a<br>ough<br>d wi | s so<br>16 <u>.</u><br>th B | ource<br><u>A</u> d<br>SUSY | 07 through 16. Add vendor CAGE 1993 SEPT 10 arce of supply to devices 07  Add t <sub>WC</sub> , t <sub>WP</sub> , t <sub>DW</sub> , t <sub>DH</sub> , t <sub>APS</sub> to JSY cycle waveform. Editorial bughout. |                                                      |              |          |         |              | M.A          | M.A. Frye          |                         |                    |                     |                  |                              |           |            |   |

| D                                                                                        |                                                             |                      |                             | tlin<br>hang                |                                                                                                                                                                                                                  | _                                                    |              |          | lerp    | Late.        |              |                    | 9                       | 6-12               | -09                 |                  | Ray Monnin                   |           |            |   |

|                                                                                          |                                                             |                      |                             |                             |                                                                                                                                                                                                                  |                                                      |              |          |         |              |              |                    |                         |                    |                     |                  |                              |           |            |   |

| REV                                                                                      |                                                             |                      |                             |                             |                                                                                                                                                                                                                  |                                                      |              |          |         |              |              |                    |                         |                    |                     |                  |                              |           |            |   |

| REV<br>SHEET                                                                             |                                                             |                      |                             |                             |                                                                                                                                                                                                                  |                                                      |              |          |         |              |              |                    |                         |                    |                     |                  |                              |           |            |   |

| SHEET                                                                                    | D                                                           | D 10                 | D                           | D 10                        | D 10                                                                                                                                                                                                             | D                                                    | D            | D        | D       | D            | D            |                    |                         |                    |                     |                  |                              |           |            |   |

| SHEET<br>REV<br>SHEET                                                                    | 15                                                          | D<br>16              | D 17                        | 18                          | 19                                                                                                                                                                                                               | D 20                                                 | 21           | 22       | 23      | 24           | 25           | D                  | D                       | D                  | D                   | D                | D                            | D         | D          |   |

|                                                                                          | 15<br>S                                                     |                      |                             | 18<br>RE <sup>\</sup>       | 19                                                                                                                                                                                                               |                                                      | <u> </u>     | <u> </u> |         |              |              | D 6                | D 7                     | D 8                | D 9                 | D 10             | D 11                         | D 12      | D 13       |   |

| SHEET REV SHEET REV STATU                                                                | 15<br>S                                                     |                      |                             | 18<br>RE\<br>SHI            | 19<br>V                                                                                                                                                                                                          | 20<br>BY                                             | 21<br>D      | 22<br>D  | 23<br>D | 24<br>D      | 25<br>D<br>5 |                    | 7                       | 8<br>JPPL          | 9<br>Y CEN          | 10               | 11<br>COLU                   | 12        | 13         | _ |

| SHEET REV SHEET REV STATU OF SHEETS PMIC N/A STA MICRO                                   | 15<br>NDA<br>OCIR                                           | 16 RD CUI            | 17                          | 18 RE' SHI PRE Jan          | 19<br>V<br>EET                                                                                                                                                                                                   | 20<br>D BY<br>Jamiso                                 | 21<br>D      | 22<br>D  | 23<br>D | 24<br>D      | 25<br>D<br>5 | 6                  | 7                       | 8<br>JPPL          | 9<br>Y CEN          | 10               | 11<br>COLU                   | 12        | 13         | _ |

| SHEET REV SHEET REV STATU OF SHEETS PMIC N/A STA MICRO DRA                               | NDA<br>OCIR                                                 | RD<br>CUI'           | 17<br>T                     | 18 RE' SHI PRE Jan CHE Cha  | 19 V EET PAREI                                                                                                                                                                                                   | 20<br>D BY<br>Jamiso<br>BY<br>eusing                 | 21<br>D      | 22<br>D  | 23<br>D | 24<br>D<br>4 | 25<br>D<br>5 | 6                  | 7 ISE SI COL            | 8<br>UPPL'<br>UMB  | 9<br>Y CEN<br>US, O | 10 ITER (        | 11<br>COLU<br>3216           | 12 MBUS   | 13         | 1 |

| SHEET REV SHEET REV STATU OF SHEETS PMIC N/A STAI MICRO DRA THIS DRAWI FOR L             | NDA<br>OCIR<br>WIN<br>NG IS A<br>ISE BY<br>RTMEN<br>NCIES ( | RD<br>CUI'<br>IG     | 17  T  BLE                  | 18 REY SHI PRE Jan CHE Cha  | 19 V EET PARECINES E CKED arles Rovei                                                                                                                                                                            | 20<br>D BY<br>Jamiso<br>BY<br>eusing<br>D BY<br>Frye | 21<br>D      | 22<br>D  | 23<br>D | 24<br>D<br>4 | D 5          | 6  RCUI  RT S  CAG | 7 ISE SI COL TS, M RAM, | 8 UPPLUMB IEMO MON | 9<br>Y CEN<br>US, O | 10  ITER ( HIO 4 | 11<br>COLUI<br>3216<br>AL, C | MBUS      | 13<br>2K X | 1 |

| SHEET REV SHEET REV STATU OF SHEETS PMIC N/A STA MICRO DRA THIS DRAWI FOR L DEPA AND AGE | NDA<br>OCIR<br>AWIN<br>NG IS A<br>ISE BY<br>INT OF I        | RD<br>CUI'<br>IG     | 17  T  BLE                  | 18 RE'SHI PRE Jan CHE Cha   | 19 V EET PAREI nes E CKED arles Ro                                                                                                                                                                               | D BY Jamiso BY eusing D BY Frye APPRO 88-1           | 21<br>D<br>1 | 22<br>D  | 23<br>D | 24<br>D<br>4 | 25<br>D<br>5 | 6  RCUI  RT S  CAG | 7<br>COL<br>TS, M       | 8 UPPLUMB IEMO MON | 9<br>Y CEN<br>US, O | 10  ITER ( HIO 4 | 11<br>COLU<br>3216           | MBUS      | 13<br>2K X | 1 |

DESC FORM 193

JUL 94

<u>DISTRIBUTION STATEMENT A.</u> Approved for public release; distribution is unlimited.

5962-E030-97

9004708 0025775 136

#### 1. SCOPE

- 1.1 Scope of his drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRE-38535, appendix A.

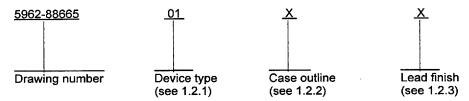

- 1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number 1/ | Circuit function                     | Access time |

|-------------|-------------------|--------------------------------------|-------------|

| 01,07       |                   | 2K X 16 dual port CMOS SRAM (master) | 90 ns       |

| 02,08       |                   | 2K X 16 dual port CMOS SRAM (slave)  | 90 ns       |

| 03,09       |                   | 2K X 16 dual port CMOS SRAM (master) | 70 ns       |

| 04,10       |                   | 2K X 16 dual port CMOS SRAM (slave)  | 70 ns       |

| 05,11       |                   | 2K X 16 dual port CMOS SRAM (master) | 55 ns       |

| 06,12       |                   | 2K X 16 dual port CMOS SRAM (slave)  | 55 ns       |

| 13          |                   | 2K X 16 dual port CMOS SRAM (master) | 45 ns       |

| 14          |                   | 2K X 16 dual port CMOS SRAM (slave)  | 45 ns       |

| 15          |                   | 2K X 16 dual port CMOS SRAM (master) | 35 ns       |

| 16          |                   | 2K X 16 dual port CMOS SRAM (slave)  | 35 ns       |

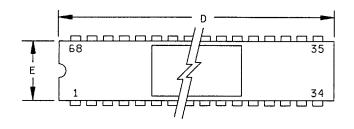

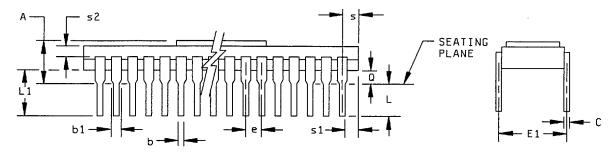

1.2.2 Case outline(s). The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                |

|----------------|------------------------|------------------|------------------------------|

| X              | See figure 1           | 68               | dual-in-line                 |

| Υ              | CQCC1-N68              | 68               | square leadless chip carrier |

| Z              | CMGA3-PN               | 68               | pin grid array 2/            |

| U              | See figure 1           | 68               | flat pack                    |

- 1.2.3 Lead finish. The lead finish is as specified in MIL-PRF-38535, appendix A.

- 1.3 Absolute maximum ratings.

| Supply voltage range                                                                                               | -0.5 V dc to +7.0 V dc<br>-0.5 V dc to +6.0 V dc<br>50 mA<br>-65°C to +150°C |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Storage temperature range                                                                                          | 2.0 W<br>+260° C                                                             |

| Thermal resistance, junction-to-case $(\Theta_{JC})$ : Case X  Cases Y and Z  Case U  Junction temperature $(T_J)$ | 37°C/W<br>See MIL-STD-1835<br>6°C/W<br>+150°C <u>3</u> /                     |

- 1/ Generic numbers are listed on the Standard Microcircuit Source Approval Bulletin at the end of this document and will also be listed in MIL-HDBK-103.

- 2/ The actual number of pins is 121, but the number of pins being used is 68. (See figure 2, case outline Z).

- 3/ Maximum junction temperature may be increased to +175°C during burn-in and steady-state life.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-88665 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>D | SHEET 2    |

DESC FORM 193A JUL 94

**9**004708 0025776 072 빼

1.4 Recommended operating conditions.

| ShipBly(/plage(50ge)(X)(b)(於 応 商<br>High level input voltage range (V <sub>III</sub> )<br>Low level input voltage range (V <sub>II</sub> ) | 4.5 V dc to 5.5 V dc      |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| High level input voltage range (V <sub>III</sub> )                                                                                         | 2.2 V dc to 6.0 V dc      |

| Low level input voltage range (V <sub>II</sub> )                                                                                           | -0.5 V dc to +0.8 V dc 4/ |

| Case operating temperature range (T <sub>C</sub> )                                                                                         | -55°C to +125°C           |

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation.

**SPECIFICATION**

**MILITARY**

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

**STANDARDS**

**MILITARY**

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines.

**HANDBOOKS**

**MILITARY**

MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's).

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

$4/V_{\parallel}$  (min) = -3.0 V dc for pulse width less than 20 ns.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88665 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | D              | 3          |

DESC FORM 193A JUL 94

9004708 0025777 TO9 📟

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.2 Fruth tables 6 The truth tables shall be as specified on figure 3.

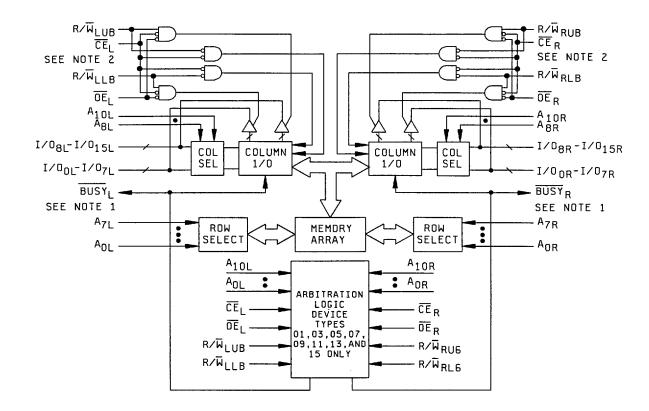

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 4.

- 3.2.4 Case outline(s). The case outline(s) shall be in accordance with 1.2.2 herein and figure 1.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103 (see 6.6 herein). For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device.

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DSCC-VA shall be required in accordance with MIL-PRF-38535, appendix A.

- 3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition C or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88665 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | D              | 4          |

9004708 0025778 945

| 查询"5962-886650 <sup>-</sup>                   | 1XX"(#<br>Symbol    | Cone                                                                            | ditions                                                                                    | Group A   | Device                              | Li          | mits | Unit     |

|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------|-------------------------------------|-------------|------|----------|

|                                               |                     | -55°C ≤ T<br>V <sub>CC</sub> = 4.<br>unless other                               | C ≤ +125°C<br>5 V to 5.5 V<br>rwise specified                                              | subgroups | types                               | Min         | Max  |          |

| Output high voltage                           | V <sub>ОН</sub>     | V <sub>CC</sub> = 4.5 V, I<br>V <sub>IL</sub> = 0.8 V, V <sub>I</sub>           | OH = -4.0 mA,<br>IH = 2.2 V                                                                | 1, 2, 3   | All                                 | 2.4         |      | V        |

| Output low voltage                            | V <sub>OL</sub>     | V <sub>CC</sub> = 4.5 V,<br>V <sub>IL</sub> = 0.8 V,<br>V <sub>II</sub> = 2.2 V | 1/O <sub>0</sub> - 1/O <sub>15</sub><br>1 <sub>OL</sub> = 4.0 mA                           | 1, 2, 3   | All                                 |             | 0.4  | V        |

|                                               |                     | VIH - 2.2 V                                                                     | BUSY<br>I <sub>OL</sub> = 16 mA                                                            | 1, 2, 3   | 01,03,<br>05,07,<br>09,11,<br>13,15 |             | 0.5  | V        |

| Input leakage current                         | 141                 | V <sub>CC</sub> = 5.5 V,<br>GND ≤ V <sub>IN</sub> ≤ V                           | v <sub>cc</sub>                                                                            | 1, 2, 3   | All                                 |             | 5.0  | μА       |

| Output leakage current                        | I <sub>LO</sub>     | $V_{CC} = 5.5 \text{ V},$<br>$GND \leq V_{OUT}$                                 | CE = V <sub>IH</sub> ,<br>≤ V <sub>CC</sub>                                                | 1, 2, 3   | All                                 |             | 5.0  | μА       |

| Dynamic operating current (both ports active) | lcc                 | V <sub>CC</sub> = 5.5 V, 0<br>f = f <sub>max</sub> 1/, ou                       | CE = V <sub>IL</sub> ,                                                                     | 1, 2, 3   | 01-04                               |             | 240  | _ mA     |

|                                               |                     | $T = T_{\text{max}} \frac{1}{2}$ , outputs open                                 |                                                                                            |           | 05,06                               |             | 260  |          |

|                                               |                     |                                                                                 |                                                                                            |           | 07-10                               |             | 280  |          |

|                                               |                     |                                                                                 |                                                                                            |           | 11,12                               |             | 285  |          |

|                                               |                     |                                                                                 |                                                                                            |           |                                     |             |      |          |

|                                               |                     |                                                                                 |                                                                                            |           | 13,14                               |             | 290  | -        |

|                                               |                     |                                                                                 | <del></del>                                                                                |           | 15,16<br>01-04,                     |             | 295  |          |

| Standby power supply current (both ports,     | I <sub>SB1</sub>    | $V_{CC} = 5.5 V,$                                                               |                                                                                            | 1, 2, 3   | 07-10<br>05,06,                     |             | 65   | _ mA     |

| TTL input levels)                             |                     | CE <sub>L</sub> and CE <sub>R</sub>                                             | ≥ V <sub>IH</sub> ,                                                                        |           | 11-14                               |             | 70   |          |

|                                               |                     | $f = f_{MAX} 1$                                                                 | CE <sub>L</sub> and CE <sub>R</sub> ≥ V <sub>IH</sub> ,<br>i = i <sub>MAX</sub> <u>1</u> / |           | 15,16                               |             | 75   |          |

| Standby power supply                          | I <sub>SB2</sub>    | V <sub>CC</sub> = 5.5 V, (                                                      | CE, or CE                                                                                  | 1, 2, 3   | 01-04                               |             | 150  | mA       |

| current (one port,<br>TTL input levels)       | SB2                 | ≥ ∨լш,                                                                          |                                                                                            | -, -, -   | 05,06                               |             | 160  |          |

| i i L iliput levels)                          |                     | f = f <sub>MAX</sub> 1/, a<br>outputs open                                      | ouve port                                                                                  |           |                                     |             |      | -        |

|                                               |                     |                                                                                 |                                                                                            |           | 07-10                               |             | 180  | -        |

|                                               |                     |                                                                                 |                                                                                            |           | 11-14                               |             | 190  | -        |

|                                               |                     |                                                                                 |                                                                                            |           | 15,16                               |             | 200  |          |

| See footnotes at end of ta                    | ble.                |                                                                                 |                                                                                            |           |                                     |             |      |          |

|                                               | <u> </u>            |                                                                                 |                                                                                            | SIZE      |                                     | <del></del> |      |          |

|                                               | TANDARD<br>RCUIT DR |                                                                                 |                                                                                            | Α         |                                     |             | 59   | 962-8866 |

| DEFENSE SUPP                                  | LY CENTE            |                                                                                 |                                                                                            | F         | REVISION L                          | EVEL        | SHE  | ET       |

9004708 0025779 881 📟

|                                                              | TAB              | LE I. Electrical performan                                                                              | ce characteristic  | s - continued.    |            |     |          |

|--------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------|--------------------|-------------------|------------|-----|----------|

| 查询"5962-886650                                               | 1XX"供应           | /商 Conditions                                                                                           | Group A<br>Subgrou |                   | Limits     |     | Unit     |

|                                                              |                  | -55° C ≤ T <sub>C</sub> ≤ +125° C<br>V <sub>CC</sub> = 4.5 V to 5.5 V<br>unless otherwise specif        | fied               | урсо              | Min        | Max |          |

| Full standby power supply current (both                      | I <sub>SB3</sub> | V <sub>CC</sub> = 5.5 V, f = 0 <u>1</u> /,                                                              | 1, 2, 3            | All               |            | 10  | mA       |

| ports, CMOS input<br>levels)                                 |                  | $\overline{CE}_L$ and $\overline{CE}_R \ge V_{CC} - 0$<br>$V_{IN} \ge V_{CC} - 0.2 \text{ V or } \le 0$ | .2 V,<br>.2 V      |                   |            |     |          |

| Full standby power                                           | I <sub>SB4</sub> | V <sub>CC</sub> = 5.5 V, f <sub>max</sub> <u>1</u> /,                                                   | 1, 2, 3            | 01,02             |            | 135 | _ mA     |

| supply current (one port, CMOS input levels)                 |                  | $CE_L$ or $CE_R \ge V_{CC} - 0.2 V_{N} \ge V_{CC} - 0.2 V_{OC}$ active port outputs open                | 2 V,               | 03,04             |            | 140 | -        |

|                                                              |                  | active port outputs open                                                                                | .z v,              | 05,06             |            | 150 | _        |

|                                                              |                  |                                                                                                         |                    | 07-10             |            | 170 | _        |

|                                                              |                  |                                                                                                         |                    | 11-14             |            | 180 | _        |

|                                                              |                  |                                                                                                         |                    | 15,16             |            | 190 |          |

| V <sub>CC</sub> for data retention                           | V <sub>DR</sub>  | CE ≥ V <sub>CC</sub> - 0.2 V,<br>V <sub>IN</sub> ≥ V <sub>CC</sub> - 0.2 V                              | 1, 2, 3            | All               | 2.0        |     | V        |

| Data retention current                                       | ICCDR            |                                                                                                         | 1, 2, 3            | All               |            | 4.0 | mA       |

| Input leakage <u>2</u> /<br>current (data<br>retention mode) | iLi              |                                                                                                         | 1, 2, 3            | 01-06             |            | 2.0 | μА       |

| Input capacitance                                            | c <sub>IN</sub>  | V <sub>CC</sub> = 5.0 V, V <sub>I/O</sub> = 0 V,<br>f = 1.0 MHz, T <sub>A</sub> = +25°C<br>see 4.3.1c   | , 4                | All               |            | 11  | pF       |

| Output capacitance                                           | COUT             | V <sub>CC</sub> = 5.0 V, V <sub>I/O</sub> = 0 V,<br>f = 1.0 MHz, T <sub>A</sub> = +25°C<br>see 4.3.1c   | , 4                | All               |            | 11  | pF       |

| Functional tests                                             |                  | See 4.3.1d                                                                                              | 7, 8A, 8I          | B All             |            |     |          |

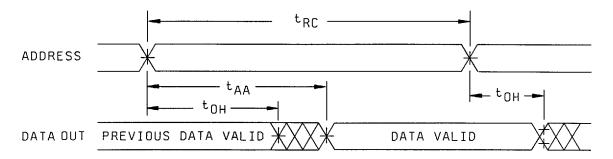

| Read cycle time                                              | 1.               | See figures 5 and 6 3/                                                                                  | 9, 10, 1           | 01,02,<br>1 07,08 | 90         |     | ns       |

| rread cycle lifte                                            | t <sub>RC</sub>  | Oce liguies 5 and 0 3/                                                                                  | 9, 10, 1           | 03,04,<br>09,10   | 70         |     | -        |

|                                                              |                  |                                                                                                         |                    | 05,06,            |            |     | -        |

|                                                              |                  |                                                                                                         |                    | 11.12             | 55         |     | -        |

|                                                              |                  |                                                                                                         |                    | 13,14             | 45         |     | -        |

| See footnotes at end of ta                                   | hle              | 1                                                                                                       |                    | 15,16             | 35         |     |          |

| occionides at end of ta                                      | J.O.             |                                                                                                         |                    |                   |            |     |          |

| s                                                            | TANDARD          |                                                                                                         | SIZE<br><b>A</b>   |                   |            | 5   | 962-8866 |

| MICROC<br>DEFENSE SUPP<br>COLUMBU                            |                  | R COLUMBUS                                                                                              | 7.                 | REVISION          | LEVEL<br>O | SHE |          |

■ 9004708 0025780 5T3 ■

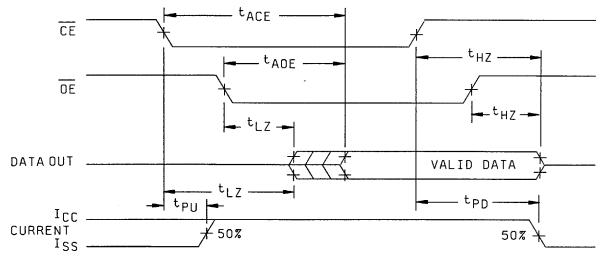

TABLE I. Electrical performance characteristics - continued. 查询"5962-8866501XX"供应商 Conditions Group A Device Limits Unit  $-55^{\circ}$  C  $\leq$  T<sub>C</sub>  $\leq$  +125° C V<sub>CC</sub> = 4.5 V to 5.5 V subgroups types Min Max unless otherwise specified 01,02, 90 ns Address access time t<sub>AA</sub> See figures 5 and 6 3/ 9, 10, 11 07,08 03,04, 09,10 70 05,06, <u>55</u> 11,12 13,14 45 15,16 35 01,02, 9, 10, 11 Output hold from See figures 5 and 6 3/ 07,08 10 ns t<sub>OH</sub> 03-06, address change 09-16 0 01,02, 90 ns See figures 5 and 6 3/ Chip enable access time 9, 10, 11 <sup>t</sup>ACE <u>07,08</u> 03,04, 70 09,10 05,06, 55 11,12 13,14 45 15.16 01-04, 40 ns 07<u>-10</u> 9, 10, 11 Output enable access See figures 5 and 6 3/ <sup>t</sup>AOE 05,06, time 11-12 35 25 13,14 20 15,16 Output low Z time t<sub>LZ</sub> See figures 5 and 6 2/4/ 9, 10, 11 01-12 5.0 ns 13-16 0 01,02, ns Output high Z time See figures 5 and 6 2/4/ 9, 10, 11 07,08 40 t<sub>HZ</sub> 03,04, 09,10 35 05,06, 20 <u>11-16</u> ΑII 0 See figures 5 and 6 2/3/ 9, 10, 11 Chip enable to power-up ns t<sub>PU</sub> time 9, 10, 11 ΑII 50 Chip disable to See figures 5 and 6 2/3/ ns <sup>t</sup>PD power-down time See footnotes at end of table. SIZE **STANDARD** 5962-88665 Α MICROCIRCUIT DRAWING **DEFENSE SUPPLY CENTER COLUMBUS** REVISION LEVEL SHEET **COLUMBUS, OHIO 43216-5000** D 7

DESC FORM 193A JUL 94

📟 9004708 0025781 43T 📟

| 查询"5962-88665                 | 501XX"供                | <del>立商</del> Conditions                                                                                    | Group A   | Device          | Limits |              | Unit                                             |

|-------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|-----------|-----------------|--------|--------------|--------------------------------------------------|

|                               |                        | $-55^{\circ}$ C ≤ T <sub>C</sub> ≤ +125°C<br>V <sub>CC</sub> = 4.5 V to 5.5 V<br>unless otherwise specified | subgroups | types           | Min    | Max          |                                                  |

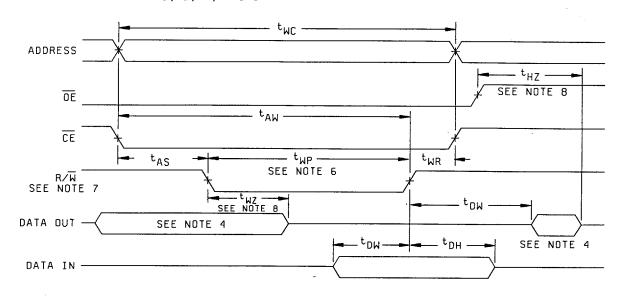

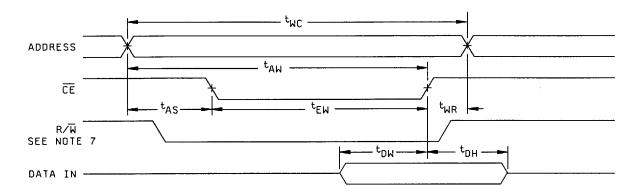

| Write cycle time <u>5</u> /   | t <sub>WC</sub>        | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | 01,02,<br>07,08 | 90     | ·            | ns                                               |

|                               |                        |                                                                                                             |           | 03,04,<br>09.10 | 70     |              | _                                                |

|                               |                        |                                                                                                             |           | 05,06,<br>11,12 | 55     |              |                                                  |

|                               |                        |                                                                                                             |           | 13,14           | 45     |              | _                                                |

|                               |                        |                                                                                                             |           | 15,16           | 35     |              |                                                  |

| Chip enable to end            | t <sub>EW</sub>        | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | 01,02,<br>07,08 | 85     |              | ns                                               |

| of write                      | 1 -EVV                 |                                                                                                             |           | 03,04,          |        |              | -                                                |

|                               | 1                      |                                                                                                             |           | 09,10<br>05,06, | 50     |              | -                                                |

|                               |                        |                                                                                                             |           | 11,12           | 40     |              | _                                                |

|                               |                        |                                                                                                             |           | 13,14           | 30     |              | _                                                |

|                               |                        |                                                                                                             |           | 15,16           | 25     |              |                                                  |

| Address valid to end of write |                        |                                                                                                             |           | 01,02,          |        |              |                                                  |

|                               | t <sub>AW</sub>        | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | 07,08<br>03,04, | 85     |              | ns                                               |

|                               |                        |                                                                                                             |           | 09,10           | 50     |              | _                                                |

|                               |                        |                                                                                                             |           | 05,06,<br>11,12 | 40     |              | _                                                |

|                               |                        |                                                                                                             |           | 13,14           | 30     |              | -                                                |

|                               |                        |                                                                                                             |           | 15,16           | 25     |              |                                                  |

| Address setup time            | tAS                    | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | All             | 0      |              | ns                                               |

| Write pulse width             | <b>.</b>               | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | 01,02,<br>07,08 | 55     |              | ns                                               |

| Write puise width             | t <sub>WP</sub>        | See ligures 5 and 7 3/                                                                                      | 9, 10, 11 | 03,04,          | 35     |              | - 115                                            |

| _                             |                        |                                                                                                             |           | 09,10           | 50     |              | _                                                |

|                               |                        |                                                                                                             |           | 05,06,<br>11,12 | 40     |              | _                                                |

|                               |                        |                                                                                                             |           | 13,14           | 30     |              | _                                                |

|                               |                        |                                                                                                             |           | 15,16           | 25     |              |                                                  |

| Write recovery time           | t <sub>WR</sub>        | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | All             | 0      |              | ns                                               |

|                               |                        |                                                                                                             |           | 01,02,          |        |              | <del>                                     </del> |

| Data valid to end of write    | t <sub>DW</sub>        | See figures 5 and 7 3/                                                                                      | 9, 10, 11 | 07-08<br>03,04, | 30     | +            | _ ns                                             |

|                               |                        |                                                                                                             |           | 09,10           | 25     | <del> </del> | _                                                |

|                               |                        |                                                                                                             |           | 05,06,<br>11-16 | 20     |              |                                                  |

| See footnotes at end of t     | able.                  | · —————                                                                                                     | ,         | , —             |        |              |                                                  |

|                               | <b>A</b>               |                                                                                                             | SIZE      |                 |        |              |                                                  |

|                               | STANDARE<br>CIRCUIT DR |                                                                                                             | A         |                 |        | 5            | 962-8866                                         |

| DEFENSE SUP                   | PLY CENTE              | ER COLUMBUS                                                                                                 |           | REVISION I      | EVEL   | SHE          | ET                                               |

| COLUMBI                       | US, OHIO 4:            | 3276-5000                                                                                                   |           |                 | `      | ı            | 8                                                |

9004708 0025782 376

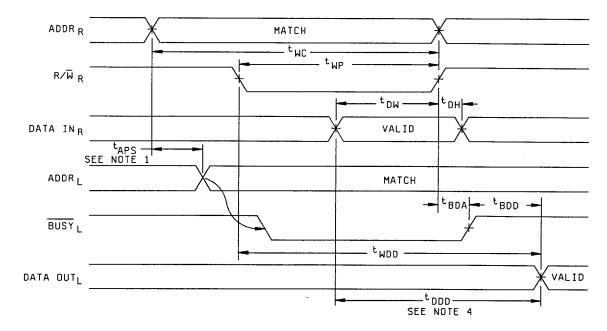

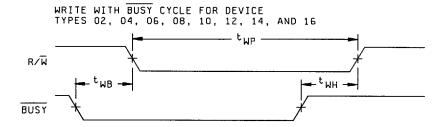

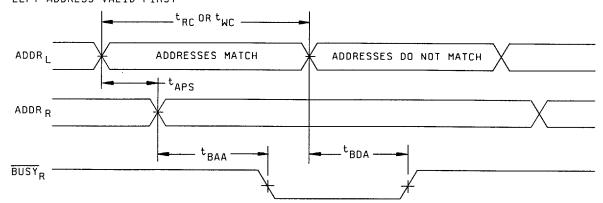

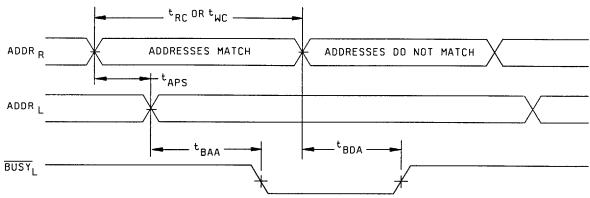

TABLE I. Electrical performance characteristics - continued. 查询"5962-8866501) Conditions Group A Device Limits Unit  $-55^{\circ}$  C  $\leq$  T<sub>C</sub>  $\leq$  +125° C V<sub>CC</sub> = 4.5 V to 5.5 V subgroups types Min Max unless otherwise specified 01-04, Output high Z time See figures 5 and 7 2/4/ 9, 10, 11 07-10 25 t<sub>HZ</sub> ns 05,06, 20 <u>11-16</u> Data hold time 7/ See figures 5 and 7 3/ 9, 10, 11 01-14 5.0 ns <sup>t</sup>DH 15,16 0 01-04, Write enable to See figures 5 and 7 2/4/ 9, 10, 11 25 t<sub>WZ</sub> 07-10 ns output in high Z 05,06, 11-16 20 01-06, Output active 7/ See figures 5 and 7 2/4/ 9, 10, 11 0 tow <u> 15,16</u> ns from end of write 07-14 5 02,04, Write to BUSY 8/ See figures 5 and 8 3/ 9, 10, 11 06,08, 0 t<sub>WB</sub> ns 10,12, 14,16 02,04, Write hold after BUSY See figures 5 and 8 3/ 9, 10, 11 06,08, 30 t<sub>WH</sub> ns 9/ 10,12, 14 <u>25</u> 16 01,03, 9, 10, 11 **BUSY** access time to See figures 5 and 8 3/ 07,09 55 t<sub>BAA</sub> ns address 05,11 50 45 13 15 35 01,03, **BUSY** disable time to See figures 5 and 8 3/ 9, 10, 11 07,09 45 <sup>t</sup>BDA ns address 05,11, 13 40 15 30 **BUSY** access time to See figures 5 and 8 3/ 9, 10, 11 01,07 45 <sup>t</sup>BAC ns chip enable 03,05, 09,11 35 13 30 15 25 See footnotes at end of table. SIZE STANDARD 5962-88665 Α MICROCIRCUIT DRAWING **DEFENSE SUPPLY CENTER COLUMBUS REVISION LEVEL** SHEET **COLUMBUS, OHIO 43216-5000** D 9

DESC FORM 193A JUL 94

**■ 9004708 0025783 202 ■**

#### TABLE I. Electrical performance characteristics - continued.

| 查询"5962-886650<br>Test            | Symbol Symbol    | Conditions                                                                                          | Group A   | Device                    | Li  | imits | _ Unit |

|-----------------------------------|------------------|-----------------------------------------------------------------------------------------------------|-----------|---------------------------|-----|-------|--------|

|                                   |                  | -55° C ≤ T <sub>C</sub> ≤ +125° C<br>V <sub>CC</sub> = 4.5 V to 5.5 V<br>unless otherwise specified | subgroups | types                     | Min | Max   |        |

| BUSY disable time to              | t <sub>BDC</sub> | See figures 5 and 8 3/                                                                              | 9, 10, 11 | 01,07                     |     | 45    | ns     |

| chip enable                       |                  |                                                                                                     |           | 03,05,<br>09,11           |     | 30    |        |

|                                   |                  |                                                                                                     |           | 13                        |     | 25    | _      |

|                                   |                  |                                                                                                     |           | 15                        |     | 20    |        |

| Write pulse to                    | t <sub>WDD</sub> | See figures 5 and 8 3/                                                                              | 9, 10, 11 | 01,02,<br>07,08           |     | 100   | ns     |

| data delay <u>2</u> / <u>10</u> / |                  |                                                                                                     |           | 03,04,<br>_09,10          |     | 90    | _      |

|                                   |                  |                                                                                                     |           | 05,06,<br>11-14           |     | 80    | _      |

|                                   |                  |                                                                                                     |           | 15,16                     |     | 60    |        |

| Write data valid to               | t <sub>DDD</sub> | See figures 5 and 8 3/                                                                              | 9, 10, 11 | 01,02,<br><u>07,08</u>    |     | 90    | ns     |

| read data delay<br>2/ <u>10</u> / |                  |                                                                                                     |           | 03,04,<br>09,10           |     | 70    | _      |

|                                   |                  | -                                                                                                   |           | 05,06                     |     | 80    | _      |

|                                   |                  |                                                                                                     |           | 11-14                     |     | 55    | _      |

|                                   |                  |                                                                                                     |           | 15,16                     |     | 45    |        |

| BUSY disable to valid data        | t <sub>BDD</sub> | See figures 5 and 8 3/                                                                              | 9, 10, 11 | All                       |     | 11/   | ns     |

| Arbitration priority              | tAPS             | See figures 5 and 8 3/                                                                              | 9, 10, 11 | 01,07                     | 10  |       | ns     |

| setup time                        | 7, 0             | _                                                                                                   |           | 03,05,<br>09,11,<br>13,15 | 5.0 |       |        |

At  $f = f_{MAX}$  address and data inputs are cycling at the maximum frequency of read cycles of  $1/t_{RC}$ . f = 0 means no input lines change.

May not be tested, but shall be guaranteed to the limits specified in table I.

For master/slave combination,  $t_{WC} = t_{BAA} + t_{WR} + t_{WP}$ .

Specified for OE at high.

10, 12, 14, and 16).

To ensure that a write cycle is completed after contention. Applicable to slave devices only (device types 02, 04, 06, 08, 10, 12, 14, and 16).

10/ Port to port delay through RAM cells from writing port to reading port.

$\overline{11}$ /  $t_{BDD}$  is a calculated parameter and is the greater of 0,  $t_{WDD}$  -  $t_{WP}$  (actual), or  $t_{DDD}$  -  $t_{DW}$  (actual).

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-88665         |

|----------------------------------------------------------------------------------------|------------------|---------------------|--------------------|

|                                                                                        |                  | REVISION LEVEL<br>D | SHEET<br><b>10</b> |

DESC FORM 193A **JUL 94**

9004708 0025784 149 📟

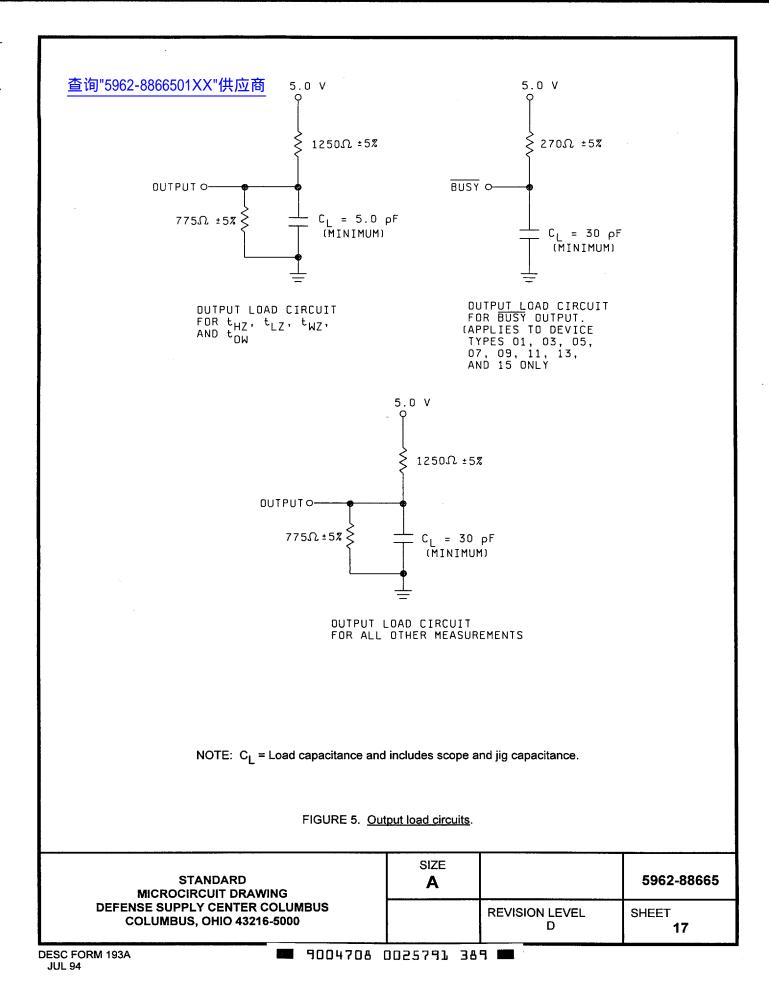

Test conditions assume signal transition times of 5.0 ns or less. Timing is referenced at input and output levels of 1.5 V and input pulse levels of 0 V to 3.0 V. Output loading is equivalent to the specified  $I_{OL}/I_{OH}$  with a load capacitance of 30 minutes are conditionally specified to the specified  $I_{OL}/I_{OH}$  with a load capacitance of 30 minutes are conditions.

Test conditions assume signal transition times of 5.0 ns or less. Transition is measured at steady-state high level of -500 mV or steady-state low level of +500 mV on the output from 1.5 V level on the input with a load capacitance of 5.0 pF (see figure 5).

The specification for t<sub>DH</sub> must be met by the device supplying write data to the RAM under all conditions. Although t<sub>DH</sub> and t<sub>OW</sub> values will vary over voltage and temperature the actual t<sub>DH</sub> will always be smaller than the actual t<sub>OW</sub>. To ensure that the write cycle is inhibited during contention. Applicable to slave devices only (device types 02, 04, 06, 08, 08, 08).

## Case outline X

# 查询"5962-8866501XX"供应商

| Symbol | Inc   | hes   | Millin | neters |

|--------|-------|-------|--------|--------|

|        | Min   | Max   | Min    | Max    |

| Α      | .085  | .190  | 2.16   | 4.83   |

| b      | .014  | .023  | 0.36   | 0.58   |

| b1     | .030  | .060  | 0.76   | 1.52   |

| C      | .008  | .015  | 0.20   | 0.38   |

| D      | 2.380 | 2.440 | 60.45  | 61.98  |

| E      | .580  | .610  | 14.73  | 15.49  |

| E1     | .590  | .620  | 14.99  | 15.75  |

| Symbol | inc  | hes  | Millin | neters |

|--------|------|------|--------|--------|

|        | Min  | Max  | Min    | Max    |

| е      | .070 | BSC  | 1.78   | BSC    |

| L      | .125 | .200 | 3.18   | 5.08   |

| L1     | .150 |      | 3.81   |        |

| Q      | .020 | .070 | 0.51   | 1.78   |

| S      | .030 | .065 | 0.77   | 1.66   |

| S1     | .005 |      | 0.13   |        |

| S2     | .005 |      | 0.13   |        |

## NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are for general information only.

FIGURE 1. Case outlines.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

SP62-88665

REVISION LEVEL

D

11

DESC FORM 193A JUL 94

9004708 0025785 085

| Symbol | Inc   | hes   | Millin | neters |

|--------|-------|-------|--------|--------|

|        | Min   | Max   | Min    | Max    |

| Α      | .080  | .120  | 2.03   | 3.05   |

| A1     | .070  | .090  | 1.78   | 2.29   |

| В      | .014  | .021  | 0.36   | 0.53   |

| С      | .008  | .012  | 0.20   | 0.30   |

| D/E    | 1.640 | 1.870 | 41.66  | 47.50  |

| D1/E1  | .926  | .970  | 23.52  | 24.64  |

| Symbol | Inches  |      | Millin   | neters |  |

|--------|---------|------|----------|--------|--|

|        | Min Max |      | Min      | Max    |  |

| D2/E2  | .800    | BSC  | 20.32    | BSC    |  |

| е      | .050    | BSC  | 1.27 BSC |        |  |

| L      | .350    | .450 | 8.89     | 11.43  |  |

| N      | 68      |      |          |        |  |

| ND     | 17      |      |          |        |  |

### NOTES:

- 1. All dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- 3. BSC Basic lead spacing between centers.4. Symbol "N" represents number of leads.

FIGURE 1. Case outlines - continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88665 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | D              | <b>12</b>  |

DESC FORM 193A JUL 94

■ 9004708 0025786 Tll **■**

查询"5962

| Device types                                                               | ALL                | ALL                | Device types    | ALL                        | ALL                |

|----------------------------------------------------------------------------|--------------------|--------------------|-----------------|----------------------------|--------------------|

| Case outlines<br>### Case Outlines<br>#################################### | ,,,,,, and U       | Z                  | Case outlines   | X, Y, and U                | Z                  |

| Terminal<br>number                                                         | Terminal sym       |                    | Terminal number | Terminal symbol            | <u>1</u> /         |

| 1                                                                          | 1/0 <sub>0L</sub>  | 1/0 <sub>9L</sub>  | 35              | GND <u>2</u> /             | A <sub>5R</sub>    |

| 2                                                                          | 1/0 <sub>1L</sub>  | 1/0 <sub>10L</sub> | 36              | R/W <sub>RUB</sub>         | A <sub>4R</sub>    |

| 3                                                                          | 1/0 <sub>2L</sub>  | <sup>I/O</sup> 11L | 37              | R/W <sub>RLB</sub>         | A <sub>3R</sub>    |

| 4                                                                          | 1/0 <sub>3L</sub>  | 1/0 <sub>12L</sub> | 38              | ōE <sub>R</sub>            | A <sub>2R</sub>    |

| 5                                                                          | 1/0 <sub>4L</sub>  | <sup>I/O</sup> 13L | 39              | A <sub>10R</sub>           | A <sub>1R</sub>    |

| 6                                                                          | 1/O <sub>5L</sub>  | 1/0 <sub>14L</sub> | 40              | A <sub>9R</sub>            | A <sub>OR</sub>    |

| 7                                                                          | <sup>I/O</sup> 6L  | <sup>I/O</sup> 15L | 41              | A <sub>8R</sub>            | BUSYR              |

| 8                                                                          | 1/0 <sub>7L</sub>  | V <sub>CC</sub> 2/ | 42              | A <sub>7R</sub>            | CER                |

| 9                                                                          | 1/0 <sub>8L</sub>  | GND <u>2</u> /     | 43              | A <sub>6R</sub>            | CEL                |

| 10                                                                         | 1/0 <sub>9L</sub>  | 1/0 <sub>0R</sub>  | 44              | A <sub>5R</sub>            | BUSYL              |

| 11                                                                         | 1/O <sub>10L</sub> | <sup>I/O</sup> 1R  | 45              | A <sub>4R</sub>            | A <sub>OL</sub>    |

| 12                                                                         | <sup>I/O</sup> 11L | 1/0 <sub>2R</sub>  | 46              | A <sub>3R</sub>            | A <sub>1L</sub>    |

| 13                                                                         | I/O <sub>12L</sub> | <sup>I/O</sup> 3R  | 47              | A <sub>2R</sub>            | A <sub>2L</sub>    |

| 14                                                                         | 1/O <sub>13L</sub> | 1/0 <sub>4R</sub>  | 48              | A <sub>1R</sub>            | A <sub>3L</sub>    |

| 15                                                                         | I/O <sub>14L</sub> | 1/0 <sub>5R</sub>  | 49              | A <sub>OR</sub>            | A <sub>4L</sub>    |

| 16                                                                         | <sup>I/O</sup> 15L | <sup>I/O</sup> 6R  | 50              | BUSYR                      | A <sub>5L</sub>    |

| 17                                                                         | V <sub>CC</sub> 2/ | 1/0 <sub>7R</sub>  | 51              | CER                        | A <sub>6L</sub>    |

| 18                                                                         | GND <u>2</u> /     | 1/0 <sub>8R</sub>  | 52              | CEL                        | A <sub>7L</sub>    |

| 19                                                                         | 1/0 <sub>0R</sub>  | 1/0 <sub>9R</sub>  | 53              | BUSYL                      | A <sub>8L</sub>    |

| 20                                                                         | <sup>1/O</sup> 1R  | <sup>I/O</sup> 10R | 54              | A <sub>OL</sub>            | A <sub>9L</sub>    |

| 21                                                                         | 1/0 <sub>2R</sub>  | I/O <sub>11R</sub> | 55              | A <sub>1L</sub>            | A <sub>10L</sub>   |

| 22                                                                         | 1/0 <sub>3R</sub>  | I/O <sub>12R</sub> | 56              | A <sub>2L</sub>            | OE <sub>L</sub>    |

| 23                                                                         | I/O <sub>4R</sub>  | I/O <sub>13R</sub> | 57              | A <sub>3L</sub>            | R/W <sub>LLB</sub> |

| 24                                                                         | !/0 <sub>5R</sub>  | I/O <sub>14R</sub> | 58              | A <sub>4L</sub>            | R∕Ŵ <sub>LUB</sub> |

| 25                                                                         | 1/0 <sub>6R</sub>  | <sup>I/O</sup> 15R | 59              | A <sub>5L</sub>            | V <sub>CC</sub> 2/ |

| 26                                                                         | 1/0 <sub>7R</sub>  | GND <u>2</u> /     | 60              | A <sub>6L</sub>            | 1/0 <sub>0L</sub>  |

| 27                                                                         | 1/0 <sub>8R</sub>  | R/W <sub>RUB</sub> | 61              | A <sub>7L</sub>            | 1/0 <sub>1L</sub>  |

| 28                                                                         | I/O <sub>9R</sub>  | R/W <sub>RLB</sub> | 62              | A <sub>8L</sub>            | 1/0 <sub>2L</sub>  |

| 29                                                                         | <sup>I/O</sup> 10R | ōE <sub>R</sub>    | 63              | A <sub>9L</sub>            | 1/0 <sub>3L</sub>  |

| 30                                                                         | <sup>I/O</sup> 11R | A <sub>10R</sub>   | 64              | A <sub>10L</sub>           | 1/0 <sub>4L</sub>  |

| 31                                                                         | 1/0 <sub>12R</sub> | A <sub>9R</sub>    | 65              | OEL                        | 1/0 <sub>5L</sub>  |

| 32                                                                         | I/O <sub>13R</sub> | A <sub>8R</sub>    | 66              | R/W <sub>LLB</sub>         | 1/0 <sub>6L</sub>  |

| 33                                                                         | I/O <sub>14R</sub> | A <sub>7R</sub>    | 67              | R/W <sub>LUB</sub>         | 1/0 <sub>7L</sub>  |

| 34                                                                         | <sup>I/O</sup> 15R | A <sub>6R</sub>    | 68              | V <sub>CC</sub> <u>2</u> / | 1/0 <sub>8L</sub>  |

<sup>1/</sup> An "L" suffix on a terminal indicates it applies to the "left port", and an "R" suffix indicates it applies to the "right port".

2/ Both V<sub>CC</sub> pins and both GND pins must be connected to the supply in order to assure reliable operation.

FIGURE 2. Terminal connections.

| STANDARD<br>MICROCIRCUIT DRAWING                         | SIZE<br><b>A</b> |                     | 5962-88665  |

|----------------------------------------------------------|------------------|---------------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>D | SHEET<br>13 |

DESC FORM 193A JUL 94

9004708 0025787 958

#### Device types: All

查询"5962-8866501XX"供应商Noncontention read/write control (see note 1)

|                   | Left              | or righ | t port ( | (see note 2)        |                     |                                                                                                        |

|-------------------|-------------------|---------|----------|---------------------|---------------------|--------------------------------------------------------------------------------------------------------|

| R/W <sub>LB</sub> | R/₩ <sub>UB</sub> | CE      | ŌΕ       | 1/O <sub>0-7</sub>  | I/O <sub>8-15</sub> | Function                                                                                               |

| Х                 | Х                 | Н       | х        | Z                   | Z                   | Port disabled and in power down mode, I <sub>SB2</sub> or I <sub>SB4</sub>                             |

| х                 | x                 | Н       | Х        | Z                   | Z                   | CE <sub>R</sub> = CE <sub>L</sub> = H, power down mode, I <sub>SB1</sub> or I <sub>SB3</sub>           |

| L                 | L                 | L       | Х        | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Data on lower byte and upper byte written into memory (see note 3).                                    |

| L                 | Н                 | L       | L        | DATA <sub>IN</sub>  | DATA <sub>OUT</sub> | Data on lower byte written into memory (see note 3). Data in memory output on upper byte (see note 4). |

| Н                 | L                 | L       | L        | DATA <sub>OUT</sub> | DATA <sub>IN</sub>  | Data in memory output on lower byte (see note 4). Data on upper byte written into memory (see note 3). |

| L                 | Н                 | L       | Н        | DATA <sub>IN</sub>  | Z                   | Data on lower byte written in memory (see note 3).                                                     |

| Н                 | L .               | L       | Н        | Z                   | DATA <sub>IN</sub>  | Data on upper byte written into memory (see note 3).                                                   |

| Н                 | Н                 | L       | L        | DATAOUT             | DATAOUT             | Data in memory output on lower byte and upper byte (see note 4).                                       |

| H                 | Н                 | L       | Н        | z                   | Z                   | High impedance outputs.                                                                                |

### NOTES:

- 1. H = High, L = Low, X = Don't care, Z = High impedance, LB = Lower byte, UB = Upper byte.

- A<sub>OL</sub> A<sub>1OL</sub> ≠ A<sub>OR</sub> A<sub>1OR</sub>

If BUSY = L, data is not written.

If BUSY = L, data may not be valid, see t<sub>WDD</sub> and t<sub>DDD</sub> timing.

### FIGURE 3. Truth tables.

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-88665      |

|----------------------------------------------------------------------------------------|------------------|---------------------|-----------------|

|                                                                                        |                  | REVISION LEVEL<br>D | SHEET <b>14</b> |

DESC FORM 193A JUL 94

9004708 0025788 894

|     | Left port          |                                     | R              | ight port                           | Fla         | ıgs        |                      |

|-----|--------------------|-------------------------------------|----------------|-------------------------------------|-------------|------------|----------------------|

| 查询  | '5 <b>9.62</b> -88 | 66504438"供应                         | 彦 <sub>R</sub> | A <sub>0R</sub> -A <sub>10R</sub>   | BUSYL       | BUSYR      | Function             |

|     | Η                  | X                                   | Н              | Х                                   | Н           | Н          | No contention        |

|     | L                  | Any                                 | Н              | Х                                   | Н           | н          | No contention        |

|     | Н                  | Х                                   | L              | Any                                 | Н           | Н          | No contention        |

|     | L                  | <sup>≠ A</sup> 0R <sup>-A</sup> 10R | L              | <sup>≠ A</sup> 0L <sup>-A</sup> 10L | Н           | Н          | No contention        |

|     |                    | Ado                                 | iress arbit    | ration with CE lov                  | w before ad | dress matc | h                    |

|     | L                  | LV5R                                | L              | LV5R                                | Н           | L          | L-Port wins          |

|     | L                  | RV5L                                | L              | RV5L                                | L           | Н          | R-Port wins          |

|     | L                  | Same                                | L              | Same                                | Н           | L          | Arbitration resolved |

|     | L                  | Same                                | L              | Same                                | L           | Н          | Arbitration resolved |

|     |                    | •                                   | CE arbitr      | ation with addres                   | s match be  | fore CE    |                      |

|     | LL5R               | = A <sub>0R</sub> -A <sub>10R</sub> | LL5R           | = A <sub>OL</sub> -A <sub>10L</sub> | Н           | L          | L-Port wins          |

|     | RL5L               | = A <sub>0R</sub> -A <sub>10R</sub> | RL5L           | = A <sub>OL</sub> -A <sub>10L</sub> | L           | Н          | R-Port wins          |

| . [ | LW5R               | = A <sub>0R</sub> -A <sub>10R</sub> | LW5R           | = A <sub>OL</sub> -A <sub>10L</sub> | Н           | L          | Arbitration resolved |

|     | LW5R               | = A <sub>OR</sub> -A <sub>10R</sub> | LW5R           | = A <sub>OL</sub> -A <sub>10L</sub> | L           | Н          | Arbitration resolved |