## **Constant Current N-Channel Controller with Thermal** Foldback for Driving LEDs

## **General Description**

The LM3424 is a versatile high voltage N-channel MosFET controller for LED drivers. It can be easily configured in buck, boost, buck-boost and SEPIC topologies. In addition, the LM3424 includes a thermal foldback feature for temperature management of the LEDs. This flexibility, along with an input voltage rating of 75V, makes the LM3424 ideal for illuminating LEDs in a large family of applications.

Adjustable high-side current sense voltage allows for tight regulation of the LED current with the highest efficiency possible. The LM3424 uses standard peak current-mode control providing inherent input voltage feed-forward compensation for better noise immunity. It is designed to provide accurate thermal foldback with a programmable foldback breakpoint and slope. In addition, a 2.45V reference is provided.

The LM3424 includes a high-voltage startup regulator that operates over a wide input range of 4.5V to 75V. The internal PWM controller is designed for adjustable switching frequencies of up to 2.0 MHz and external synchronization is possible. The controller is capable of high speed PWM dimming and analog dimming. Additional features include slope compensation, softstart, over-voltage and under-voltage lock-out, cycle-by-cycle current limit, and thermal shutdown.

The LM3424Q is an Automotive Grade product that is AEC-Q100 grade 1 qualified.

### **Features**

- LM3424Q is an Automotive Grade product that is AEC-Q100 grade 1 gualified (-40°C to +125°C operating junction temperarure)

- V<sub>IN</sub> range from 4.5V to 75V

- -High-side adjustable current sense

- 2Ω, 1A Peak MosFET gate driver

- Input under-voltage and output over-voltage protection

- PWM and analog dimming

- Cycle-by-cycle current limit

- Programmable slope compensation

- Programmable, synchronizable switching frequency

- Programmable thermal foldback

- Programmable softstart

- Precision voltage reference

- Low power shutdown and thermal shutdown

## Applications

- LED Drivers Buck, Boost, Buck-Boost, and SEPIC

- Indoor and Outdoor Area SSL

- Automotive

- **General Illumination**

100

95

90

85

80 ⊾ 10

EFFICIENCY (%)

**Constant-Current Regulators**

20

15

.M3424 Constant Current N-Channel Controller with Thermal Foldback for Driving LEDs

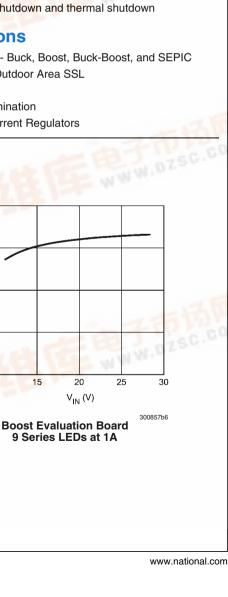

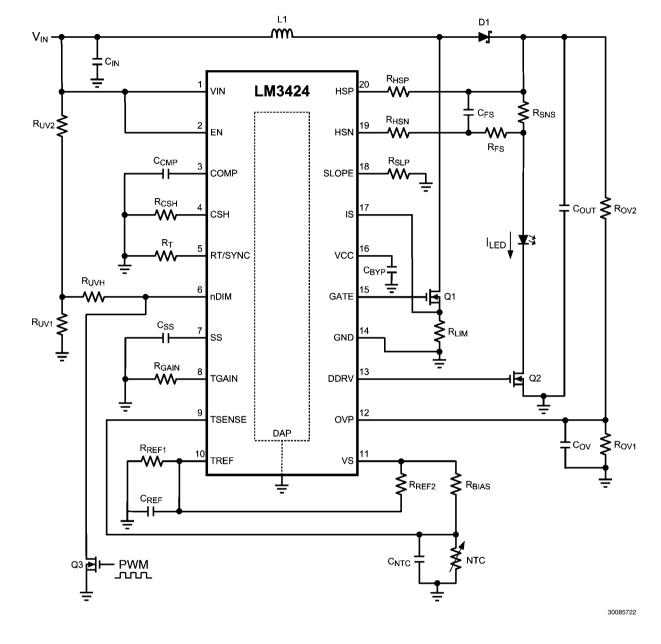

## Typical Boost Application Circuit

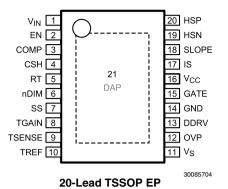

## 查**倚onmaoti**帜型諸agram

## **Ordering Information**

| Order      | Spec. | Package Type | NSC Package | Supplied As               | Features                             |

|------------|-------|--------------|-------------|---------------------------|--------------------------------------|

| Number     |       |              | Drawing     |                           |                                      |

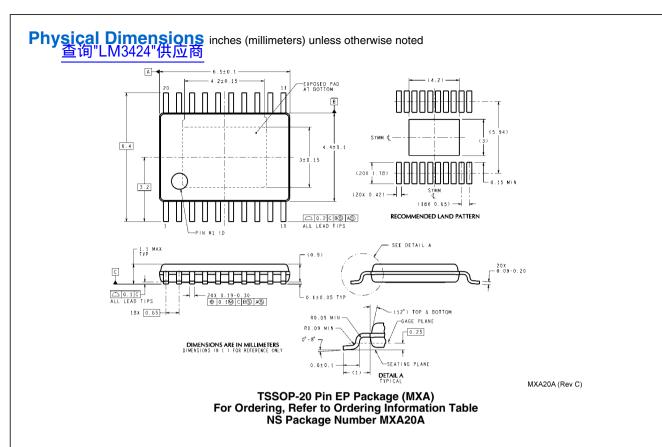

| LM3424MH   | NOPB  | TSSOP-20 EP  | MXA20A      | 73 Units, Rail            |                                      |

| LM3424MHX  | NOPB  | TSSOP-20 EP  | MXA20A      | 2500 Units, Tape and Reel |                                      |

| LM3424QMH  | NOPB  | TSSOP-20 EP  | MXA20A      | 73 Units, Rail            | AEC-Q100 Grade 1 qualified.          |

| LM3424QMHX | NOPB  | TSSOP-20 EP  | MXA20A      | 2500 Units, Tape and Reel | Automotive Grade Production<br>Flow* |

\*Automotive Grade (Q) product incorporates enhanced manufacturing and support processes for the automotive market, including defect detection methodologies. Reliability qualification is compliant with the requirements and temperature grades defined in the AEC-Q100 standard. Automotive grade products are identified with the letter Q. For more information go to http://www.national.com/automotive.

| Pin | <b>Descrip</b><br>查询"LM3 | <b>tions</b><br>424"供应商                     |                                                                                                                                                                  |  |  |

|-----|--------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin | Name                     | Description                                 | Application Information                                                                                                                                          |  |  |

| 1   | V <sub>IN</sub>          | Input Voltage                               | Bypass with 100 nF capacitor to GND as close to the device as possible.                                                                                          |  |  |

| 2   | EN                       | Enable                                      | Connect to $> 2.4V$ to enable the device or to $< 0.8V$ for low power shutdown.                                                                                  |  |  |

| 3   | COMP                     | Compensation                                | Connect a capacitor to GND to compensate control loop.                                                                                                           |  |  |

| 4   | CSH                      | Current Sense High                          | Connect a resistor to GND to set the signal current. Can also be used to analog dim as explained in the <i>Thermal Foldback / Analog Dimming</i> section.        |  |  |

| 5   | RT                       | Resistor Timing                             | Connect a resistor to GND to set the switching frequency. Can also be used to synchronize external clock as explained in the <i>Switching Frequency</i> section. |  |  |

| 6   | nDIM                     | Dimming Input /<br>Under-Voltage Protection | Connect a PWM signal for dimming as detailed in the <i>PWM Dimming</i> section and/or a resistor divider from $V_{IN}$ to program input under-voltage lockout.   |  |  |

| 7   | SS                       | Soft-start                                  | Connect a capacitor to GND to extend start-up time.                                                                                                              |  |  |

| 8   | TGAIN                    | Temp Foldback Gain                          | Connect a resistor to GND to set the foldback slope.                                                                                                             |  |  |

| 9   | TSENSE                   | Temp Sense Input                            | Connect a resistor/ thermistor divider from V <sub>S</sub> to sense the temperature as explained in the <i>Thermal Foldback / Analog Dimming</i> section.        |  |  |

| 10  | TREF                     | Temp Foldback Reference                     | Connect a resistor divider from V <sub>S</sub> to set the foldback reference voltage.                                                                            |  |  |

| 11  | Vs                       | Voltage Reference                           | 2.45V reference for temperature foldback circuit and other external circuitry.                                                                                   |  |  |

| 12  | OVP                      | Over-Voltage Protection                     | Connect a resistor divider from V <sub>O</sub> to program output over-voltage lockout.                                                                           |  |  |

| 13  | DDRV                     | Dimming Gate Drive Output                   | Connect to gate of dimming MosFET.                                                                                                                               |  |  |

| 14  | GND                      | Ground                                      | Connect to DAP to provide proper system GND                                                                                                                      |  |  |

| 15  | GATE                     | Main Gate Drive Output                      | Connect to gate of main switching MosFET.                                                                                                                        |  |  |

| 16  | V <sub>cc</sub>          | Internal Regulator Output                   | Bypass with a 2.2 $\mu$ F – 3.3 $\mu$ F, ceramic capacitor to GND.                                                                                               |  |  |

| 17  | IS                       | Main Switch Current Sense                   | Connect to the drain of the main N-channel MosFET switch for R <sub>DS-ON</sub> sensin<br>or to a sense resistor installed in the source of the same device.     |  |  |

| 18  | SLOPE                    | Slope Compensation                          | Connect a resistor to GND to set slope of additional ramp.                                                                                                       |  |  |

| 19  | HSN                      | LED Current Sense Negative                  | Connect through a series resistor to LED current sense resistor (negative).                                                                                      |  |  |

| 20  | HSP                      | LED Current Sense Positive                  | Connect through a series resistor to LED current sense resistor (positive).                                                                                      |  |  |

| DAP | DAP                      | Thermal pad on bottom of IC                 | Connect to GND. Refer to ( <i>Note 2</i> ) for thermal considerations.                                                                                           |  |  |

Absolute Maximum Ratings (Note 1) 间"I M3424"供放荷 In Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| V <sub>IN</sub> , EN, nDIM            | -0.3V to 76.0V                       |

|---------------------------------------|--------------------------------------|

|                                       | -1 mA continuous                     |

| OVP, HSP, HSN                         | -0.3V to 76.0V                       |

|                                       | -100 µA continuous                   |

| IS                                    | -0.3V to 76.0V                       |

|                                       | -2V for 100 ns                       |

|                                       | -1 mA continuous                     |

| V <sub>CC</sub>                       | -0.3V to 8.0V                        |

| V <sub>S</sub> , TREF, TSENSE, TGAIN, |                                      |

| COMP, CSH, RT, SLOPE, SS              | -0.3V to 6.0V                        |

| SS                                    | -30 μA to +30 μA                     |

|                                       | continuous                           |

| GATE, DDRV                            | -0.3V to V <sub>CC</sub>             |

|                                       | -2.5V for 100 ns                     |

|                                       | V <sub>CC</sub> +2.5V for 100 ns     |

|                                       | d and the indiana A manufactures and |

-1 mA to +1 mA continuous

#### GND

| GND                                                            | -0.3V to 0.3V<br>-2.5V to 2.5V for 100 ns |

|----------------------------------------------------------------|-------------------------------------------|

| Maximum Junction<br>Temperature                                | Internally Limited                        |

| Storage Temperature Range                                      | –65°C to +150°C                           |

| Maximum Lead Temperature (Reflow and Solder) ( <i>Note 3</i> ) | 260°C                                     |

| Continuous Power Dissipation                                   | Internally Limited                        |

| ESD Susceptibility (Note 4)                                    |                                           |

| Human Body Model                                               | 2 kV                                      |

## **Operating Conditions** (Note 1)

| Operating Junction            |                 |

|-------------------------------|-----------------|

| Temperature Range             | –40°C to +125°C |

| Input Voltage V <sub>IN</sub> | 4.5V to 75V     |

## Electrical Characteristics (Note 1)

Specifications in standard type face are for  $T_J = 25^{\circ}C$  and those with **boldface type** apply over the full **Operating Temperature** Range (T<sub>1</sub> = -40°C to +125°C). Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_1 = +25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise stated the following condition applies:  $V_{IN} = +14V$ .

| Symbol               | Parameter                             | Conditions                      | Min<br>( <i>Note 5</i> ) | Typ<br>( <i>Note 6</i> ) | Max<br>( <i>Note 5</i> ) | Units |  |

|----------------------|---------------------------------------|---------------------------------|--------------------------|--------------------------|--------------------------|-------|--|

| STARTUP REG          | ULATOR (V <sub>cc</sub> )             |                                 |                          |                          |                          |       |  |

| V <sub>CC-REG</sub>  | V <sub>CC</sub> Regulation            | I <sub>CC</sub> = 0 mA          | 6.30                     | 6.90                     | 7.35                     | V     |  |

| CC-LIM               | V <sub>CC</sub> Current Limit         | $V_{CC} = 0V$                   | 20                       | 25                       |                          |       |  |

| l <sub>o</sub>       | Quiescent Current                     | EN = 3.0V, Static               |                          | 2.0                      | 3.0                      | mA    |  |

| SD                   | Shutdown Current                      | EN = 0V                         |                          | 0.1                      | 1.0                      | μA    |  |

| V <sub>CC-UVLO</sub> | V <sub>CC</sub> UVLO Threshold        | V <sub>CC</sub> Increasing      |                          | 4.17                     | 4.50                     |       |  |

|                      |                                       | V <sub>CC</sub> Decreasing      | 3.70                     | 4.08                     |                          | v     |  |

| V <sub>CC-HYS</sub>  | V <sub>CC</sub> UVLO Hysteresis       |                                 |                          | 0.1                      |                          |       |  |

| ENABLE (EN)          |                                       |                                 |                          |                          |                          |       |  |

| V <sub>EN-ST</sub>   | EN Startup Threshold                  | EN Increasing                   |                          | 1.75                     | 2.40                     | V     |  |

|                      |                                       | EN decreasing                   | 0.80                     | 1.63                     |                          |       |  |

| V <sub>EN-HYS</sub>  | EN Startup Hysteresis                 |                                 |                          | 0.1                      |                          |       |  |

| R <sub>EN</sub>      | EN Pull-down Resistance               |                                 | 0.45                     | 0.82                     | 1.30                     | MΩ    |  |

| OVER-VOLTAC          | GE PROTECTION (OVP)                   |                                 |                          | •                        |                          |       |  |

| V <sub>TH-OVP</sub>  | OVP OVLO Threshold                    | OVP Increasing                  | 1.185                    | 1.240                    | 1.285                    | V     |  |

| I <sub>HYS-OVP</sub> | OVP Hysteresis Source<br>Current      | OVP Active (high)               | 13                       | 20                       | 27                       | μA    |  |

| ERROR AMPLI          | FIER                                  |                                 |                          |                          |                          |       |  |

| V <sub>CSH</sub>     | CSH Reference Voltage                 | With Respect to GND             | 1.210                    | 1.235                    | 1.260                    | V     |  |

|                      | Error Amplifier Input Bias<br>Current |                                 | -0.6                     | 0                        | 0.6                      | μA    |  |

|                      | COMP Sink / Source Current            |                                 | 17                       | 26                       | 35                       |       |  |

|                      | Transconductance                      |                                 |                          | 100                      |                          | μA/V  |  |

|                      | Linear Input Range                    | (Note 7)                        |                          | ±125                     |                          | mV    |  |

|                      | Transconductance<br>Bandwidth         | -6dB Unloaded Response (Note 7) |                          | 1.0                      |                          | MHz   |  |

| Symbol。<br>查询"                       | LM3424 <sup>Parameter</sup>                      | Conditions                                                      |                                                        | Min<br>( <i>Note 5</i> ) | Typ<br>( <i>Note 6</i> ) | Max<br>( <i>Note 5</i> ) | Units      |  |

|--------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------|--------------------------|--------------------------|--------------------------|------------|--|

| OSCILLATOR (I                        | RT)                                              |                                                                 |                                                        |                          |                          |                          |            |  |

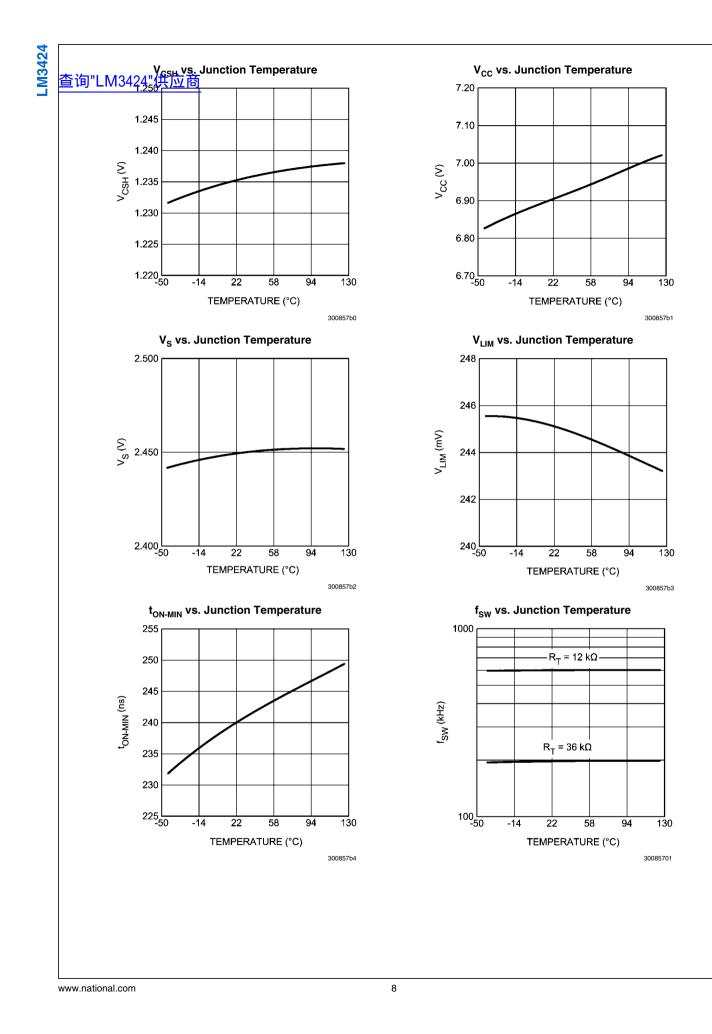

| f <sub>sw</sub>                      | Switching Frequency                              | $R_T = 36 \text{ k}\Omega$                                      |                                                        | 164                      | 207                      | 250                      |            |  |

|                                      |                                                  | R <sub>T</sub> = 12 kΩ                                          |                                                        | 525                      | 597                      | 669                      | kHz        |  |

| V <sub>RT-SYNC</sub>                 | Sync Threshold                                   |                                                                 |                                                        |                          | 3.5                      |                          | V          |  |

| PWM COMPARA                          |                                                  |                                                                 |                                                        |                          |                          |                          |            |  |

| V <sub>CP-BASE</sub>                 | COMP to PWM Offset - No                          |                                                                 |                                                        |                          |                          |                          |            |  |

| CP-BASE                              | Slope Compensation                               |                                                                 |                                                        | 750                      | 900                      | 1050                     | mV         |  |

| SLOPE COMPE                          | NSATION (SLOPE)                                  |                                                                 |                                                        |                          |                          |                          |            |  |

| ΔV <sub>CP</sub>                     | Slope Compensation                               | Additional C                                                    | OMP to PWM Offset -                                    |                          |                          |                          |            |  |

| CP                                   | Amplitude                                        | SLOPE sink                                                      |                                                        |                          | 85                       |                          | mV         |  |

| CURRENT LIMI                         | T (IS)                                           |                                                                 |                                                        |                          |                          |                          |            |  |

| V <sub>LIM</sub>                     | Current Limit Threshold                          |                                                                 |                                                        | 215                      | 245                      | 275                      | mV         |  |

| LIW                                  | V <sub>LIM</sub> Delay to Output                 |                                                                 |                                                        |                          | 35                       | 75                       |            |  |

| t                                    | Leading Edge Blanking Time                       |                                                                 |                                                        | 140                      | 240                      | 340                      | ns         |  |

| t <sub>on-min</sub><br>HIGH SIDE TRA | INSCONDUCTANCE AMPLIFI                           | FR                                                              |                                                        | 140                      | 240                      | 570                      |            |  |

| INGI SIDE IRA                        | Input Bias Current                               |                                                                 |                                                        |                          | 10                       |                          | μA         |  |

|                                      | Transconductance                                 |                                                                 |                                                        | 20                       | 10                       |                          | μA<br>mA/V |  |

|                                      |                                                  |                                                                 |                                                        | -1.5                     |                          | 1.5                      |            |  |

|                                      | Input Offset Current                             |                                                                 |                                                        |                          | 0                        |                          | μA<br>m\/  |  |

|                                      | Input Offset Voltage                             | 1 400                                                           |                                                        | -5                       | 0                        | 5                        | mV         |  |

|                                      | Transconductance<br>Bandwidth                    | I <sub>CSH</sub> = 100 μ                                        | IA ( <i>Note 7</i> )                                   |                          | 500                      |                          | kHz        |  |

| GATE DRIVER (                        |                                                  |                                                                 |                                                        |                          |                          |                          |            |  |

| R <sub>SRC-GATE</sub>                | GATE Sourcing Resistance                         | GATE = Hig                                                      | h                                                      |                          | 2.0                      | 6.0                      | 0          |  |

| R <sub>SNK-GATE</sub>                | GATE Sinking Resistance                          | GATE = Lov                                                      | V                                                      |                          | 1.3                      | 4.5                      | Ω          |  |

|                                      | GE LOCKOUT and DIM INPU                          | T (nDIM)                                                        |                                                        |                          |                          |                          |            |  |

| V <sub>TH-nDIM</sub>                 | nDIM / UVLO Threshold                            |                                                                 |                                                        | 1.185                    | 1.240                    | 1.285                    | V          |  |

| I <sub>HYS-nDIM</sub>                | nDIM Hysteresis Current                          |                                                                 |                                                        | 13                       | 20                       | 27                       | μA         |  |

| DIM DRIVER (D                        |                                                  |                                                                 |                                                        |                          |                          |                          |            |  |

| R <sub>SRC-DDRV</sub>                | DDRV Sourcing Resistance                         | DDRV = Hig                                                      | ıh                                                     |                          | 13.5                     | 30.0                     |            |  |

|                                      | DDRV Sinking Resistance                          | DDRV = Lov                                                      |                                                        |                          | 3.5                      | 10.0                     | Ω          |  |

| R <sub>SNK-DDRV</sub>                |                                                  |                                                                 | <i></i>                                                |                          | 700                      | 10.0                     |            |  |

|                                      | nDIM rising to DDRV rising                       |                                                                 |                                                        |                          |                          |                          | ns         |  |

| COLT-STADT (                         | nDIM rising to DDRV falling                      |                                                                 |                                                        |                          | 360                      |                          |            |  |

| SOFT-START (S                        |                                                  | 1                                                               |                                                        |                          | 10                       |                          |            |  |

|                                      | Soft-start current                               |                                                                 |                                                        |                          | 10                       |                          | μA         |  |

| THERMAL CON                          |                                                  |                                                                 |                                                        | 1                        |                          | I                        |            |  |

| V <sub>S</sub>                       | V <sub>S</sub> Voltage                           | I <sub>VS</sub> = 0A                                            |                                                        | 2.40                     | 2.45                     | 2.50                     | V          |  |

|                                      |                                                  | I <sub>VS</sub> = 1 mA                                          |                                                        |                          |                          |                          |            |  |

|                                      | TREF input bias current                          | $V_{\text{TREF}} = 1.5^{\circ}$<br>$V_{\text{TSENSE}} = 1$      |                                                        |                          | 0.1                      |                          |            |  |

|                                      | TSENSE Input Bias Current                        | V <sub>TREF</sub> = 1.5 <sup>v</sup><br>V <sub>TSENSE</sub> = 1 | V                                                      |                          | 0.1                      |                          |            |  |

| I <sub>TGAIN-MAX</sub>               | TGAIN Maximum Sourcing<br>Current                | V <sub>TGAIN</sub> = 2V                                         |                                                        | 200                      | 600                      |                          |            |  |

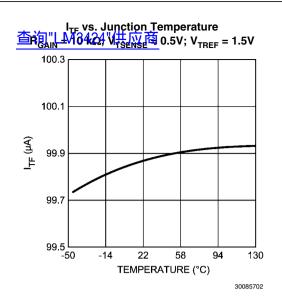

| I <sub>TF</sub>                      | CSH Current with High-side<br>Amplifier Disabled | R <sub>TGAIN</sub> = 10<br>kΩ                                   | V <sub>TREF</sub> = 1.5V<br>V <sub>TSENSE</sub> = 0.5V |                          | 100                      |                          | μA         |  |

|                                      |                                                  | 1.22                                                            | $V_{\text{TREF}} = 1.5V$<br>$V_{\text{TSENSE}} = 1.4V$ |                          | 10                       |                          |            |  |

|                                      |                                                  |                                                                 | TSENSE - 1.4V                                          | 1                        |                          |                          |            |  |

| 查询 <sup>Symba</sup> | 。<br>424"供应商 <sup>Parameter</sup> | Conditions            | Min<br>( <i>Note 5</i> ) | Typ<br>( <i>Note 6</i> ) | Max<br>( <i>Note 5</i> ) | Units |

|---------------------|-----------------------------------|-----------------------|--------------------------|--------------------------|--------------------------|-------|

| THERMAL             | SHUTDOWN                          |                       |                          |                          |                          |       |

| T <sub>SD</sub>     | Thermal Shutdown<br>Threshold     | (Note 7)              |                          | 165                      | °C                       |       |

| T <sub>HYS</sub>    | Thermal Shutdown<br>Hysteresis    | (Note 7)              |                          | 25                       |                          | °C    |

| THERMAL             | RESISTANCE                        |                       |                          |                          |                          |       |

| θ <sub>JA</sub>     | Junction to Ambient               | 20L TSSOP EP (Note 2) |                          | 34                       |                          | °C/W  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Operating Ratings is not implied. The recommended Operating Ratings indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are with respect to the potential at the GND pin, unless otherwise specified.

**Note 2:** Junction-to-ambient thermal resistance is highly board-layout dependent. The numbers listed in the table are given for a reference layout wherein the 20L TSSOP EP package has its DAP pad populated with 9 vias. In applications where high maximum power dissipation exists, namely driving a large MosFET at high switching frequency from a high input voltage, special care must be paid to thermal dissipation issues during board design. In high-power dissipation applications, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{A-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125^{\circ}C$ ), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to ambient thermal resistance of the package in the application ( $\theta_{J,A}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{J,A} \times P_{D-MAX})$ . In most applications there is little need for the full power dissipation capability of this advanced package. Under these circumstances, no vias would be required and the thermal resistance with a straight line to get a thermal resistance for any number of vias in between these two limits.

Note 3: Refer to National's packaging website for more detailed information and mounting techniques. http://www.national.com/analog/packaging/

Note 4: Human Body Model, applicable std. JESD22-A114-C.

Note 5: All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 6: Typical numbers are at 25°C and represent the most likely norm.

Note 7: These electrical parameters are guaranteed by design, and are not verified by test.

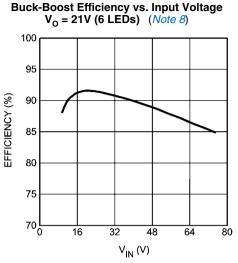

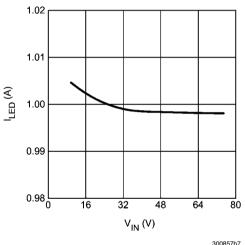

Note 8: The measurements were made using the standard buck-boost evaluation board from AN-1967.

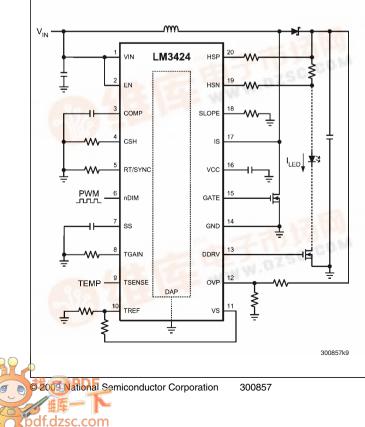

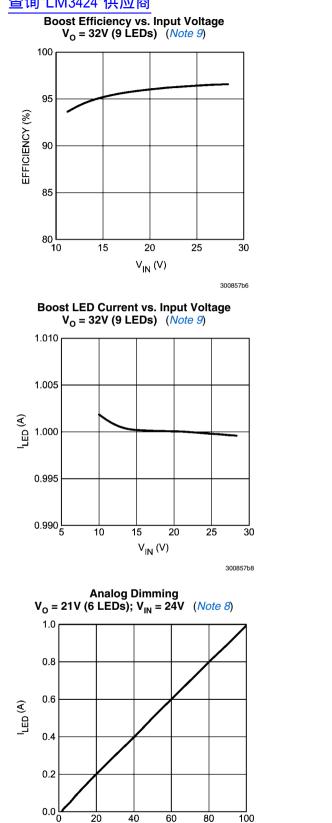

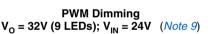

Note 9: The measurements were made using the standard boost evaluation board from AN-1969.

Ι<sub>CSH</sub> (μΑ)

300857b9

Ideal Thermal Foldback - Varied Breakpoint  $R_{REF1} = R_{REF2} = 49.9 \text{ k}\Omega; R_{GAIN} = 10 \text{ k}\Omega$

## 2727 查**静<sup>1</sup>20%。424%供应商**

## **Theory of Operation**

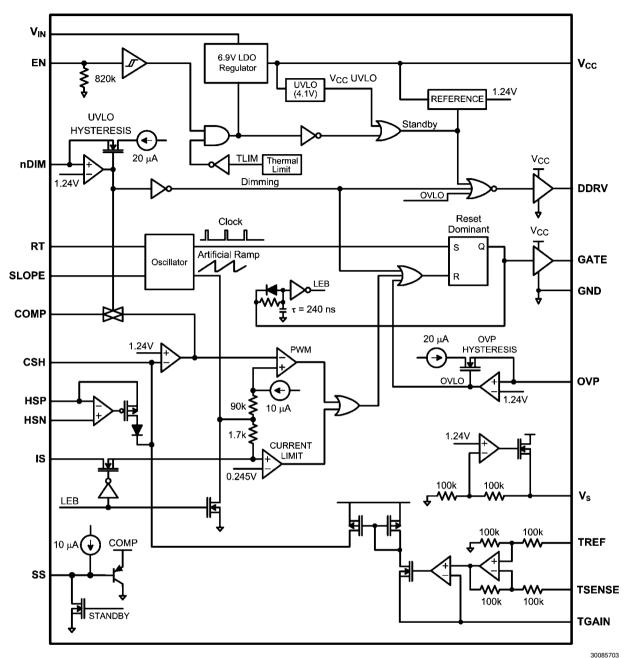

The LM3424 is an N-channel MosFET (NFET) controller for buck, boost and buck-boost current regulators which are ideal for driving LED loads. The controller has wide input voltage range allowing for regulation of a variety of LED loads. The high-side differential current sense, with low adjustable threshold voltage, provides an excellent method for regulating output current while maintaining high system efficiency. The LM3424 uses peak current mode control providing good noise immunity and an inherent cycle-by-cycle current limit. The adjustable current sense threshold provides the capability to amplitude (analog) dim the LED current and the thermal foldback circuitry allows for precise temperature management of the LEDs. Tthe output enable/disable function coupled with an internal dimming drive circuit provides high speed PWM dimming through the use of an external MosFET placed at the LED load. When designing, the maximum attainable LED current is not internally limited because the LM3424 is a controller. Instead it is a function of the system operating point, component choices, and switching frequency allowing the LM3424 to easily provide constant currents up to 5A. This simple controller contains all the features necessary to implement a high efficiency versatile LED driver.

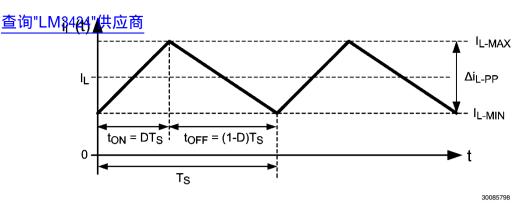

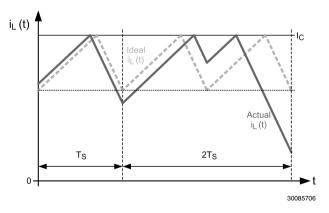

FIGURE 1. Ideal CCM Regulator Inductor Current i, (t)

#### **CURRENT REGULATORS**

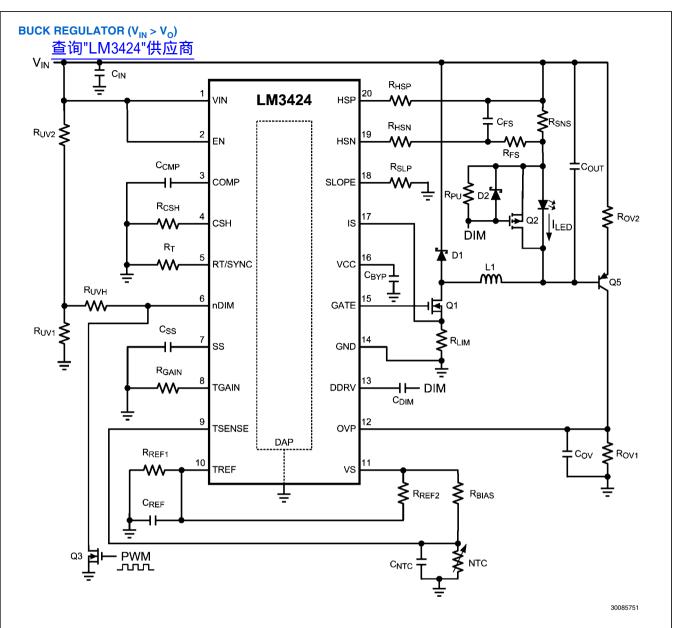

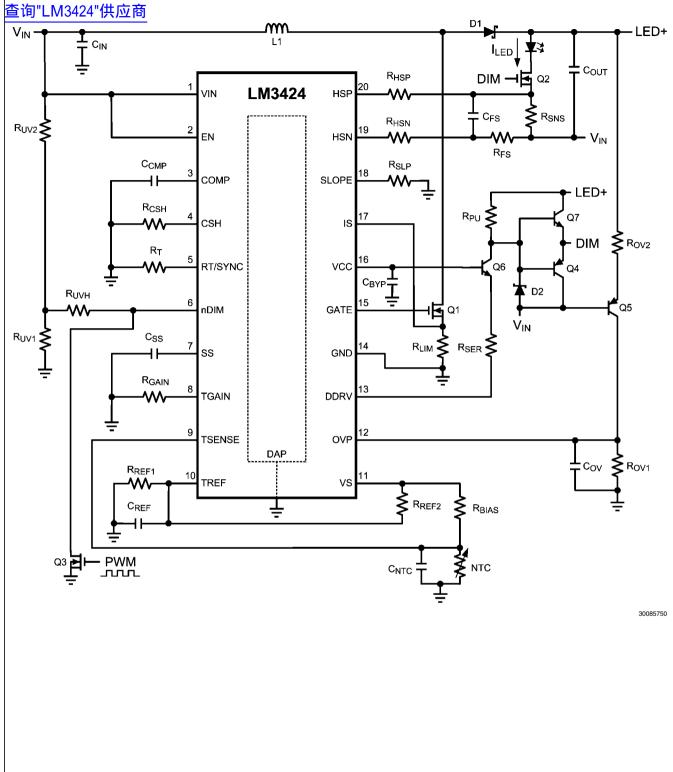

Current regulators can be designed to accomplish three basic functions: buck, boost, and buck-boost. All three topologies in their most basic form contain a main switching MosFET, a recirculating diode, an inductor and capacitors. The LM3424 is designed to drive a ground referenced NFET which is perfect for a standard boost regulator. Buck and buck-boost regulators, on the other hand, usually have a high-side switch. When driving an LED load, a ground referenced load is often not necessary, therefore a ground referenced switch can be used to drive a floating load instead. The LM3424 can then be used to drive all three basic topologies as shown in the *Basic Topology Schematics* section. Other topologies such as the SEPIC and flyback converter (both derivatives of the buck-boost) can be implemented as well.

Looking at the buck-boost design, the basic operation of a current regulator can be analyzed. During the time that the NFET (Q1) is turned on  $(t_{ON})$ , the input voltage source stores energy in the inductor (L1) while the output capacitor (C<sub>O</sub>) provides energy to the LED load. When Q1 is turned off ( $t_{OFF}$ ), the re-circulating diode (D1) becomes forward biased and L1 provides energy to both C<sub>O</sub> and the LED load. *Figure 1* shows the inductor current ( $i_L(t)$ ) waveform for a regulator operating in CCM.

The average output LED current ( $I_{LED}$ ) is proportional to the average inductor current ( $I_L$ ), therefore if  $I_L$  is tightly controlled,  $I_{LED}$  will be well regulated. As the system changes input voltage or output voltage, the ideal duty cycle (D) is varied to regulate  $I_L$  and ultimately  $I_{LED}$ . For any current regulator, D is a function of the conversion ratio:

Buck

Boost

$$D = \frac{V_{\rm O} - V_{\rm IN}}{V_{\rm O}}$$

$D = \frac{V_0}{V_{o}}$

**Buck-boost**

$$D = \frac{V_0}{V_0 + V_{IN}}$$

#### PEAK CURRENT MODE CONTROL

Peak current mode control is used by the LM3424 to regulate the average LED current through an array of HBLEDs. This method of control uses a series resistor in the LED path to sense LED current and can use either a series resistor in the MosFET path or the MosFET  $R_{DS-ON}$  for both cycle-by-cycle current limit and input voltage feed forward. The controller has a fixed switching frequency set by an internal programmable oscillator which means current mode instability can occur at duty cycles higher than 50%. To mitigate this standard problem, an aritifical ramp is added to the control signal internally. The slope of this ramp is programmable to allow for a wider range of component choices for a given design. A detailed explanation of this control method is presented in the following sections.

#### SWITCHING FREQUENCY

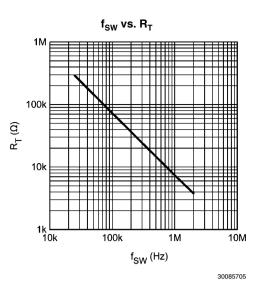

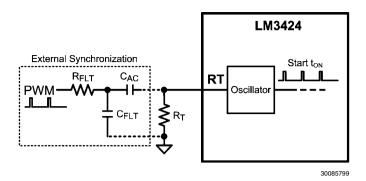

The switching frequency of the LM3424 is programmed using an external resistor ( $R_T$ ) connected from the RT pin to GND as shown in *Figure 2*.

Alternatively, an external PWM signal can be applied to the RT pin through a filter ( $R_{FLT}$  and  $C_{FLT}$ ) and an AC coupling capacitor ( $C_{AC}$ ) to synchronize the part to an external clock as shown in *Figure 2*. If the external PWM signal is applied at a frequency higher than the base frequency set by the  $R_T$  resistor, the internal oscillator is bypassed and the switching frequency becomes the synchronized frequency. The external synchronization signal should have a pulse width of 100ns, an amplitude between 3V and 6V, and be AC coupled to the RT pin with a ceramic capacitor ( $C_{AC} = 100$  pF). A 10MHz RC filter ( $R_{FLT} = 150\Omega$  and  $C_{FLT} = 100$  pF) should be placed between the PWM signal and  $C_{AC}$  to eliminate unwanted high frequency noise from coupling into the RT pin. The switching frequency is defined:

$$f_{SW} = \frac{1}{1.40e^{-10} \text{ x } \text{R}_{\text{T}} - 1.95e^{-8}}$$

See the Typical Performance Characteristics section for a plot of  $\mathsf{R}_{\mathsf{T}}$  vs.  $\mathsf{f}_{\mathsf{SW}}.$

## 查询"LM3424"供应商

**FIGURE 2. Timing Circuitry**

#### AVERAGE LED CURRENT

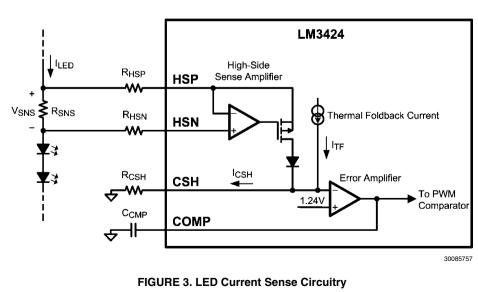

To first understand how the LM3424 regulates LED current, the thermal foldback functionality will be ignored. Figure 3 shows the physical implementation of the LED current sense circuitry assuming the thermal foldback circuitry is a simple current source which, for now, will be set to zero ( $I_{TF} = 0A$ ). The LM3424 uses an external current sense resistor (R<sub>SNS</sub>) placed in series with the LED load to convert the LED current  $(\mathrm{I}_{\mathrm{LED}})$  into a voltage (V\_{SNS}). The HSP and HSN pins are the inputs to the high-side sense amplifier which are forced to be equal potential (V<sub>HSP</sub>=V<sub>HSN</sub>) through negative feedback. Because of this, the  $V_{SNS}$  voltage is forced across  $R_{HSP}$  which generates a current that is summed with the thermal foldback current  $(I_{TF})$  to generate the signal current  $(I_{CSH})$  which flows out of the CSH pin and through the  $\mathrm{R}_{\mathrm{CSH}}$  resistor. The error amplifier will regulate the CSH pin to 1.24V and assuming  $I_{TE} = 0A$ ,  $I_{CSH}$  can be calculated:

$$I_{CSH} = \frac{V_{SNS}}{R_{HSP}}$$

This means V<sub>SNS</sub> will be regulated as follows:

$$V_{SNS} = 1.24V \times \frac{R_{HSP}}{R_{CSH}}$$

ILED can then be calculated:

$$I_{LED} = \frac{V_{SNS}}{R_{SNS}} = \frac{1.24V}{R_{SNS}} \times \frac{R_{HSP}}{R_{CSH}}$$

The selection of the three resistors (R<sub>SNS</sub>, R<sub>CSH</sub>, and R<sub>HSP</sub>) is not arbitrary. For matching and noise performance, the suggested signal current I<sub>CSH</sub> is approximately 100 µA. This current does not flow in the LEDs and will not affect either the off-state LED current or the regulated LED current. I<sub>CSH</sub> can be above or below this value, but the high-side amplifier offset characteristics may be affected slightly. In addition, to minimize the effect of the high-side amplifier voltage offset on LED current accuracy, the minimum V<sub>SNS</sub> is suggested to be 50 mV. Finally, a resistor (R<sub>HSN</sub> = R<sub>HSP</sub>) should be placed in series with the HSN pin to cancel out the effects of the input bias current (~10 µA) of both inputs of the high-side sense amplifier.

Note that he CSH pin can also be used as a low-side current sense input regulated to 1.24V. The high-side sense amplifier is disabled if HSP and HSN are tied to GND.

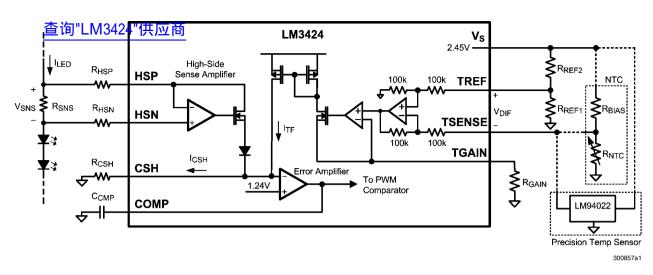

FIGURE 4. Thermal Foldback Circuitry

#### THERMAL FOLDBACK / ANALOG DIMMING

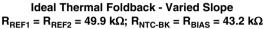

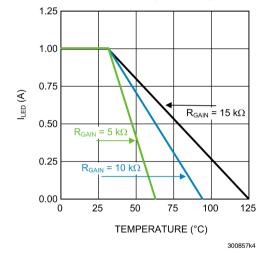

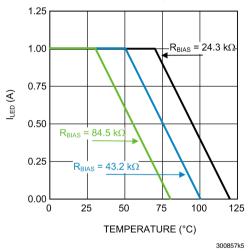

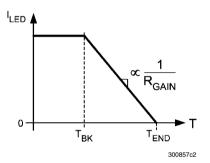

Thermal foldback is necessary in many applications due to the extreme temperatures created in LED environments. In general, two functions are necessary: a temperature breakpoint ( $T_{BK}$ ) after which the nominal operating current needs to be reduced, and a slope corresponding to the amount of LED current decrease per temperature increase as shown in *Figure 5*. The LM3424 allows the user to program both the breakpoint and slope of the thermal foldback profile.

FIGURE 5. Ideal Thermal Foldback Profile

Foldback is accomplished by adding current ( $I_{TF}$ ) to the CSH summing node. As more current is added, less current is needed from the high side amplifier and correspondingly, the LED current is regulated to a lower value. The final temperature ( $T_{END}$ ) is reached when  $I_{TF} = I_{CSH}$  causing no current to be needed from the high-side amplifier, yielding  $I_{LED} = 0A$ .

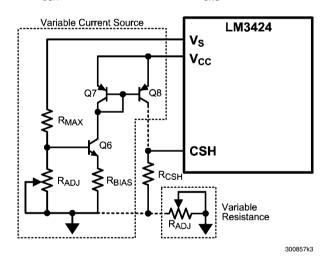

*Figure 4* shows how the thermal foldback circuitry is physically implemented in the system. I<sub>TF</sub> is set by placing a differential voltage ( $V_{DIF} = V_{TREF} - V_{TSENSE}$ ) across TSENSE and TREF.  $V_{TREF}$  can be set with a simple resistor divider ( $R_{REF1}$  and  $R_{REF2}$ ) supplied from the V<sub>S</sub> voltage reference (typical 2.45V).  $V_{TSENSE}$  is set with a temperature dependant voltage (as temperature increases, voltage should decrease).

An NTC thermistor is the most cost effective device used to sense temperature. As the temperature of the thermistor increases, its resistance decreases (albeit non-linearly). Usually, the NTC manufacturer's datasheet will detail the resistance-temperature characteristic of the thermistor. The thermistor will have a different resistance ( $R_{NTC}$ ) at each tem-

perature. The nominal resistance of an NTC is the resistance when the temperature is 25°C (R<sub>25</sub>) and in many datasheets this will be given a multiplier of 1. Then the resistance at a higher temperature will have a multiplier less than 1 (i.e. R<sub>85</sub> multiplier is 0.161 therefore R<sub>85</sub> = 0.161 x R<sub>25</sub>). Given a desired T<sub>BK</sub> and T<sub>END</sub>, the corresponding resistances at those temperatures (R<sub>NTC-BK</sub> and R<sub>NTC-END</sub>) can be found.

Using the NTC method, a resistor divider from V<sub>S</sub> can be implemented with a resistor connected between V<sub>S</sub> and TSENSE and the NTC thermistor placed at the desired location and connected from TSENSE to GND. This will ensure that the desired temperature-voltage characteristic occurs at TSENSE.

If a linear decrease over the foldback range is necessary, a precision temperature sensor such as the LM94022 can be used instead as shown in *Figure 4*. Either method can be used to set  $V_{\text{TSENSE}}$  according to the temperature. However, for the rest of this datasheet, the NTC method will be used for thermal foldback calculations.

During operation, if  $V_{DIF} < 0V$ , then the sensed temperature is less than  $T_{BK}$  and the differential sense amplifier will regulate its output to zero forcing  $I_{TF} = 0$ . This maintains the nominal LED current and no foldback is observed.

At T<sub>BK</sub>, V<sub>DIF</sub> = 0V exactly and I<sub>TF</sub> is still zero. Looking at the manufacturer's datasheet for the NTC thermistor, R<sub>NTC-BK</sub> can be obtained for the desired T<sub>BK</sub> and the voltage relationship at the breakpoint (V<sub>TSENSE-BK</sub> = V<sub>TREF</sub>) can be defined:

$$\frac{R_{REF1}}{R_{REF1} + R_{REF2}} = \frac{R_{NTC-BK}}{R_{NTC-BK} + R_{BIAS}}$$

A general rule of thumb is to set  $R_{REF1}$  =  $R_{REF2}$  simplifying the breakpoint relationship to  $R_{BIAS}$  =  $R_{NTC-BK}$ .

If  $V_{DIF} > 0V$  (temperature is above  $T_{BK}$ ), then the amplifier will regulate its output equal to the input forcing  $V_{DIF}$  across the resistor ( $R_{GAIN}$ ) connected from TGAIN to GND.  $R_{GAIN}$  ultimately sets the slope of the LED current decrease with respect to increasing temperature by changing  $I_{TE}$ :

$$I_{TF} = \frac{V_{TREF} - V_{TSENSE}}{R_{GAIN}}$$

If an analog temperature sensor such as the LM94022 is 有可以此时,我们的12月1日。 VIENSE will be the direct voltage output of the sensor.

Since the NTC is not usually local to the controller, a bypass capacitor ( $C_{NTC}$ ) is suggested from TSENSE to GND. If a capacitor is used at TSENSE, then a capacitor ( $C_{REF}$ ) of equal or greater value should be placed from TREF to GND in order to ensure the controller does not start-up in foldback. Alternatively, a smaller  $C_{REF}$  can be used to create a fade-up function at start-up (see *Application Information* section).

Thermal foldback is simply analog dimming according to a specific profile, therefore any method of controlling the differential voltage between TREF and TSENSE can be use to analog dim the LED current. The corresponding LED current for any  $V_{\text{DIF}} > 0V$  is defined:

$$I_{\text{LED}} = (I_{\text{CSH}} - I_{\text{TF}}) \times \left(\frac{R_{\text{HSP}}}{R_{\text{SNS}}}\right)$$

The CSH pin can also be used to analog dim the LED current by adjusting the current sense voltage (V<sub>SNS</sub>), similar to thermal foldback. There are several different methods to adjust V<sub>SNS</sub> using the CSH pin:

- 1. External variable resistance : Adjust a potentiometer placed in series with R<sub>CSH</sub> to vary V<sub>SNS</sub>.

- 2. External variable current source: Source current (0  $\mu A$  to  $I_{CSH})$  into the CSH pin to adjust  $V_{SNS}.$

FIGURE 6. Analog Dimming Circuitry

In general, analog dimming applications require a lower switching frequency to minimize the effect of the leading edge blanking circuit. As the LED current is reduced, the output voltage and the duty cycle decreases. Eventually, the minimum on-time is reached. The lower the switching frequency, the wider the linear dimming range. *Figure 6* shows how both CSH methods are physically implemented.

Method 1 uses an external potentiometer in the CSH path which is a simple addition to the existing circuitry. However, the LEDs cannot dim completely because there is always some resistance causing signal current to flow. This method is also susceptible to noise coupling at the CSH pin since the potentiometer increases the size of the signal current loop.

Method 2 provides a complete dimming range and better noise performance, though it is more complex. Like thermal foldback, it simply sources current into the CSH pin, decreasing the amount of signal current that is necessary. This method consists of a PNP current mirror and a bias network consisting of an NPN, 2 resistors and a potentiometer ( $R_{AD,J}$ ), where  $R_{AD,J}$  controls the amount of current sourced into the CSH pin. A higher resistance value will source more current into the CSH pin causing less regulated signal current through  $R_{HSP}$ , effectively dimming the LEDs. Q7 and Q8 should be a dual pair PNP for best matching and performance. The additional current ( $I_{ADD}$ ) sourced into the CSH pin causing less regulated signal current can be calculated:

$$I_{ADD} = \frac{\left(\frac{R_{ADJ} \times V_{REF}}{R_{ADJ} + R_{MAX}}\right) - V_{BE-Q6}}{R_{BIAS}}$$

The corresponding I<sub>LED</sub> for a specific I<sub>ADD</sub> is:

$$I_{LED} = (I_{CSH} - I_{ADD}) x \left(\frac{R_{HSP}}{R_{SNS}}\right)$$

#### THERMAL SHUTDOWN

The LM3424 includes thermal shutdown. If the die temperature reaches approximately 165°C the device will shut down (GATE pin low), until it reaches approximately 140°C where it turns on again.

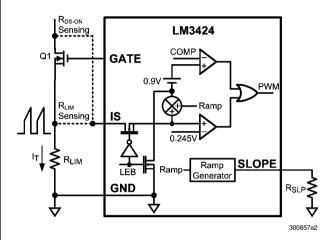

#### **CURRENT SENSE/CURRENT LIMIT**

FIGURE 7. Current Sense / Current Limit Circuitry

There are two possible methods to sense the transistor current. The  $R_{DS-ON}$  of the main power MosFET can be used as the current sense resistance because the IS pin was designed to withstand the high voltages present on the drain when the MosFET is in the off state. Alternatively, a sense resistor located in the source of the MosFET may be used for current sensing, however a low inductance (ESL) type is suggested. The cycle-by-cycle current limit (I<sub>LIM</sub>) can be calculated using either method as the limiting resistance (R<sub>LIM</sub>):

$$I_{\text{LIM}} = \frac{245 \text{ mV}}{R_{\text{LIM}}}$$

In general, the external series resistor allows for more design flexibility, however it is important to ensure all of the noise sensitive low power ground connections are connected together local to the controller and a single connection is made to GND.

#### **SLOPE COMPENSATION**

The LM3424 has programmable slope compensation in order to provide stability over a wide range of operating conditions. Without slope compensation, a well-known condition called current mode instability (or sub-harmonic oscillation) can result if there is a perturbation of the MosFET current sense voltage at the IS pin, due to noise or a some type of transient. Through a mathematical / geometrical analysis of the inductor current (I<sub>L</sub>) and the corresponding control current (I<sub>C</sub>, it can be shown that if D < 0.5, the effect of the perturbation will decrease each switching cycle and the system will remain stable. However, if D > 0.5 then the perturbation will grow as shown in *Figure 8*, eventually causing a "period doubling" effect where the effect of the perturbation remains, yielding current mode instability.

Looking at *Figure 7*, the positive PWM comparator input is the IS voltage, a mirror of  $I_L$  during  $t_{ON}$ , plus a typical 900 mV offset. The negative input of the PWM comparator is the COMP pin which is proportional to  $I_C$ , the threshold at which the main MosFET (Q1) is turned off.

The LM3424 mitigates current mode instability by implementing an aritifical ramp (commonly called slope compensation) which is summed with the sensed MosFET current at the IS pin as shown in *Figure 7*. This combined signal is compared to the COMP pin to generate the PWM signal. An increase in the ramp that is added to the sense voltage will increase the maximum achievable duty cycle. It should be noted that as the artificial ramp is increased more and more, the control method approaches standard voltage mode control and the benefits of current mode control are reduced.

To program the slope compensation, an external resistor,  $R_{SLP}$ , is connected from SLOPE to GND. This sets the slope of the artificial ramp that is added to the MosFET current sense voltage. A smaller  $R_{SLP}$  value will increase the slope of the added ramp. A simple calculation is suggested to ensure any duty cycle is attainable while preventing the addition of excessive ramp. This method requires the artifical ramp slope (M<sub>A</sub>) to be equal to half the inductor slope during  $t_{OFF}$ :

$$M_{A} = \frac{7.5 e^{12}}{R_{T} \times R_{SLP} \times R_{SNS}} = \frac{V_{O}}{2 \times L1}$$

FIGURE 8. "Period Doubling" due to Current Mode Instability

#### CONTROL LOOP COMPENSATION

**The second seco**

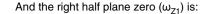

A buck-boost regulator will be used as an example case. See the *Design Guide* section for compensation of all topologies. The uncompensated loop gain for a buck-boost regulator is given by the following equation:

$$T_{U} = T_{U0} \times \frac{\left(1 - \frac{s}{\omega_{Z1}}\right)}{\left(1 + \frac{s}{\omega_{P1}}\right)}$$

Where the uncompensated DC loop gain of the system is described as:

$$T_{U0} = \frac{D' x \, 500V x \, R_{CSH} \, x \, R_{SNS}}{(1+D) x \, R_{HSP} \, x \, R_{LIM}} = \frac{D' \, x \, 620V}{(1+D) x \, I_{LED} \, x \, R_{LIM}}$$

And the output pole  $(\omega_{P1})$  is approximated:

$$\omega_{\rm P1} = \frac{1+D}{r_{\rm D} \times C_{\rm O}}$$

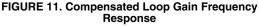

FIGURE 9. Uncompensated Loop Gain Frequency Response

*Figure 9* shows the uncompensated loop gain in a worst-case scenario when the RHP zero is below the output pole. This occurs at high duty cycles when the regulator is trying to boost the output voltage significantly. The RHP zero adds 20dB/ decade of gain while loosing 45°/decade of phase which places the crossover frequency (when the gain is zero dB) extremely high because the gain only starts falling again due to the high frequency pole (not modeled or shown in figure). The phase will be below -180° at the crossover frequency which means there is no phase margin (180° + phase at crossover frequency) causing system instability. Even if the output pole is below the RHP zero, the phase will still reach -180° before the crossover frequency in most cases yielding instability.

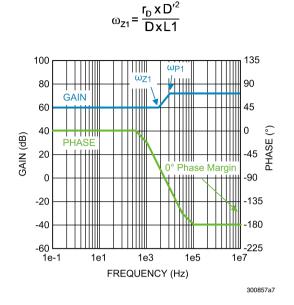

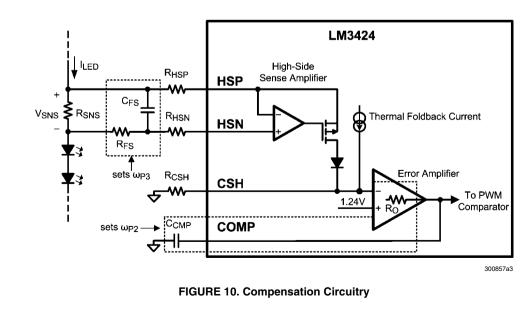

To mitigate this problem, a compensator should be designed to give the problem of the problem of the conservation of the cons

$$\omega_{\rm P2} = \frac{1}{5e^6\Omega \times C_{\rm CMP}}$$

It may also be necessary to add one final pole at least one decade above the crossover frequency to attenuate switching noise and, in some cases, provide better gain margin. This pole can be placed across  $R_{SNS}$  to filter the ESL of the sense resistor at the same time. *Figure 10* shows how the compensation is physically implemented in the system.

The high frequency pole ( $\omega_{P3}$ ) can be calculated:

$$\omega_{P3} = \frac{1}{R_{FS} \times C_{FS}}$$

The total system transfer function becomes:

$$T = T_{U0} x \frac{\left(1 - \frac{s}{\omega_{Z1}}\right)}{\left(1 + \frac{s}{\omega_{P1}}\right) x \left(1 + \frac{s}{\omega_{P2}}\right) x \left(1 + \frac{s}{\omega_{P3}}\right)}$$

The resulting compensated loop gain frequency response shown in *Figure 11* indicates that the system has adequate phase margin (above 45°) if the dominant compensation pole is placed low enough, ensuring stability:

FIGURE 12. Start-up Waveforms

#### **START-UP REGULATOR and SOFT-START**

The LM3424 includes a high voltage, low dropout bias regulator. When power is applied, the regulator is enabled and sources current into an external capacitor (C<sub>BYP</sub>) connected to the V<sub>CC</sub> pin. The recommended bypass capacitance for the V<sub>CC</sub> regulator is 2.2 µF to 3.3 µF. The output of the V<sub>CC</sub> regulator is monitored by an internal UVLO circuit that protects the device from attempting to operate with insufficient supply voltage and the supply is also internally current limited.

The LM3424 also has programmable soft-start, set by an external capacitor ( $C_{SS}$ ), connected from SS to GND. For  $C_{SS}$  to affect start-up,  $C_{REF} > C_{NTC}$  must be maintained so that the converter does not start in foldback mode. *Figure 12* shows the typical start-up waveforms for the LM3424 assuming  $C_{REF} > C_{NTC}$ .

First,  $C_{BYP}$  is charged to be above  $V_{CC}$  UVLO threshold (~4.2V). The  $C_{VCC}$  charging time ( $t_{VCC}$ ) can be estimated as:

$$t_{VCC} = \frac{4.2V}{25 \text{ mA}} \text{ x } C_{BYP} = 168\Omega \text{ x } C_{BYP}$$

Assuming there is no  $C_{\rm SS}$  or if  $C_{\rm SS}$  is less than 40% of  $C_{\rm CMP}$ ,  $C_{\rm CMP}$  is then charged to 0.9V over the charging time  $(t_{\rm CMP})$  which can be estimated as:

$$t_{CMP} = \frac{0.9V}{25 \,\mu A} \times C_{CMP} = 36 \,k\Omega \times C_{CMP}$$

Once  $C_{CMP} = 0.9V$ , the part starts switching to charge  $C_O$  until the LED current is in regulation. The  $C_O$  charging time ( $t_{CO}$ ) can be roughly estimated as:

$$\mathbf{t}_{\rm CO} = \mathbf{C}_{\rm O} \, \mathbf{x} \, \frac{\mathbf{V}_{\rm O}}{\mathbf{I}_{\rm LED}}$$

If  $C_{SS}$  is greater than 40% of  $C_{CMP}$ , the compensation capacitor will only charge to 0.7V over a smaller  $C_{CMP}$  charging time  $(t_{CMP-SS})$  which can be estimated as:

$$t_{CMP-SS} = \frac{0.70V}{25\,\mu A} \times C_{CMP} = 28 \,k\Omega \times C_{CMP}$$

Then COMP will clamp to SS, forcing COMP to rise (the last

$$t_{\rm SS} = \frac{0.2V}{10\,\mu A} \times C_{\rm SS} = 20 \ k\Omega \times C_{\rm SS}$$

The system start-up time ( $t_{SU}$  or  $t_{SU-SS}$ ) is defined as:

$C_{SS} < 0.4 \text{ x } C_{CMP}$

$$t_{SU} = t_{VCC} + t_{CMP} + t_{CO}$$

$C_{SS} > 0.4 \times C_{CMP}$

$$t_{SU-SS} = t_{VCC} + t_{CMP-SS} + t_{SS} + t_{CC}$$

As a general rule of thumb, standard smooth startup operation can be achieved with  $\rm C_{SS}=C_{CMP}.$

#### **OVER-VOLTAGE LOCKOUT (OVLO)**

FIGURE 13. Over-Voltage Protection Circuitry

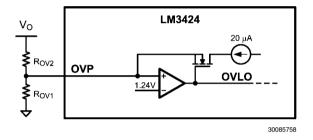

The LM3424 can be configured to detect an output (or input) over-voltage condition via the OVP pin. The pin features a precision 1.24V threshold with 20  $\mu$ A (typical) of hysteresis current as shown in *Figure 13*. When the OVLO threshold is exceeded, the GATE pin is immediately pulled low and a 20  $\mu$ A current source provides hysteresis to the lower threshold of the OVLO hysteretic band.

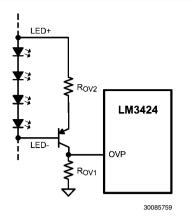

If the LEDs are referenced to a potential other than ground (floating), as in the buck-boost and buck configuration, the output voltage ( $V_O$ ) should be sensed and translated to ground by using a single PNP as shown in *Figure 14*.

The over-voltage turn-off threshold ( $V_{TURN-OFF}$ ) is defined:

#### **Ground Referenced**

$$V_{\text{TURN-OFF}} = 1.24 \text{Vx} \left( \frac{\text{R}_{\text{OV1}} + \text{R}_{\text{OV2}}}{\text{R}_{\text{OV1}}} \right)$$

Floating

$$V_{\text{TURN-OFF}} = 1.24 V x \left( \frac{0.5 x R_{\text{OV1}} + R_{\text{OV2}}}{R_{\text{OV1}}} \right)$$

In the ground referenced configuration, the voltage across  $R_{OV2}$  is  $V_O$  - 1.24V whereas in the floating configuration it is  $V_O$  - 620 mV where 620 mV approximates  $V_{BE}$  of the PNP. The over-voltage hysteresis ( $V_{HYSO}$ ) is defined:

$$V_{HYSO} = 20 \,\mu A \, x \, R_{OV2}$$

FIGURE 14. Floating Output OVP Circuitry

#### **INPUT UNDER-VOLTAGE LOCKOUT (UVLO)**

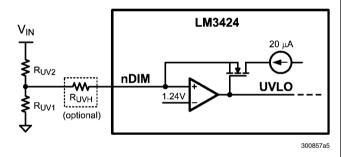

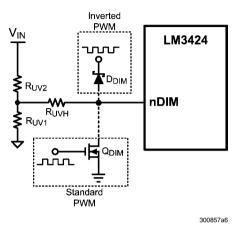

The nDIM pin is a dual-function input that features an accurate 1.24V threshold with programmable hysteresis as shown in *Figure 15*. This pin functions as both the PWM dimming input for the LEDs and as a  $V_{IN}$  UVLO. When the pin voltage rises and exceeds the 1.24V threshold, 20  $\mu$ A (typical) of current is driven out of the nDIM pin into the resistor divider providing programmable hysteresis.

#### FIGURE 15. UVLO Circuit

When using the nDIM pin for UVLO and PWM dimming concurrently, the UVLO circuit can have an extra series resistor to set the hysteresis. This allows the standard resistor divider to have smaller resistor values minimizing PWM delays due to a pull-down MosFET at the nDIM pin (see *PWM Dimming* section). In general, at least 3V of hysteresis is preferable when PWM dimming, if operating near the UVLO threshold. The turn-on threshold ( $V_{TURN-ON}$ ) is defined as follows:

$$V_{\text{TURN ON}} = 1.24 \text{V} \text{x} \left( \frac{\text{R}_{\text{UV1}} + \text{R}_{\text{UV2}}}{\text{R}_{\text{UV1}}} \right)$$

The hysteresis ( $V_{HYS}$ ) is defined as follows:

UVLO only

$$V_{HYS} = 20 \,\mu A \, x \, R_{UV2}$$

#### **PWM dimming and UVLO**

$$V_{HYS} = 20 \,\mu A \, x \left( R_{UV2} + \frac{R_{UVH} \, x \left( R_{UV1} + R_{UV2} \right)}{R_{UV1}} \right)^2$$

#### **PWM DIMMING**

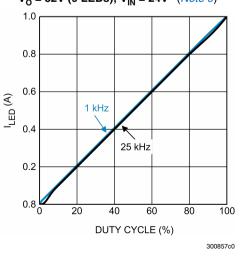

The action of the the main NFET and the dimming FET (dim-FET). The brightness of the LEDs can be varied by modulating the duty cycle of this signal. LED brightness is approximately proportional to the PWM signal duty cycle, (i.e. 30% duty cycle ~ 30% LED brightness). This function can be ignored if PWM dimming is not required by using nDIM solely as a V<sub>IN</sub> UVLO input as described in the *Input Under-Voltage Lockout* section or by tying it directly to V<sub>CC</sub> or V<sub>IN</sub>.

FIGURE 16. PWM Dimming Circuit

Figure 16 shows how the PWM signal is applied to nDIM:

- Connect the dimming MosFET (Q<sub>DIM</sub>) with the drain to the nDIM pin and the source to GND. Apply an external logic-level PWM signal to the gate of Q<sub>DIM</sub>.

- Connect the anode of a Schottky diode (D<sub>DIM</sub>) to the nDIM pin. Apply an inverted external logic-level PWM signal to the cathode of the same diode.

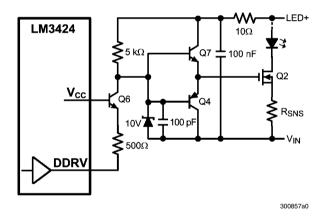

The DDRV pin is a PWM output that follows the nDIM PWM input signal. When the nDIM pin rises, the DDRV pin rises and the PWM latch reset signal is removed allowing the main MosFET Q1 to turn on at the beginning of the next clock set pulse. In boost and buck-boost topologies, the DDRV pin is used to control a N-channel MosFET placed in series with the LED load, while it would control a P-channel MosFET in parallel with the load for a buck topology.

The series dimFET will open the LED load, when nDIM is low, effectively speeding up the rise and fall times of the LED current. Without any dimFET, the rise and fall times are limited by the inductor slew rate and dimming frequencies above 1 kHz are impractical. Using the series dimFET, dimming frequencies up to 30 kHz are achievable. With a parallel dimFET (buck topology), even higher dimming frequencies are achievable.

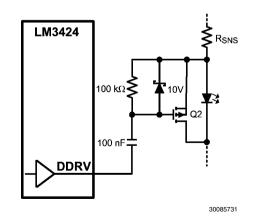

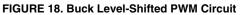

When using the PWM functionality in a boost regulator, the PWM signal drives a ground referenced FET. However, with buck-boost and buck topologies, level shifting circuitry is necessary to translate the PWM dim signal to the floating dimFET as shown in *Figure 17* and *Figure 18*.

When using a series dimFET to PWM dim the LED current, more output capacitance is always better. A general rule of thumb is to use a minimum of  $40 \,\mu$ F when PWM dimming. For most applications, this will provide adequate energy storage at the output when the dimFET turns off and opens the LED load. Then when the dimFET is turned back on, the capacitance helps source current into the load, improving the LED current rise time.

A minimum on-time must be maintained in order for PWM dimming to operate in the linear region of its transfer function. Because the controller is disabled during dimming, the PWM pulse must be long enough such that the energy intercepted from the input is greater than or equal to the energy being put into the LEDs. For boost and buck-boost regulators, the minimum dimming pulse length in seconds ( $t_{PULSE}$ ) is:

$$t_{\text{PULSE}} = \frac{2 \times I_{\text{LED}} \times V_{\text{O}} \times L^2}{V_{\text{IN}}^2}$$

Even maintaining a dimming pulse greater than  $t_{PULSE}$ , preserving linearity at low dimming duty cycles is difficult. Several modifications are suggested for applications requiring low dimming duty cycles. Since nDIM rising releases the latch but does not trigger the on-time specifically, there will be an effective jitter on the rising edge of the LED current. This jitter can be easily removed by tying the PWM input signal through the synchronization network at the RT pin (shown in *Figure 2*), forcing the on-time to synchronize with the nDIM pulse.

The second helpful modification is to remove the C<sub>FS</sub> capacitor and R<sub>FS</sub> resistor, eliminating the high frequency compensation pole. This should not affect stability, but it will speed up the response of the CSH pin, specifically at the rising edge of the LED current when PWM dimming, thus improving the achievable linearity at low dimming duty cycles.

FIGURE 17. Buck-boost Level-Shifted PWM Circuit

#### Design Considerations 询们 M3424"供应商

询"LM3424"供应商 This section describes the application level considerations when designing with the LM3424. For corresponding calculations, refer to the *Design Guide* section.

#### INDUCTOR

The inductor (L1) is the main energy storage device in a switching regulator. Depending on the topology, energy is stored in the inductor and transfered to the load in different ways (as an example, buck-boost operation is detailed in the Current Regulators section). The size of the inductor, the voltage across it, and the length of the switching subinterval  $(t_{ON} \text{ or } t_{OFF})$  determines the inductor current ripple ( $\Delta i_{I-PP}$ ). In the design process, L1 is chosen to provide a desired  $\Delta i_{I,PP}$ . For a buck regulator the inductor has a direct connection to the load, which is good for a current regulator. This requires little to no output capacitance therefore  $\Delta i_{L-PP}$  is basically equal to the LED ripple current  $\Delta i_{LED-PP}$ . However, for boost and buck-boost regulators, there is always an output capacitor which reduces  $\Delta i_{I ED-PP}$ , therefore the inductor ripple can be larger than in the buck regulator case where output capacitance is minimal or completely absent.

In general,  $\Delta i_{LED-PP}$  is recommended by manufacturers to be less than 40% of the average LED current ( $I_{LED}$ ). Therefore, for the buck regulator with no output capacitance,  $\Delta i_{L-PP}$  should also be less than 40% of  $I_{LED}$ . For the boost and buckboost topologies,  $\Delta i_{L-PP}$  can be much higher depending on the output capacitance value. However,  $\Delta i_{L-PP}$  is suggested to be less than 100% of the average inductor current ( $I_L$ ) to limit the RMS inductor current.

L1 is also suggested to have an RMS current rating at least 25% higher than the calculated minimum allowable RMS inductor current ( $I_{L-RMS}$ ).

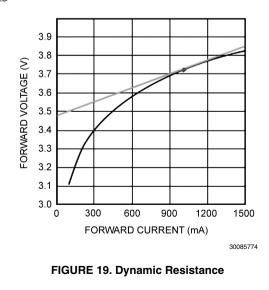

#### LED DYNAMIC RESISTANCE

When the load is a string of LEDs, the output load resistance is the LED string dynamic resistance plus  $R_{SNS}$ . LEDs are PN junction diodes, and their dynamic resistance shifts as their forward current changes. Dividing the forward voltage of a single LED ( $V_{LED}$ ) by the forward current ( $I_{LED}$ ) leads to an incorrect calculation of the dynamic resistance of a single LED ( $r_{LED}$ ). The result can be 5 to 10 times higher than the true  $r_{LED}$  value.

Obtaining  $r_{LED}$  is accomplished by refering to the manufacturer's LED I-V characteristic. It can be calculated as the slope at the nominal operating point as shown in *Figure 19.* For any application with more than 2 series LEDs,  $R_{SNS}$  can be neglected allowing  $r_D$  to be approximated as the number of LEDs multiplied by  $r_{LED}$ .

#### **OUTPUT CAPACITOR**

For boost and buck-boost regulators, the output capacitor (C<sub>O</sub>) provides energy to the load when the recirculating diode (D1) is reverse biased during the first switching subinterval. An output capacitor in a buck topology will simply reduce the LED current ripple ( $\Delta i_{LED-PP}$ ) below the inductor current ripple ( $\Delta i_{LED-PP}$ ). In all cases, C<sub>O</sub> is sized to provide a desired  $\Delta i_{LED-PP}$ . As mentioned in the *Inductor* section,  $\Delta i_{LED-PP}$  is recommended by manufacturers to be less than 40% of the average LED current (I<sub>LED-PP</sub>).

$\rm C_O$  should be carefully chosen to account for derating due to temperature and operating voltage. It must also have the necessary RMS current rating. Ceramic capacitors are the best choice due to their high ripple current rating, long lifetime, and good temperature performance. An X7R dieletric rating is suggested.

#### **INPUT CAPACITORS**

The input capacitance (C<sub>IN</sub>) provides energy during the discontinuous portions of the switching period. For buck and buck-boost regulators, C<sub>IN</sub> provides energy during t<sub>ON</sub> and during t<sub>OFF</sub>, the input voltage source charges up C<sub>IN</sub> with the average input current (I<sub>IN</sub>). For boost regulators, C<sub>IN</sub> only needs to provide the ripple current due to the direct connection to the inductor. C<sub>IN</sub> is selected given the maximum input voltage ripple ( $\Delta v_{IN-PP}$ ) which can be tolerated.  $\Delta v_{IN-PP}$  is suggested to be less than 10% of the input voltage (V<sub>IN</sub>).

An input capacitance at least 100% greater than the calculated  $C_{IN}$  value is recommended to account for derating due to temperature and operating voltage. When PWM dimming, even more capacitance can be helpful to minimize the large current draw from the input voltage source during the rising transistion of the LED current waveform.

The chosen input capacitors must also have the necessary RMS current rating. Ceramic capacitors are again the best choice due to their high ripple current rating, long lifetime, and good temperature performance. An X7R dieletric rating is suggested.

For most applications, it is recommended to bypass the V<sub>IN</sub> pin will an 0.1 µF ceramic capacitor placed as close as possible to the pin. In situations where the bulk input capacitance may be far from the LM3424 device, a 10  $\Omega$  series resistor can be placed between the bulk input capacitance and the bypass capacitor, creating a 150 kHz filter to eliminate undesired high frequency noise.

#### MAIN MosFET / DIMMING MosFET

The LN2443 "LetwiceSat" (Attack of the switching regulator. Q1) as the main power MosFET for the switching regulator. Q1 is recommended to have a voltage rating at least 15% higher than the maximum transistor voltage to ensure safe operation during the ringing of the switch node. In practice, all switching regulators have some ringing at the switch node due to the diode parasitic capacitance and the lead inductance. The current rating is recommended to be at least 10% higher than the average transistor current. The power rating is then verified by calculating the power loss given the RMS transistor current and the NFET on-resistance (R<sub>DS-ON</sub>).

When PWM dimming, the LM3424 requires another MosFET (Q2) placed in series (or parallel for a buck regulator) with the LED load. This MosFET should have a voltage rating equal to the output voltage ( $V_O$ ) and a current rating at least 10% higher than the nominal LED current ( $I_{LED}$ ). The power rating is simply  $V_O$  multiplied by  $I_{LED}$ , assuming 100% dimming duty cycle (continuous operation) will occur.

In general, the NFETs should be chosen to minimize total gate charge  $(Q_g)$  when  $f_{SW}$  is high and minimize  $R_{DS-ON}$  otherwise. This will minimize the dominant power losses in the system. Frequently, higher current NFETs in larger packages are chosen for better thermal performance.

#### **RE-CIRCULATING DIODE**

A re-circulating diode (D1) is required to carry the inductor current during t<sub>OFF</sub>. The most efficient choice for D1 is a Schottky diode due to low forward voltage drop and near-zero reverse recovery time. Similar to Q1, D1 is recommended to have a voltage rating at least 15% higher than the maximum transistor voltage to ensure safe operation during the ringing of the switch node and a current rating at least 10% higher than the average diode current. The power rating is verified by calculating the power loss through the diode. This is accomplished by checking the typical diode forward voltage from the I-V curve on the product datasheet and multiplying by the average diode current. In general, higher current diodes have a lower forward voltage and come in better performing packages minimizing both power losses and temperature rise.

#### **CIRCUIT LAYOUT**

The performance of any switching regulator depends as much upon the layout of the PCB as the component selection. Following a few simple guidelines will maximize noise rejection and minimize the generation of EMI within the circuit.

Discontinuous currents are the most likely to generate EMI. therefore care should be taken when routing these paths. The main path for discontinuous current in the LM3424 buck regulator contains the input capacitor (C<sub>IN</sub>), the recirculating diode (D1), the N-channel MosFET (Q1), and the sense resistor (R<sub>LIM</sub>). In the LM3424 boost regulator, the discontinuous current flows through the output capacitor ( $C_{\Omega}$ ), D1, Q1, and R<sub>IIM</sub>. In the buck-boost regulator both loops are discontinuous and should be carefully layed out. These loops should be kept as small as possible and the connections between all the components should be short and thick to minimize parasitic inductance. In particular, the switch node (where L1, D1 and Q1 connect) should be just large enough to connect the components. To minimize excessive heating, large copper pours can be placed adjacent to the short current path of the switch node.

The RT, COMP, CSH, IS, TSENSE, TREF, HSP and HSN pins are all high-impedance inputs which couple external noise easily, therefore the loops containing these nodes should be minimized whenever possible.

In some applications the LED or LED array can be far away (several inches or more) from the LM3424, or on a separate PCB connected by a wiring harness. When an output capacitor is used and the LED array is large or separated from the rest of the regulator, the output capacitor should be placed close to the LEDs to reduce the effects of parasitic inductance on the AC impedance of the capacitor.

#

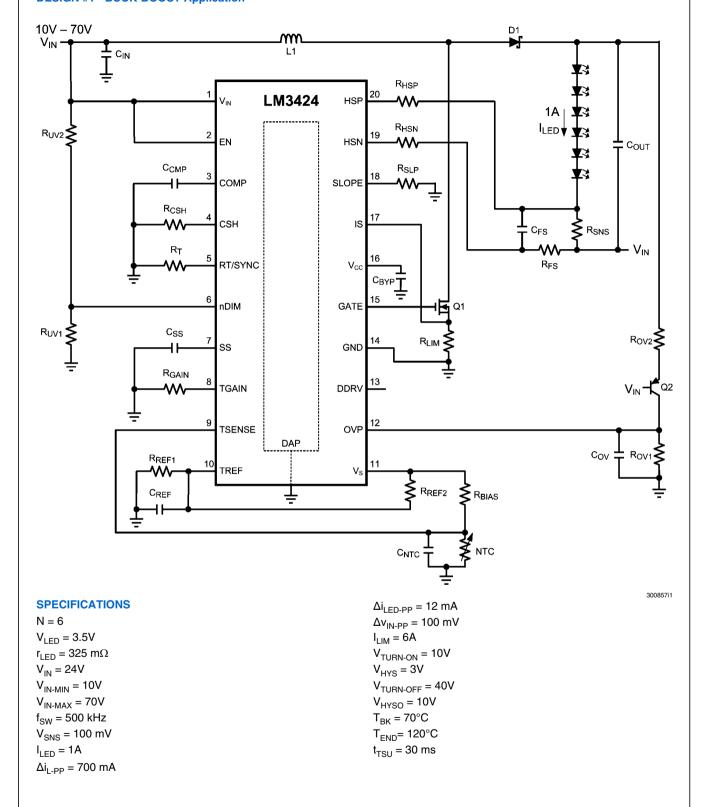

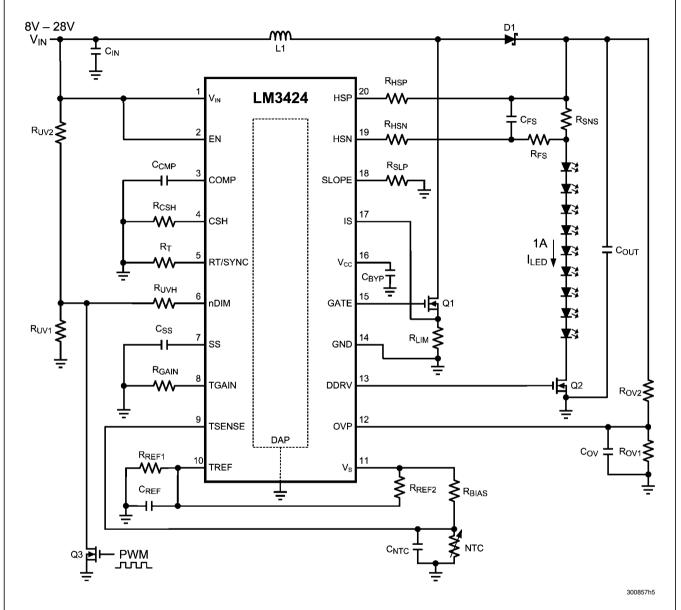

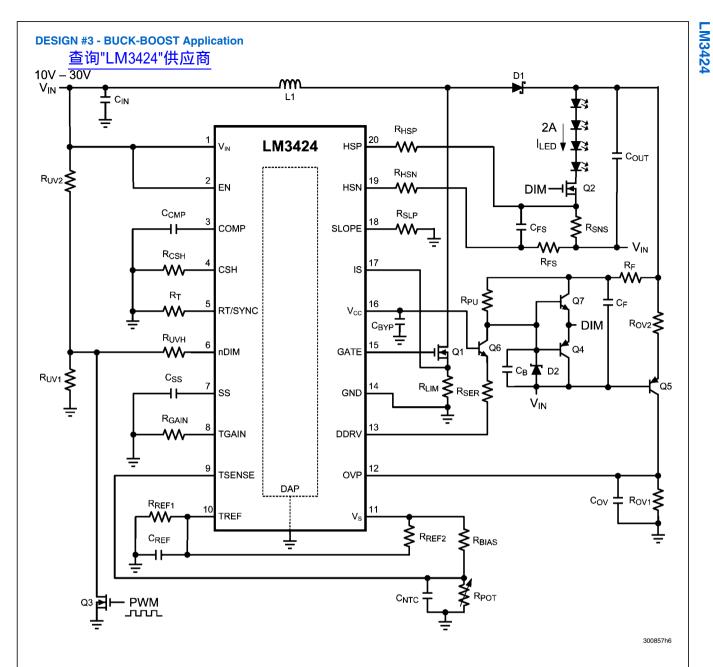

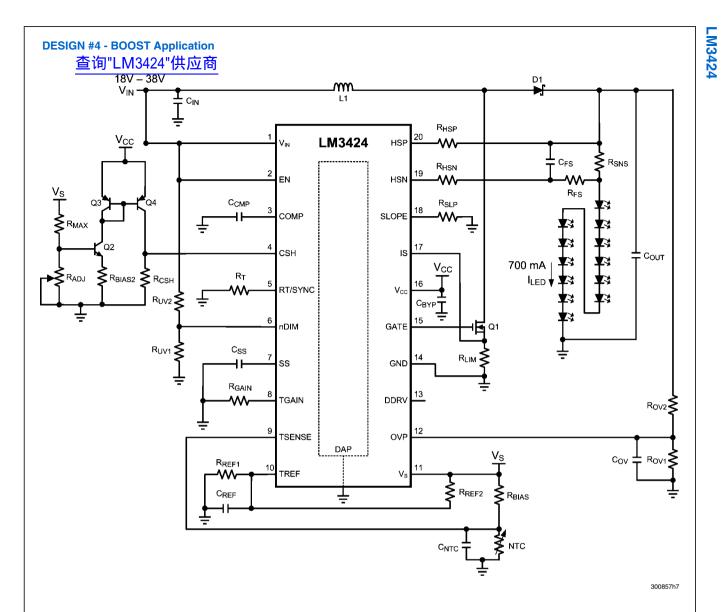

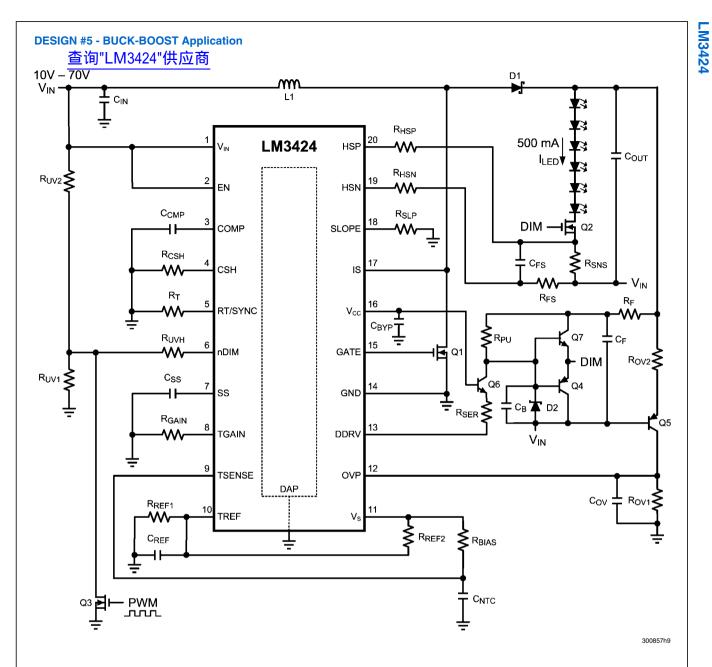

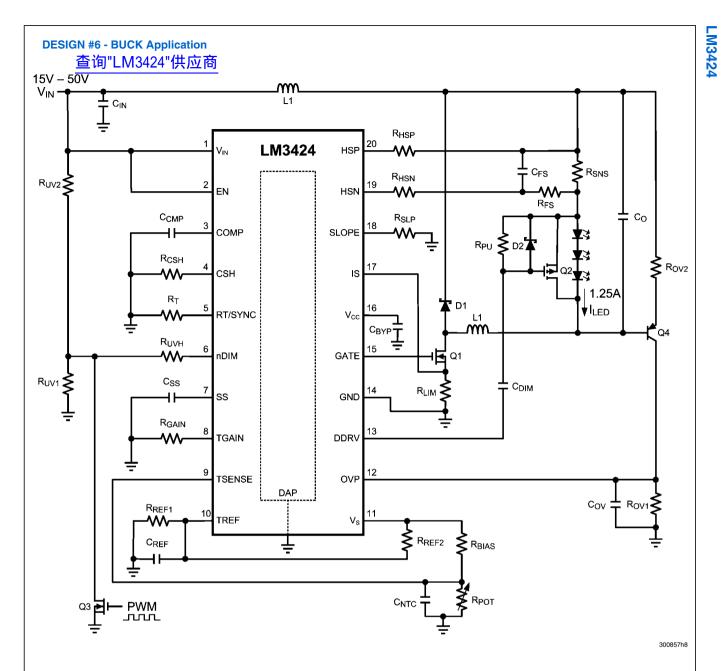

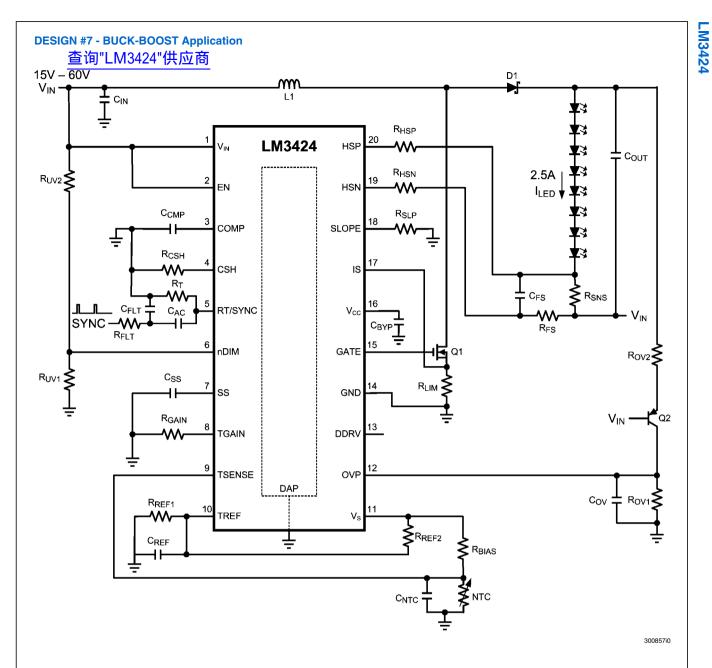

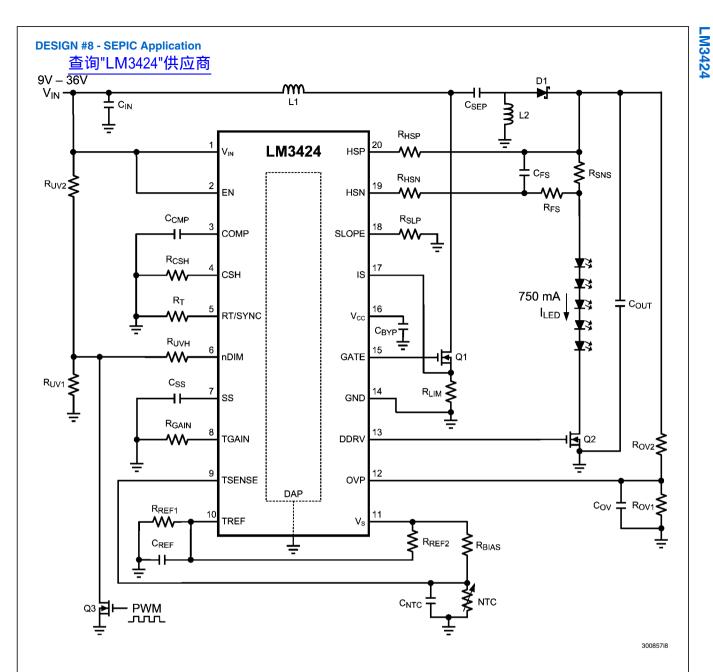

#### BUCK-BOOST REGULATOR 杳询"I M3424"供应商

### Design Guide Befer to Basic Jopology Schematics secti

Refer to Basic Topology Schematics section.

#### SPECIFICATIONS

Number of series LEDs: N Single LED forward voltage: VIED Single LED dynamic resistance: r Nominal input voltage: VIN Input voltage range: VIN-MAX, VIN-MIN Switching frequency: f<sub>SW</sub> Current sense voltage: V<sub>SNS</sub> Average LED current: ILED Inductor current ripple:  $\Delta i_{I_{-}PP}$ LED current ripple: Δi<sub>LED-PP</sub> Peak current limit: ILIM Input voltage ripple: Δv<sub>IN-PP</sub> Output OVLO characteristics: V<sub>TURN-OFF</sub>, V<sub>HYSO</sub> Input UVLO characteristics:  $V_{TURN-ON}$ ,  $V_{HYS}$ Thermal foldback characteristics: T<sub>BK</sub>, T<sub>END</sub> Total start-up time: t<sub>TSU</sub>

#### **1. OPERATING POINT**

Given the number of series LEDs (N), the forward voltage ( $V_{LED}$ ) and dynamic resistance ( $r_{LED}$ ) for a single LED, solve for the nominal output voltage ( $V_O$ ) and the nominal LED string dynamic resistance ( $r_D$ ):

$$V_{O} = N \times V_{LED}$$

$r_{D} = N \times r_{LED}$

Solve for the ideal nominal duty cycle (D):

Buck

$$D = \frac{V_C}{V_{IN}}$$

Boost

$$D = \frac{V_0 - V_{IN}}{V_0}$$

Buck-boost

$$D = \frac{V_0}{V_0 + V_{IN}}$$