#### MILITARY DATA SHEET

Original Creation Date: 10/30/95 Last Update Date: 08/28/96 Last Major Revision Date: 08/21/96

# LOW POWER HEX D FLIP-FLOP

#### General Description

MN100351-X REV 1A0

The F100351 contains six D-type, edge-triggered master/slave flip-flops with true and complement outputs, a pair of common clock inputs (CPa and CPb) and common Master Reset (MR) input. Data enters a master when both CPa and CPb are LOW and transfers to the slave when CPa and CPb (or both) go HIGH. The MR input overrides all other inputs and makes the Q outputs LOW. All inputs have 50K ohm pull-down resistors.

#### Industry Part Number

100351

#### Prime Die

F351

#### NS Part Numbers

100351DMQB 100351FMQB 100351J-QMLV 100351W-QMLV

10

11

#### Processing

MIL-STD-883, Method 5004

#### Quality Conformance Inspection

WWW.DZSG.CON

MIL-STD-883, Method 5005

| Subgrp                                              | Description                                                                                                                                                                        | Temp (°C)                                               |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 <b>A</b><br>8B | Static tests at Static tests at Static tests at Dynamic tests at Dynamic tests at Dynamic tests at Functional tests at Functional tests at Functional tests at Functional tests at | +25<br>+125<br>-55<br>+25<br>+125<br>-55<br>+125<br>-55 |

| 9                                                   | Switching tests at                                                                                                                                                                 | +25                                                     |

Switching tests at Switching tests at

+125

#### MN100351-X REV 1A0

#### **Features**

- 40% Power Reduction of the 100151

- 2000V ESD Protection

- Pin/function compatible with 100151

- Voltage compensated operating range: -4.2V to -5.7V

- Available to industrial grade temperature range

## (Absolute Maximum Ratings)

(Note 1)

Storage Temperature (Tstg)  $$-65\mbox{C}$$  to  $+150\mbox{C}$

Maximum Junction Temperature (Tj)

Ceramic +175C

Plastic +150C

Vee Pin Potential to Ground Pin -7.0V to +0.5V

Input Voltage (DC)

Output Current (DC Output HIGH)

-50 mA

ESD (Note 2)

<u>≥</u>2000V

Note 1: Absolute maximum ratings are those values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not

nave its useful life impaired. Functional operation under these conditions is no implied.

Vee to +0.5V

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

### Recommended Operating Conditions

Case Temperature (Tc)

Commercial

Industrial

Military

Commercial

0 C to +85 C

-40 C to +85C

-55C to +125C

-5.7V to -4.2V

# Electrical Characteristics DC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) DC: Vee Range: -4.2V to -5.7V, Tc= -55C to +125C, VCC=VCCA=GND

| SYMBOL                                    | PARAMETER                     | CONDITIONS                                                          | NOTES      | PIN-<br>NAME | MIN   | MAX   | UNIT | SUB-<br>GROUPS |

|-------------------------------------------|-------------------------------|---------------------------------------------------------------------|------------|--------------|-------|-------|------|----------------|

| IIH Input HIGH<br>Current                 |                               | VEE=-5.7V, VM=-0.87V                                                | 1, 3       | Dn           |       | 240   | uA   | 1, 2           |

|                                           | Carrene                       |                                                                     | 1, 3       | Dn           |       | 340   | uA   | 3              |

|                                           |                               | VEE =-5.7V, VM =-0.87V                                              | 1, 3       | MR, CPn      |       | 350   | uA   | 1, 2           |

|                                           |                               |                                                                     | 1, 3       | MR, CPn      |       | 500   | uA   | 3              |

| IIL                                       | Input Low Current             | VEE=-4.2V, VM=-1.83V                                                | 1, 3       | INPUTS       | 0.5   |       | uA   | 1, 2,          |

| VOH Output HIGH<br>Voltage                |                               | VEE=-4.2V/-5.7V, VIH=-0.87V, VIL=-1.83V, LOADING:50 Ohms to -2.0V   | 1, 3       | OUTPUTS      | -1025 | -870  | mV   | 1, 2           |

|                                           | Voicage                       |                                                                     | 1, 3       | OUTPUTS      | -1085 | -870  | mV   | 3              |

| VOL Output LOW Voltage                    |                               | Vee=-4.2V/-5.7V, VIH=-0.87V, VIL=-1.83V, LOADING:50 Ohms to -2.0V   | 1, 3       | OUTPUTS      | -1830 | -1620 | mV   | 1, 2           |

|                                           | Volcage                       |                                                                     | 1, 3       | OUTPUTS      | -1830 | -1555 | mV   | 3              |

| VOHC Output HIGH                          | Output HIGH<br>Voltage Corner | Vee=-4.2V/-5.7V, VIH=-1.165V, VIL=-1.475V, Loading:50 Ohms to -2.0V | 1, 3       | OUTPUTS      | -1035 |       | mV   | 1, 2           |

|                                           | Point High                    |                                                                     | 1, 3       | OUTPUTS      | -1085 |       | mV   | 3              |

| VOLC Output LOW Voltage Corner Point High |                               | Corner VIL=-1.475V, Loading:50 Ohms to -2.0V                        | 1, 3       | OUTPUTS      |       | -1610 | mV   | 1, 2           |

|                                           |                               |                                                                     | 1, 3       | OUTPUTS      |       | -1555 | mV   | 3              |

| VIH                                       | Input HIGH<br>Voltage         |                                                                     | 1,<br>3, 7 | INPUTS       | -1165 | -870  | mV   | 1, 2,          |

| VIL                                       | Input LOW Voltage             |                                                                     | 1,<br>3, 7 | INPUTS       | -1830 | -1475 | mV   | 1, 2,          |

| IEE                                       | Power Supply<br>Current       | VEE=-4.2/-5.7V                                                      | 1, 3       | VEE          | -135  | -50   | mA   | 1, 2,          |

# Electrical Characteristics AC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) AC: VEE Range: -4.2V to -5.7V, LOADING: 50 Ohms to -2.0V, VCC=VCCA=GND

| SYMBOL                         | PARAMETER                  | CONDITIONS      | NOTES | PIN-<br>NAME    | MIN | MAX | UNIT | SUB-<br>GROUPS |

|--------------------------------|----------------------------|-----------------|-------|-----------------|-----|-----|------|----------------|

| tpLH/tpHL( Pro                 | Propagation Delay          | VEE=-4.2/-5.7V  | 2, 4  | CPn to<br>Qn/Qn | 0.5 | 2.2 | ns   | 9              |

|                                |                            |                 | 2, 4  | CPn_to<br>Qn/Qn | 0.5 | 2.6 | ns   | 10             |

|                                |                            |                 | 2, 4  | CPn_to<br>Qn/Qn | 0.4 | 2.4 | ns   | 11             |

| tpLH/tpHL( Propagation Del. 2) | Propagation Delay          | VEE=-4.2/-5.7V  | 2, 4  | MR to<br>Qn/Qn  | 0.7 | 2.6 | ns   | 9              |

|                                |                            |                 | 2, 4  | MR to<br>Qn/Qn  | 0.8 | 2.9 | ns   | 10             |

|                                |                            |                 | 2, 4  | MR to<br>Qn/Qn  | 0.6 | 2.7 | ns   | 11             |

| tTLH/tTHL                      | Transistion Time           | VEE=-4.2/-5.7V  | 6     | Qn/Qn           | 0.2 | 1.6 | ns   | 9, 10,<br>11   |

| ts                             | Setup Time                 | VEE=-4.2/-5.7V  | 6     | Dn to<br>CPn    | 0.8 |     | ns   | 9              |

|                                |                            |                 | 6     | Dn to<br>CPn    | 0.9 |     | ns   | 10, 11         |

| tH                             | Hold Time                  | VEE=-4.2/-5.7V  | 6     | Dn to<br>CPn    | 1.4 |     | ns   | 9              |

|                                |                            |                 | 6     | Dn to<br>CPn    | 1.6 |     | ns   | 10             |

|                                |                            |                 | 6     | Dn to<br>CPn    | 1.5 |     | ns   | 11             |

| trel                           |                            | VEE= -4.2/-5.7V | 6     | MR              | 1.8 |     | ns   | 9              |

|                                |                            |                 | 6     | MR              | 2.6 |     | ns   | 10             |

|                                |                            |                 | 6     | MR              | 1.6 |     | ns   | 11             |

| tPW(H)                         | Pulse Width                | VEE= -4.2/-5.7V | 6     | CPn/MR          | 2.0 |     | ns   | 9, 10,<br>11   |

| fMAX                           | Maximum Clock<br>Frequency | VEE= -4.2/-5.7V | 6     | CPn             | 375 |     | MHz  | 9, 10,<br>11   |

- Screen tested 100% on each device at -55 C, +25 C and +125 C temp., subgroups 1, 2, Note 1:

- 3, 7 & 8.

- For QB devices, screen tested 100% on each device at +25C temperature only, subgroup A9. For QMLV devices, screen tested 100% on each device at +25C, +125C & -55C Note 2:

- Sample tested (Method 5005, Table 1) on each MFG. lot at +25 C, +125 C & -55 C temp., subgroups A1, 2, 3, 7 & 8. Note 3:

- Sample tested (Method 5005, Table 1) on each MFG. lot at +25 C, subgroup A9, and at +125 C & -55 C temp., subgroups A10 & 11. Sample tested (Method 5005, Table 1) on each MFG. lot at +25 C temp. only, subgroup Note 4:

- Note 5:

- Α9. Note 6:

- Not tested at +25 C, +125 C & -55 C temp. (DESIGN CHARACTERIZATION DATA). Guaranteed by applying specified input condition and testing VOH/VOL. Note 7:

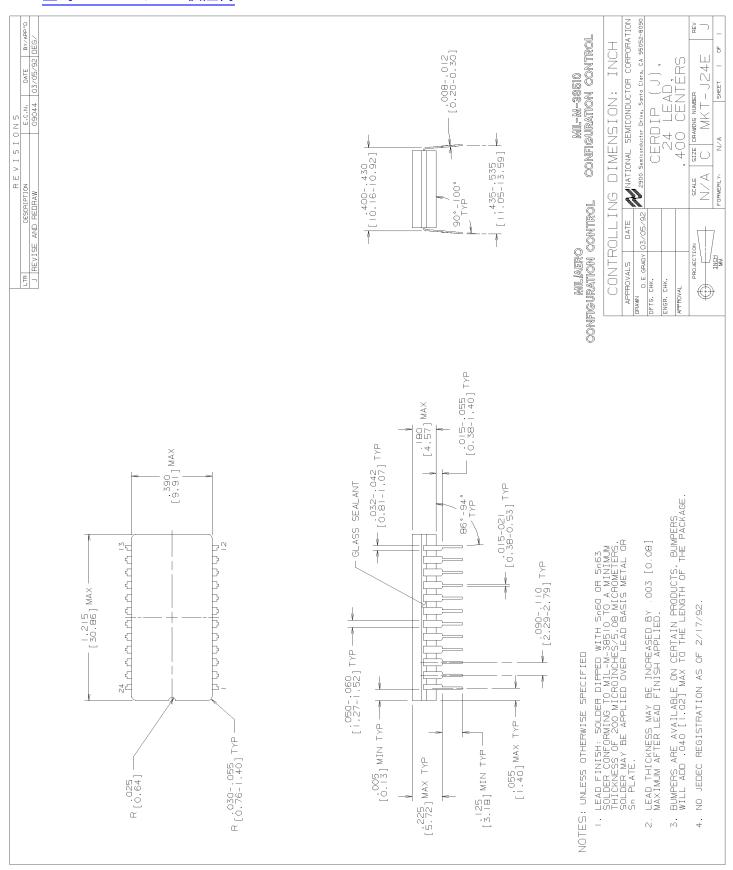

# Graphics and Diagrams

| GRAPHICS# | DESCRIPTION                             |

|-----------|-----------------------------------------|

| J24ERJ    | CERDIP(J), 24LD .400 CENTERS (P/P DWG)  |

| P000078A  | CERDIP (J), 24LD .400 CENTERS (PIN OUT) |

| P000079A  | CERPAC, QUAD, 24 LEAD (PIN OUT)         |

| W24BRE    | CERPAC, QUAD, 24 LEAD (P/P DWG)         |

See attached graphics following this page.

# 查询"100351J-QMLV"供应商