### **MB1503** LOW-POWER PLL FREQUENCY SYNTHESIZER WITH POWER SAVE FUNCTION (1.1GHz)

The Fujitsu MB1503 is a serial input phase-locked loop (PLL) frequency synthesizer with a pulse-swallow function. A stand-by mode is provided to limit power consumption during intermittent operation.

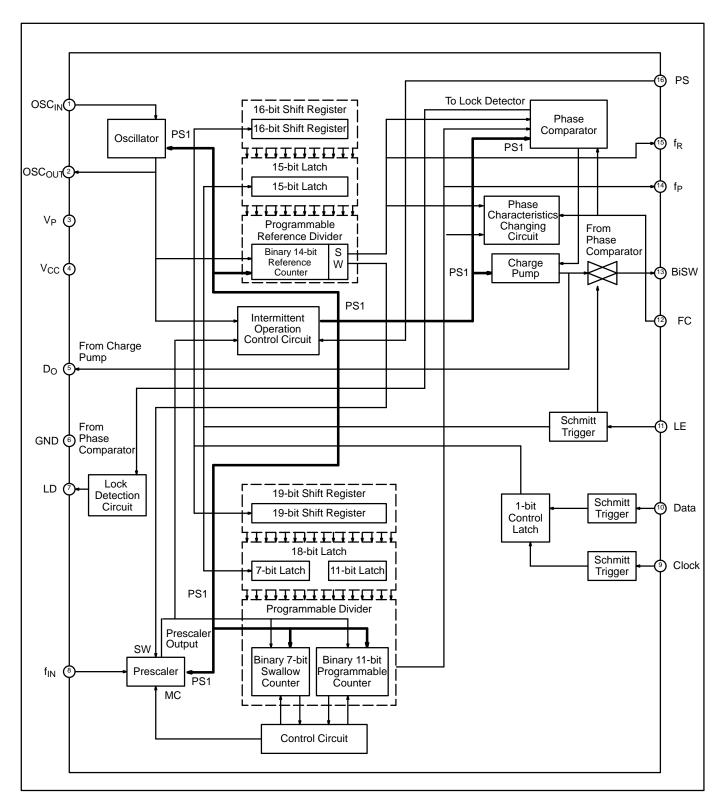

The MB1503 is configured of a 1.1GHz dual-modulus prescaler with 128/129 divide ratio, control signal generator, 16-bit shift register, 15-bit latch, programmable reference divider (binary 14-bit programmable reference counter), 1-bit switch counter, phase comparator with phase conversion function, charge pump, crystal oscillator, 19-bit shift register, 18-bit latch, programmable divider (binary 7-bit swallow counter and binary 11-bit programmable counter), analog switches, and an intermittent operation control circuit that selects the operating or stand-by mode depending on the power-save control input state (PS). The MB1503 operates from a single +5 V supply. Fujitsu's advanced technology achieves an Icc of 8mA, typical. The stand-by mode current consumption is just 100µA.

#### Features

- High operating frequency

- :  $f_{IN} = 1.1 GHz (P_{IN} = -10 dBm)$

- Pulse-swallow function

Low supply current

- : High-speed dual-modulus prescaler with 128/129 divide ratio

- :  $I_{CC} = 8mA$  typ. at 5V

- Power-saving stand-by mode : 100µA

- Serial input, 18-bit programmable divider consisting of:

- Binary 7-bit swallow counter : 0 to 127

- Binary 11-bit programmable counter: 16 to 2,047

- Serial input 15-bit programmable reference divider consisting of:

- Binary 15-bit programmable reference counter: 8 to 16,383

- 1-bit switch counter sets prescaler divide ratio

- On-chip analog switch for fast lock-up

- On-chip charge pump

- Wide operating temperature range: -40 to +85°C

- Plastic 16-pin dual inline package (Suffix : -P)

- Plastic 16-pin small outline package (Suffix : -PF)

#### **ABSOLUTE MAXIMUM RATINGS (See NOTE)**

| Ratings             | Symbol           | Value                        | Unit |

|---------------------|------------------|------------------------------|------|

| Supply Voltage      | V <sub>CC</sub>  | -0.5 to +7.0                 | V    |

|                     | V <sub>P</sub>   | $V_{CC} \le V_P \le 10.0$    | V    |

| Output Voltage      | V <sub>OUT</sub> | –0.5 to V <sub>CC</sub> +0.5 | V    |

| Output Current      | I <sub>OUT</sub> | ±10                          | mA   |

| Storage Temperature | Tstg             | -55 to +125                  | °C   |

NOTE: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

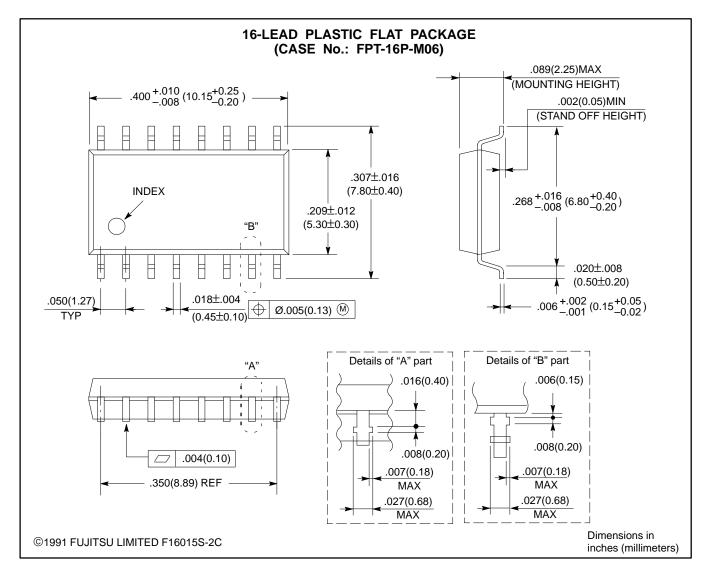

PLASTIC PACKAGE (FPT-16P-M06)

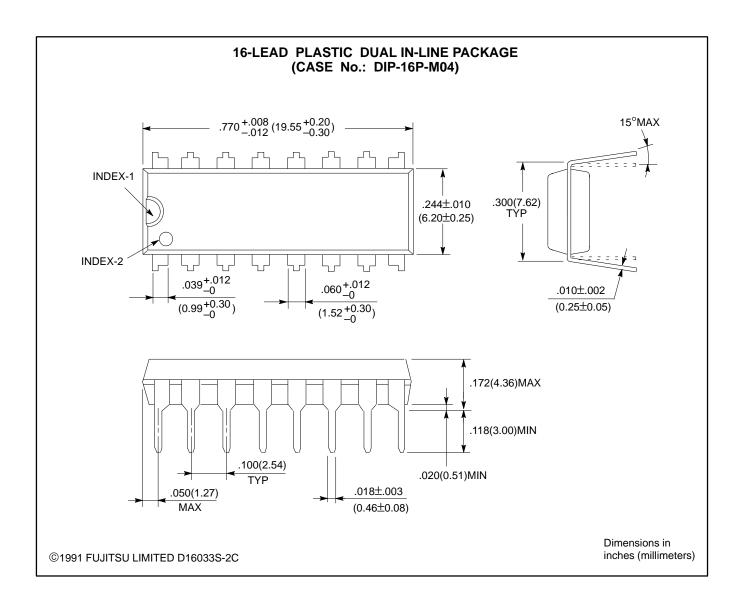

PLASTIC PACKAGE (DIP-16P-M04)

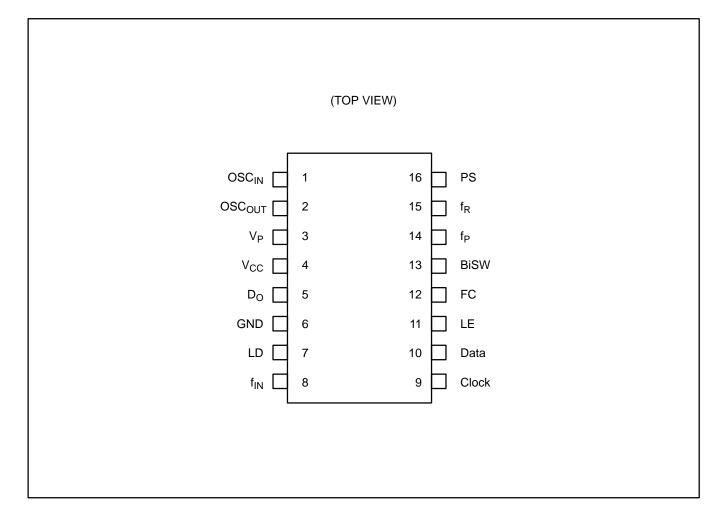

## **PIN ASSIGNMENT**

### **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| Pin No. | Pin Name           | I/O | Description                                                                                                                                                                                                                                                                                                                         |

|---------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OSC <sub>IN</sub>  | I   | Programmable reference divider input<br>Oscillator input<br>An external crystal is connected to this pin.                                                                                                                                                                                                                           |

| 2       | OSC <sub>OUT</sub> | 0   | Oscillator output<br>An external crystal is connected to this pin.                                                                                                                                                                                                                                                                  |

| 3       | V <sub>P</sub>     | -   | Power supply input for charge pump and analog switch                                                                                                                                                                                                                                                                                |

| 4       | V <sub>CC</sub>    | _   | Power supply                                                                                                                                                                                                                                                                                                                        |

| 5       | D <sub>O</sub>     | 0   | Charge pump output<br>The phase of the charge pump is reversed depending on the FC input.                                                                                                                                                                                                                                           |

| 6       | GND                | _   | Ground                                                                                                                                                                                                                                                                                                                              |

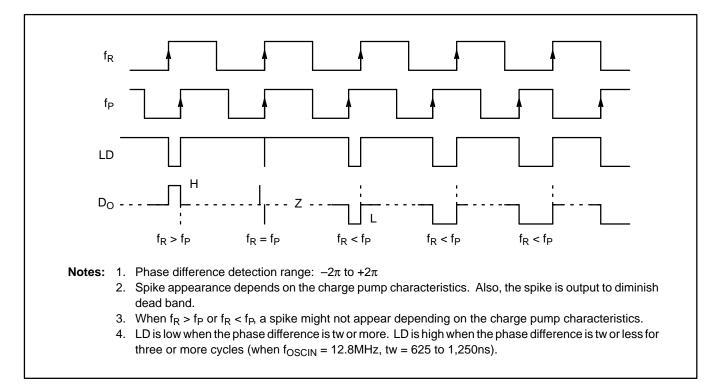

| 7       | LD                 | 0   | Phase comparator output<br>The output level is high when LD is locked. The output level is low when LD is unlocked.                                                                                                                                                                                                                 |

| 8       | f <sub>IN</sub>    | Ι   | Prescaler input<br>Connection with an external VCO should be done by AC coupling.                                                                                                                                                                                                                                                   |

| 9       | Clock              | I   | Clock input for 19-bit and 16-bit shift registers<br>Data is shifted into the shift register on the rising edge of the clock. The Schmitt trigger is<br>contained.                                                                                                                                                                  |

| 10      | Data               | I   | Serial data input using binary code<br>The last bit of the data is a control bit.<br>When the control bit is high, data is transmitted to the 15-bit latch.<br>When it is low, data is transmitted to the 18-bit latch.The Schmitt trigger input is involved.                                                                       |

| 11      | LE                 | I   | Load enable signal input<br>When LE is high, the data of the shift register are transferred to a latch, depending on the<br>control bit in the serial data. At the same time, an internal analog switch turns on and the output<br>of the internal charge pump is connected to the BiSW pin. The Schmitt trigger input is involved. |

| 12      | FC                 | I   | Phase select input of phase comparator (with internal pull-up resistor)<br>When FC is low, the characteristics of the charge pump and phase comparator are reversed.<br>The FC input signal is also used to control the $f_{OUT}$ pin (test pin) of $f_R$ or $f_P$ .                                                                |

| 13      | BiSW               | 0   | Analog switch output<br>BiSW is usually in the high-impedance state. When the switch is turned on (LE is high), the<br>state of the internal charge pump is output.                                                                                                                                                                 |

| 14      | f <sub>P</sub>     | 0   | Monitor pin of programmable counter output                                                                                                                                                                                                                                                                                          |

| 15      | f <sub>R</sub>     | 0   | Monitor pin of reference counter output                                                                                                                                                                                                                                                                                             |

| 16      | PS                 | I   | Power save signal input<br>Set PS low while the system is powered (never use pin 16 as it is opened)<br>PS = High : Operation mode<br>PS = Low : Stand-by mode                                                                                                                                                                      |

## **FUNCTIONAL DESCRIPTIONS**

#### **Pulse swallow function**

The divide ratio can be calculated using the following equation:

$f_{VCO} = [(M \times N) + A] \times f_{OSC} \div R \quad (A < N)$

- f<sub>VCO</sub>: Output frequency of external voltage controlled oscillator (VCO)

- N : Preset divide ratio of binary 11-bit programmable counter (16 to 2,047)

- A : Preset divide ratio of binary 7-bit swallow counter ( $0 \le A \le 127$ )

- f<sub>OSC</sub>: Output frequency of the reference frequency oscillator

- R : Preset divide ratio of binary 14-bit programmable reference counter (8 to 16,383)

- M : Preset divide ratio of modules prescaler (128)

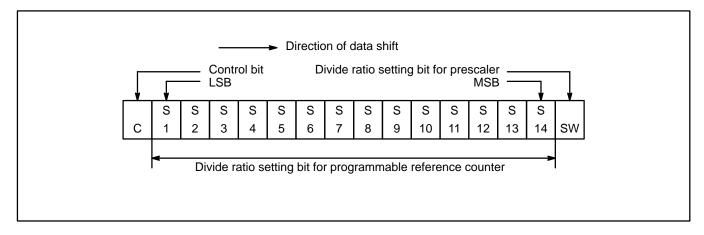

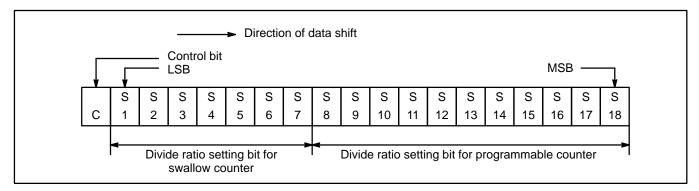

#### Serial data input

Serial data is input using the Data, Clock, and LE pins. Serial data controls the 15-bit programmable reference divider and 18-bit programmable divider separately.

Binary serial data is input to the Data pin.

One bit of data is shifted into the internal shift registers on the rising edge of the clock. When the load enable pin is high or open, stored data is latched depending on the control data as follows:

| Control data | Destination of serial data |

|--------------|----------------------------|

| Н            | 15-bit latch               |

| L            | 18-bit latch               |

(a) Programmable reference divider ratio

The programmable reference divider consists of a 15-bit latch and a 14-bit reference counter. The serial 16-bit data format is shown below:

| Divide ratio<br>R | S<br>14 | S<br>13 | S<br>12 | S<br>11 | S<br>10 | S 9 | S<br>8 | S<br>7 | S<br>6 | S<br>5 | S<br>4 | S<br>3 | S<br>2 | S<br>1 |

|-------------------|---------|---------|---------|---------|---------|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| 8                 | 0       | 0       | 0       | 0       | 0       | 0   | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      |

| 9                 | 0       | 0       | 0       | 0       | 0       | 0   | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 1      |

| •                 | •       | •       | •       | •       | •       | •   | •      | •      | •      | •      | •      | •      | •      | •      |

| 16383             | 1       | 1       | 1       | 1       | 1       | 1   | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

• 14-bit programmable reference counter divide ratio

(Divide ratio = 8 to 16,383)

**Notes:** 1. Divide ratios less than 8 are prohibited

- 2. SW: This bit selects the divide ratio of the prescaler SW Low: 128 or 129 (SW must be always be low)

- 3. S1 to S14: These bits select the divide ratio of the programmable reference counter (8 to 16,383)

- 4. C: Control bit: Set high

- 5. Input MSB data first

- (b) Programmable divider divide ratio

The programmable divider consists of a 19-bit shift register, 18-bit latch, 7-bit swallow counter, and 11-bit programmable counter. The serial 19-bit data format is shown below:

• 7-bit swallow counter divide ratio

| Divide<br>ratio<br>A      | S<br>7 | S<br>6 | S<br>5 | S<br>4 | S<br>3 | S<br>2 | S<br>1 |  |  |

|---------------------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| 0                         | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| 1                         | 0      | 0      | 0      | 0      | 0      | 0      | 1      |  |  |

| •                         | •      | •      | •      | •      | •      | •      | •      |  |  |

| 127                       | 1      | 1      | 1      | 1      | 1      | 1      | 1      |  |  |

| (Divide ratio = 0 to 127) |        |        |        |        |        |        |        |  |  |

• 11-bit programmable counter divide ratio

| Divide<br>ratio<br>N         | S<br>18 | S<br>17 | S<br>16 | S<br>15 | S<br>14 | S<br>13 | S<br>12 | S<br>11 | S<br>10 | S<br>9 | S<br>8 |

|------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------|--------|

| 16                           | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0      | 0      |

| 17                           | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0      | 1      |

| •                            | •       | •       | •       | •       | •       | •       | •       | •       | •       | •      | •      |

| 2047                         | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1      | 1      |

| (Divide ratio = 16 to 2,047) |         |         |         |         |         |         |         |         |         |        |        |

**Notes:** 1. Divide ratios less than 16 are prohibited for the 11–bit programmable counter

- 2. S1 to S7: These bits select the divide ratio of the swallow counter (0 to 127)

- 3. S8 to S18: These bits select the divide ratio of the programmable counter (16 to 2,047)

- 4. C: Control bit: (Set low)

- 5. Input MSB data first

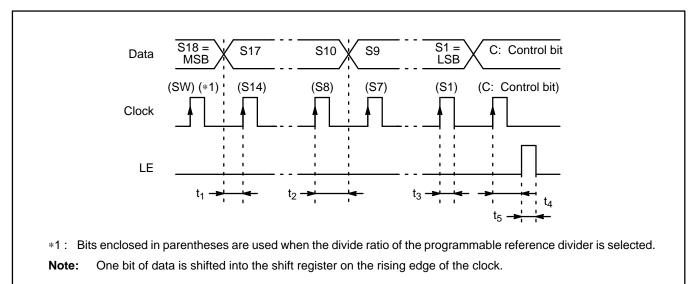

#### Serial data input timing

•  $t_1 (\ge 1\mu s)$ : Data setup time  $t_2 (\ge 1\mu s)$ : Data hold time  $t_4 (\ge 1\mu s)$ : LE setup time to the rising edge of last clock

$t_3 (\ge 1\mu s)$  : Clock pulse width  $t_5 (\ge 1\mu s)$  : LE pulse width

#### Intermittent operation

Intermittent operation limits power consumption by shutting down or starting the internal circuits according to their necessity. If device operation resumes uncontrolled, the error signal output from the phase comparator may exceed the limit due to an undefined phase relationship between the reference frequency ( $f_R$ ) and the comparison frequency ( $f_P$ ) and frequency lock is lost.

To prevent this, an intermittent operation control circuit is provided to decrease the variation in the locking frequency by forcibly correcting the phase of both frequencies to limit the error signal output. This is done by the PS control circuit. If PS is set high, the circuit enters the operating mode. If PS is set low, operation stops and the device enters the stand-by mode. Each mode is explained below:

Operating mode (PS =High Level) All circuits are operating, and PLL operation is normal.

Stand-by mode (PS = Low level)

Circuits that do not affect operation are powered down to limit current consumption.

The current in the power save state is typically  $100\mu A$ .

At this time, the levels of  $\mathsf{D}_\mathsf{O}$  and LD are the same as when the PLL is locked.

Since  $D_O$  is placed in the high-impedance state and the input voltage of the voltage controlled oscillator (VCO) is set to the voltage in the operating mode (when locked) by the time constant of the low-pass filter, the frequency output from the VCO ( $f_{VCO}$ ) is kept at the locking frequency.

The operating and stand-by modes alternate repeatedly. This intermittent operation limits the error signal by forcibly correcting the phase of the reference and comparison frequencies to limit power consumption. The device must be set in the stand-by mode (PS = low) when it is powered up.

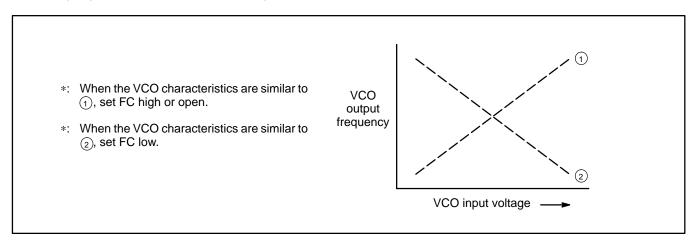

#### Relationship between the FC input and phase characteristics

The FC pin changes the phase characteristics of the phase comparator. The internal charge pump output level ( $D_0$ ) is reversed, depending on the FC pin input level. The relationship between the FC input level and  $D_0$  is shown below:

|                                 | FC = High or open | FC = Low |

|---------------------------------|-------------------|----------|

| f <sub>R</sub> > f <sub>P</sub> | Н                 | L        |

| f <sub>R</sub> < f <sub>P</sub> | L                 | Н        |

| $f_R = f_P$                     | Z (*1)            | Z (*1)   |

\*1: High impedance

When designing a synthesizer, the FC pin setting depends on the VCO characteristics.

#### Phase comparator output waveform (FC = High)

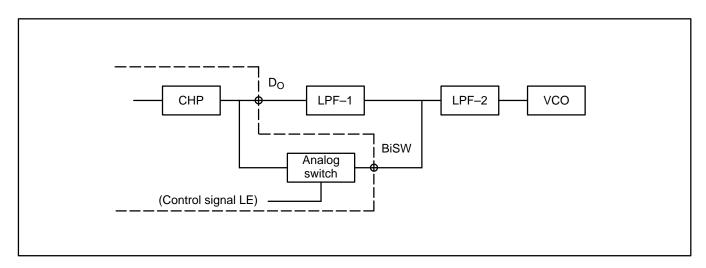

#### Analog switch

The LE signal turns the analog switch on or off. When the analog switch is turned on, the charge pump output  $(D_0)$  is output through the BiSW pin. When it is turned off, the BiSW pin is in the high-impedance state.

When LE = high (when the divide ratio of the internal divider is changed): Analog switch = on When LE = low (normal operating mode): Analog switch = off

The LPF time constant can be decreased by inserting an analog switch between LPF1 and LPF2. This decreases the lock-up time when the PLL channel is changed.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          |     | Unit |                 |      |  |

|-----------------------|-----------------|-----|------|-----------------|------|--|

| Falameter             | Symbol          | Min | Тур  | Max             | Unit |  |

| Supply Voltage        | V <sub>CC</sub> | 4.5 | 5.0  | 5.5             | V    |  |

| Supply Voltage        | VP              |     | V    |                 |      |  |

| Input Voltage         | VI              | GND | _    | V <sub>CC</sub> | V    |  |

| Operating Temperature | T <sub>A</sub>  | -40 | _    | +85             | °C   |  |

### HANDLING PRECAUTIONS

- This device should be transported and stored in anti-static containers.

- This is a static-sensitive device; take proper anti-ESD precautions. Ensure that personnel and equipment are properly grounded. Cover workbenches with grounded conductive mats.

- Always turn the power supply off before inserting or removing the device from its socket.

- Protect leads with a conductive sheet when handling or transporting PC boards with devices.

# **ELECTRICAL CHARACTERISTICS**

| Deveryor                          |                            | Cumb al           |                       | Value |                       | 11                                                                                                                          | Condition                                                                                                                                                            |  |

|-----------------------------------|----------------------------|-------------------|-----------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                         |                            | Symbol            | Min                   | Тур   | Max                   | Unit                                                                                                                        | Condition                                                                                                                                                            |  |

| Supply Current                    | I <sub>CC</sub>            | _                 | 8.0                   | 12.0  | mA                    | With $f_{IN}$ = 1.1GHz, OSC <sub>IN</sub> = 12MHz, V <sub>CC</sub> = 5.0V. Inputs are V <sub>CC</sub> and outputs are open. |                                                                                                                                                                      |  |

| Stand-by Current                  |                            | IPS               | _                     | 100   | _                     | μΑ                                                                                                                          | With $f_{IN} = 1.1 GHz$ , OSC <sub>IN</sub> = 12MHz, V <sub>CC</sub> = 5.0V. The PS pin is grounded, remaining inputs are at V <sub>CC</sub> , and outputs are open. |  |

| Operating Frequency               | f <sub>IN</sub>            | f <sub>IN</sub>   | 10                    | _     | 1100                  | MHz                                                                                                                         | AC coupling. The minimum<br>operating frequency is<br>measured with a 100pF ca-<br>pacitor connected.                                                                |  |

|                                   | OSC <sub>IN</sub>          | f <sub>OSC</sub>  | _                     | 12    | 20                    | MHz                                                                                                                         | _                                                                                                                                                                    |  |

| Innut Consitiuity                 | f <sub>IN</sub>            | P <sub>f IN</sub> | -10                   | _     | 6                     | dBm                                                                                                                         | —                                                                                                                                                                    |  |

| Input Sensitivity                 | OSC <sub>IN</sub>          | V <sub>OSC</sub>  | 0.5                   | _     | -                     | Vp–p                                                                                                                        | —                                                                                                                                                                    |  |

| High-level Input Voltage          | Except f <sub>IN</sub> and | V <sub>IH</sub>   | V <sub>CC</sub> x 0.7 | _     | -                     | V                                                                                                                           | —                                                                                                                                                                    |  |

| Low-level Input Voltage           | OSCIN                      | V <sub>IL</sub>   | _                     | _     | V <sub>CC</sub> x 0.3 | V                                                                                                                           | —                                                                                                                                                                    |  |

| High-level Input Current          | Data, Clock,               | I <sub>IH</sub>   | -                     | 1.0   | -                     | μΑ                                                                                                                          | _                                                                                                                                                                    |  |

|                                   | LE                         | IIL               | -                     | -1.0  | -                     | μΑ                                                                                                                          | —                                                                                                                                                                    |  |

| Low-level Input Current           | FC                         | I <sub>FC</sub>   | _                     | -60   | _                     | μΑ                                                                                                                          | _                                                                                                                                                                    |  |

| Input Current                     | OSC <sub>IN</sub>          | I <sub>OSC</sub>  | -                     | ±50   | -                     | μA                                                                                                                          | _                                                                                                                                                                    |  |

| High-level Output<br>Voltage      | Except D <sub>O</sub> and  | V <sub>OH</sub>   | 4.4                   | _     | -                     | V                                                                                                                           | $V_{CC} = 5V$                                                                                                                                                        |  |

| Low-level Output Voltage          | OSCOUT                     | V <sub>OL</sub>   | -                     | _     | 0.4                   | V                                                                                                                           | _                                                                                                                                                                    |  |

| High-impedance<br>Cut off Current | D <sub>O</sub>             | I <sub>OFF</sub>  | -                     | -     | 1.1                   | μA                                                                                                                          | $\begin{array}{l} V_{DO} = GND \text{ to } 8V \\ V_{CC} \leq V_P \leq 8V \end{array}$                                                                                |  |

| Output Current                    | Except D <sub>O</sub> and  | I <sub>OH</sub>   | -1.0                  | -     | -                     | mA                                                                                                                          | —                                                                                                                                                                    |  |

|                                   | OSCOUT                     | I <sub>OL</sub>   | 1.0                   | -     | -                     | mA                                                                                                                          | —                                                                                                                                                                    |  |

| Analog Switch ON Resist           | ance                       | R <sub>ON</sub>   | _                     | 25    | _                     | Ω                                                                                                                           | _                                                                                                                                                                    |  |

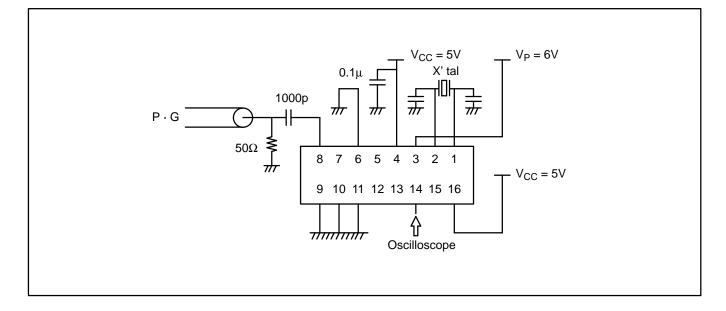

### TEST CIRCUIT (FOR MEASURING PRESCALER INPUT SENSITIVITY)

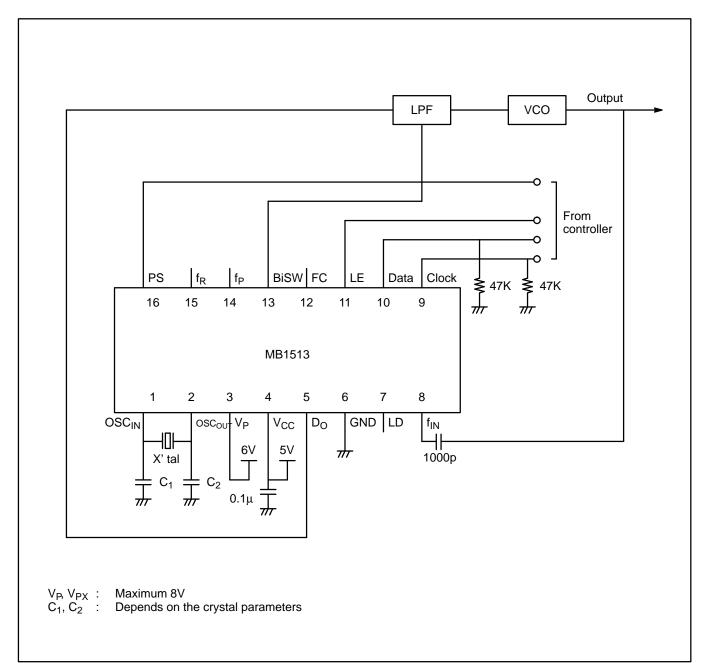

### **APPLICATION EXAMPLE**

## PACKAGE DIMENSIONS