## EM78468

# 8-BIT Microcontroller

# Product Specification

Doc. Version 1.1

ELAN MICROELECTRONICS CORP.

April 2005

Trademark Acknowledgments:

IBM is a registered trademark and PS/2 is a trademark of IBM.

Windows is a trademark of Microsoft Corporation.

ELAN and ELAN logo are trademarks of ELAN Microelectronics Corporation.

#### Copyright © 2005 by ELAN Microelectronics Corporation All Rights Reserved

Printed in Taiwan

The contents of in this specification are subject to change without notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible to any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising out of the use of such information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited.

NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESS WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

#### **ELAN MICROELECTRONICS CORPORATION**

#### **Headquarters:**

No. 12, Innovation Road 1 Science-based Industrial Park Hsinchu, Taiwan, 308 Tel: +886 3 563-9977

Fax: +886 3 563-9966

http://www.emc.com.tw

Hong Kong:

Elan (HK) Microelectronics Corporation, Ltd.

Rm. 1005B, 10/F Empire Centre 68 Mody Road, Tsimshatsui Kowloon, HONG KONG

Tel: +852 2723-3376 Fax: +852 2723-7780

elanhk@emc.com.hk

USA:

Elan Information Technology Group

1821 Saratoga Ave., Suite 250 Saratoga, CA 95070

**USA**

Tel: +1 408 366-8223 Fax: +1 408 366-8220

Europe:

Elan Microelectronics Corp. Elan Microelectronics (Europe)

Siewerdtstrasse 105 8050 Zurich, SWITZERLAND Tel:+41 43 299-4060

Fax:+41 43 299-4079 http://www.elan-europe.com Shenzhen:

Shenzhen, Ltd.

SSMEC Bldg., 3F, Gaoxin S. Ave. Shenzhen Hi-Tech Industrial Park Shenzhen, Guandong, CHINA Tel: +86 755 2601-0565

Fax: +86 755 2601-0500

Shanghai:

**Elan Microelectronics** Shanghai Corporation, Ltd.

23/Bldg. #115 Lane 572, Bibo Road

Zhangjiang Hi-Tech Park Shanghai, CHINA Tel: +86 021 5080-3866 Fax: +86 021 5080-4600

### **Contents**

| 1 | GEN        | NERAL DESCRIPTION                                           | ··· 1 |

|---|------------|-------------------------------------------------------------|-------|

| 2 | <b>FEA</b> | ATURES                                                      |       |

|   | 2.2        | LCD Circuit                                                 |       |

|   | 2.3        | Applications                                                |       |

| 2 |            | ASSIGNMENTS                                                 |       |

| 3 |            | QFP - 64                                                    |       |

|   | 3.1        | LQFP - 64 ······                                            | _     |

|   | 3.2        | LQFP - 44·····                                              |       |

|   | 3.4        | QFP - 44·····                                               | _     |

|   | _          |                                                             |       |

| 4 |            | ICTION DESCRIPTION                                          |       |

|   | 4.1        | Operational Registers                                       |       |

|   | 4.2        | Special Purpose Registers                                   |       |

|   | 4.3        | TCC and WDT Pre-scaler                                      |       |

|   | 4.4<br>4.5 | RESET and Wake-up                                           |       |

|   | 4.6        | Oscillator ·····                                            |       |

|   | 4.7        | Power-on Considerations ·····                               |       |

|   | 4.8        | Interrupt ·····                                             |       |

|   | 4.9        | LCD Driver·····                                             |       |

|   | 4.10       | Infrared Remote Control Application / PWM Waveform Generate | · 48  |

|   | 4.11       | Code Options ·····                                          | · 52  |

|   | 4.12       | Instruction Set ·····                                       | · 53  |

|   | 4.13       | Timing Diagram ·····                                        | · 55  |

| 5 | ABS        | SOLUTE MAXIMUM RATINGS                                      | · 56  |

| 6 | ELE        | CTRICAL CHARACTERISTIC                                      | · 57  |

|   | 6.1        | DC ELECTRICAL CHARACTERISTICS                               |       |

|   | 6.2        | AC Electrical Characteristics                               |       |

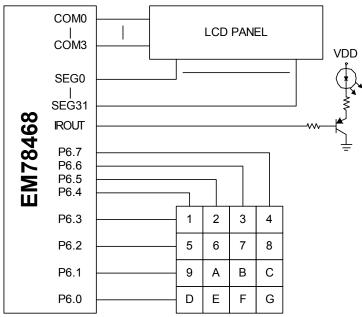

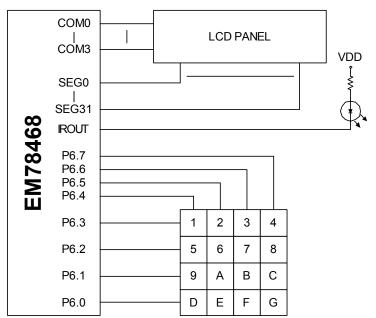

| 7 | App        | olication Circuit·····                                      | -60   |

|   |            | APPENDIX A                                                  |       |

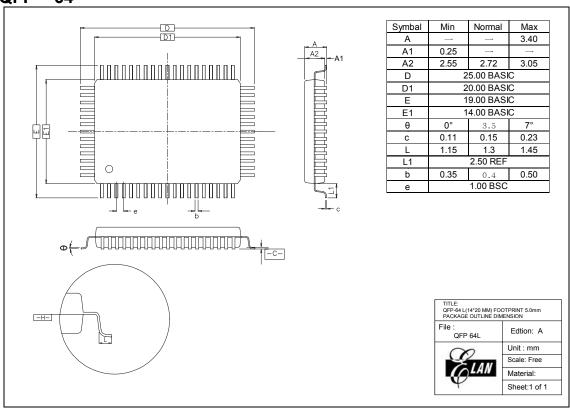

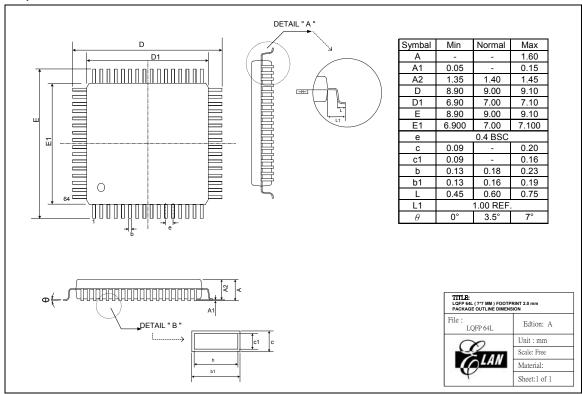

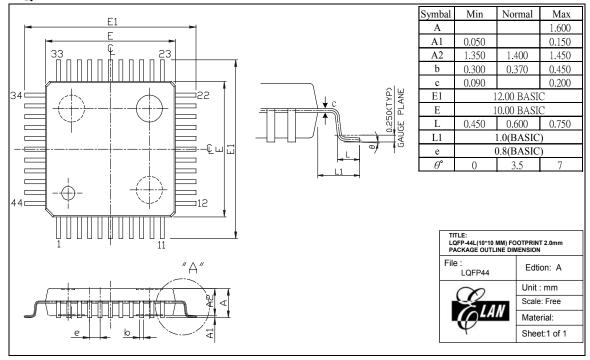

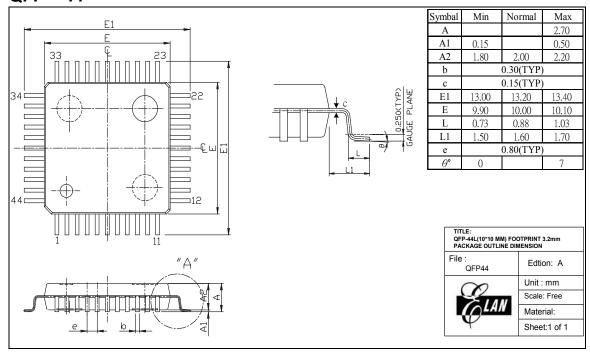

|   | A.1        | Package Types ····                                          | · 61  |

|   | A.2        | Package Information                                         | · 61  |

|   |            | APPENDIX B                                                  |       |

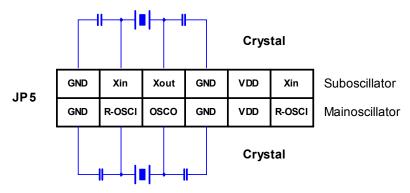

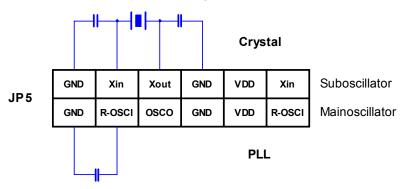

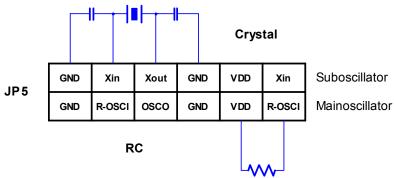

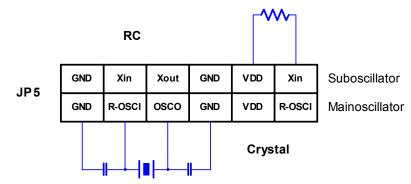

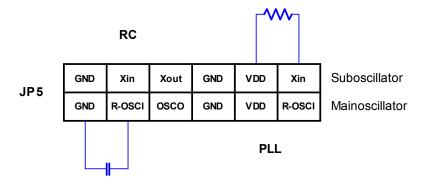

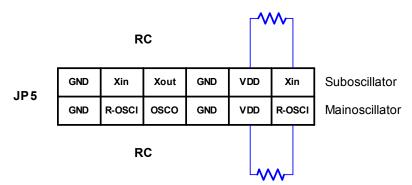

|   | B.1        | ICE 468XA Oscillator circuit (JP 5)                         |       |

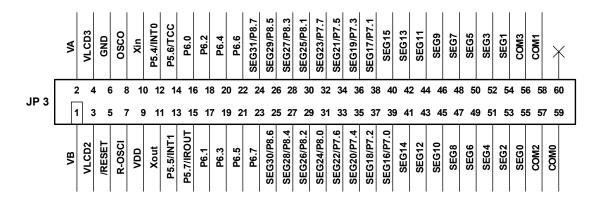

|   | B.2        | ICE 468XA output pin assignment (JP 3)·····                 | · 67  |

|         | Specification Revision History |             |  |  |  |  |  |  |  |  |  |

|---------|--------------------------------|-------------|--|--|--|--|--|--|--|--|--|

| Version | Revision Description           | Date        |  |  |  |  |  |  |  |  |  |

| 1.0     | Initial version                | 2005//03/02 |  |  |  |  |  |  |  |  |  |

| 1.1     | Add LQFP 64 package            | 2005/04/11  |  |  |  |  |  |  |  |  |  |

#### 1 GENERAL DESCRIPTION

This LSI is an 8-bit RISC type microprocessor with high speed CMOS technology and low power consumption. Integrated onto a single chip are on chip watchdog timer (WDT), Data RAM, ROM, programmable real time clock counter, internal/external interrupt, power down mode, LCD driver, infrared transmitter function, and tri-state I/O. The EM78468 provides a seven option bits to accommodate user's requirements.

#### 2 FEATURES

#### 2.1 CPU

- Operating voltage and temperature range:

- 2.2V ~ 5.5 V. (at 0°C ~+70°C)

- Operation speed: DC ~ 10MHz clock input.

- Dual clock operation

- High frequency oscillator can select among Crystal, RC, or PLL (phase lock loop)

- Low frequency oscillator can select between Crystal or RC mode

- Totally 272 bytes SRAM

- 144 bytes general purpose register

- 128 bytes on chip data RAM

- 4K\*13 bits MASK ROM

- Up to 28 bi-directional tri-state I/O ports

- Typically, 12 bi-directional tri-state I/O ports.

- 16 bi-directional tri-state I/O ports shared with LCD segment output pin.

- 8-level stack for subroutine nesting

- 8-bit real time clock/counter (TCC)

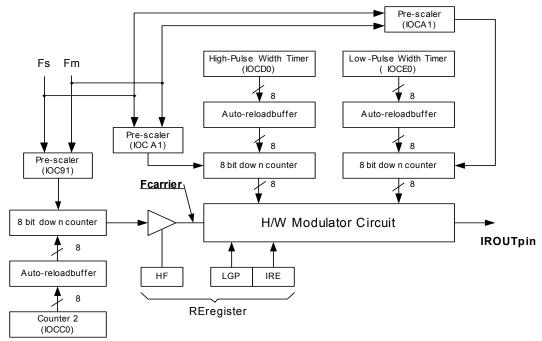

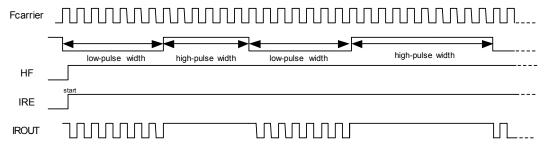

- One infrared transmitter/PWM generator function

- Four sets of 8 bits auto reload timer can be used as interrupt sources

- Counter 1: independent down-count timer.

- Counter 2, High Pulse Width Timer (HPWT), and Low Pulse Width Timer (LPWT) shared with IR function.

- Programmable free running on chip watchdog timer (WDT). This function can operate on Normal, Green and Idle mode.

查询"EM78468供应商 8-BIT Microcontroller

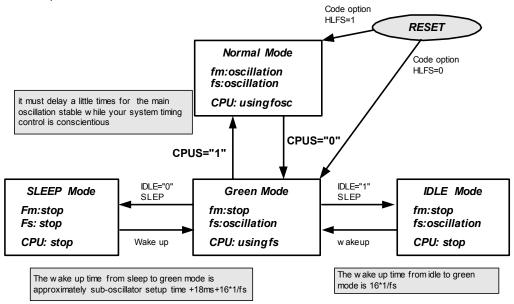

- Operation modes:

- Normal mode: The CPU operated on frequency of main oscillator (Fm)

- Green mode: The CPU operated on frequency sub-oscillator (Fs) and main oscillator (Fm) stop.

- Idle mode: CPU idle, LCD display remains working

- Sleep mode: whole chip stop working.

- Input port wake up function (PORT6, PORT8). Working on Idle and sleep mode.

- Eight interrupt sources, three external and five internal.

- Internal interrupt source : TCC; Counter 1,2; High/Low pulse width timer.

- External interrupt source: INT0, INT1 and Pin change wake-up (Port 6 and Port 8)

- Packages:

- Dice form : 59 pin

- QFP-64 pin : EM78468Q (Body 14mm\*20mm)

- LQFP-64 pin : EM78468AQ (Body 7mm\*7mm)

- LQFP-44 pin : EM78468BQ (Body 10mm\*10mm)

- QFP-44 pin : EM78468CQ (Body 10mm\*10mm)

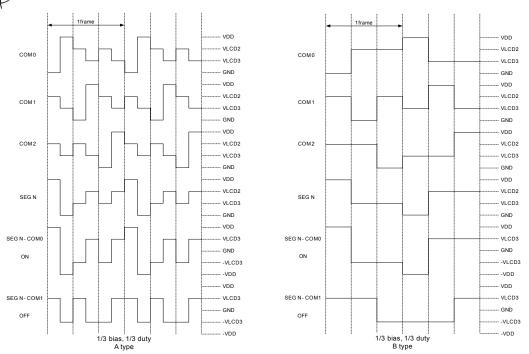

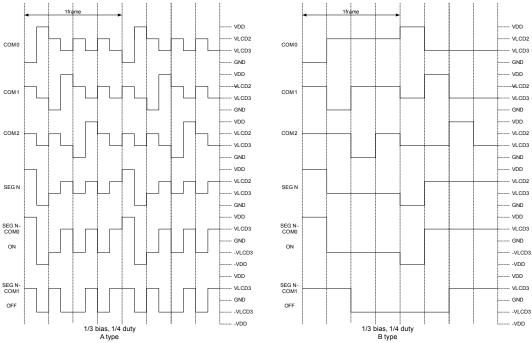

#### 2.2 LCD Circuit

- Common driver pins: 4

- Segment driver pins: 32

- LCD Bias: 1/3, 1/2 bias

- LCD Duty: 1/4, 1/3, 1/2 duty

#### 2.3 Applications

- Remote control for air conditioner

- Health care

- Home appliances

#### 3 PIN ASSIGNMENTS

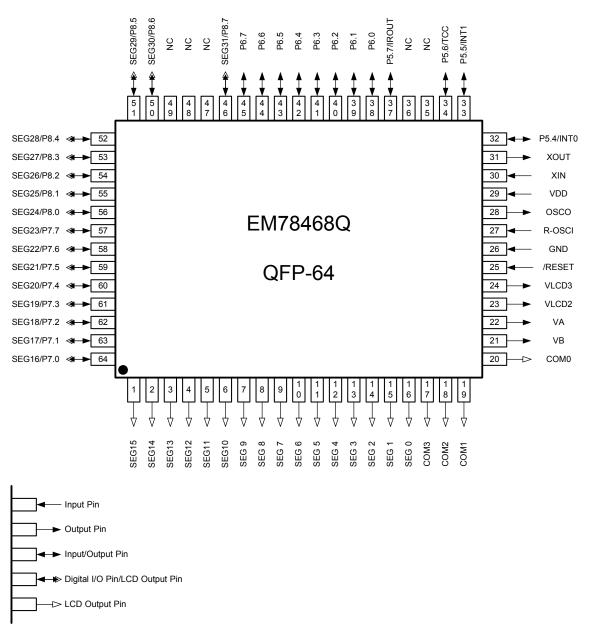

Fig. 1-(a) Pins Configuration for 64 Pin QFP Package

#### 3.2 LQFP - 64

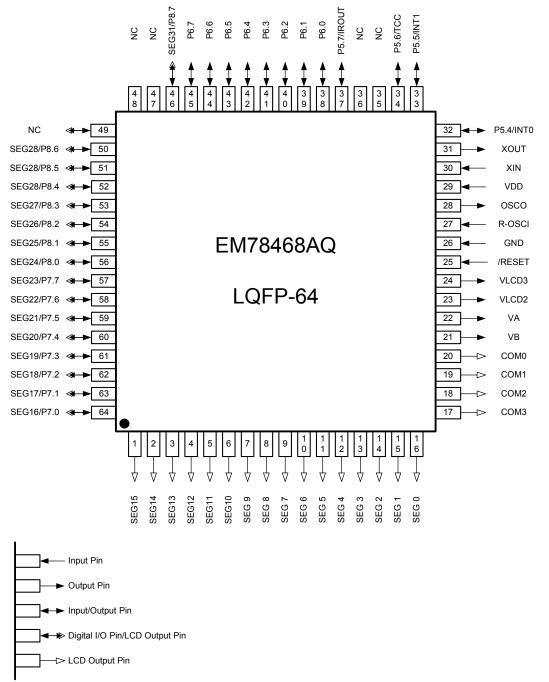

Fig. 1-(b) Pins Configuration for 64 Pin LQFP Package

#### 3.3 LQFP - 44

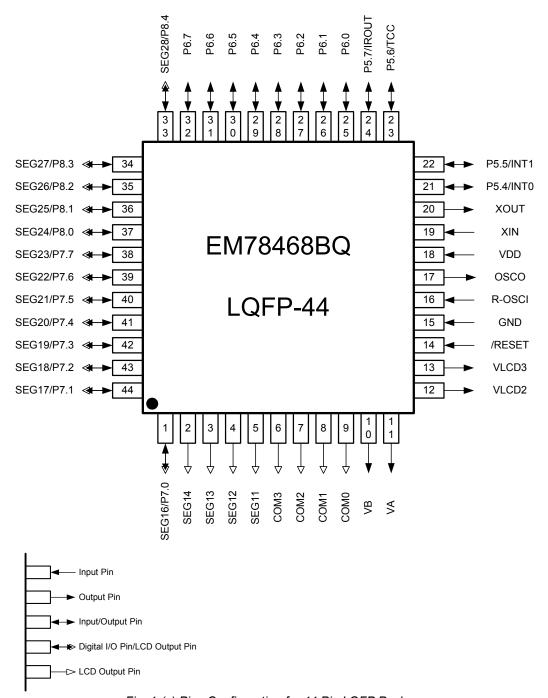

Fig. 1-(c) Pins Configuration for 44 Pin LQFP Package

#### 3.4 QFP - 44

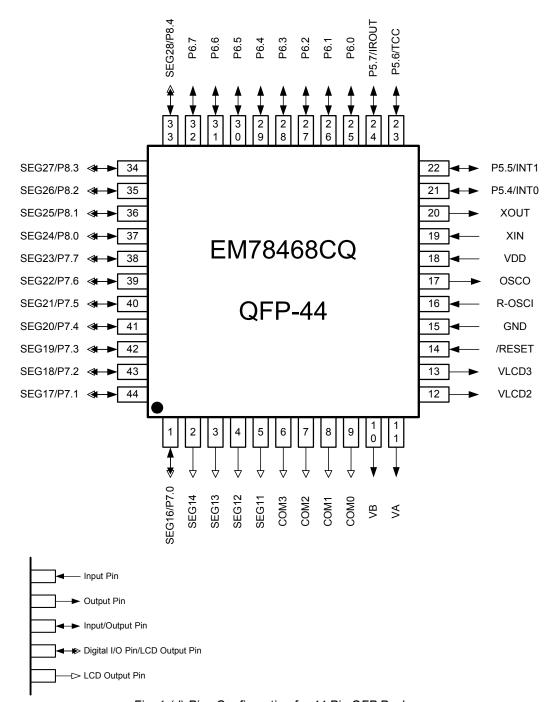

Fig. 1-(d) Pins Configuration for 44 Pin QFP Package

Table 1 (a) Pin Description for Package of QFP64 and LQFP64

|                                             | rable T (a) Pl      | n Description | for Package of QFP64 and LQFP64                                                                                                                                                                                                                                           |

|---------------------------------------------|---------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                         | Pin Number          | I/O type      | Description                                                                                                                                                                                                                                                               |

| VDD                                         | 29                  | I             | * Power supply pin                                                                                                                                                                                                                                                        |

| GND                                         | 26                  | I             | * System ground pin                                                                                                                                                                                                                                                       |

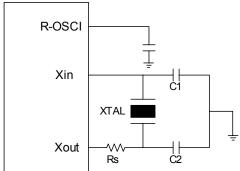

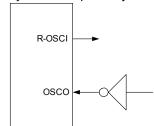

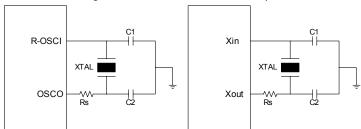

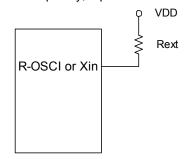

| R-OSCI                                      | 27                  | I             | <ul> <li>* In crystal mode: crystal input</li> <li>* In RC mode: resistor pull high.</li> <li>* In PLL mode: connect 0.01 μ F capacitance to GND</li> <li>* Connect 0.01 μ F capacitor to GND and code option select PLL mode when high oscillator is not use.</li> </ul> |

| osco                                        | 28                  | 0             | * In crystal mode: crystal output * In RC mode: instruction clock output                                                                                                                                                                                                  |

| Xin                                         | 30                  | I             | * In crystal mode:Input pin for sub-oscillator. Connect to a 32.768KHz crystal     * RC mode: this pin is connected with a resistor to high level.                                                                                                                        |

| Xout                                        | 31                  | 0             | * In crystal: Connect to a 32.768KHz crystal * In RC mode: instruction clock output                                                                                                                                                                                       |

| /RESET                                      | 25                  | I             | * Low active. If set as /RESET and remains at logic low, the devices will be reset                                                                                                                                                                                        |

| P5.4/INT0                                   | 32                  | I/O           | * General purpose I/O pin. /external interrupt.  * INT0 interruption source can be set to falling or rising edge by IOC71 register bit 7 (INT_EDGE).  * Wake up from sleep mode and idle mode when the pin status changes.                                                |

| P5.5/INT1                                   | 33                  | I/O           | * General purpose I/O pin. /external interrupt.  * Interruption source is a falling edge signal.  * Wake up from sleep mode and idle mode when the pin status changes.                                                                                                    |

| P5.6/TCC                                    | 34                  | I/O           | * General purpose I/O/ external counter input * This pin works in normal/green/idle mode.                                                                                                                                                                                 |

| P5.7/IROUT                                  | 37                  | I/O           | * General purpose I/O pin or IR/PWM mode output pin, * Capable of sinking 18mA/5V.                                                                                                                                                                                        |

| P6.0<br>~<br>P6.7                           | 38~45               | I/O           | * General purpose I/O pin.  * Pull-high, pull-low and open drain function support.  * All pins can wake up from sleep and idle modes when the pin status changes.                                                                                                         |

| COM3~0                                      | 17~20               | 0             | * LCD common output pin.                                                                                                                                                                                                                                                  |

| SEG0~SEG15                                  | 16~1                | 0             | * LCD segment output pin.                                                                                                                                                                                                                                                 |

| SEG16/P7.0<br>~<br>SEG23/P7.7               | 64<br>~<br>57       | O/(I/O)       | * LCD segment output pin. Can be shared with general purposes I/O pin                                                                                                                                                                                                     |

| SEG24/P8.0<br>~<br>SEG30/P8.6<br>SEG31/P8.7 | 56<br>~<br>50<br>46 | O/(I/O)       | * LCD segment output pin. Can be shared with general I/O pin     * For general purpose I/O use, can wake up from sleep mode and idle mode when the pin status changes.     * For general purposes I/O use, supports pull-high function.                                   |

| VB                                          | 21                  | 0             | * Connect capacitors for LCD bias voltage                                                                                                                                                                                                                                 |

| VA                                          | 22                  | 0             | * Connect capacitors for LCD bias voltage                                                                                                                                                                                                                                 |

| VLCD2                                       | 23                  | 0             | * One of LCD bias voltage                                                                                                                                                                                                                                                 |

| VLCD3                                       | 24                  | 0             | * One of LCD bias voltage                                                                                                                                                                                                                                                 |

| NC                                          | 35~36<br>47~49      |               |                                                                                                                                                                                                                                                                           |

Table 1 (b) Pin Description for Package of QFP44 and LQFP44

|                               |               |          | lor r ackage of Qr r 44 and EQr r 44                                                                                                                                                                                                                                        |

|-------------------------------|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                           | Pin Number    | I/O type | Description                                                                                                                                                                                                                                                                 |

| VDD                           | 18            | l        | * Power supply pin                                                                                                                                                                                                                                                          |

| GND                           | 15            | I        | * System ground pin                                                                                                                                                                                                                                                         |

| R-OSCI                        | 16            | I        | <ul> <li>* In crystal mode: crystal input</li> <li>* In RC mode: resistor pull high.</li> <li>* In PLL mode: connect 0.01 μ F capacitance to GND</li> <li>* Connect 0.01 μ F capacitance to GND and code option select PLL mode when high oscillator is not use.</li> </ul> |

| osco                          | 17            | 0        | * In crystal mode: crystal output * In RC mode: instruction clock output                                                                                                                                                                                                    |

| Xin                           | 19            | I        | * In crystal mode:Input pin for sub-oscillator. Connect to a 32.768KHz crystal * RC mode: this pin is connected with a resistor to high level.                                                                                                                              |

| Xout                          | 20            | 0        | * In crystal: Connect to a 32.768KHz crystal * In RC mode: instruction clock output                                                                                                                                                                                         |

| /RESET                        | 14            | I        | * Low active. If set as /RESET and remains at logic low, the devices will be reset                                                                                                                                                                                          |

| P5.4/INT0                     | 21            | I/O      | * General purpose I/O pin. /external interrupt.  * INT0 interruption source can be set to falling or rising edge by IOC71 register bit 7 (INT_EDGE).  * Wake up from sleep mode and idle mode when the pin status changes.                                                  |

| P5.5/INT1                     | 22            | I/O      | * General purpose I/O pin. /external interrupt.  * Interruption source is a falling edge signal.  * Wake up from sleep mode and idle mode when the pin status changes.                                                                                                      |

| P5.6/TCC                      | 23            | I/O      | * General purpose I/O/ external counter input * This pin works in normal/green/idle mode.                                                                                                                                                                                   |

| P5.7/IROUT                    | 24            | I/O      | * General purpose I/O pin or IR/PWM mode output pin,<br>* Capable of sinking 18mA/5V.                                                                                                                                                                                       |

| P6.0<br>~<br>P6.7             | 25~32         | I/O      | * General purpose I/O pin.  * Pull-high, pull-low and open drain function support.  * All pins can wake up from sleep and idle modes when the pin status changes.                                                                                                           |

| COM3~0                        | 6~9           | 0        | * LCD common output pin.                                                                                                                                                                                                                                                    |

| SEG11~SEG14                   | 5~2           | 0        | * LCD segment output pin.                                                                                                                                                                                                                                                   |

| SEG16/P7.0<br>SEG17/P7.1      | 1<br>44<br>~  | O/(I/O)  | * LCD segment output pin. Can be shared with general purposes I/O pin                                                                                                                                                                                                       |

| SEG23/P7.7                    | 38            |          | p.mpssss                                                                                                                                                                                                                                                                    |

| SEG24/P8.0<br>~<br>SEG31/P8.4 | 37<br>~<br>33 | O/(I/O)  | * LCD segment output pin. Can be shared with general I/O pin  * For general purpose I/O use, can wake up from sleep mode and idle mode when the pin status changes.                                                                                                         |

| VD                            | 10            |          | * For general purposes I/O use, supports pull-high function.                                                                                                                                                                                                                |

| VB<br>VA                      | 10<br>11      | 0        | Connect capacitors for LCD bias voltage     Connect capacitors for LCD bias voltage                                                                                                                                                                                         |

| VA<br>VLCD2                   | 12            | 0        | * One of LCD bias voltage                                                                                                                                                                                                                                                   |

|                               | ł             |          | * One of LCD bias voltage                                                                                                                                                                                                                                                   |

| VLCD3                         | 13            | 0        | One of LOD bias voltage                                                                                                                                                                                                                                                     |

#### 4 FUNCTION DESCRIPTION

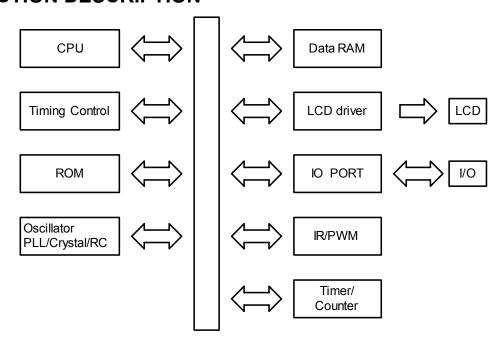

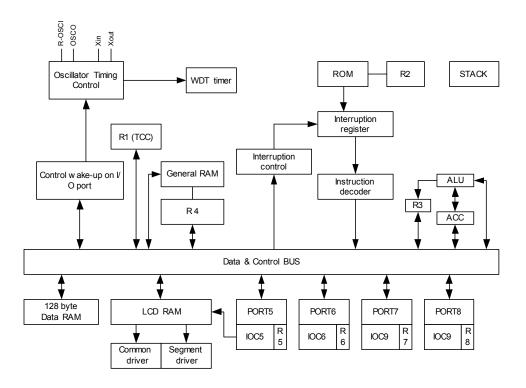

Fig. 2 System Block Diagram

#### 4.1 Operational Registers

### 4.1.1 R0/IAR (Indirect Addressing Register) (Address: 00h)

R0 is not a physically implemented register. It is used as indirect addressing pointer. Any instruction using R0 as register actually accesses the data pointed by the RAM Select Register (R4).

### 4.1.2 R1/TCC (Time Clock /Counter) (Address: 01h)

Increases by an external signal edge applied to TCC, or by the instruction cycle clock.

Written and read by the program as any other register.

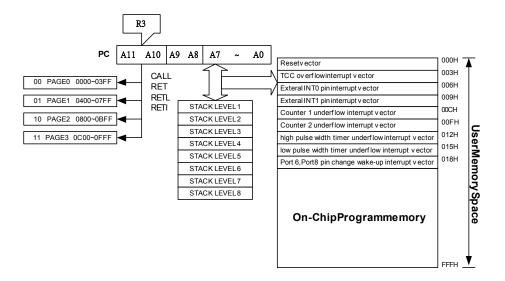

### 4.1.3 R2/PC (Program Counter) (Address: 02h)

- \* The structure is depicted in Fig. 3

- $^{\star}$  Generates 4K imes 13 on-chip ROM addresses to the relative programming instruction codes.

- \* "JMP" instruction allows direct loading of the low 10 program counter bits.

- \* "CALL" instruction loads the low 10 bits of the PC and PC+1, then push it into the stack.

- \* "RET" ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack.

- \* "MOV R2, A" allows the loading of an address from the A register to the PC. The contents of the ninth and tenth bits do not change.

- \* "ADD R2, A" allows a relative address be added to the current PC.

- \* The most significant bit (A10~A11) will be loaded with the content of bits PS0~PS1 in the Status register (R3) upon execution of a "JMP" or "CALL" instruction.

Fig. 3 Program Counter Organization

Product Specification (V1.1) 04.11.2005

### 4.1.4 R3/SR (Status Register) (Address: 03h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | PS1   | PS0   | Т     | Р     | Z     | DC    | С     |

Bit 7: Not used

Bit 6, 5 (PS1 ~ PS0): Page select bits

| PS1 | PS0 | ROM Page (Address)   |

|-----|-----|----------------------|

| 0   | 0   | Page 0 (000H ~ 3FFH) |

| 0   | 1   | Page 1 (400H ~ 7FFH) |

| 1   | 0   | Page 2 (800H ~ BFFH) |

| 1   | 1   | Page 3 (C00H ~ FFFH) |

PS0~PS1 are used to select a ROM page. User can use PAGE instruction (e.g. PAGE 1) or set PS1~PS0 bits to change ROM page. When executing a "JMP", "CALL", or other instructions which causes the program counter to be changed (e.g. MOV R2, A), PS0~PS1 are loaded into the 11th and 12th bits of the program counter where it selects one of the available program memory pages. Note that RET (RETL, RETI) instruction does not change the PS0~PS1 bits. That is, the return will always be to the page from where the subroutine was called, regardless of the current setting of PS0~PS1 bits.

**Bit 4 (T):** Time-out bit. Set to 1 by the "SLEP" and "WDTC" commands or during power up and reset to 0 by WDT timeout.

| EVENT                         | Т | Р | REMARK        |

|-------------------------------|---|---|---------------|

| WDT wake up from sleep mode   | 0 | 0 |               |

| WDT time out (not sleep mode) | 0 | 1 |               |

| /RESET wake up from sleep     | 1 | 0 |               |

| Power up                      | 1 | 1 |               |

| Low pulse on /RESET           | 1 | 1 | X: don't care |

**Bit 3 (P):** Power down bit. Set to 1 during power on or by a "WDTC" command and reset to 0 by a "SLEP" command.

Bit 2 (Z): Zero flag

Bit 1 (DC): Auxiliary carry flag.

Bit 0 (C): Carry flag

#### 4.1.5 R4/RSR (RAM Select Register)

(Address: 04h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RBS1  | RBS0  | RSR5  | RSR4  | RSR3  | RSR2  | RSR1  | RSR0  |

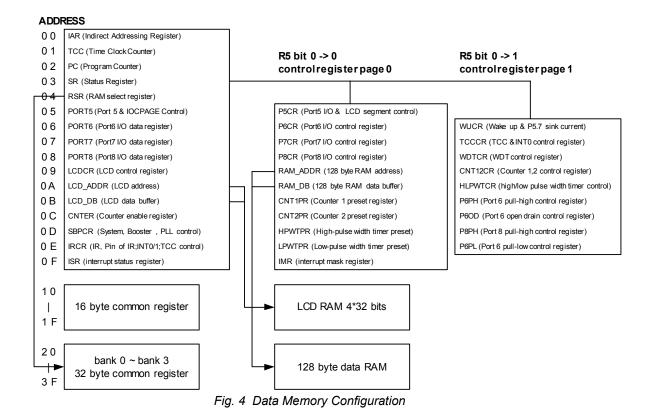

Bits 7 ~ 6 (RBS1 ~ RBS0) determine which bank is activated among the 4 banks. See the configuration of the data memory in Fig.4. Use BANK instruction (e.g. BABK 1) to change bank.

**Bits 5 ~ 0 (RSR 5 ~ RSR 0)** are used to select up to 64 registers (address: 00~3F) in the indirect addressing mode. If no indirect addressing is used, the RSR can be used as an 8-bit general purposes read/writer register.

### 4.1.6 R5/PORT5 (PORT 5 I/O Data and Page of Register Select) (Address: 05h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   |

|-------|-------|-------|-------|-------|-------|-------|---------|

| R57   | R56   | R55   | R54   |       |       |       | IOCPAGE |

Bit 7~4: 4-bits I/O registers of PORT5

User can use IOC50 register to define input or output each bit.

Bit 3~1: Not used

Bit 0 (IOCPAGE): change IOC5 ~ IOCF to another page, 0/1 => page0 / page1

**IOCPAGE = "0":** Page 0 (select register of IOC50 to IOCF0)

IOCPAGE = "1": Page 1 (select register of IOC61 to IOCE1)

#### 4.1.7 R6/PORT6 (PORT 6 I/O Data Register)

(Address: 06h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| R67   | R66   | R65   | R64   | R63   | R62   | R61   | R60   |

Bit 7~0: 8-bit I/O registers of PORT 6

User can use IOC60 register to define input or output each bit.

#### 4.1.8 R7/PORT7 (PORT 7 I/O Data Register)

(Address: 07h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| R77   | R76   | R75   | R74   | R73   | R72   | R71   | R70   |

Bit 7~0: 8-bit I/O registers of PORT 7

User can use IOC70 register to define input or output each bit.

#### 4.1.9 R8/PORT8 (PORT 8 I/O Data Register)

(Address: 08h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| R87   | R86   | R85   | R84   | R83   | R82   | R81   | R80   |

Bit 7~0: 8-bit I/O registers of PORT 8

User can use IOC80 register to define input or output each bit.

#### 4.1.10 R9/LCDCR (LCD Control Register)

(Address: 09h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|---------|-------|-------|

| BS    | DS1   | DS0   | LCDEN |       | LCDTYPE | LCDF1 | LCDF0 |

Bit 7 (BS): LCD bias select bit,

**BS = "0":** 1/2 bias

**BS = "1":** 1/3 bias

Bit 6 ~ 5 (DS1 ~ DS0): LCD duty select

| DS1 | DS0 | LCD duty |  |  |

|-----|-----|----------|--|--|

| 0   | 0   | 1/2 duty |  |  |

| 0   | 1   | 1/3 duty |  |  |

| 1   | Х   | 1/4 duty |  |  |

Bit 4 (LCDEN): LCD enable bit.

**LCDEN = "0":** LCD circuit disable, all common/segment outputs are set to ground (GND) level.

LCDEN = "1": LCD circuit enable

Bit 3: Not used

Bit 2 (LCDTYPE): LCD drive waveform type select bit

LCDTYPE = "0": A type waveform

**LCDTYPE = "1":** B type waveform

Bit 1 ~ 0 (LCDF1 ~ LCDF0): LCD frame frequency control bits

| LCDF1 | LCDF0 | LCD frame frequency (e.g. Fs=32.768KHz) |                 |                  |  |  |  |

|-------|-------|-----------------------------------------|-----------------|------------------|--|--|--|

| LODFI | LODFO | 1/2 duty                                | 1/3 duty        | 1/4 duty         |  |  |  |

| 0     | 0     | Fs/(256*2)=64.0                         | Fs/(172*3)=63.5 | Fs/(128*4) =64.0 |  |  |  |

| 0     | 1     | Fs/(280*2)=58.5                         | Fs/(188*3)=58.0 | Fs/(140*4) =58.5 |  |  |  |

| 1     | 0     | Fs/(304*2)=53.9                         | Fs/(204*3)=53.5 | Fs/(152*4) =53.9 |  |  |  |

| 1     | 1     | Fs/(232*2)=70.6                         | Fs/(156*3)=70.0 | Fs/(116*4) =70.6 |  |  |  |

Fs: sub-oscillator frequency

#### 4.1.11 RA/LCD\_ADDR (LCD Address)

(Address: 0Ah)

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| 0     | 0     | 0     | LCD_A4 | LCD_A3 | LCD_A2 | LCD_A1 | LCD_A0 |

Bit 7 ~ 5: Not used, fixed to "0"

Bit 4 ~ 0 (LCDA4 ~ LCDA0): LCD RAM address

| RA            |          | RB (L             |                   |                   |                   |         |

|---------------|----------|-------------------|-------------------|-------------------|-------------------|---------|

| (LCD address) | Bit 7 ~4 | Bit 3<br>(LCD_D3) | Bit 2<br>(LCD_D2) | Bit 1<br>(LCD_D1) | Bit 0<br>(LCD_D0) | Segment |

| 00H           |          |                   |                   |                   |                   | SEG0    |

| 01H           |          |                   |                   |                   |                   | SEG1    |

| 02H           |          |                   |                   |                   |                   | SEG2    |

| I             |          |                   |                   |                   | I                 |         |

| 1DH           | 1        |                   |                   |                   |                   | SEG29   |

| 1EH           | 1        |                   |                   |                   |                   | SEG30   |

| 1FH           | 1        |                   |                   |                   |                   | SEG31   |

| Common        | Х        | СОМЗ              | COM2              | COM1              | COM0              |         |

#### 4.1.12 RB/LCD\_DB (LCD Data Buffer)

(Address: 0Bh)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-------|-------|-------|-------|---------|---------|---------|---------|

|       |       |       |       | LCD_D 3 | LCD_D 2 | LCD_D 1 | LCD_D 0 |

Bit 7 ~ 4: Not used

Bit 3~0 (LCD\_D3 ~ LCD\_D0): LCD RAM data transfer register

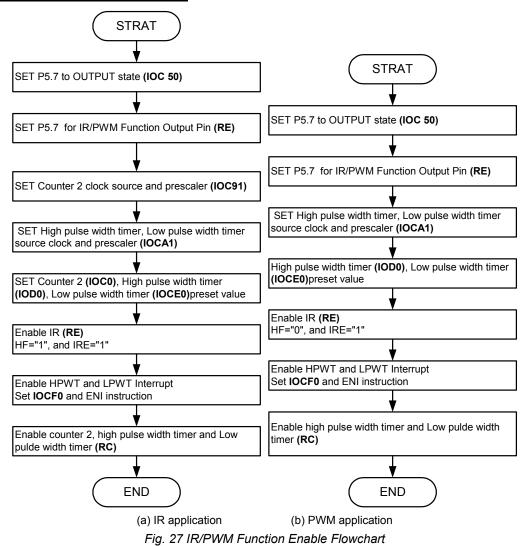

#### 4.1.13 RC/CNTER (Counter Enable Register)

(Address: 0Ch)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

|       |       |       |       | LPWTEN | HPWTEN | CNT2EN | CNT1EN |

Bit 7,5: Not used, must fixed to "0"

Bit 6,4: Not used

Bit 3(LPWTEN): low pulse width timer enable bit,

**LPWTEN = "0":** Disable LPWT. Count operation stop.

**LPWTEN = "1":** Enable LPWT. Count operation start.

Bit 2(HPWTEN): high pulse width timer enable bit

**HPWTEN = "0":** Disable HPWT. Count operation stop.

**HPWTEN = "1":** Enable HPWT. Count operation start.

Bit 1(CNT2EN): counter 2 enable bit

**CNT2EN = "0":** Disable Counter 2. Count operation stop.

**CNT2EN = "1":** Enable Counter 2. Count operation start.

Bit 0(CNT1EN): counter 1 enable bit

**CNT1EN = "0":** Disable Counter 1. Count operation stop.

**CNT1EN = "1":** Enable Counter 1. Count operation start.

### 4.1.14 RD/SBPCR (System, Booster and PLL Control Register) (Address: 0Dh)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | CLK2  | CLK1  | CLK0  | IDLE  | BF1   | BF0   | CPUS  |

Bit 7: Not used

Bit 6 ~ 4 (CLK2 ~ CLK0): main clock selection bits for PLL mode (code option select)

| CLK2 | CLK1 | CLK0 | Main clock | Example Fs=32.768K |

|------|------|------|------------|--------------------|

| 0    | 0    | 0    | Fs*130     | 4.26 MHz           |

| 0    | 0    | 1    | Fs*65      | 2.13 MHz           |

| 0    | 1    | 0    | Fs*65/2    | 1.065 MHz          |

| 0    | 1    | 1    | Fs*65/4    | 532 KHz            |

| 1    | Х    | Х    | Fs*244     | 8 MHz              |

**Bit 3 (IDLE):** idle mode enable bit. This bit will decide the intended mode of the SLEP instruction.

IDLE="0"+SLEP instruction => sleep mode

IDLE="1"+SLEP instruction => idle mode

Example:IDLE mode: IDLE bit = "1" +SLEP instruction + NOP instruction

SLEEP mode: IDLE bit = "0" +SLEP instruction + NOP instruction

Bit 2 ~ 1 (BF1 ~ BF0): LCD booster frequency select bit to adjust VLCD 2,3 driving.

| BF1 | BF0 | Booster frequency |  |  |

|-----|-----|-------------------|--|--|

| 0   | 0   | Fs                |  |  |

| 0   | 1   | Fs/4              |  |  |

| 1   | 0   | Fs/8              |  |  |

| 1   | 1   | Fs/16             |  |  |

**Bit 0 (CPUS):** CPU oscillator source select, When CPUS=0, the CPU oscillator select sub-oscillator and the main oscillator is stopped.

CPUS = "0": sub-oscillator (Fs)

CPUS = "1": main oscillator (Fm)

<sup>\*</sup> NOP instruction must be added after SLEP instruction.

#### **CPU Operation Mode**

Fig. 5 CPU Operation Mode

### 4.1.15 RE/IRCR (IR and PORT 5 Setting Control Register) (Address: 0Eh)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

| IRE   | HF    | LGP   |       | IROUTE | TCCE  | EINT1 | EINT0 |

Bit 7 (IRE): Infrared Remote Enable bit

**IRE = "0":** Disable IR/PWM function. The state of P5.7/IROUT pin is determined by bit 7 of IOC50 if it's for IROUT.

IRE = "1": Enable IR or PWM function.

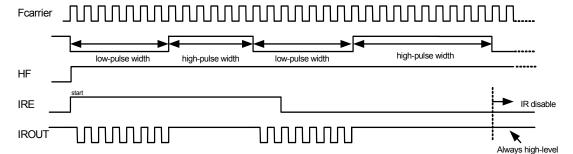

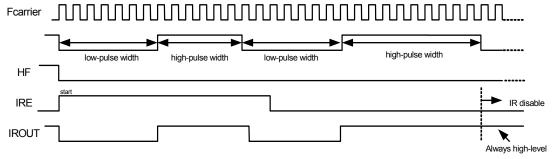

Bit 6 (HF): High carry frequency.

**HF = "0":** For PWM application, disable H/W modulator function. IROUT waveform is created according to high-pulse and low-pulse time as determined by the high pulse and low pulse width timers respectively. The counter 2 is an independent auto reload timer.

**HF = "1":** For IR application mode, enable H/W modulator function, the low time sections of the generated pulse is modulated with the frequency Fcarrier. The frequency of Fcarrier provide by counter 2.

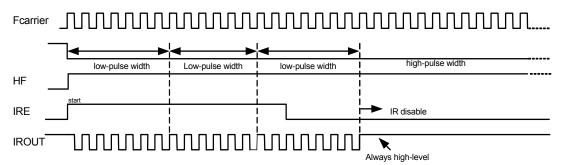

Bit 5 (LGP): IROUT for long time of low pulse.

**LGP = "0":** The high-pulse width timer register and low-pulse width timer is valid.

**LGP = "1":** The high-pulse width timer register is ignored. So the IROUT waveform is dependent on low-pulse width timer register only.

Bit 4: Not used

查询"E**FM78468**供应商

Bit 3 (IROUTE): Define the function of P5.7/IROUT pin.

**IROUTE = "0":** for bi-directional general I/O pin.

**IROUTE = "1":** for IR or PWM output pin, the control bit of P5.7 (bit 7 of IOC50) must be set to "0"

Bit 2 (TCCE): Define the function of P5.6/TCC pin.

**TCCE = "0":** for bi-directional general I/O pin.

**TCCE = "1":** for external input pin of TCC, the control bit of P5.6 (bit 6 of IOC50) must be set to "1"

Bit 1 (EINT1): Define the function of P5.5/INT1 pin.

**EINT1 = "0":** for bi-directional general I/O pin.

**EINT1 = "1":** for external interrupt pin of INT1, the control bit of P5.5 (bit 5 of IOC50) must be set to "1"

Bit 0 (EINT0): Define the function of P5.4/INT0 pin.

**EINT0 = "0":** for bi-directional general I/O pin.

**EINTO = "1":** for external interrupt pin of INTO, the control bit of P5.4 (bit 4 of IOC50) must be set to "1"

#### 4.1.16 Address: 0Fh; RF/ISR (Interrupt Status Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ICIF  | LPWTF | HPWTF | CNT2F | CNT1F | INT1F | INT0F | TCIF  |

These bits are set to "1" when interrupt occurs respectively.

**Bit 7 (ICIF):** PORT 6, PORT 8, input status changed interrupt flag. Set when PORT6, PORT8 input changes.

Bit 6 (LPWTF): interrupt flag of internal low-pulse width timer underflow.

Bit 5 (HPWTF): interrupt flag of internal high-pulse width timer underflow.

Bit 4 (CNT2F): interrupt flag of internal counter 2 under-flow.

Bit 3 (CNT1F): interrupt flag of internal counter 1 underflow.

Bit 2 (INT1F): external INT1 pin interrupt flag.

Bit 1 (INT0F): external INT0 pin interrupt flag.

Bit 0 (TCIF): TCC timer overflow interrupt flag. Set when TCC timer overflows.

#### 4.1.17 Address: 10h~3Fh;R10~R3F (General Purpose Register)

R10~R31F and R20~R3F (Banks 0~3) are general purposes register.

#### 4.2 Special Purpose Registers

#### 4.2.1 A (Accumulator)

- Internal data transfer, or instruction operand holding

- This is not an addressable register.

Registers of IOC Page 0 (IOC50 ~ IOCF0, Bit 0 of R5 = "0")

### 4.2.2 IOC50/P5CR (PORT 5 I/O and PORT 7, 8 for LCD Segment Control Register)

(Address: 05h,  $Bit\ 0\ of\ R5 = "0")$

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC57 | IOC56 | IOC55 | IOC54 | P8HS  | P8LS  | P7HS  | P7LS  |

Bit 7~4(IOC57~54): PORT 5 I/O direction control register

**IOC5x = "0":** set the relative P5.x I/O pins as output

IOC5x = "1": set the relative P5.x I/O pin into high impedance (input pin)

**Bit 3(P8HS):** Switch to high nibble I/O of PORT 8 or to LCD segment output as share pins SEGxx/P8.x pins

P8HS = "0": select high nibble of PORT 8 as normal P8.4~P8.7

P8HS = "1": select LCD SEGMENT output as SEG 28~SEG 31 output

**Bit 2(P8LS):** Switch to low nibble I/O of PORT 8 or to LCD segment output as share pins SEGxx/P8.x pins

P8LS = "0": select low nibble of PORT 8 as normal P8.0~P8.3

P8LS = "1": select LCD SEGMENT output as SEG 24~SEG 27 output

**Bit 1(P7HS):** Switch to high nibble I/O of PORT 7 or to LCD segment output as share pins SEGxx/P7.x pins

P7HS = "0": select high nibble of PORT 7 as normal P7.4~P7.7

P7HS = "1": select LCD SEGMENT output as SEG 20~SEG 23 output

**Bit 0(P7LS):** Switch to low nibble I/O of PORT 7 or to LCD segment output as share pins SEGxx/P7.x pins

P7LS = "0": select low nibble of PORT 7 as normal P7.0~P7.3

P7LS = "1": select LCD SEGMENT output as SEG 16~SEG 19 output

#### 4.2.3 IOC60/P6CR (PORT 6 I/O Control Register)

(Address: 06h, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC67 | IOC66 | IOC65 | IOC64 | IOC63 | IOC62 | IOC61 | IOC60 |

查询"EN 8468 供应商

Bit 7 (IOC67)~Bit 0(IOC60): PORT 6 I/O direction control register

IOC6x ="0": set the relative PORT6.x I/O pins as output

**IOC6x ="1":** set the relative PORT6.x I/O pin into high impedance (input pin)

### 4.2.4 IOC70/P7CR (PORT 7 I/O Control Register) (Address: 07h, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC77 | IOC76 | IOC75 | IOC74 | IOC73 | IOC72 | IOC71 | IOC70 |

Bit 7 (IOC77)~Bit 0(IOC70): PORT 7 I/O direction control register

IOC7x = "0": set the relative PORT7.x I/O pins as output

**IOC7x = "1":** set the relative PORT7.x I/O pin into high impedance (input pin)

### 4.2.5 IOC80/P8CR (PORT 8 I/O Control Register) (Address: 08h, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC87 | IOC86 | IOC85 | IOC84 | IOC83 | IOC82 | IOC81 | IOC80 |

Bit 7 (IOC 87)~Bit 0(IOC 80): PORT 8 I/O direction control register

IOC8x = "0": set the relative PORT8.x I/O pins as output

**IOC8x = "1":** set the relative PORT8.x I/O pin into high impedance (input pin)

### 4.2.6 IOC90/RAM\_ADDR (128 Bytes General Purpose RAM Address) (Address: 09h, Bit 0 of R5 = "0")

| Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| 0     | RAM_A6 | RAM_A5 | RAM_A4 | RAM_A3 | RAM_A2 | RAM_A1 | RAM_A0 |

Bit 7: Not used, fixed at "0"

Bit 6~0: 128 bytes RAM address

### 4.2.7 IOCA0/RAM\_DB (128 Bytes General Purpose RAM Data Buffer) (Address: 0Ah, Bit 0 of R5 = "0")

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RAM_D7 | RAM_D6 | RAM_D5 | RAM_D4 | RAM_D3 | RAM_D2 | RAM_D1 | RAM_D0 |

Bit 7~0: 128 bytes RAM data transfer register

### 4.2.8 IOCB0/CNT1PR (Counter 1 Preset Register) (Address: 0Bh. Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

Bit 7 ~ Bit 0: All are Counter 1 buffer that user can read and write. The Counter 1 is an 8-bit down-count timer/counter with 8-bit pre-scaler that is used as this register to preset

the counter and read preset value. The pre-scaler is set by IOC91 register. After an interruption, it will auto reload the preset value.

### 4.2.9 IOCCO/CNT2PR (Counter 2 Preset Register) (Address: 0Ch, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

**Bit 7 ~ Bit 0:** All are Counter 2 buffer that user can read and write. The Counter 2 is an 8-bit down-count timer with 8-bit pre-scaler that is used as this register to preset the counter and read preset value. The pre-scaler is set by IOC91 register. After an interruption, it will reload the preset value.

When IR output is enabled, this control register can obtain carrier frequency output.

If the Counter 2 clock source is equal to F<sub>T</sub>-

Carrier frequency (Fcarrier) =

$$\frac{F_T}{2 * (preset \_ value + 1) * prescaler}$$

### 4.2.10 IOCD0/HPWTPR (High-Pulse Width Timer Preset Register) (Address: 0Dh, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

**Bit 7 ~ Bit 0:** All are high-pulse width timer buffer that user can read and write. High-pulse width timer preset register is an eight-bit down-count timer with 8-bit pre-scaler that is used as IOCD0 to preset the counter and read preset value. The pre-scaler is set by IOCA1 register. After an interruption, it will reload the preset value.

For PWM or IR application, this control register is set as high pulse width.

If the high-pulse width timer source clock is  $F_T$  –

High pulse time =

$$\frac{\text{prescaler * (preset \_ value + 1)}}{F_{T}}$$

### 4.2.11 IOCE0/LPWTPR (Low-Pulse Width Timer Preset Register) (Address: 0Eh, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

Bit 7 ~ Bit 0: All are low-pulse width timer buffer that user can read and write. Low-pulse width timer preset is an eight-bit down-count timer with 8-bit pre-scaler that is used as IOCE0 to preset the counter and read preset value. The pre-scaler is set by IOCA1 register. After an interruption, it will reload the preset value.

For PWM or IR application, this control register is set as low pulse width.

If the low-pulse width timer source clock is F<sub>T</sub>-

查询"E**FM78468**供应商

Low pulse time =

$$\frac{prescaler * (preset \_value + 1)}{F_T}$$

#### 4.2.12 IOCF0/IMR (Interrupt Mask Register)

(Address: 0Fh, Bit 0 of R5 = "0")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ICIE  | LPWTE | HPWTE | CNT2E | CNT1E | INT1E | INT0E | TCIE  |

Bit 7~Bit 0: interrupt enable bit. Enable interrupt source respectively.

0: disable interrupt

1: enable interrupt

IOCF0 register is readable and writable.

#### Registers of IOC Page 1 (IOC61 ~ IOCE1, Bit 0 of R5 = "1")

### 4.2.13 IOC61/WUCR (Wake Up and sink current of P5.7/IROUT Control Register)

(Address: 06h, Bit 0 of R5 = "1")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| IROCS |       |       |       | /WUE8H | /WUE8L | /WUE6H | /WUE6L |

Bit 7: IROCS: IROUT/PORT5.7 output sink current set

| Dit 11 INCOC: INCO 1/1 CINTOC CUIPAR CHING CAITCHE CON |                         |        |  |  |  |  |

|--------------------------------------------------------|-------------------------|--------|--|--|--|--|

| IROCS                                                  | P5.7/IROUT Sink current |        |  |  |  |  |

| IIKOOO                                                 | VDD=5V                  | VDD=3V |  |  |  |  |

| 0                                                      | 9 mA                    | 6 mA   |  |  |  |  |

| 1                                                      | 18 mA                   | 12 mA  |  |  |  |  |

Bit 6,5,4: Not used

Bit 3 (/WUE8H): 0/1=> enable/disable P8.4~P8.7 pin change wake up function

Bit 2 (/WUE8L): 0/1=> enable/disable P8.0~P8.3 pin change wake up function

Bit 1 (/WUE6H): 0/1=> enable/disable P6.4~P6.7 pin change wake up function

Bit 0 (/WUE6L): 0/1=> enable/disable P6.0~P6.3 pin change wake up function

Port 6 and Port 8 must avoid input floating when wakeup function is enabled.

The initial state of wakeup function is enabled.

#### 4.2.14 IOC71/TCCCR (TCC Control Register)

(Address: 07h, Bit 0 of R5 = "1")

| Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| INT_EDGE | INT   | TS    | TE    | PSRE  | TCCP2 | TCCP1 | TCCP0 |

Bit 7 (INT\_EDGE):

**INT\_EDGE = "0":** Interrupt on rising edge of P5.4/INT0 pin

**INT\_EDGE = "1":** Interrupt on falling edge of P5.4/INT0 pin

Bit 6 (INT): INT enable flag, this bit is read only

INT = "0": interrupt masked by DISI or hardware interrupt

INT = "1": interrupt enabled by ENI/RETI instructions

Bit 5 (TS): TCC signal source

TS = "0": internal instruction cycle clock

TS = "1": transition on TCC pin, TCC period > internal instruction clock period

Bit 4 (TE): TCC signal edge

**TE = "0":** increment by TCC pin rising edge

TE = "1": increment by TCC pin falling edge

#### Bit 3~0 (PSRE, TCCP2~TCCP0): TCC pre-scaler bits.

| PSRE | TCCP2 | TCCP1 | TCCP0 | TCC Rate |

|------|-------|-------|-------|----------|

| 0    | X     | X     | X     | 1:1      |

| 1    | 0     | 0     | 0     | 1:2      |

| 1    | 0     | 0     | 1     | 1:4      |

| 1    | 0     | 1     | 0     | 1:8      |

| 1    | 0     | 1     | 1     | 1:16     |

| 1    | 1     | 0     | 0     | 1:32     |

| 1    | 1     | 0     | 1     | 1:64     |

| 1    | 1     | 1     | 0     | 1:128    |

| 1    | 1     | 1     | 1     | 1:256    |

#### 4.2.15 IOC81/WDTCR (WDT Control Register)

(Address: 08h, Bit 0 of R5 = "1")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       |       | WDTE  | WDTP2 | WDTP1 | WDTP0 |

Bit 7 ~ 4:Not used

**Bit 3 (WDTE):** watchdog timer enable. This control bit is used to enable the Watchdog timer,

WDTE = "0": Disable WDT function.

WDTE = "1": enable WDT function.

Bit  $2 \sim 0$  (WDTP2  $\sim$  WDTP0): watchdog timer pre-scaler bits. The WDT source clock is sub-oscillation frequency.

| WDTP2 | WDTP1 | WDTP0 | WDT rate |

|-------|-------|-------|----------|

| 0     | 0     | 0     | 1:1      |

| 0     | 0     | 1     | 1:2      |

| 0     | 1     | 0     | 1:4      |

| 0     | 1     | 1     | 1:8      |

| 1     | 0     | 0     | 1:16     |

| 1     | 0     | 1     | 1:32     |

| 1     | 1     | 0     | 1:64     |

| 1     | 1     | 1     | 1:128    |

### 4.2.16 IOC91/CNT12CR (Counter 1, 2 Control Register) (Address: 09h, Bit 0 of R5 = "1")

| Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|-------|--------|--------|--------|

| CNT2S | CNT2P2 | CNT2P1 | CNT2P0 | CNT1S | CNT1P2 | CNT1P1 | CNT1P0 |

Bit 7(CNT2S):Counter 2 clock source select 0/1 => Fs/ Fm\*

(\*Fs: sub-oscillator clock, Fm: main-oscillator clock)

Bit 6~4(CNT2P2~CNT2P0): Counter 2 pre-scaler select bits

| bit o 4(citizi z citizi o). Counter z pre sociel select bits |        |        |                 |  |  |  |  |  |

|--------------------------------------------------------------|--------|--------|-----------------|--|--|--|--|--|

| CNT2P2                                                       | CNT2P1 | CNT1P0 | Counter 2 scale |  |  |  |  |  |

| 0                                                            | 0      | 0      | 1:2             |  |  |  |  |  |

| 0                                                            | 0      | 1      | 1:4             |  |  |  |  |  |

| 0                                                            | 1      | 0      | 1:8             |  |  |  |  |  |

| 0                                                            | 1      | 1      | 1:16            |  |  |  |  |  |

| 1                                                            | 0      | 0      | 1:32            |  |  |  |  |  |

| 1                                                            | 0 1    |        | 1:64            |  |  |  |  |  |

| 1                                                            | 1      | 0      | 1:128           |  |  |  |  |  |

| 1                                                            | 1      | 1      | 1:256           |  |  |  |  |  |

Bit 3(CNT1S):Counter 1 clock source select 0/1 => Fs/ Fm

Bit 2~0 (CNT1P2~CNT1P0): Counter 1 pre-scaler select bits

| те с ( |               |   |                 |  |  |  |  |  |

|--------|---------------|---|-----------------|--|--|--|--|--|

| CNT1P2 | CNT1P2 CNT1P1 |   | Counter 1 scale |  |  |  |  |  |

| 0      | 0             | 0 | 1:2             |  |  |  |  |  |

| 0      | 0             | 1 | 1:4             |  |  |  |  |  |

| 0      | 1             | 0 | 1:8             |  |  |  |  |  |

| 0      | 1             | 1 | 1:16            |  |  |  |  |  |

| 1      | 0             | 0 | 1:32            |  |  |  |  |  |

| 1      | 1 0           |   | 1:64            |  |  |  |  |  |

| 1      | 1             | 0 | 1:128           |  |  |  |  |  |

| 1      | 1             | 1 | 1:256           |  |  |  |  |  |

### 4.2.17 IOCA1/HLPWTCR (High/Low Pulse Width Timer Control Register)

(Address: 0Ah, Bit 0 of R5 = "1")

| Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|-------|--------|--------|--------|

| LPWTS | LPWTP2 | LPWTP1 | LPWTP0 | HPWTS | HPWTP2 | HPWTP1 | HPWTP0 |

Bit 7(LPWTS): low-pulse width timer clock source select 0/1 -> Fs/ Fm\*

(\*Fs: sub-oscillator clock, Fm: main-oscillator clock)

Bit 6~4 (LPWTP2~ LPWTP0): low-pulse width timer pre-scaler select bits

| LPWTP2 | LPWTP1 | LPWTP0 | Low-pulse width timer scale |

|--------|--------|--------|-----------------------------|

| 0      | 0      | 0      | 1:2                         |

| 0      | 0      | 1      | 1:4                         |

| 0      | 1      | 0      | 1:8                         |

| 0      | 1      | 1      | 1:16                        |

| 1      | 0      | 0      | 1:32                        |

| 1      | 0      | 1      | 1:64                        |

| 1      | 1      | 0      | 1:128                       |

| 1      | 1      | 1      | 1:256                       |

Bit 3(HPWTS): high-pulse width timer clock source select 0/1 -> Fs/ Fm

Bit 2~0(HPWTP2~ HPWTP0): high-pulse width timer pre-scaler select bits

| HPWTP2 | HPWTP1 | HPWTP0 | High-pulse width timer scale |

|--------|--------|--------|------------------------------|

| 0      | 0      | 0      | 1:2                          |

| 0      | 0      | 1      | 1:4                          |

| 0      | 1      | 0      | 1:8                          |

| 0      | 1      | 1      | 1:16                         |

| 1      | 0      | 0      | 1:32                         |

| 1      | 0      | 1      | 1:64                         |

| 1      | 1      | 0      | 1:128                        |

| 1      | 1      | 1      | 1:256                        |

### 4.2.18 IOCB1/P6PH (PORT 6 Pull High Control Register)

(Address: 0Bh, Bit 0 of R5 = "1")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PH67  | PH66  | PH65  | PH64  | PH63  | PH62  | PH61  | PH60  |

Bit 7 ~ Bit 0 (PH67 ~ PH60): The enable bits of PORT 6 pull high function.

**PH6x = "0":** disable pin of P6.x internal pull-high resistor function

**PH6x = "1":** enable pin of P6.x internal pull-high resistor function

### 4.2.19 IOCC1/P6OD (PORT 6 Open Drain Control Register) (Address: 0Ch, Bit 0 of R5 = "1")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

| OP67  | OP66  | OP65  | OP64  | OP63  | OP62  | OP61  | OP60  |  |

Bit 7 ~ Bit 0: The enable bits of PORT 6 open drain function.

**OD6x = "0":** disable pin of P6.x open drain function

**OD6x = "1":** enable pin of P6.x open drain function

### 4.2.20 IOCD1/P8PH (PORT 8 Pull High Control Register) (Address: 0Dh, Bit 0 of R5 = "1")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PH87  | PH86  | PH85  | PH84  | PH83  | PH82  | PH81  | PH80  |

Bit 7 ~ Bit 0: The enable bits of PORT 8 pull-high function.

**PH8x = "0":** disable pin of P8.x internal pull-high resistor function

PH8x = "1": enable pin of P8.x pull-high resistor function

### 4.2.21 IOCE1/P6PL (PORT 6 Pull-Low Control Register) (Address: 0Eh, Bit 0 of R5 = "1")

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

| PL67  | PL66  | PL65  | PL64  | PL63  | PL62  | PL61  | PL60  |  |

Bit 7 ~ Bit 0: The enable bits of PORT 6 pull low function.

**PL6x = "0":** disable pin of P6.x internal pull-low resistor function

**PL6x = "1":** enable pin of P6.x internal pull-low resistor function

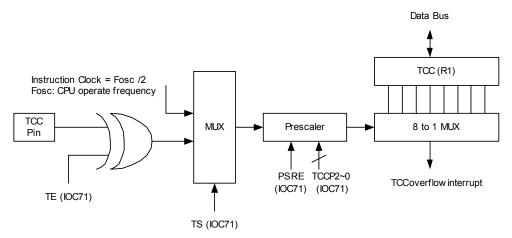

#### 4.3 TCC and WDT Pre-scaler

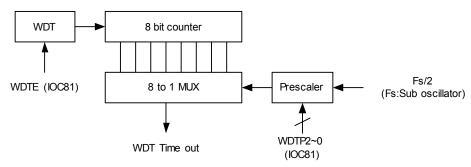

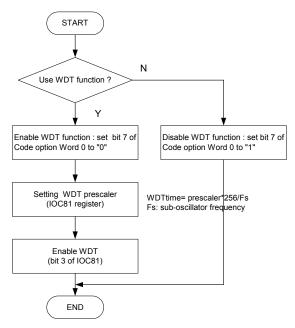

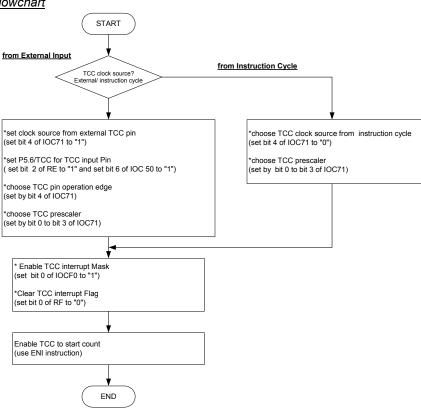

Two 8-bit counters are available as pre-scalers for the TCC (Time Clock Counter) and WDT (Watch Dog Timer). The TCCP2~TCCP0 bits of the IOC71 register are used to determine the ratio of the TCC pre-scaler. Likewise, the WDTP2~WDTP0 bits of the IOC81 register are used to determine the WDT pre-scaler. The TCC pre-scaler (TCCP2~TCCP0) is cleared by the instructions each time they are written into TCC, while the WDT pre-scaler is cleared by the "WDTC" and "SLEP" instructions. Fig.7 depicts the circuit diagram of TCC and WDT.

R1 (TCC) is an 8-bit timer/counter. The clock source of TCC can be selected by internal instruction clock or external signal input (edge selectable from the TCC control register). If TCC signal source is from internal instruction clock, TCC will increase by 1 at every instruction cycle (without pre-scaler). If TCC signal source is from external clock input, TCC will increase by 1 at every falling edge or rising edge of the TCC pin.

The watchdog timer is a free running sub-oscillator. The WDT will keep on running even after the oscillator driver has been turned off. During Normal mode, Green mode, or Idle mode operation, a WDT time-out (if enabled) will cause the device to reset. The WDT can be enabled or disabled at any time during the Normal mode and Green mode by software programming. Refer to WDTE bit of IOC81 register. The WDT time-out period is equal to (pre-scaler\*256/ (Fs/2)).

Fig. 7(a) Block Diagram of TCC

Fig. 7(b) Block Diagram of WDT

#### WDT setting flowchart

#### TCC setting flowchart

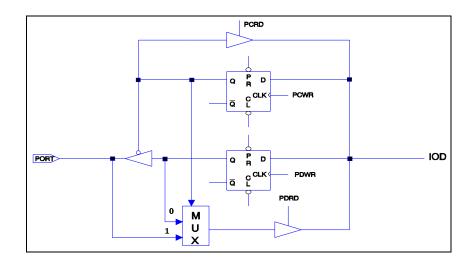

#### 4.4 I/O Ports

The I/O registers, (PORT 5, PORT 6, PORT 7 and PORT 8), are bi-directional tri-state I/O ports. PORT 6 and PORT 8 are pulled-high internally by software; PORT 6 is also pulled-low internally by software. Furthermore, PORT 6 has its open-drain output also through software. PORT 6 and PORT 8 features an input status changed interrupt (or wake-up) function and is pulled-high by software. Each I/O pin can be defined as "input" or "output" pin by the I/O control register (IOC50 ~ IOC80). The I/O registers and I/O control registers are both readable and writable. The I/O interface circuits are shown in Fig. 8

NOTE: Open-drain, pull high, and pull down are not shown in the figure.

Fig. 8 The Circuit of I/O Port and I/O Control Register for PORT 5 ~ 8

#### 4.5 RESET and Wake-up

A reset can be activated by

- POR (Power On Reset)

- WDT timeout. (if enabled)

- /RESET pin go to low.

Note: The power on reset circuit is always enabled. It will reset CPU at about 1.9V.

Once reset occurs, the following functions are performed

- The oscillator is running, or will be started.

- The program counter (R2/PC) is set to all "0".

- All I/O port pins are configured as input mode (high-impedance state).

- The TCC/Watchdog timer and pre-scaler are cleared.

- When power on, the Bit 5, 6 of R3 and the upper 2 bits of R4 are cleared.

- Bits of the IOC71 register are set to all "1" except for Bit 6 (INT flag).

- For other registers, see Table 2 below.

Table 2 Summary of the Initialized Values for Registers

|         |                   | Reset Type                         |               |        | Bit 5  | Di4 A  | Bit 3  | Dit 2   | Bit 1  | Dit 0  |

|---------|-------------------|------------------------------------|---------------|--------|--------|--------|--------|---------|--------|--------|

| Address | Name              | Reset Type                         | Bit 7         | Bit 6  |        | Bit 4  |        | Bit 2   |        | Bit 0  |

|         |                   | Bit Name                           | IOC57         | IOC56  | IOC55  | IOC54  | P8HS   | P8LS    | P7HS   | P7LS   |

| 0x05    | IOC50             | Power-On /RESET and WDT            | <u>1</u><br>1 | 1      | 1      | 1      | 0      | 0       | 0      | 0      |

| 0,000   | (P5CR)            | Wake-Up from Pin                   |               |        |        |        | -      | -       |        | -      |

|         |                   | Change                             | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | IOC67         | IOC66  | IOC65  | IOC64  | IOC63  | IOC62   | IOC61  | IOC60  |

|         | 10000             | Power-On                           | 1             | 1      | 1      | 1      | 1      | 1       | 1      | 1      |

| 0x06    | IOC60<br>(P6CR)   | /RESET and WDT                     | 1             | 1      | 1      | 1      | 1      | 1       | 1      | 1      |

|         | (FOCIN)           | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | IOC77         | IOC76  | IOC75  | IOC74  | IOC73  | IOC72   | IOC71  | IOC70  |

|         | IOC70             | Power-On                           | 1             | 1      | 1      | 1      | 1      | 1       | 1      | 1      |

| 0x07    | (P7CR)            | /RESET and WDT                     | 1             | 1      | 1      | 1      | 1      | 1       | 1      | 1      |

|         | , ,               | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | IOC87         | IOC86  | IOC85  | IOC84  | IOC83  | IOC82   | IOC81  | IOC80  |

|         | IOC80             | Power-On                           | 1             | 1      | 1      | 1      | 1      | 1       | 1      | 1      |

| 80x0    | (P8CR)            | /RESET and WDT                     | 1             | 1      | 1      | 1      | 1      | 1       | 1      | 1      |

|         |                   | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | Χ             | RAM_A6 | RAM_A5 | RAM_A4 | RAM_A3 | RAM_A2  | RAM_A1 | RAM_A0 |

|         | IOC90             | Power-On                           | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| 0x09    | (RAM_ADDR)        | /RESET and WDT                     | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

|         | /                 | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | RAM_D7        |        |        |        |        |         | RAM_D1 |        |

| 004     | IOCA0             | Power-On                           | U             | U      | U      | U      | U      | U       | U      | U      |

| 0x0A    | (RAM_DB)          | /RESET and WDT                     | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         | ` _ ′             | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         | IOCB0<br>(CNT1PR) | Bit Name                           | Bit 7         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  |

| 0x0B    |                   | Power-On /RESET and WDT            | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| OXOB    |                   | Wake-Up from Pin                   | P             | P      | P      | P      | P      | P       | P      | P      |

|         |                   | Change<br>Bit Name                 | Bit 7         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2 B | Bit 1  | Bit 0  |

|         |                   | Power-On                           | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| 0x0C    | IOCC0             | /RESET and WDT                     | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| 0,100   | (CNT2PR)          | Wake-Up from Pin                   |               |        |        |        |        |         |        |        |

|         |                   | Change                             | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         | IOCD0<br>(HPWTPR) | Bit Name                           | Bit 7         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  |

|         |                   | Power-On                           | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| 0x0D    |                   | /RESET and WDT                     | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

|         |                   | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | Bit 7         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  |

|         | IOCE0             | Power-On                           | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| 0x0E    | (LPW/TPR)         | /RESET and WDT                     | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

|         |                   | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | ICIE          | LPWTE  | HPWTE  | CNT2E  | CNT1E  | INT1E   | INT0E  | TCIE   |

|         | IOCF0             | Power-On                           | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

| 0x0F    | (IMR)             | /RESET and WDT                     | 0             | 0      | 0      | 0      | 0      | 0       | 0      | 0      |

|         | (                 | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

|         |                   | Bit Name                           | IROCS         | X      | X      | X      | /WUE8H |         | /WUE6H |        |

| 000     |                   | Power-On                           | 0             | U      | U      | U      | 0      | 0       | 0      | 0      |

| 0x06    |                   | /RESET and WDT<br>Wake-Up from Pin | 0<br>P        | U      | U      | U      | 0<br>P | 0<br>P  | 0<br>P | 0<br>P |

|         |                   | Change                             |               |        |        |        |        |         |        | -      |

| 1       |                   | Bit Name                           | INT_EDGE      | INT    | TS     | TE     | PSRE   | TCCP2   | TCCP1  | TCCP0  |

| 0: 07   | IOC71             | Power-On                           | 1             | 0      | 1      | 1      | 1      | 1       | 1      | 1      |

| 0x07    | (TCCCR)           | /RESET and WDT                     | 1             | 0      | 1      | 1      | 1      | 1       | 1      | 1      |

|         |                   | Wake-Up from Pin<br>Change         | Р             | Р      | Р      | Р      | Р      | Р       | Р      | Р      |

| Address | Name            | Reset Type                         | Bit 7      | Bit 6     | Bit 5      | Bit 4       | Bit 3        | Bit 2       | Bit 1       | Bit 0    |

|---------|-----------------|------------------------------------|------------|-----------|------------|-------------|--------------|-------------|-------------|----------|

|         |                 | Bit Name                           | Χ          | Х         | Х          | Х           | WDTE         | WDTP2       | WDTP1       | WDTP0    |

|         | IOC81           | Power-On                           | U          | U         | U          | U           | 0            | 1           | 1           | 1        |

| 80x0    | (WDTCR)         | /RESET and WDT                     | U          | U         | U          | U           | 0            | 1           | 1           | 1        |

|         | (1121011)       | Wake-Up from Pin                   | U          | U         | U          | U           | Р            | Р           | Р           | Р        |

|         |                 | Change                             | ONITOO     | ONITODO   | ONITODA    | ONITODO     | ONITAO       | ONIT4 DO    | ONITADA     | ONIT4 DO |

|         |                 | Bit Name<br>Power-On               | CNT2S<br>0 | CNT2P2    | 0          | CNT2P0      | CNT1S<br>0   | CNT1P2<br>0 | CNT1P1<br>0 | 0        |

| 0x09    | IOC91           | /RESET and WDT                     | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

| 0,000   | (CNT12CR)       | Wake-Up from Pin                   |            |           |            |             |              | -           |             |          |

|         |                 | Change                             | Р          | Р         | Р          | Р           | Р            | Р           | Р           | Р        |

|         |                 | Bit Name                           | LPWTS      | LPWTP2    | LPWTP1     | LPWTP0      | <b>HPWTS</b> | HPWTP2      | HPWTP1      | HPWTP0   |

|         | IOCA1           | Power-On                           | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

| 0x0A    | (HLPWTCR)       | /RESET and WDT                     | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

|         | ,               | Wake-Up from Pin<br>Change         | Р          | Р         | Р          | Р           | Р            | Р           | Р           | Р        |

|         |                 | Bit Name                           | PH67       | PH66      | PH65       | PH64        | PH63         | PH62        | PH61        | PH60     |

|         | IOCD4           | Power-On                           | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

| 0x0B    | IOCB1<br>(P6PH) | /RESET and WDT                     | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

|         | (FOFII)         | Wake-Up from Pin                   | Р          | Р         | Р          | Р           | Р            | Р           | Р           | Р        |

|         |                 | Change<br>Bit Name                 | OP67       | OP66      | OP65       | OP64        | OP63         | OP62        | OP61        | OP60     |

|         |                 | Power-On                           | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

| 0x0C    | IOCC1           | /RESET and WDT                     | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

|         | (P6OD)          | Wake-Up from Pin                   | Р          | Р         | Р          | Р           | Р            | Р           | Р           | Р        |

|         |                 | Change<br>Bit Name                 | PH87       | PH86      | PH85       | PH84        | PH83         | PH82        | PH81        | PH80     |

|         |                 | Power-On                           | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

| 0x0D    | IOCD1           | /RESET and WDT                     | 0          | 0         | 0          | 0           | 0            | 0           | 0           | 0        |

| OXOD    | (P8PH)          | Wake-Up from Pin                   |            |           |            |             |              | -           |             |          |

|         |                 | Change                             | Р          | Р         | Р          | Р           | Р            | Р           | Р           | Р        |

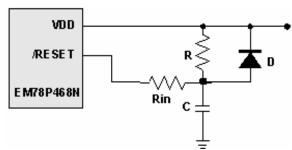

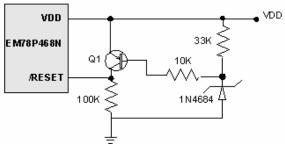

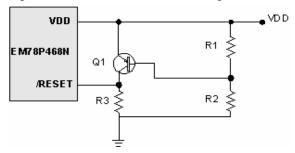

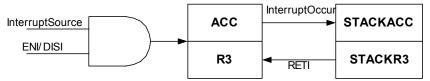

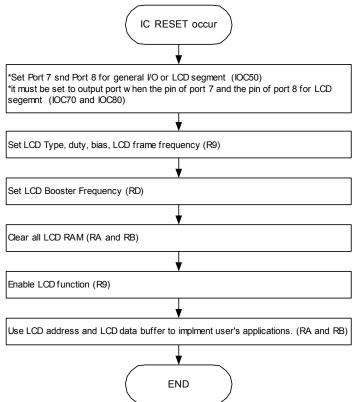

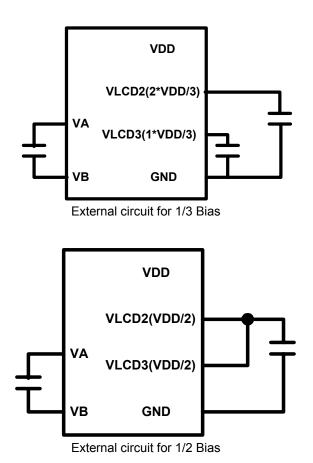

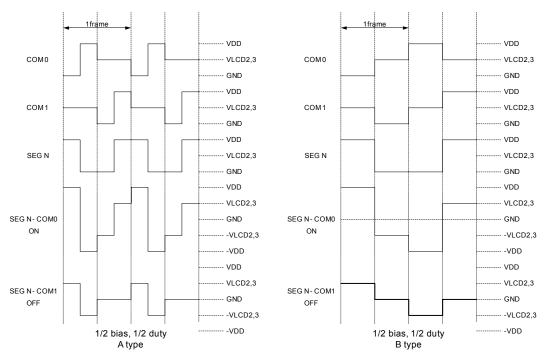

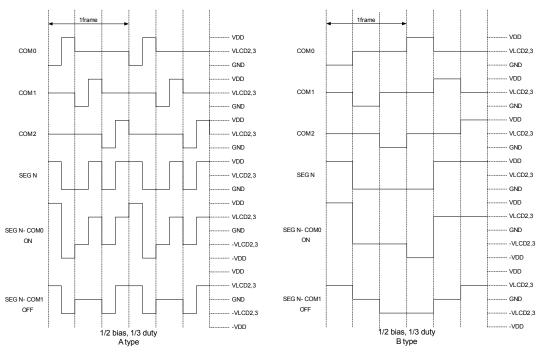

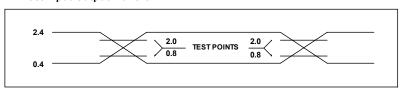

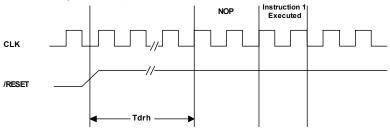

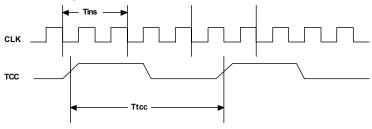

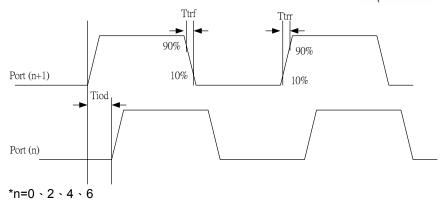

|         | IOCE1<br>(P6PL) | Bit Name                           | PL67       | PL66      | PL65       | PL64        | PL63         | PL62        | PL61        | PL60     |