~

-

|                      |                                                                              |                                                                                                                    |                                       |      |                                          |          |          |          |                      | R          | EVI          | SIO          | NS                                                      |              |              |              |             |             |          |             | -        |         |          |          |          |

|----------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------------------------------------------|----------|----------|----------|----------------------|------------|--------------|--------------|---------------------------------------------------------|--------------|--------------|--------------|-------------|-------------|----------|-------------|----------|---------|----------|----------|----------|

| LTR                  | DESCRIPTION<br>Change operating temperature range. Change table I limits for |                                                                                                                    |                                       |      |                                          |          |          |          |                      |            |              |              |                                                         |              | TE (1        |              | -           |             |          | ROVE        |          |         |          |          |          |

|                      | Chan<br><sup>I</sup> X1L<br>Edite                                            | , <sup>1</sup> x2                                                                                                  | Ή' <sup>7</sup>                       | Ά, 1 | 4, 2                                     | З, а     | and      | 40A.     | ige.<br>A            | Ch<br>dd f | ang<br>oot   | e ta<br>note | ible<br>8                                               | I 1<br>to 1  | limi<br>tabl | ts f<br>e I. | or          | 1988 DEC 20 |          |             | 1.a. fg. |         |          |          |          |

|                      |                                                                              |                                                                                                                    | · · · · · · · · · · · · · · · · · · · |      |                                          |          |          |          |                      |            |              |              |                                                         |              |              |              |             |             |          |             |          |         |          |          |          |

| REV                  | T                                                                            |                                                                                                                    | Т-                                    |      | r-                                       | <u>г</u> | -        | <u> </u> | <b></b>              | <b></b>    | <u> </u>     | <u> </u>     | 1                                                       | <b>T</b>     | <u> </u>     | r            |             | 1-          | <b>I</b> | 1           | r –      | T       | <b>—</b> | <b>—</b> | <b>-</b> |

| SHEET                | -+                                                                           |                                                                                                                    | +-                                    | +    |                                          | ┢──      | $\vdash$ | ┢──      |                      | -          | ┝            | ┼─           |                                                         |              | ┝            |              |             | ┢           | ┢        | ┞           | ╀─       | ┝─      |          | ╋        | ╂—       |

| REV                  |                                                                              |                                                                                                                    | ╈                                     | +    |                                          |          |          |          |                      |            | ┢──          |              | ┝                                                       | -            |              |              |             | ┢─          | <u> </u> | ┢           | ┢        | -       | ┢        | +        |          |

| SHEET                | 2                                                                            | 2 2:                                                                                                               | 3 24                                  | 1 25 |                                          |          |          | Î        |                      |            | $\square$    |              |                                                         |              |              |              |             |             |          |             |          |         |          | ╆        |          |

| REV STAT             |                                                                              |                                                                                                                    | REV                                   |      | Α                                        | А        |          | А        | А                    | Α          | A            | A            | A                                                       |              |              |              |             |             |          |             |          |         |          | A        |          |

| OF SHEE              | TS<br>                                                                       |                                                                                                                    | HEE                                   | T    | 1                                        | 2        | 3        | 4        | 5                    | 6          | 7            | 8            | 9                                                       | 10           | 11           | 12           | 13          | 14          | 15       | 16          | 17       | 18      | 19       | 20       | 21       |

| PMIC N/A             | DAR                                                                          |                                                                                                                    | ED                                    |      | PREPARED BY<br>Bray A. Pot<br>CHECKED BY |          |          |          |                      |            |              |              | DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |              |              |              |             |             |          | ER          |          |         |          |          |          |

| DR                   | MILITARY Ray Monnin<br>DRAWING APPROVEDLY                                    |                                                                                                                    |                                       |      |                                          |          |          | SE       | ICRO<br>ERIA<br>ILIC | IL CI      | CUIT<br>Ommu | S, D<br>NIC/ |                                                         | TAL,<br>NS ( | NM<br>CONT   | OS (<br>ROLL | DUAL<br>ER, | UN<br>MO    | IVER     | SAL<br>THIC |          |         |          |          |          |

| FOR USE BY<br>AND AG |                                                                              | IG IS AVAILABLE DRAWING APPROVAL CATE<br>LL DEPARTMENTS<br>ICIES OF THE 4 MAY 1988<br>IT OF DEFENSE REVISION LEVEL |                                       |      |                                          |          |          |          |                      | size<br>A  |              |              | AGE (                                                   |              |              |              | 59          | 62          | -8       | 68          | 10       |         |          |          |          |

|                      | /A                                                                           |                                                                                                                    |                                       |      | A                                        |          |          |          |                      |            |              | S            | SHE                                                     | ET           |              | 1            | -           | OF          | 25       |             |          |         |          |          |          |

| ESC FORM             | 193                                                                          | -                                                                                                                  |                                       |      |                                          |          |          |          |                      |            |              |              |                                                         |              |              | •            | U.S. G      | OVERN       |          |             |          | HCE: 19 | 87 —     | 748-12   | 9/60911  |

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E1137

| 查询"5962-8681001XA"供应商                                                                                                              |                               |                                               |                                |                                    |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------|--------------------------------|------------------------------------|

| 1. SCOPE                                                                                                                           |                               |                                               |                                |                                    |

| 1.1 Scope. This drawing describes with 1.2.1 of MIL-STD-883, "Provision: non-JAN devices".                                         | device requi<br>s for the use | rements for class B m<br>of MIL-STD-883 in co | icrocircuits<br>njunction with | in accordance<br>h compliant       |

| 1.2 Part number. The complete part                                                                                                 | t number shal                 | l be as shown in the                          | following exa                  | nple:                              |

| <u>5962-86810</u>                                                                                                                  |                               | <u>×</u>                                      | -                              | <u>×</u>                           |

|                                                                                                                                    |                               |                                               |                                |                                    |

|                                                                                                                                    | vice type<br>1.2.1)           | Case outline<br>(1.2.2)                       |                                | l<br>Inish per<br>1-38510          |

| 1.2.1 <u>Device type</u> . The device type                                                                                         | e shall ident                 | ify the circuit funct                         | ion as follows                 | 5:                                 |

| Device type Generic                                                                                                                | number                        | Circuit                                       | function                       |                                    |

| 01 685                                                                                                                             | 62                            | Dual universal<br>controller (DU              | serial commun<br>SCC)          | lications                          |

| 1.2.2 <u>Case outline</u> . The case outlines follows:                                                                             | ne shall be a                 | as designated in appe                         | ndix C of MIL-                 | M-38510, and                       |

| Outline letter                                                                                                                     |                               | Case outl                                     | ine                            |                                    |

| x                                                                                                                                  | D-14 (48-1                    | ead, 2.435" x .620"                           | x .225"), dual                 | -in-line package                   |

| 1.3 Absolute maximum ratings.                                                                                                      |                               |                                               |                                | -                                  |

| Maximum power dissipation $(P_D)$ -<br>Lead temperature (soldering, 10<br>Junction temperature<br>Thermal resistance, junction-to- | case (O <sub>JC</sub> ) -     | +175°C                                        | , appendix C                   |                                    |

| 1.4 Recommended operating condition                                                                                                | <u>s</u> .                    |                                               |                                |                                    |

| Supply voltage (V <sub>CC</sub> ) High level input voltage (V <sub>IH</sub> ):                                                     |                               | 4.5 V dc to 5.5                               | V dc                           |                                    |

| High level input voltage (V <sub>IH</sub> ):<br>All except X1/CLK                                                                  |                               | 2.0 V                                         |                                |                                    |

| Low level input voltage (V <sub>IL</sub> ):<br>All except X1/CLK                                                                   |                               | •                                             |                                |                                    |

| X1/CLK                                                                                                                             |                               | 0.8 V<br>0.4 V                                |                                |                                    |

| Low level output current (I <sub>OL</sub> ):<br>All except DONEN and IRQN                                                          |                               | 5.3 mA                                        |                                |                                    |

| DONEN and IRQN                                                                                                                     |                               | – – 8,8 mA<br>– – –400 µA                     |                                |                                    |

| Case operating temperature range                                                                                                   | (T <sub>C</sub> )             | 55°C to +110°C                                |                                |                                    |

|                                                                                                                                    |                               |                                               |                                |                                    |

|                                                                                                                                    |                               |                                               |                                |                                    |

|                                                                                                                                    |                               |                                               |                                |                                    |

| STANDARDIZED                                                                                                                       | SIZE                          | I                                             |                                |                                    |

| <b>MILITARY DRAWING</b>                                                                                                            | A                             |                                               | 5962-8681                      | D                                  |

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444                                                                            |                               | REVISION LEVEL                                | SH                             | EET 2                              |

| SC FORM 193A<br>SEP 87                                                                                                             |                               | <u>^</u>                                      |                                | 2<br>PRINTING OFFICE: 1988-550-547 |

~

~

<u> 查询"5962-8681001XA"供应商</u>

2.1 <u>Government specification and standard</u>. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

SPECIFICATION

MILITARY

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

REQUIREMENTS

3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

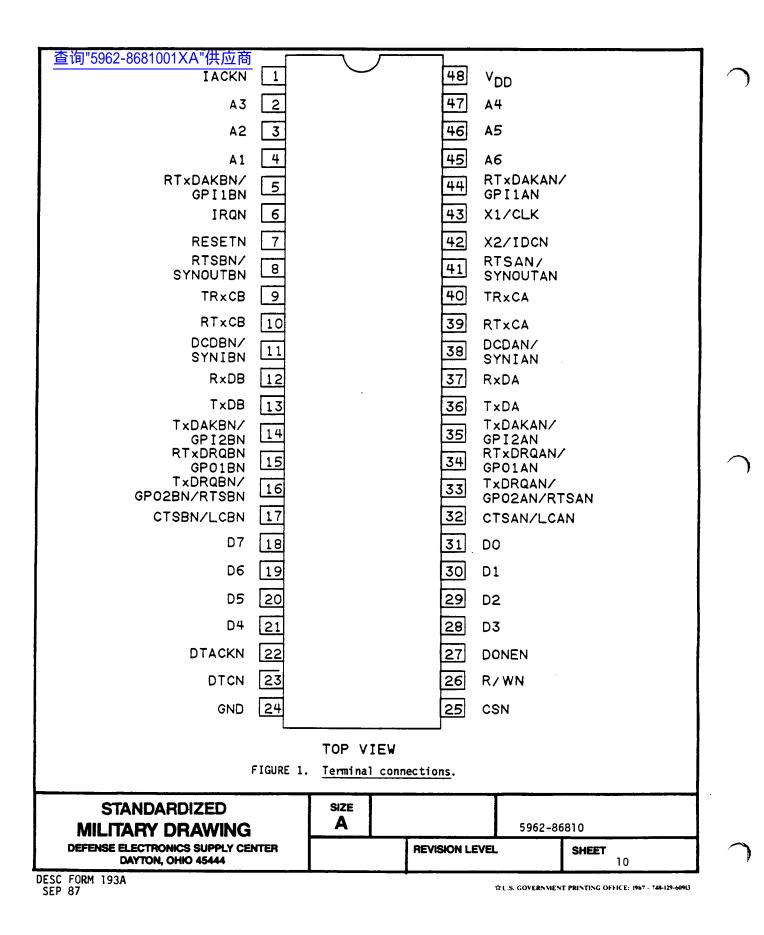

3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

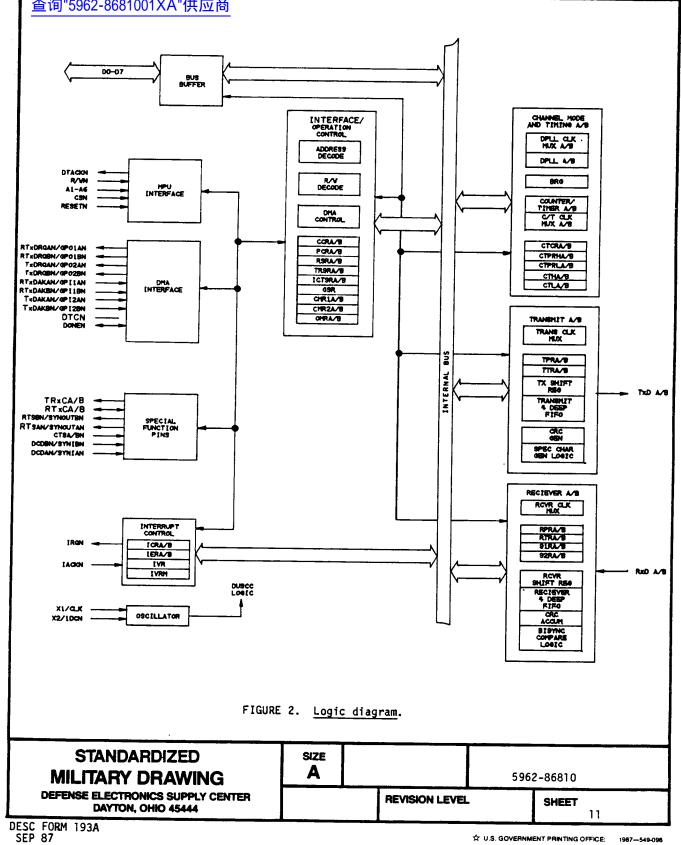

3.2.2 Logic diagram. The logic diagram shall be as specified on figure 2.

3.2.3 Case outline. The case outline shall be in accordance with 1.2.2 herein.

3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

3.4 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

3.5 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

3.6 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARDIZED<br>MILITARY DRAWING                        | size<br>A |                | 5962-86810 |

|---------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 3    |

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987-549-096

| Test                                            | Symbol           |                 | _55°C <                                       | onditi             | ons<br>110°C         | Group A<br>subgroups |       | nits         | Unit               |          |

|-------------------------------------------------|------------------|-----------------|-----------------------------------------------|--------------------|----------------------|----------------------|-------|--------------|--------------------|----------|

|                                                 |                  |                 | 4.5 V                                         | < Vcc              | < 5.5 V<br>Tse spect | fied                 |       |              | Max                |          |

| Power supply current                            | Icc              |                 | V(                                            | CC = 5             | .5 V                 |                      | 1,2,3 |              | 325                | mA       |

| Output low voltage, except<br>DONEN and IRQN    | V <sub>OL</sub>  | v <sub>c</sub>  | c = 4.5 V                                     | I <sub>OL</sub>    | = 5.3 mA             |                      | 1,2,3 |              | 0.5                | ۷        |

| Output voltage low<br>DONEN and IRQN            | VOL              | Vc              | c = 4.5 V                                     | I <sub>OL</sub> -  | * 8.8 mA             |                      | 1,2,3 |              | 0.5                | V        |

| Output high voltage                             | V <sub>OH</sub>  | v <sub>c</sub>  | c = 4.5 V                                     | I <sub>OH</sub> =  | -400 μA              |                      | 1,2,3 | 2.4          |                    | γ        |

| Open collector output<br>leakage current        | IOC              | VC              | c = 5.5 V<br>V <sub>0</sub> = 0 V             | to V <sub>C(</sub> | ;                    |                      | 1,2,3 |              | 10                 | μA       |

| Input low voltage, all<br>except X1/CLK         | V <sub>IL1</sub> |                 |                                               |                    |                      |                      | 1,2,3 |              | 0.8                | V        |

| Input low voltage, X1/CLK                       | ۷ <sub>IL2</sub> |                 |                                               |                    |                      |                      | 1,2,3 |              | 0.4                | ۷        |

| Input high voltage, all<br>except X1/CLK        | V <sub>IH1</sub> |                 |                                               |                    |                      |                      | 1,2,3 | 2.0          |                    | ۷        |

| Input high voltage, X1/CLK                      | V <sub>IH2</sub> | 1               |                                               |                    |                      |                      | 1,2,3 | 2.4          | 1                  | ۷        |

| Three-state leakage<br>current                  | IOZ              | ۷ <sub>0</sub>  | = 0 V to<br>V <sub>CC</sub> = 5.5             | vcc<br>v           | - , ,,               |                      | 1,2,3 | -10          | 10                 | μA       |

| X1/CLK low input current                        | IXIL             | 1               | = 5.5 V<br>IN = 0 V,<br>IN = 0 V,             | X2/ID              | CN float<br>CN groun | 3/<br>ed<br>ded      | 1,2,3 | -5.0<br>-2.0 |                    | mA<br>mA |

| K1/CLK high input current                       | IX1H             | VC              | = 5.5 V<br>IN = $V_{CC}$ ,<br>IN = $V_{CC}$ , | X2/ID<br>X2/ID     | CN float<br>CN groun | 3/<br>ed<br>ded      | 1,2,3 |              | <br> 36.0<br>  1.0 | mA<br>mA |

| (2/IDCN low input current                       | I <sub>X2L</sub> | VCC             | = 5.5 V<br>IN = 0 V,                          | X1/CL              | K floate             | <u>3/</u>            | 1,2,3 | -100         |                    | μA       |

| (2/IDCN high input current                      | I <sub>X2H</sub> | ۷ <sub>CQ</sub> | = 5.5 V<br>IN = V <sub>CC</sub> ,             | X1/CL              | K floate             | <u>3/</u>            | 1,2,3 |              | 100                | μA       |

| See footnotes at end of table                   | •                |                 |                                               |                    |                      |                      |       | <u> </u>     | : <b>!</b>         |          |

| STANDARDIZED                                    |                  | size<br>A       |                                               |                    | 5962-86810           |                      |       |              |                    |          |

| DEFENSE ELECTRONICS SUPPL<br>DAYTON, OHIO 45444 |                  |                 |                                               |                    | REVISION             | LEVEL                |       | SHEET        |                    |          |

•

٠

| 查询"5962-8681001XA"供历<br>TABLE 1                               | 1         | Condi                                            | tions 1/2/                            | Group A    | I Lim           | its | Unt        |

|---------------------------------------------------------------|-----------|--------------------------------------------------|---------------------------------------|------------|-----------------|-----|------------|

| Test                                                          | Symbol    | -55°C < TC<br>4.5 V < VC<br>unless othe          | <pre>&lt; +110°C</pre>                | s ubgroups | <br>  1417n<br> | Max | <br> <br>  |

| Input leakage current                                         | IIH       | $V_{\rm CC} = 5.5 V V_{\rm I}$                   | N = 5.5 V                             | 1,2,3      |                 | 10  | μA         |

| Input low current. all<br>except DTCN, RTxDAKA/B,<br>TxDAKA/B | IIL       | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 0 V |                                       | 1,2,3      | - 100           |     | μ <b>Α</b> |

| Input low current,<br>remaining input pins                    | IIL       | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 0 V |                                       | 1,2,3      | -10             |     | μA         |

| Functional tests                                              |           | see 4.3.1d                                       |                                       | 7,8        |                 |     |            |

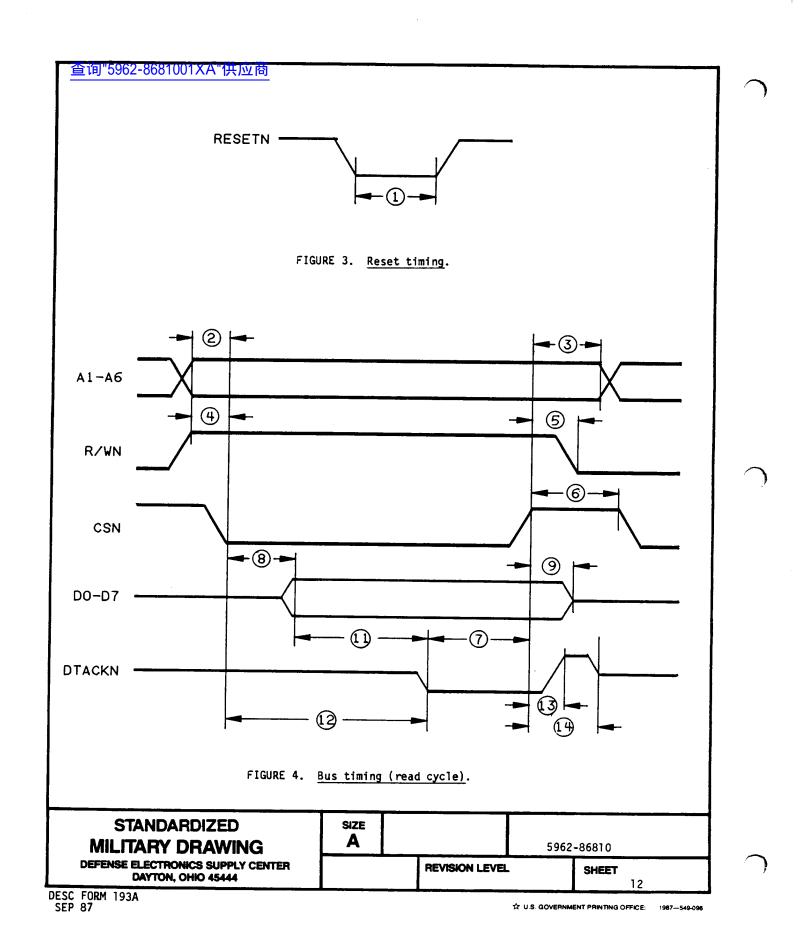

| RESETN pulse width                                            |           | <br>  see figure 3<br>                           |                                       | 9,10,11    | 1.2             |     | μS         |

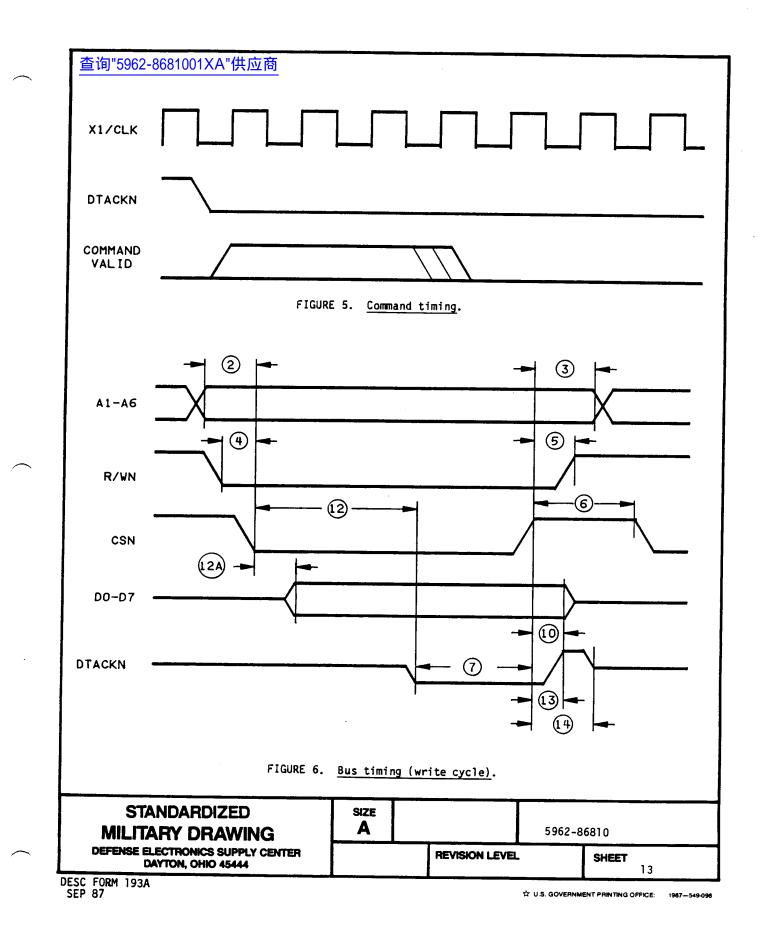

| Al-A6 setup time to CSN<br>low                                | 2         | see figures 4 a                                  | and 6                                 | 9,10,11    | 10              |     | ns         |

| Al-A6 hold time from CSN<br>high                              | 3         |                                                  |                                       | 9,10,11    | 0               |     | ns         |

| R/WN setup time to CSN<br>low                                 | 4         |                                                  |                                       | 9,10,11    | 0               |     | ns         |

| R/WN hold time to CSN high                                    | 5         | F<br>I<br>I                                      |                                       | 9,10,11    | 0               |     | ns         |

| CSN high pulse width <u>4</u> /                               | 6         |                                                  |                                       | 9,10,11    | 160             |     | ns         |

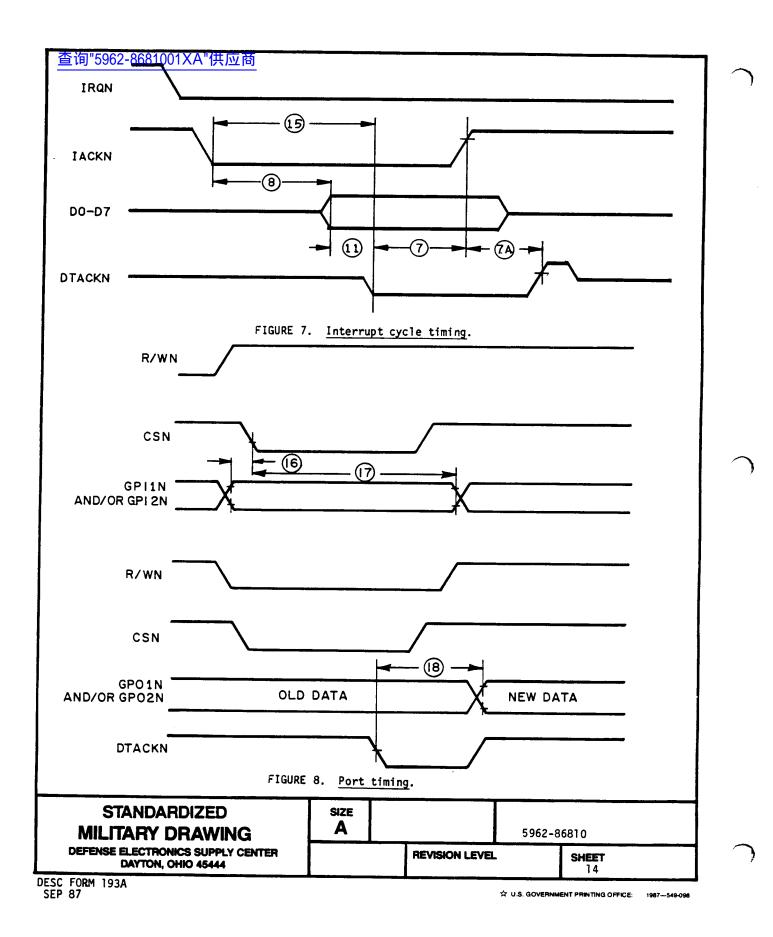

| CSN or IACKN high from<br>DTACKN low                          | 7         | see figures 4,                                   | 6, and 7                              | 9,10,11    | 30              |     | ns         |

| IACKN high to DTACKN high                                     | 7A        | see figure 7                                     | · · · · · · · · · · · · · · · · · · · | 9,10,11    |                 | 200 | ns         |

| Data valid from CSN or<br>IACKN low                           | 8         | see figures 4 a                                  | ind 7                                 | 9,10,11    |                 | 300 | ns         |

| See footnotes at end of table                                 |           |                                                  |                                       | <u> </u>   | <b>I</b>        |     |            |

| STANDARDIZED<br>MILITARY DRAWI                                |           | SIZE<br>A                                        |                                       | 5962-86    | 5810            |     |            |

| DEFENSE ELECTRONICS SUPPI                                     | LY CENTER |                                                  | <b>REVISION LEVEL</b>                 |            | SHEET           |     |            |

1

.

```

Powered by ICminer.com Electronic-Library Service CopyRight 2003

```

.

•

|                                               |                 | Conditions 1/2                                                                                                                   | Group A   |     | ts  | Unit |

|-----------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|------|

| Test                                          | Symbol<br> <br> | $\begin{array}{c c} -55^{\circ}C < T_{C} < \pm 110^{\circ}C \\ 4.5 V < V_{CC} < 5.5 V \\ unless otherwise specified \end{array}$ | subgroups | Min | Max |      |

| Data bus floating from<br>CSN high <u>5</u> / | 9               | see figure 4                                                                                                                     | 9,10,11   |     | 100 | ns   |

| Data hold time from<br>DTACKN low <u>6</u> /  | 10              | see figure 6                                                                                                                     | 9,10,11   | 0   |     | ns   |

| DTACKN low from read data ready               | 11              | see figures 4 and 7                                                                                                              | 9,10,11   | 0   |     | ns   |

| DTACKN low from CSN low                       | 12              | see figures 4 and 6                                                                                                              | 9,10,11   |     | 560 | ns   |

| CSN low to write data valid                   | 12A             | see figure 6                                                                                                                     | 9,10,11   |     | 50  | ns   |

| DTACKN high from CSN high                     | 13              | see figures 4 and 6                                                                                                              | 9,10,11   |     | 150 | ns   |

| DTACKN high impedance from<br>CSN high        | 14              | -                                                                                                                                | 9,10,11   |     | 185 | ns   |

| DTACKN low from IACKN low                     | 15              | see figure 7                                                                                                                     | 9,10,11   |     | 550 | ns   |

| GPI input setup time CSN<br>low               | 16              | see figure 8                                                                                                                     | 9,10,11   | 20  |     | ns   |

| GPI input hold time from<br>CSN low           | 17              | -                                                                                                                                | 9,10,11   | 100 |     | ns   |

| GPO output valid from<br>DTACKN low           | 18              | -                                                                                                                                | 9,10,11   |     | 300 | ns   |

| See footnotes at end of table                 | •               |                                                                                                                                  |           |     |     |      |

| STANDARDIZED<br>MILITARY DRAWIN               | IG              | SIZE<br>A                                                                                                                        | 5962-86   | 810 |     |      |

|                                               |                 |                                                                                                                                  |           |     |     |      |

1

•

٠

| 查询"5962-8681001入A"供应                                                                                                                                                                                  | T                | <u> </u>   | C                          | onditi                                | ons 1/2/                           | Group A            |                                                 | its        | Uni                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|----------------------------|---------------------------------------|------------------------------------|--------------------|-------------------------------------------------|------------|-------------------------------------------------------|

| Test                                                                                                                                                                                                  | Symbo]<br> <br>  |            | -55 C <<br>4.5 V<br>unless | <u>&lt; V<sub>CC</sub><br/>othern</u> | +110°C<br>< 5.5 V<br>Tse specified | subgroup:<br> <br> |                                                 | Max        | <br> <br>                                             |

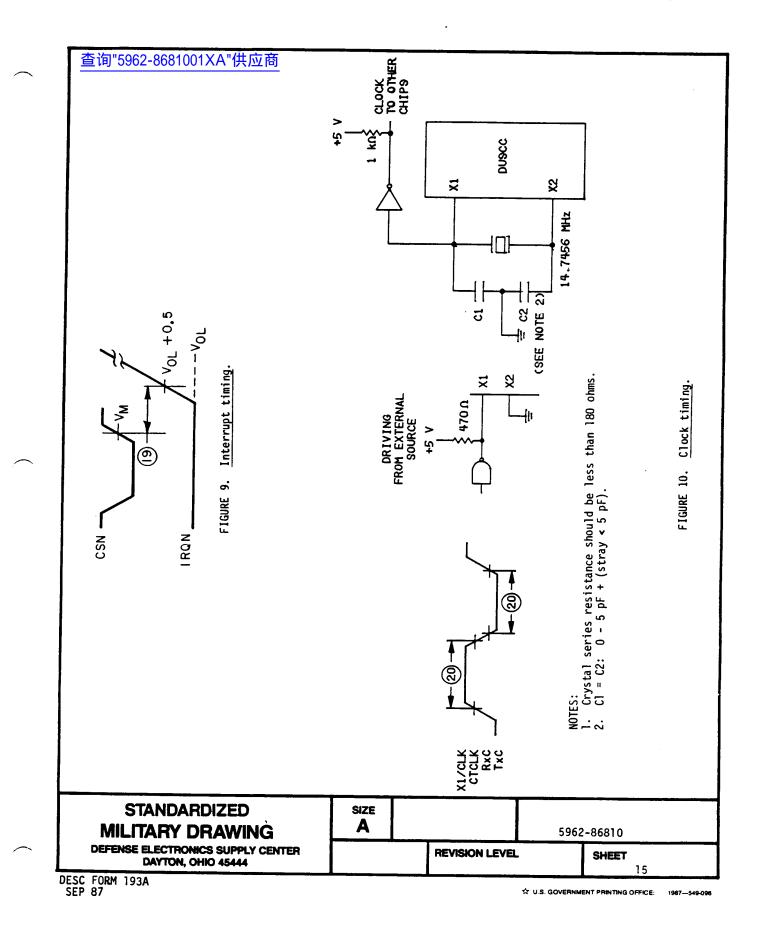

| IRQN high from:<br>Read RxFIFO (RxRDY<br>interrupt)<br>Write TxFIFO (TxRDY<br>interrupt) 7/<br>Write receive status<br>register (Rx condition<br>interrupt) 7/                                        | 19               | see        | e figure                   | 9                                     |                                    | 9,10,11            |                                                 | 450        | ns<br>ns                                              |

| Write transmit/receive<br>status register (Rx/Tx<br>interrupt) 7/<br>Write input counter/timer<br>status register (port                                                                               | ]<br>]<br>]<br>] |            |                            |                                       |                                    |                    |                                                 | 400        | ns<br> <br>  ns<br>                                   |

| change and CT int.) 7/                                                                                                                                                                                |                  | 1<br> <br> |                            |                                       |                                    |                    | }<br> <br>                                      | 400        | l<br>Ins                                              |

| X1/CLK high or low time<br>X1/CLK frequency<br>CTCLK high or low time<br>CTCLK frequency<br>RxC high or low time<br>RxC frequency (16x or 1x) 8/<br>TxC high or low time<br>TxC frequency (16x or 1x) | 20               | see        | figure                     | 10                                    |                                    | 9,10,11            | 25<br>2.0<br>100<br>110<br>110<br>0<br>110<br>0 | 16         | ns<br>  MHz<br>  ns<br>  MHz<br>  ns<br>  MHz<br>  ns |

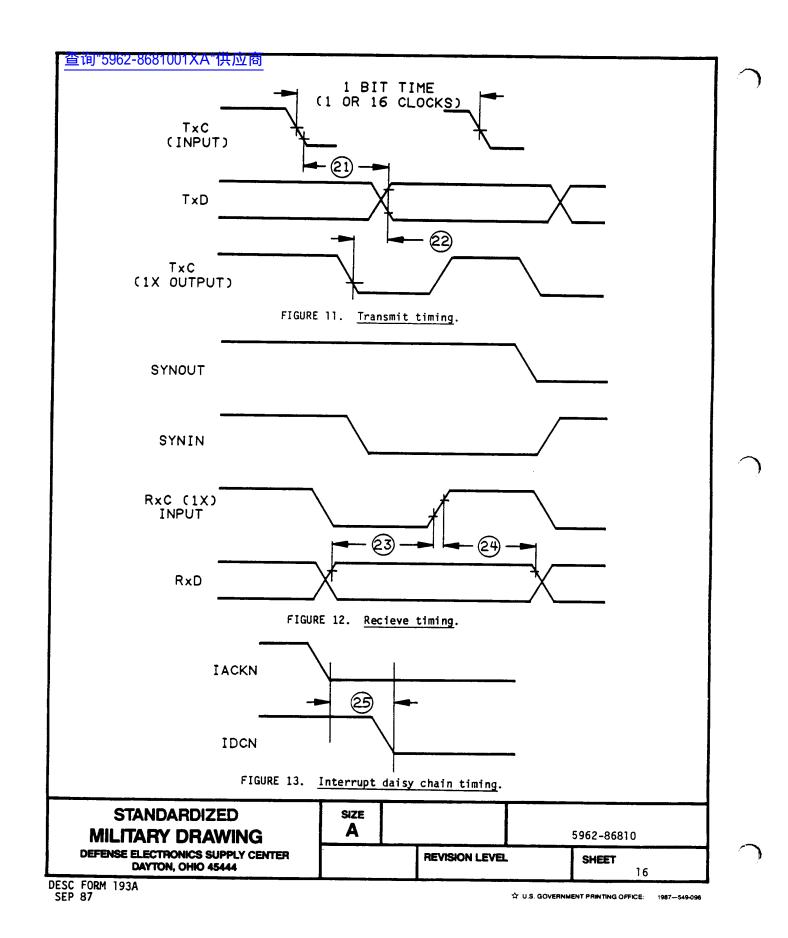

| TxD output from TxC input<br>low (lx)<br>(l6x)                                                                                                                                                        | 21               | see        | figure                     | 11                                    |                                    | 9,10,11            |                                                 | 240<br>435 | ns                                                    |

| TxD output from TxC output<br>low                                                                                                                                                                     | 22               |            |                            |                                       |                                    | 9,10,11            |                                                 | 50         | ns                                                    |

| RxD data setup time to RxC<br>high                                                                                                                                                                    | 23               | see        | figure                     | 12                                    |                                    | 9,10,11            | 50                                              |            | ns                                                    |

| RxD data hold time from RxC<br>high                                                                                                                                                                   | 24               |            |                            |                                       |                                    | 9,10,11            | 50                                              |            | ns                                                    |

| IACKN low to IDCN low                                                                                                                                                                                 | 25               | see        | figure                     | 13                                    |                                    | 9,10,11            | 1                                               | 200        | ns                                                    |

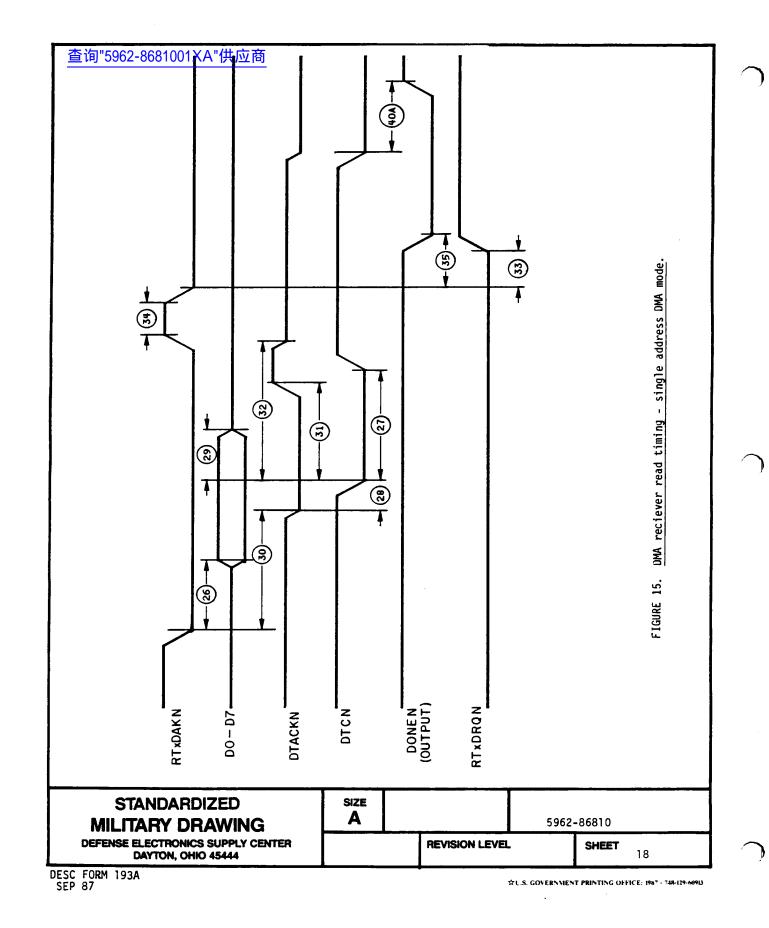

| Data valid from received<br>DMA acknowledge (RTxDAKN)                                                                                                                                                 | 26               | see        | figure                     | 15                                    |                                    | 9,10,11            |                                                 | 300        | ns                                                    |

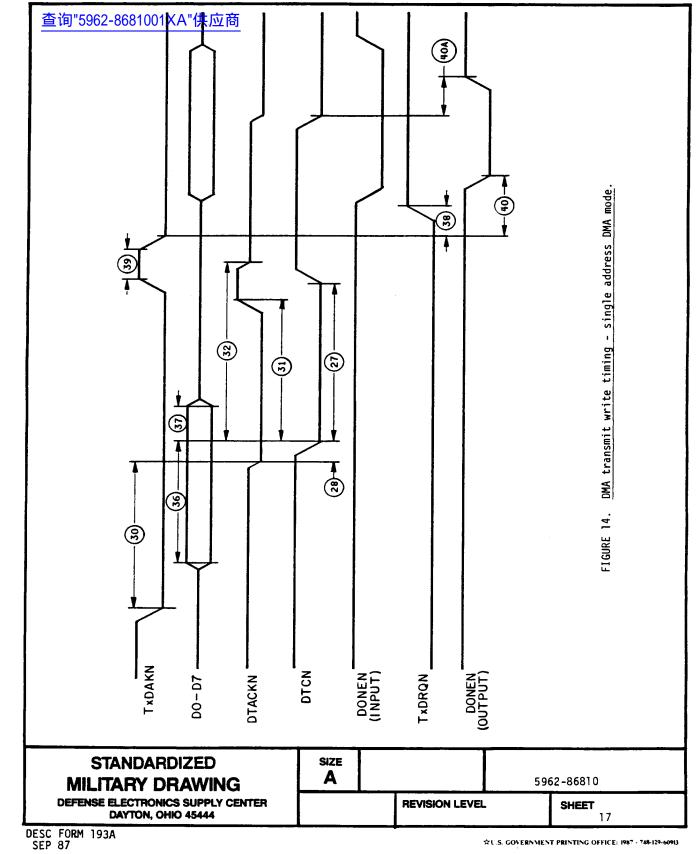

| DTCN width                                                                                                                                                                                            | 27               | see        | figures                    | 14 ar                                 | d 15                               | 9,10,11            | 100                                             | i<br>i     | ns                                                    |

| See footnotes at end of table.                                                                                                                                                                        |                  |            | • ių                       |                                       |                                    | ·                  | . <u> </u>                                      |            | <u> </u>                                              |

| STANDARDIZED<br>MILITARY DRAWIN                                                                                                                                                                       | G                |            | size<br>A                  |                                       |                                    | 5962-86            | 5810                                            |            |                                                       |

| DEFENSE ELECTRONICS SUPPLY (<br>DAYTON, OHIO 45444                                                                                                                                                    | CENTER           |            |                            |                                       | REVISION LEVEL                     |                    | SHEET                                           | 7          |                                                       |

•

•

Powered by ICminer.com Electronic-Library Service CopyRight 2003

| Test                                                                    | <br> Symbol | Condit                                      | :10ns 1/                | 2/ Group A |                 | its       | Unit      |

|-------------------------------------------------------------------------|-------------|---------------------------------------------|-------------------------|------------|-----------------|-----------|-----------|

|                                                                         |             | -55°C < TC <<br>4.5 V < VCC<br>unless other | < 5.5 V<br>wise specifi | ed         | MIN             | Max       | <br> <br> |

| DTACKN low to DTCN low                                                  | 28          | see figures 14                              | and 15                  | 9,10,11    | 80              | <br> <br> | ns<br>I   |

| Data bus float from DTCN<br>low <u>5</u> /                              | 29          | see figure 15<br> <br>                      |                         | 9,10,11    |                 | 200       | Ins       |

| DMA acknowledge (TxDAKN or<br>RTxDAKN) low to DTACKN low                | 30          | see figures 14                              | and 15                  | 9,10,11    |                 | 360       | ns        |

| DTACKN high from DTCN low                                               | 31          | T<br> <br>                                  |                         | 9,10,11    | †<br> <br>      | 230       | ns        |

| DTACKN high impedance from<br>DTCN low                                  | 32          | T<br> <br> <br>                             |                         | 9,10,11    | †<br> <br> <br> | 250       | ns        |

| Receive DMA request (RTxDRQN)<br>high from DMA acknowledge<br>(RTxDAKN) | 33          | see figure 15                               |                         | 9,10,11    |                 | 325       | ns        |

| Receive DMA acknowledge<br>(RTxDAKN) width                              | 34          |                                             |                         | 9,10,11    | 150             |           | ns        |

| Receive DMA acknowledge<br>(RTxDAKN) low to DONEN low                   | 35          |                                             |                         | 9,10,11    |                 | 250       | ns        |

| Data setup to DTCN low                                                  | 36          | see figure 14                               | <u> </u>                | 9,10,11    | 50              |           | ٦s        |

| Data hold from DTCN low <u>9</u> /                                      | 37          | T                                           |                         | 9,10,11    | 50              |           | ns        |

| Transmit DMA request (TxDRQN)<br>high from acknowledge<br>(TxDAKN)      | 38          | -                                           |                         | 9,10,11    |                 | 340       | ns        |

| Fransmit DMA acknowledge<br>(TxDAKN) width                              | 39          | •                                           |                         | 9,10,11    | 150             |           | ns        |

| <pre>'ransmit DMA acknowledge (TxDAKN) low to DONEN low output</pre>    | 40          |                                             |                         | 9,10,11    |                 | 250       | ns        |

| DTCN low DONEN output high                                              | 40A         |                                             |                         | 9,10,11    |                 | 260       | ns        |

| ee footnotes at end of table.                                           | <u> </u>    | <u> </u>                                    |                         |            | <u> </u>        | 1         |           |

| STANDARDIZED                                                            |             | SIZE<br>A                                   |                         | 5050.0     | 5010            | <u> </u>  |           |

| MILITARY DRAWIN                                                         |             |                                             | REVISION LE             | 5962-8     | SHEET           |           |           |

SEP 87

\* U. S. GOVERNMENT PRINTING OFFICE: 1988-550-547

•

•

| Test                                                                                                                     | Symbol                                       | -55°C <<br>4.5 V             | onditions<br>T <u>c &lt; +110</u> °C<br>< V <u>cc &lt;</u> 5.5 V | <u>1/2/</u> | Group A<br>subgroups |           | its<br>Max | Uni |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------|------------------------------------------------------------------|-------------|----------------------|-----------|------------|-----|

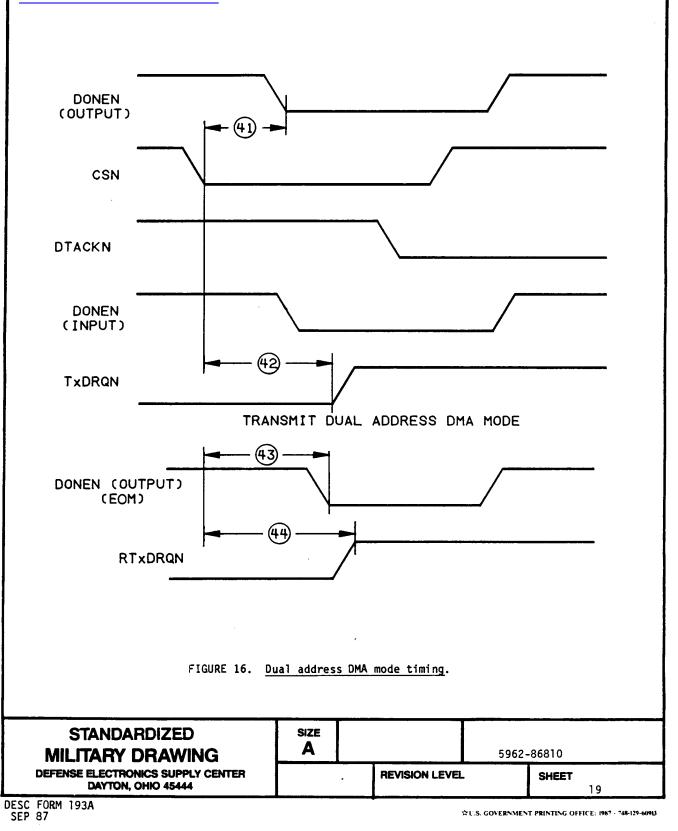

| CSN low to transmit DONEN<br>low output                                                                                  | 41                                           | unless<br> <br>  see figure  | otherwise spe                                                    | cified      | 9,10,11              | <br> <br> | 300        | ns  |

|                                                                                                                          | ļ<br>                                        |                              |                                                                  |             | ļ                    |           |            |     |

| CSN low to transmit DMA<br>request negated (TxDRQN)                                                                      | 42                                           |                              |                                                                  |             | 9,10,11              |           | 400        | ns  |

| CSN low to receive DONEN low                                                                                             | 43                                           | Г<br>                        |                                                                  |             | 9,10,11              |           | 300        | ns  |

| CSN low to receive DMA request<br>negated (RTxDRQN)                                                                      | 44                                           | <b>F</b>                     |                                                                  |             | 9,10,11              |           | 400        | ns  |

| 1/ All voltage measurements a<br>inputs except X1/CLK swing<br>X1/CLK, this swing is betw<br>voltages of 0.2 V and 2.4 V | between<br>een 0.4 V                         | 0.4 V and 2.<br>/ and 4.4 V. | 4 V with a to                                                    | ransition   | time of 20           | ) ne ma   | aximum     | For |

| 2/ Test condition for outputs<br>interrupt outputs: CL = 50                                                              | : C <sub>L</sub> = 1<br>D pF, R <sub>L</sub> | 50 pF, excep<br>= 2.7 k ohm  | t interrupt o<br>to V <sub>CC</sub> .                            | utputs.     | Test condi           | tion f    | or         |     |

| 3/ X1/CLK and X2/IDCN are not                                                                                            | tested w                                     | with a crysta                | 1 installed.                                                     |             |                      |           |            |     |

| 4/ This specification will im<br>repeating bus cycles are no                                                             | oose maxi<br>ot perfor                       | mum 68000 CP<br>med.         | U CLK to 6 MH                                                    | z. Highe    | r CPU CLK c          | an be     | used i     | f   |

| 5/ These values were not expl                                                                                            | icitly te                                    | sted, they a                 | re guaranteed                                                    | by desi     | gn and char          | acteri    | zation     | dat |

| 5/ Execution of the valid comm<br>figure 14).                                                                            | mand (aft                                    | er it is lat                 | ched) require                                                    | s three     | falling edg          | es of     | X1 (se     | e   |

| / These timings are from the                                                                                             | falling                                      | edge of DTAC                 | KN (not CSN r                                                    | ising).     |                      |           |            |     |

| / X1/CLK frequency must be at                                                                                            | : least 4                                    | times the r                  | eceiver seria                                                    | 1 data r    | ate.                 |           |            |     |

| / In single address DMA mode                                                                                             | write op                                     | eration, dat                 | a is latched                                                     | by the f    | alling edge          | of DT     | CN.        |     |

|                                                                                                                          |                                              |                              |                                                                  |             |                      |           |            |     |

|                                                                                                                          |                                              |                              |                                                                  |             |                      |           |            |     |

|                                                                                                                          |                                              |                              |                                                                  |             |                      |           |            |     |

|                                                                                                                          |                                              |                              |                                                                  |             |                      |           |            |     |

|                                                                                                                          |                                              |                              |                                                                  |             |                      |           |            |     |

|                                                                                                                          |                                              |                              |                                                                  |             |                      |           |            |     |

| STANDARDIZED<br>MILITARY DRAWIN                                                                                          | G                                            | size<br>A                    |                                                                  |             | 5962-868             | 310       |            |     |

| DEFENSE ELECTRONICS SUPPLY                                                                                               | CENTER                                       |                              | REVISIO                                                          | N LEVEL     |                      | SHEET     |            |     |

F

• •

.

.

.

-

.

-

☆U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

.

.

查询"5962-8681001XA"供应商 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

3.8 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

4. QUALITY ASSURANCE PROVISIONS

4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

4.2 Screening. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_{A} = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroups 7 and 8 shall consist of verifying the functionality of the device. These tests form a part of the vendors test tape and shall be maintained and available from the approved sources of supply.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_{A} = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED<br>MILITARY DRAWING                        | size<br>A |                | 5962 - | 86810       |

|---------------------------------------------------------|-----------|----------------|--------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | REVISION LEVEL | L      | SHEET<br>20 |

DESC FORM 193A SEP 87

\* U. S. GOVERNMENT PRINTING OFFICE: 1988-550-547

| MIL-STD-883 test requirements                                      | Subgroups<br>(per method<br>5005, table I)<br><u>1</u> / |

|--------------------------------------------------------------------|----------------------------------------------------------|

| Interim electrical parameters<br>(method 5004)                     | 1                                                        |

| Final electrical test parameters (method 5004)                     | 1*,2,3,7,8,9,<br>10,11                                   |

| Group A test requirements<br>(method 5005)                         | 1,2,3,7,8,9,<br>10,11                                    |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1,2,3                                                    |

查询"5962-8681001XA"供应商 ABLE II. <u>Electrical test requirements</u>.

\* PDA applies to subgroup 1.

1/ Any subgroup at the same temperature may be combined using a multifunction tester.

5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

6. NOTES

6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

| STANDARDIZED<br>MILITARY DRAWING                        | size<br>A |                       | 5962-          | -86810                |              |

|---------------------------------------------------------|-----------|-----------------------|----------------|-----------------------|--------------|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | <b>REVISION LEVEL</b> | •              | SHEET 21              |              |

| DESC FORM 193A<br>SEP 87                                |           | A                     | ☆ U.S. GOVERNN | IENT PRINTING OFFICE: | 1987-549-096 |

6.3 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

-

.

6.4 Pin descriptions.

| Mnemonic                 | <u>Pin</u>     | Туре     | Name and function                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|--------------------------|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| A6-A1                    | 45-47<br>2-4   | I        | Address lines: Active high. Address inputs which specify which of the internal registers is accessed for read/write operations.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| D7-D0,                   | 18-21<br>28-31 | I/O      | Bidirectional data bus: Active high, three-state. Bit 0 is the<br>LSB and bit 7 is the MSB. All data, command, and status transfers<br>between the CPU and the DUSCC take place over this bus. The data<br>bus is enabled when CSN is low, during interrupt acknowledge<br>cycles and single address DMA acknowledge cycles.                                                                                                                |  |  |  |  |  |  |

| R ∕₩N                    | 26             | I        | Read/Write: A high input indicates a read cycle and a low inpu<br>indicates a write cycle when a cycle is initiated by assertion<br>the CSN input.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| CSN                      | 25             | I        | Chip select: Active low input. When low, data transfers between the CPU and the DUSCC are enabled on DO-D7 as controlled by $R/WN$ and A1-A6 inputs. When CSN is high, the DUSCC is isolated from the data bus (except during interrupt acknowledge cycles and single address DMA transfers) and DO-D7 are placed in the 3-state condition.                                                                                                 |  |  |  |  |  |  |

| IRQN                     | 6              | 0        | Interrupt request: Active low, open drain. This output is<br>asserted upon occurrence of any enabled interrupting condition.<br>The CPU can read the general status register to determine the<br>interrupting condition(s), or can respond with an interrupt<br>acknowledge cycle to cause the DUSCC to output an interrupt vector<br>on the data bus.                                                                                      |  |  |  |  |  |  |

| IACKN                    | 1              | I        | Interrupt acknowledge: Active low. When IACK is asserted, the<br>DUSCC responds by placing the contents of the interrupt vector<br>register (modified or unmodified by status) on the data bus and<br>asserting DTACKN. If no active interrupt is pending, DTACKN is<br>not asserted.                                                                                                                                                       |  |  |  |  |  |  |

| X1/CLK                   | 43             | I        | Crystal or external clock: When using the crystal oscillator, the crystal is connected between pins X1 and X2. If a crystal is not used, an external clock must be supplied at this input. This clock input is used to drive the internal bit rate generator, as an optional input to the counter/timer (CT) or digital phase lock loop (DPLL), and to provide other required clocking signals.                                             |  |  |  |  |  |  |

| X2/IDCN                  | 42             | I /0     | Crystal or interrupt daisy chain: When a crystal is used as the timing source, the crystal is connected between pins X1 and X2. This pin can be programmed to provide an interrupt daisy chain active low output which propagates the IACKN signal to lower priority devices if no active interrupt is pending. This pin should be grounded when an external clock is used on X1 and X2 and is not used as an interrupt daisy chain output. |  |  |  |  |  |  |

| STAN<br>MILITAF          |                |          | SIZE 5962-86810                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| DEFENSE ELEC             |                | UPPLY CE | NTER REVISION LEVEL SHEET 22                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| DESC FORM 193A<br>SEP 87 |                |          | ☆ U.S. GOVERNMENT PRINTING OFFICE: 1987-549-096                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 询"5962-8681<br><u>Mnemonic</u> | <u>001XA"</u> | <del>供应商</del> | Name and function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| RESETN                         | 7             | I              | Master reset: Active low. A low on this pin resets the<br>transmitters and receivers and resets the registers shown in<br>figure 2. Reset is asynchronous, i.e., no clock is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| RxDA,RxDB                      | 37,12         | I              | Channel A (B) receiver serial data input: The least significant<br>bit is received first. If external receiver clock is specified<br>for the channel, the input is sampled on the rising edge of the<br>clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TxDA,TxDB                      | 36,13         | 0              | Channel A (B) transmitter serial data output: The least<br>significant bit is transmitted first. This output is held in the<br>marking (high) condition when the transmitter is disabled or when<br>the channel is operating in local loopback mode. If external<br>transmitter clock is specified for the channel, the data is<br>shifted on the falling edge of the clock.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| RTxCA,RTxCB                    | 39,10         | I/O            | Channel A (B) receiver/transmitter clock: As an input it can be<br>programmed to supply the receiver, transmitter, counter/timer, o<br>DPLL clock. As an output, can supply the counter/timer output,<br>the transmitter shift clock (1X), or the receiver sampling clock<br>(1X). The maximum external receiver/transmitter clock frequency<br>is 4 MHz.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| TRXCA, TRXCB                   | 40.,9         | I/O            | Channel A (B) transmitter/receiver clock: As an input it can<br>supply the receiver, transmitter, counter/timer, or DPLL clock.<br>As an output, it can supply the counter/timer output, the DPLL<br>output, the transmitter shift clock (1X), the receiver sampling<br>clock (1X), the transmitter bit rate generator (BRG) clock (16X),<br>the receiver BRG (16X), or the internal system clock (X1/2). The<br>maximum external receiver/transmitter clock frequency is 4 MHz.                                                                                                                                                                                                                       |  |  |  |  |  |  |

| CTSA/BN,<br>LCA/BN             | 32,17         | I/O            | Channel A (B) clear to send input or loop control output: Active<br>low. The signal can be programmed to act as an enable for the<br>transmitter when not in loop mode. The DUSCC detects logic level<br>transitions on this input and can be programmed to generate an<br>interrupt when a transition occurs. When operating in bit<br>oriented protocol (BOP) loop mode, this pin becomes a loop control<br>output which is asserted and negated by DUSCC commands. This<br>output provides the means of controlling external loop interface<br>hardware to go on-line and off-line without disturbing operation<br>of the loop.                                                                     |  |  |  |  |  |  |

| DCDA/BN,<br>SYNIA/BN           | 38,11         | I              | Channel A (B) data carrier detect or external sync input: The<br>function of this pin is programmable. As a DCD active low input,<br>it acts as an enable for the receiver or can be used as a general<br>purpose input. For the DCD function, the DUSCC detects logic<br>level transitions on this input and can be programmed to generate<br>an interrupt when a transition occurs. As an active low external<br>sync input, it is used in character oriented protocol (COP) modes<br>to obtain character synchronization without receipt of a SYN<br>character. This mode can be used in disc or tape controller<br>applications or for the optional byte timing lead in protocol<br>standard X.21. |  |  |  |  |  |  |

| STAND                          |               | ED             | SIZE 5000 00010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| MILITARY                       | ' DRA         | WING           | A 5962-86810                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| DEFENSE ELECTR                 | IONICS SL     | IPPI Y CEN     | ER REVISION LEVEL SHEET 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

• •