## MC145106

## PLL Frequency Synthesizer CMOS

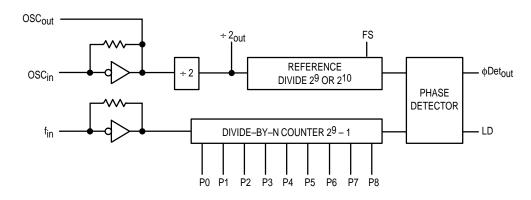

The MC145106 is a phase–locked loop (PLL) frequency synthesizer constructed in CMOS on a single monolithic structure. This synthesizer finds applications in such areas as CB and FM transceivers. The device contains an oscillator/amplifier, a  $2^{10}$  or  $2^{11}$  divider chain for the oscillator signal, a programmable divider chain for the input signal, and a phase detector. The MC145106 has circuitry for a 10.24 MHz oscillator or may operate with an external signal. The circuit provides a 5.12 MHz output signal, which can be used for frequency tripling. A  $2^9$  programmable divider divides the input signal frequency for channel selection. The inputs to the programmable divider are standard ground–to–supply binary signals. Pull–down resistors on these inputs normally set these inputs to ground enabling these programmable inputs to be controlled from a mechanical switch or electronic circuitry.

The phase detector may control a VCO and yields a high level signal when input frequency is low, and a low level signal when input frequency is high. An out–of–lock signal is provided from the on–chip lock detector with a "0" level for the out–of–lock condition.

- Single Power Supply

- Wide Supply Range: 4.5 to 12 V

- Provision for 10.24 MHz Crystal Oscillator

- 5.12 MHz Output

- Programmable Division Binary Input Selects up to 2<sup>9</sup>

- On-Chip Pull-Down Resistors on Programmable Divider Inputs

- Selectable Reference Divider, 2<sup>10</sup> or 2<sup>11</sup> (Including ÷ 2)

- Three–State Phase Detector

- See Application Note AN535 and Article Reprint AR254

- Chip Complexity: 880 FETs or 220 Equivalent Gates

- See the MC145151–2 and MC145152–2 for Higher Performance and Added Flexibility

#### **BLOCK DIAGRAM**

#### REV 3 1/98

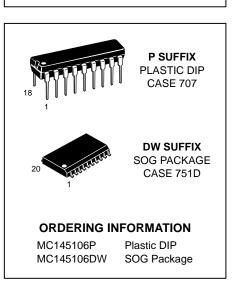

#### **PIN ASSIGNMENTS**

## 查询"MC145106"供应商

| PLASTIC DIP           |    |    |   |     |  |  |  |

|-----------------------|----|----|---|-----|--|--|--|

| V <sub>DD</sub> [     | 1● | 18 | þ | VSS |  |  |  |

| fin 🛙                 | 2  | 17 | þ | P0  |  |  |  |

| osc <sub>in</sub> [   | 3  | 16 | þ | P1  |  |  |  |

| osc <sub>out</sub> [  | 4  | 15 | þ | P2  |  |  |  |

| ÷ 2 <sub>out</sub> [  | 5  | 14 | D | P3  |  |  |  |

| FS [                  | 6  | 13 |   | P4  |  |  |  |

| φDet <sub>out</sub> [ | 7  | 12 | þ | P5  |  |  |  |

| LD 🛛                  | 8  | 11 | þ | P6  |  |  |  |

| P8 [                  | 9  | 10 | þ | P7  |  |  |  |

#### SOG PACKAGE

| V <sub>DD</sub> [     | 1● | 20 | D v <sub>ss</sub> |

|-----------------------|----|----|-------------------|

| f <sub>in</sub> D     | 2  | 19 | ] P0              |

| osc <sub>in</sub> [   | 3  | 18 | ] NC              |

| osc <sub>out</sub> [  | 4  | 17 | ] P1              |

| ÷ 2 <sub>out</sub> [  | 5  | 16 | ] P2              |

| FS [                  | 6  | 15 | ] P3              |

| φDet <sub>out</sub> [ | 7  | 14 | ] P4              |

| LD [                  | 8  | 13 | ] NC              |

| P8 [                  | 9  | 12 | ] P5              |

| P7 [                  | 10 | 11 | ] P6              |

|                       |    |    |                   |

NC = NO CONNECTION

#### MAXIMUM RATINGS (Voltages Referenced to VSS)

| Parameter                   | Symbol           | Value                          | Unit |

|-----------------------------|------------------|--------------------------------|------|

| DC Supply Voltage           | V <sub>DD</sub>  | – 0.5 to + 12                  | V    |

| Input Voltage, All Inputs   | V <sub>in</sub>  | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Input Current, per Pin   | I                | ± 10                           | mA   |

| Operating Temperature Range | ТĄ               | – 40 to + 85                   | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | – 65 to + 150                  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub>  $\leq$  (V<sub>in</sub> or V<sub>out</sub>)  $\leq$  V<sub>DD</sub>.

### **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ Unless Otherwise Stated, Voltages Referenced to $V_{SS}$ )

| 查询"MC145106"供应商                                                                   |           |                   | V <sub>DD</sub> | All Types               |                         |                         |               |

|-----------------------------------------------------------------------------------|-----------|-------------------|-----------------|-------------------------|-------------------------|-------------------------|---------------|

| Characteristic                                                                    |           | Symbol            | Vdc             | Min                     | Тур*                    | Max                     | Unit          |

| Power Supply Voltage Range                                                        |           | V <sub>DD</sub>   |                 | 4.5                     | _                       | 12                      | V             |

| Supply Current                                                                    |           | IDD               | 5.0<br>10<br>12 |                         | 6<br>20<br>28           | 10<br>35<br>50          | mA            |

| Input Voltage                                                                     | "0" Level | VIL               | 5.0<br>10<br>12 | _<br>_<br>_             |                         | 1.5<br>3.0<br>3.6       | V             |

|                                                                                   | "1" Level | VIH               | 5.0<br>10<br>12 | 3.5<br>7.0<br>8.4       | <br><br>                |                         |               |

| Input Current<br>FS, Pull–Up Resistor Source Current)                             | "0" Level | l <sub>in</sub>   | 5.0<br>10<br>12 | - 5.0<br>- 15<br>- 20   | - 20<br>- 60<br>- 80    | - 50<br>- 150<br>- 200  | μA            |

| (P0 – P8)                                                                         |           |                   | 5.0<br>10<br>12 |                         |                         | - 0.3<br>- 0.3<br>- 0.3 |               |

| (FS)                                                                              | "1" Level |                   | 5.0<br>10<br>12 |                         | <br><br>                | 0.3<br>0.3<br>0.3       |               |

| (P0 – P8, Pull–Down Resistor Sink Current)                                        |           |                   | 5.0<br>10<br>12 | 7.5<br>22.5<br>30       | 30<br>90<br>120         | 75<br>225<br>300        |               |

| (OSC <sub>in</sub> , f <sub>in</sub> )                                            | "0" Level |                   | 5.0<br>10<br>12 | - 2.0<br>- 6.0<br>- 9.0 | - 6.0<br>- 25<br>- 37   | - 15<br>- 62<br>- 92    |               |

| (OSC <sub>in</sub> , f <sub>in</sub> )                                            | "1" Level |                   | 5.0<br>10<br>12 | 2.0<br>6.0<br>9.0       | 6.0<br>25<br>37         | 15<br>62<br>92          |               |

| Output Drive Current<br>$(V_O = 4.5 V)$<br>$(V_O = 9.5 V)$<br>$(V_O = 11.5 V)$    | Source    | ЮН                | 5.0<br>10<br>12 | - 0.7<br>- 1.1<br>- 1.5 | - 1.4<br>- 2.2<br>- 3.0 | <br><br>                | mA            |

| (V <sub>O</sub> = 0.5 V)<br>(V <sub>O</sub> = 0.5 V)<br>(V <sub>O</sub> = 0.5 V)  | Sink      | lol               | 5.0<br>10<br>12 | 0.9<br>1.4<br>2.0       | 1.8<br>2.8<br>4.0       | <br><br>                |               |

| Input Amplitude<br>(f <sub>in</sub> @ 4.0 MHz)<br>(OSC <sub>in</sub> @ 10.24 MHz) |           | —                 | _               | 1.0<br>1.5              | 0.2<br>0.3              |                         | V p–µ<br>Sine |

| Input Resistance<br>(OSC <sub>in</sub> , f <sub>in</sub> )                        |           | R <sub>in</sub>   | 5.0<br>10<br>12 | <br>                    | 1.0<br>0.5<br>—         | <br><br>                | MΩ            |

| Input Capacitance<br>(OSC <sub>in</sub> , f <sub>in</sub> )                       |           | C <sub>in</sub>   | _               | -                       | 6.0                     | —                       | pF            |

| Three–State Leakage Current<br>(¢Det <sub>out</sub> )                             |           | loz               | 5.0<br>10<br>12 | _<br>_<br>_             |                         | 1.0<br>1.0<br>1.0       | μA            |

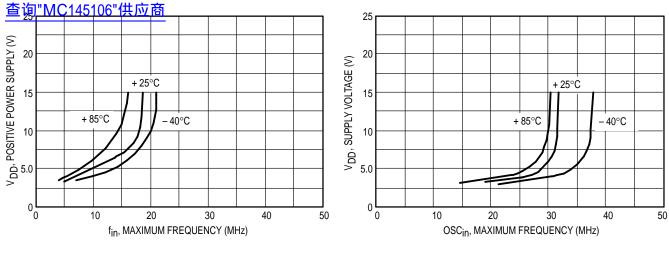

| Input Frequency<br>(- 40 to + 85°C)                                               |           | f <sub>in</sub>   | 4.5<br>12       | 0<br>0                  |                         | 4.0<br>4.0              | MHz           |

| Oscillator Frequency<br>(– 40 to + 85°C)                                          |           | OSC <sub>in</sub> | 4.5<br>12       | 0.1<br>0.1              | _                       | 10.24<br>10.24          | MHz           |

\*Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

### **TYPICAL CHARACTERISTICS\***

Figure 2. Maximum Oscillator Input Frequency versus Supply Voltage

\* Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

#### **TRUTH TABLE**

| Selection |    |    |    |    |            |    |    |    |             |

|-----------|----|----|----|----|------------|----|----|----|-------------|

| P8        | P7 | P6 | P5 | P4 | <b>P</b> 3 | P2 | P1 | P0 | Divide by N |

| 0         | 0  | 0  | 0  | 0  | 0          | 0  | 0  | 0  | 2*          |

| 0         | 0  | 0  | 0  | 0  | 0          | 0  | 0  | 1  | 3*          |

| 0         | 0  | 0  | 0  | 0  | 0          | 0  | 1  | 0  | 2           |

| 0         | 0  | 0  | 0  | 0  | 0          | 0  | 1  | 1  | 3           |

| 0         | 0  | 0  | 0  | 0  | 0          | 1  | 0  | 0  | 4           |

| •         | •  | •  | •  | •  | •          | •  | •  | •  | •           |

| :         |    | :  |    |    |            |    | :  |    | :           |

| 0         | 1  | 1  | 1  | 1  | 1          | 1  | 1  | 1  | 255         |

| •         | •  | •  | •  | •  | •          | •  | •  | •  | •           |

|           | :  |    |    |    |            |    |    |    | •           |

| 1         | 1  | 1  | 1  | 1  | 1          | 1  | 1  | 1  | 511         |

1: Voltage level = V<sub>DD</sub>.

0: Voltage level = 0 or open circuit input.

\* The binary setting of 0000000 and 0000001 on P8 to P0 results in a 2 and 3 division which is not in the  $2^{N} - 1$  sequence. When pin is not connected the logic signal on that pin can be treated as a "0".

#### **PIN DESCRIPTIONS**

#### P0 – P8

Programmable Inputs (PDIP — Pins 17 – 9; SOG — Pins 19, 17 – 14, 12 – 9)

Programmable divider inputs (binary).

#### fin

#### Frequency Input (PDIP, SOG — Pin 2)

Frequency input to programmable divider (derived from VCO).

#### OSCin, OSCout

# Oscillator Input and Oscillator Output (PDIP, SOG — Pins 3, 4)

Oscillator/amplifier input and output terminals.

#### LD Lock Detector (PDIP, SOG — Pin 8)

LD is high when loop is locked, pulses low when out–of–lock.

####

Signal for control of external VCO, output high when  $f_{in}/N$  is less than the reference frequency; output low when  $f_{in}/N$  is greater than the reference frequency. Reference frequency is the divided down oscillator — input frequency typically 5.0 or 10 kHz.

#### NOTE

Phase Detector Gain =  $V_{DD}/4\pi$ .

#### FS

# Reference Oscillator Frequency Division Select (PDIP, SOG — Pin 6)

When using 10.24 MHz OSC frequency, this control selects 10 kHz, a "0" selects 5.0 kHz.

#### ÷ 2out (PDIP, SOG - Pin 5)

Reference OSC frequency divided by 2 output; when using 10.24 MHz OSC frequency, this output is 5.12 MHz for frequency tripling applications.

#### V<sub>DD</sub>

Positive Power Supply (PDIP, SOG - Pin 1)

#### Vss

Ground (PDIP — Pin 18, SOG — Pin 20)

#### PLL SYNTHESIZER APPLICATIONS

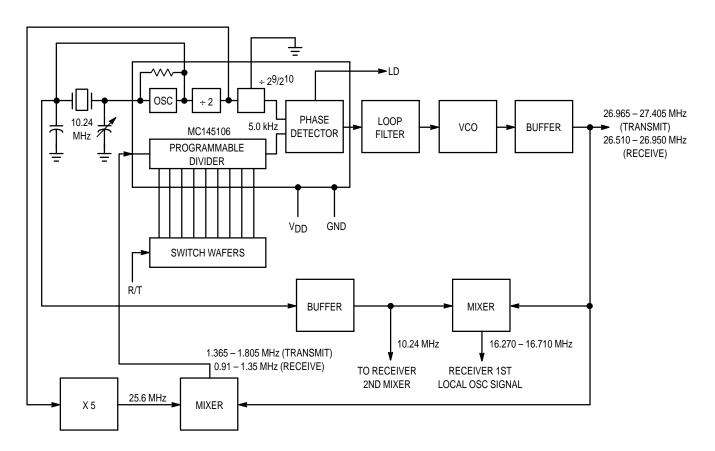

**The WC45606 WEIGHT** d for applications in CB radios because of the channelized frequency requirements. A typical 40 channel CB transceiver synthesizer, using a single crystal reference, is shown in Figure 3 for receiver IF values of 10.695 MHz and 455 kHz.

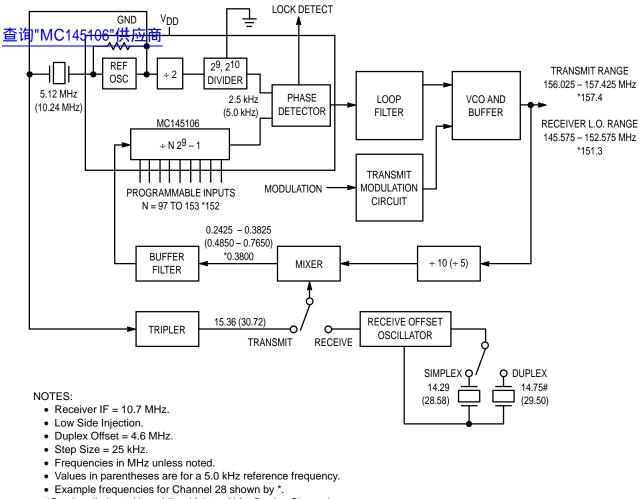

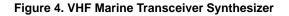

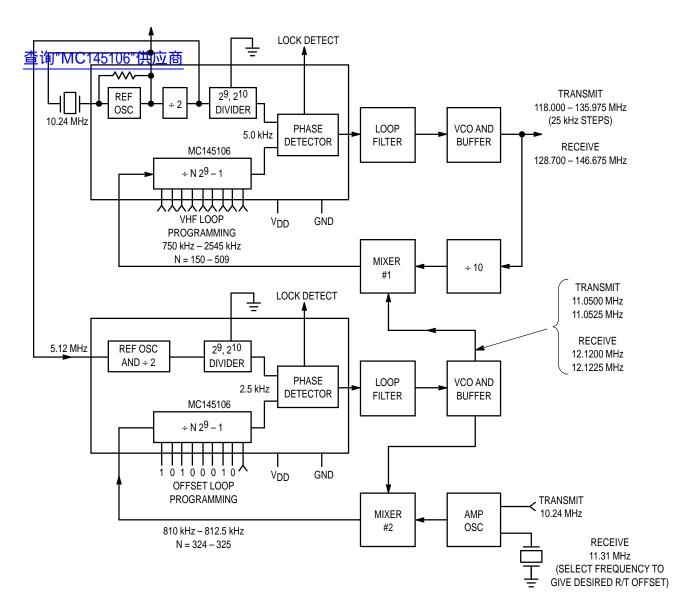

In addition to applications in CB radios, the MC145106 can be used as a synthesizer for several other systems. Various frequency spectrums can be achieved through the use of proper offset, prescaling, and loop programming techniques. In general, 300 – 400 channels can be synthesized using a single loop, with many additional channels available when multiple loop approaches are employed. Figures 4 and 5 are examples of some possibilities.

In the aircraft synthesizer of Figure 5, the VHF loop (top) will provide a 50 kHz, 360 channel system with 10.7 MHz R/T offset when only the 11.0500 MHz (transmit) and

12.1200 MHz (receive) frequencies are provided to mixer #1. When these signals are provided with crystal oscillators, the result is a three crystal 360 channel, 50 kHz step synthesizer. When using the offset loop (bottom) in Figure 5 to provide the indicated injection frequencies for mixer #1 (two for transmit and two for receive) 360 additional channels are possible. This results in a 720–channel, 25 kHz step synthesizer which requires only two crystals and provides R/T offset capability. The receive offset value is determined by the 11.31 MHz crystal frequency and is 10.7 MHz for the example.

The VHF marine synthesizer in Figure 4 depicts a single loop approach for FM transceivers. The VCO operates on frequency during transmit and is offset downward during receive. The offset corresponds to the receive IF (10.7 MHz) for channels having identical receive/transmit frequencies (simplex), and is (10.7 - 4.6 = 6.1) MHz for duplex channels. Carrier modulation is introduced in the loop during transmit.

Figure 3. Single Crystal CB Synthesizer Featuring On–Frequency VCO During Transmit

#Can be eliminated by adding 184 to + N for Duplex Channels.

Figure 5. VHF Aircraft 720 Channel Two Crystal Frequency Synthesizer

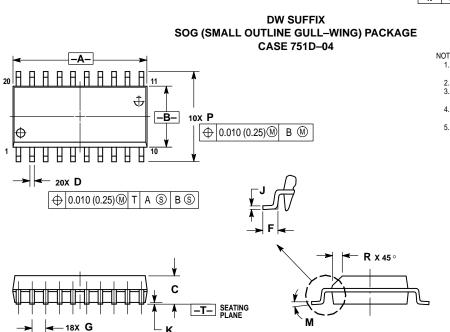

#### PACKAGE DIMENSIONS

查询"MC145106"供应商

$\cap$

ስ ስ ስ

D

G

ጥ

10

B

С

SEATING PLANE

ለ ለ ለ ለ

P SUFFIX PLASTIC DIP (DUAL IN–LINE PACKAGE) CASE 707–02

NOTES:

2.

POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25 (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | MILLIM | ETERS | INC       | HES   |  |

|-----|--------|-------|-----------|-------|--|

| DIM | MIN    | MAX   | MIN       | MAX   |  |

| Α   | 22.22  | 23.24 | 0.875     | 0.915 |  |

| В   | 6.10   | 6.60  | 0.240     | 0.260 |  |

| С   | 3.56   | 4.57  | 0.140     | 0.180 |  |

| D   | 0.36   | 0.56  | 0.014     | 0.022 |  |

| F   | 1.27   | 1.78  | 0.050     | 0.070 |  |

| G   | 2.54   | BSC   | 0.100 BSC |       |  |

| н   | 1.02   | 1.52  | 0.040     | 0.060 |  |

| J   | 0.20   | 0.30  | 0.008     | 0.012 |  |

| K   | 2.92   | 3.43  | 0.115     | 0.135 |  |

| L   | 7.62   | BSC   | 0.300     | BSC   |  |

| М   | 0°     | 15°   | 0°        | 15°   |  |

| N   | 0.51   | 1.02  | 0.020     | 0.040 |  |

| NOT | ES:                              |

|-----|----------------------------------|

| 1.  | DIMENSIONING AND TOLERANCING PER |

ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.150

(0.006) PER SIDE. 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE

DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INCHES |       |  |

|-----|--------|--------|--------|-------|--|

| DIM | MIN    | MAX    | MIN    | MAX   |  |

| Α   | 12.65  | 12.95  | 0.499  | 0.510 |  |

| В   | 7.40   | 7.60   | 0.292  | 0.299 |  |

| С   | 2.35   | 2.65   | 0.093  | 0.104 |  |

| D   | 0.35   | 0.49   | 0.014  | 0.019 |  |

| F   | 0.50   | 0.90   | 0.020  | 0.035 |  |

| G   | 1.27   | BSC    | 0.050  | BSC   |  |

| J   | 0.25   | 0.32   | 0.010  | 0.012 |  |

| ĸ   | 0.10   | 0.25   | 0.004  | 0.009 |  |

| М   | 0 °    | 7 °    | 0 °    | 7°    |  |

| Р   | 10.05  | 10.55  | 0.395  | 0.415 |  |

| R   | 0.25   | 0.75   | 0.010  | 0.029 |  |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and *Q* are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado, 80217. 1-303-675-2140 or 1-800-441-2447

Mfax™: RMFAX0@email.sps.mot.com

- TOUCHTONE 1-602-244-6609

Motorola Fax Back System

- US & Canada ONLY 1-800-774-1848

- http://sps.motorola.com/mfax/

٥

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

JAPAN: Nippon Motorola Ltd.; SPD, Strategic Planning Office; 4-32-1, Nishi-Gotanda; Shinagawa-ku, Tokyo 141, Japan. 81-3-5487-8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

CUSTOMER FOCUS CENTER: 1-800-521-6274