www.ti.com SLAS672 - SEPTEMBER 2009

# 64 Channel Analog Front End for Digital X-Ray Detector

Check for Samples : AFE0064

### **FEATURES**

- 64 Channels

- 28.32 µSec Min Scan Time (including integration and data transfer for all 64 channels)

- 7.5 MHz Max Data Transfer Rate

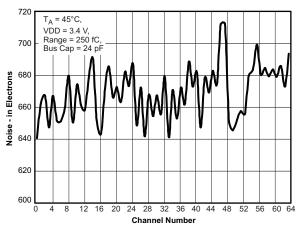

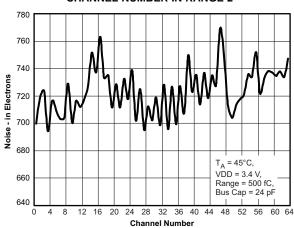

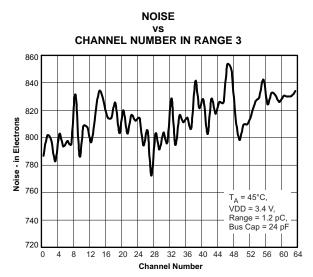

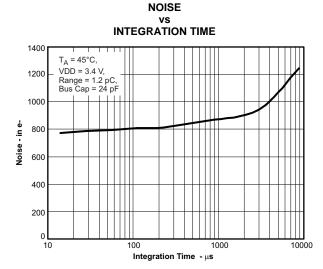

- Noise 824 e-RMS with 30 pF Sensor Capacitor in 1.2 pC Range

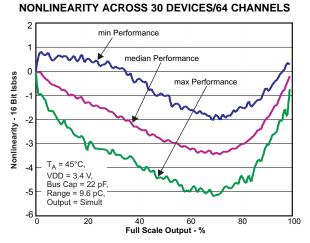

- Integral Nonlinearity: ±0.006% of FSR

- Eight Adjustable Full Scale Ranges (0.13 pC min to 9.5 pC max)

- Built in CDS (signal sample offset sample)

- Selectable Integration Up/Down Mode

- Low Power: 175 mWNAP Mode: 49.5 mW

- 14 mm x 14 mm 128 Pin TQFP Package

### **APPLICATIONS**

- Digital Radiography

- CT Scanners

- Baggage Scanners

- Infrared Spectroscopy

### **DESCRIPTION**

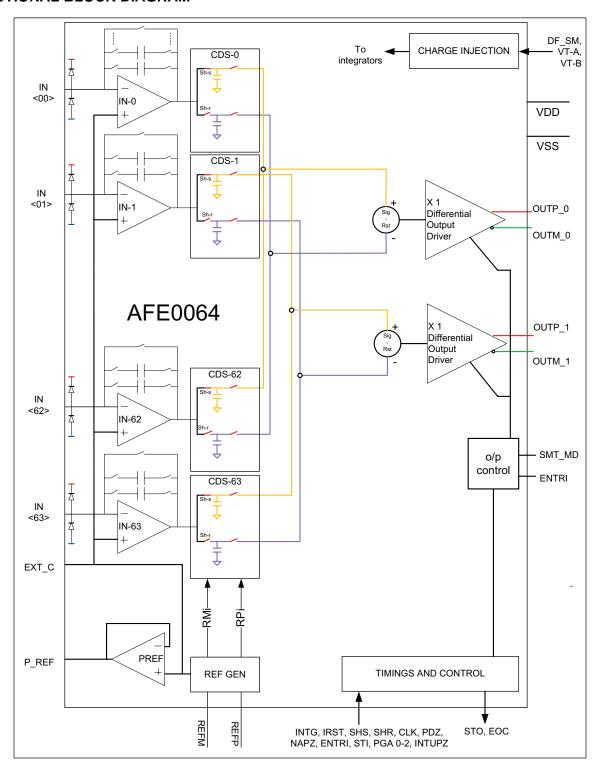

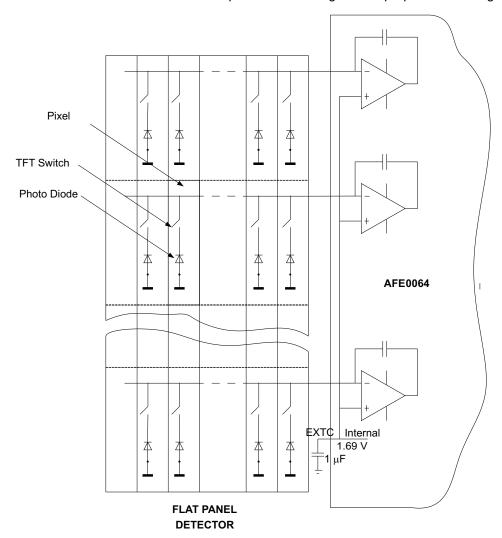

The AFE0064 is a 64 channel analog front end designed to suit the requirements of flat panel detector based digital X-ray systems.

AFE0064

The device includes 64 integrators, a PGA for full scale charge level selection, correlated double sampler, 64 as to 2 multiplexer, and two differential output drivers.

Hardware selectable Integration polarity allows integration of a positive or negative charge and provides more flexibility in system design. In addition, the device features TFT (Thin Film Transistor from Flat Panel Detector) charge injection compensation. This feature helps maximize the usable signal charge range of the device.

The nap feature enables substantial power saving. This is especially useful for power saving during long X-ray exposure periods.

The AFE0064 is available in a 128 pin TQFP package.

### ORDERING INFORMATION<sup>(1)</sup>

| MODEL    | INTEGRAL<br>LINEARITY<br>% of FS | POWER<br>DISSIPATION | MIN SCAN<br>TIME<br>(μSec) | NUMBER OF<br>CHANNELS | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QUANTITY |

|----------|----------------------------------|----------------------|----------------------------|-----------------------|-----------------|-----------------------|----------------------|-------------------------|--------------------------------|

| AFE0064  | 0.006                            | 175 mW               | 28.32                      | 64                    | TQFP            | PBK                   | -40 to 85°C          | AFE0064IPBK             | 90(5+1)                        |

| AI LUUU4 | 0.000                            | 17311100             | 20.32                      | 04                    | TQIF            | FBR                   | -40 to 65 C          | AFE0064IPBKR            | 1000                           |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

df.dzsc.com

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **FUNCTIONAL BLOCK DIAGRAM**

<u>₩豐梅們FE0064IPBK"供应商</u>

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                                           |                       | VALUE / UNIT                                |

|-------------------------------------------|-----------------------|---------------------------------------------|

| IN <n> to VSS</n>                         |                       | -0.3 V to +VDD + 0.3 V                      |

| VDD to AGND                               |                       | −0.3 V to 5 V                               |

| Digital input voltage to GND              |                       | -0.3 V to (+VDD + 0.3 V)                    |

| Digital output to GND                     |                       | -0.3 V to (+VDD + 0.3 V)                    |

| Operating temperature range               |                       | -40°C to 85°C                               |

| Storage temperature range                 |                       | −65°C to 150°C                              |

| Junction temperature (T <sub>J</sub> max) |                       | 150°C                                       |

| TQFP package <sup>(2)</sup>               | Power dissipation     | (T <sub>J</sub> max – T <sub>A</sub> )/ θJA |

| TOFF Package                              | θJA Thermal impedance | 45°C/W                                      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **SPECIFICATIONS**

$T_A$  = 25 to 85°C, +VDD = 3.3 V,  $f_{CLK}$  = 15 MHz for sequential mode and 3.75 MHz for simultaneous mode, scan time = 28.32  $\mu$ s (unless otherwise noted)

| PARAMETER                                | TEST CONDITIONS | MIN              | TYP  | MAX             | UNIT |

|------------------------------------------|-----------------|------------------|------|-----------------|------|

| ANALOG INPUT RANGE                       |                 |                  |      | ,               |      |

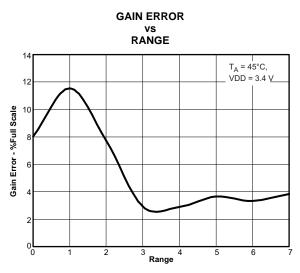

| Range 0                                  |                 |                  | 0.13 |                 | ρС   |

| Range 1                                  |                 |                  | 0.25 |                 | ρC   |

| Range 2                                  |                 |                  | 0.5  |                 | ρС   |

| Range 3                                  |                 |                  | 1.2  |                 | ρC   |

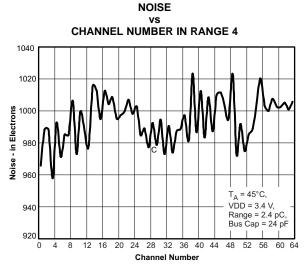

| Range 4                                  |                 |                  | 2.4  |                 | ρC   |

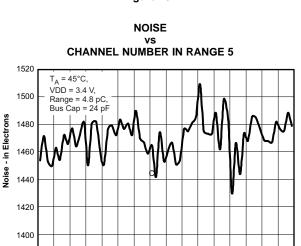

| Range 5                                  |                 |                  | 4.8  |                 | ρC   |

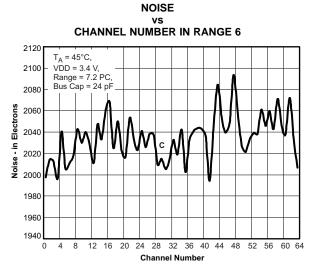

| Range 6                                  |                 |                  | 7.2  |                 | ρС   |

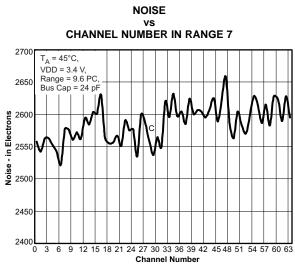

| Range 7                                  |                 |                  | 9.6  |                 | ρC   |

| Input current                            |                 |                  | 30   |                 | μΑ   |

| Integrator positive input voltage        |                 | 1.66             | 1.68 | 1.70            | V    |

| ANALOG OUTPUT                            |                 |                  |      |                 |      |

| Differential full scale analog output    | For all ranges  | –(REFP-<br>REFM) | ±1.4 | (REFP-<br>REFM) | V    |

| Output common-mode voltage (REFP+REFM)/2 |                 |                  | 1.55 |                 |      |

Copyright © 2009, Texas Instruments Incorporated

<sup>(2)</sup> Device confirms to MSL level 3 at 260°C as per JEDEC -033.

# **SPECIFICATIONS** (continued)

$T_A$  = 25 to 85°C, +VDD = 3.3 V,  $f_{CLK}$  = 15 MHz for sequential mode and 3.75 MHz for simultaneous mode, scan time = 28.32  $\mu$ s (unless otherwise noted)

| PARAMETER                                                                              | TEST CONDITIONS                                                           | MIN     | TYP    | MAX            | UNIT                       |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------|--------|----------------|----------------------------|

| ACCURACY                                                                               |                                                                           |         |        |                |                            |

|                                                                                        | C-sensor <sup>(1)</sup> 1= 30 pF, Range 3, 14 μSec integration time       |         | 824    |                |                            |

| Noise in electrons referred to input of integrator                                     | C-sensor <sup>(1)</sup> = 20 pF, Range 3 14 $\mu$ Sec integration time    |         | 600    |                | e-                         |

|                                                                                        | C-sensor <sup>(1)</sup> = 30 pF, Range 3, 270 μSec integration time       |         | 1400   |                |                            |

| Integral nonlinearity                                                                  |                                                                           |         | ±0.006 |                | % of<br>FSR <sup>(2)</sup> |

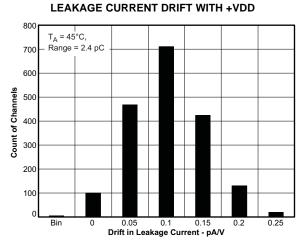

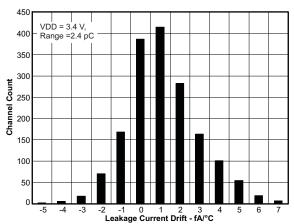

| Analog input channel leakage current                                                   | This current is integrated and reflects as a part of offset error.        |         | 2      |                | pA                         |

| Channel to channel full-scale error matching                                           | For ranges 3 to 7                                                         |         | ±0.7   |                | % of<br>FSR <sup>(2)</sup> |

| Offset error                                                                           | Device output offset, resulting from integration of input leakage current |         | ±0.07  |                | % of<br>FSR <sup>(2)</sup> |

| Channel to channel offset error matching                                               |                                                                           |         | ±0.07  |                | % of<br>FSR <sup>(2)</sup> |

| Integrator input offset:(difference between integrator positive and negative terminal) | Integrator input offset mean across channels                              |         | ±0.002 |                | mV                         |

| Integrator input offset matching across channels                                       | ±3 sigma limit of integrator input offset across channels                 |         | ±1.5   |                | mV                         |

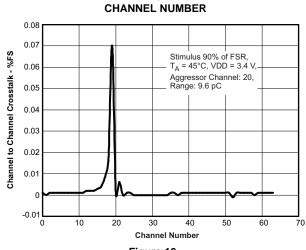

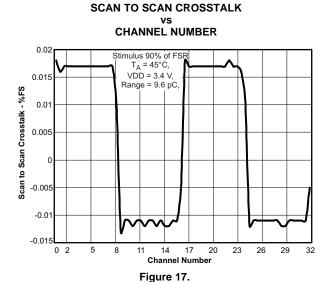

| Channel to channel crosstalk                                                           | Aggressor channel with full scale charge to next adjacent channel         |         | 0.08   |                | % of<br>FSR <sup>(2)</sup> |

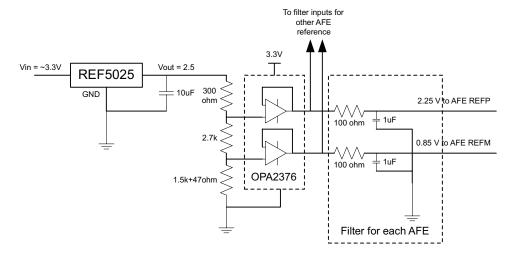

| EXTERNAL REFERENCE INPUT                                                               |                                                                           | II.     |        | 1              |                            |

| REFP                                                                                   |                                                                           | 2.24    | 2.25   | +VDD -<br>0.85 | V                          |

| REFM                                                                                   |                                                                           | 0.84    | 0.85   | 0.86           | V                          |

| Input current                                                                          |                                                                           |         | 50     |                | nΑ                         |

| P_REF output                                                                           |                                                                           |         | 1.68   |                | V                          |

| P_REF current source capacity                                                          |                                                                           |         | ±1     |                | mA                         |

| POWER SUPPLY REQUIREMENTS                                                              |                                                                           |         |        |                |                            |

| Power supply voltage, +VDD                                                             |                                                                           | 3.2     | 3.3    | 3.6            |                            |

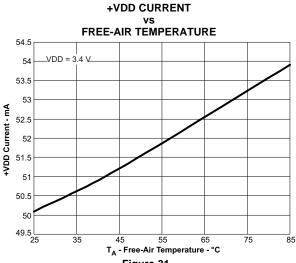

| D                                                                                      | During operation                                                          |         | 53     | 58             | mA                         |

| Power supply current                                                                   | During NAP                                                                |         | 15     |                | mA                         |

| Power up time from NAP                                                                 |                                                                           |         | 10     |                | μSec                       |

| DIGITAL INPUT OUTPUT                                                                   |                                                                           |         |        |                |                            |

| Logic levels                                                                           |                                                                           |         |        |                |                            |

| V <sub>IH</sub>                                                                        |                                                                           | 0.8×VDD |        | VDD+0.1        |                            |

| V <sub>IL</sub>                                                                        |                                                                           | -0.1    |        | 0.2×VDD        |                            |

| V <sub>OH</sub>                                                                        | I <sub>OH</sub> = -500 μA                                                 | VDD-0.4 |        |                |                            |

| V <sub>OL</sub>                                                                        | I <sub>OL</sub> = 500 μA                                                  |         |        | 0.4            |                            |

| TEMPERATURE RANGE                                                                      | 1                                                                         | IL .    |        |                |                            |

| Operating free air                                                                     |                                                                           | 0       |        | 85             | °C                         |

<sup>(1)</sup> C-Sensor is total external capacitance seen at IN(x) pin. This includes capacitance of all the TFT switches connected to that node and the routing capacitance.

<sup>(2)</sup> FSR is full-scale range. There are eight ranges from 0.13 pC to 9.6 pC.

<u>₩豐铈™FE0064IPBK"供应商</u>

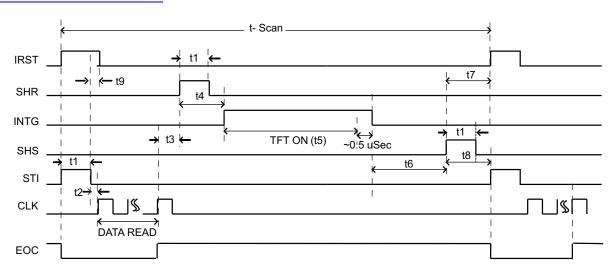

# **TIMING REQUIREMENTS**

$T_A = 0$  to 85°C, +VDD = 3.3 V

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PARAMETER                                                                                  | MIN  | TYP | MAX     | UNIT  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-----|---------|-------|--|--|--|

| t-scan Scan time, See Figure 1, Figure 7  11 IRST, SHR, SHS, STI high duration, See Figure 1, Figure 7  12 Setup time, STI falling edge to first clock rising edge, See Figure 1, Figure 7  13 Setup time, IRST falling edge to first clock rising edge, See Figure 1, Figure 7  14 Setup time, IRST falling edge to SHR rising edge, See Figure 1, Figure 7  15 Delay time, 133 <sup>rd</sup> clock rising edge to SHR rising edge, See Figure 1, Figure 7  16 Delay time, INTG falling edge to INTG rising edge, See Figure 1, Figure 7  17 Delay time, INTG falling edge to SHS rising edge, See Figure 1, Figure 7  18 Delay time, SHS rising edge to IRST rising edge, See Figure 1, Figure 7  19 Hold time, STI falling edge to IRST falling edge, See Figure 1, Figure 7  10 Interval 10 Inte |                                                                                            |      |     |         |       |  |  |  |

| t-scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Scan time, See Figure 1, Figure 7                                                          |      |     | See (1) | μSec  |  |  |  |

| t1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IRST, SHR, SHS, STI high duration, See Figure 1, Figure 7                                  | 30   |     |         | nSec  |  |  |  |

| t2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Setup time, STI falling edge to first clock rising edge, See Figure 1, Figure 7            | 30   |     |         | nSec  |  |  |  |

| t2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Setup time, IRST falling edge to first clock rising edge, See Figure 1, Figure 7           | 30   |     |         | nSec  |  |  |  |

| t3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Delay time, 133 <sup>rd</sup> clock rising edge to SHR rising edge, See Figure 1, Figure 7 | 400  |     |         | nSec  |  |  |  |

| t4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Delay time, SHR rising edge to INTG rising edge, See Figure 1, Figure 7                    | 30   |     |         | nSec  |  |  |  |

| t5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INTG high duration (TFT on time), See Figure 1, Figure 7                                   | 14   |     | See (2) | μSec  |  |  |  |

| t6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Delay time, INTG falling edge to SHS rising edge, See Figure 1, Figure 7                   | 4.5  |     |         | μSec  |  |  |  |

| t7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Delay time, SHS rising edge to IRST rising edge, See Figure 1                              | 30   |     |         | nSec  |  |  |  |

| t8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Delay time, SHS rising edge to STI rising edge, See Figure 1, Figure 7                     | 30   |     |         | nSec  |  |  |  |

| t9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Hold time, STI falling edge to IRST falling edge, See Figure 1, Figure 7                   | 10   |     |         | nSec  |  |  |  |

| In sequential mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Clash (CLV) fragues                                                                        | 1    |     | 15      | MHz   |  |  |  |

| In simult mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Clock (CLK) frequency                                                                      | 0.25 |     | 3.75    | IVI□Z |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OUTP or OUTM settling time to 16 bit accuracy with 30 pF load and full scale step          |      |     | 375     | nSec  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OUTP or OUTM settling time to 16 bit accuracy with 15 pF load and full scale step          |      |     | 250     | nSec  |  |  |  |

<sup>(1)</sup> See max specification for t5 and minimum specification for CLK frequency. Also see the section Running the Device at Higher Scan Time.

<sup>(2)</sup> There is no real limit on maximum integration time, however as integration time increases the offset value changes due to integration of leakage current (2 pA typical) also the 1/f noise contribution to output increases, refer to the typical noise numbers at 14 and 270 μSec integration time in the Specifications table and also see Figure 28.

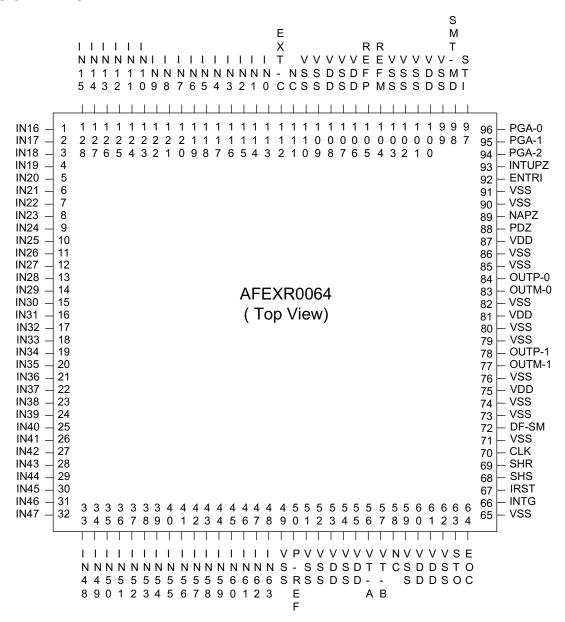

#### **DEVICE INFORMATION**

#### PIN ASSIGNMENTS

### **PIN FUNCTIONS**

| P              | PIN              |           | DECODIPTION                              |  |  |  |  |

|----------------|------------------|-----------|------------------------------------------|--|--|--|--|

| NUMBER         | NAME             | 1/0       | DESCRIPTION                              |  |  |  |  |

|                |                  |           | ANALOG INPUT PINS                        |  |  |  |  |

| 113128         | IN<0><br>IN<15>  | I         | Analog input channels from 0 to 63       |  |  |  |  |

| 1 48           | IN<16><br>IN<63> | I         |                                          |  |  |  |  |

|                |                  |           | DIFFERENTIAL ANALOG OUTPUT PINS          |  |  |  |  |

| 84             | OUTP-0           | 0         | Driver 0-analog output positive terminal |  |  |  |  |

| 83             | OUTM-0           | 0         | Driver 0-analog output negative terminal |  |  |  |  |

| river 0 output | ts analog data f | or channe | els 31 to 0                              |  |  |  |  |

# **PIN FUNCTIONS (continued)**

| Г                                                  |                  |             | PIN FUNCTIONS (continued)                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | IN               | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |

| NUMBER                                             | NAME             |             | 2200                                                                                                                                                                                                                                                                                                                                   |

| 78                                                 | OUTP-1           | 0           | Driver 1-analog output positive terminal                                                                                                                                                                                                                                                                                               |

| 77                                                 | OUTM-1           | 0           | Driver 1-analog output negative terminal                                                                                                                                                                                                                                                                                               |

| Driver 1 output                                    | s analog data f  | or channe   | els 63 to 32                                                                                                                                                                                                                                                                                                                           |

| Note that the c                                    | levice output is | differentia | al (OUTP-OUTM) with common mode of (OUTP+OUTM)/2                                                                                                                                                                                                                                                                                       |

|                                                    |                  |             | REFERENCE                                                                                                                                                                                                                                                                                                                              |

| 105                                                | REFP             | I           | Positive reference input                                                                                                                                                                                                                                                                                                               |

| 104                                                | REFM             | I           | Negative reference input                                                                                                                                                                                                                                                                                                               |

| Decouple REF at output termi                       |                  | rminals to  | VSS with suitable capacitor and use low noise reference, noise on these terminals will add to noise                                                                                                                                                                                                                                    |

| 112                                                | EXT_C            | 0           | Terminal available for decoupling internally generated integrator common-mode voltage (1.68 V). Decouple this pin to VSS with 1 µF ceramic capacitor. Internally connected to +ve terminals of all 64 integrators.                                                                                                                     |

| 50                                                 | P_REF            | 0           | Internally generated 1.68 V reference output available for referencing photodiode cathodes.                                                                                                                                                                                                                                            |

|                                                    |                  |             | CONTROL PINS                                                                                                                                                                                                                                                                                                                           |

| 63                                                 | STO              | 0           | Delayed ST for cascading next ASIC                                                                                                                                                                                                                                                                                                     |

| 64                                                 | EOC              | 0           | End of data shifting, EOC is low during data read.                                                                                                                                                                                                                                                                                     |

| 66                                                 | INTG             | I           | Filter bandwidth control for Signal sample (SHS). Filter BW is high when this signal is high and filter BW is low when this signal is low. Typically this signal should go high with TFT switch turn on and should go low ~0.5 µSec after TFT switch off.                                                                              |

| 67                                                 | IRST             | I           | Resets the integrator capacitors on rising edge of this input.                                                                                                                                                                                                                                                                         |

| 68                                                 | SHS              | I           | Device samples 'signal' level of integrator output(0 to 63) onto the respective CDS on rising edge of this input.                                                                                                                                                                                                                      |

| 69                                                 | SHR              | I           | Device samples 'reset' level of integrator output (0 to 63) onto the respective CDS on rising edge of this input.                                                                                                                                                                                                                      |

| 70                                                 | CLK              | I           | For simultaneous mode: Device serially outputs the analog voltage from each integrator channel on each rising edge of CLK.                                                                                                                                                                                                             |

|                                                    |                  |             | For sequential mode: Device serially outputs the analog voltage from each integrator channel on every fourth rising edge of CLK.                                                                                                                                                                                                       |

| 88                                                 | PDz              | I           | Low level puts device in powerdown mode.                                                                                                                                                                                                                                                                                               |

| 89                                                 | NAPz             | I           | Low level puts device in NAP mode, this is useful for power saving during X-ray exposure period.                                                                                                                                                                                                                                       |

| 92                                                 | ENTRI            | - 1         | High on this pin enables 3-state of analog output drivers after shift out of data for all 64 channels.                                                                                                                                                                                                                                 |

| 97                                                 | STI              | I           | Rising edge resets the channel counter. Falling edge enables data transfer on OUTP and OUTM terminals.                                                                                                                                                                                                                                 |

|                                                    |                  | 1           | PGA-I/P RANGE SELECTION                                                                                                                                                                                                                                                                                                                |

| 94                                                 | PGA-2            | I           | Selects eight different analog input ranges. Three bit word with these three bits represents binary number corresponding to Analog Input Range. PGA-2 is MSB and PGA-0 is LSB. Example 000 is                                                                                                                                          |

| 95                                                 | PGA-1            | I           | range 0 and 100 is range 4.                                                                                                                                                                                                                                                                                                            |

| 96                                                 | PGA-0            | I           |                                                                                                                                                                                                                                                                                                                                        |

|                                                    |                  | 1           | MODE SELECTION                                                                                                                                                                                                                                                                                                                         |

| 93                                                 | INTUPz           | I           | High level selects 'integration-down' mode. In this mode device integrates positive pixel current into each channels, starting from reset level (REFP) down to REFM low level selects 'integration-up' mode. In this mode the device integrates negative pixel current into each channel, starting from reset level (REFM) up to REFP. |

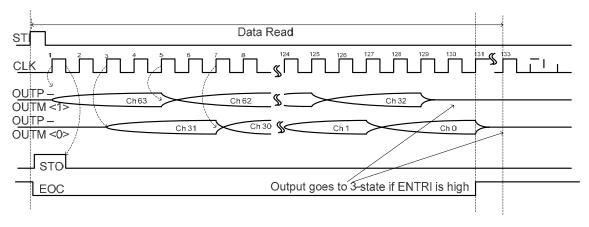

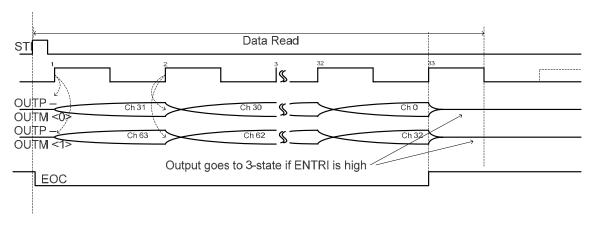

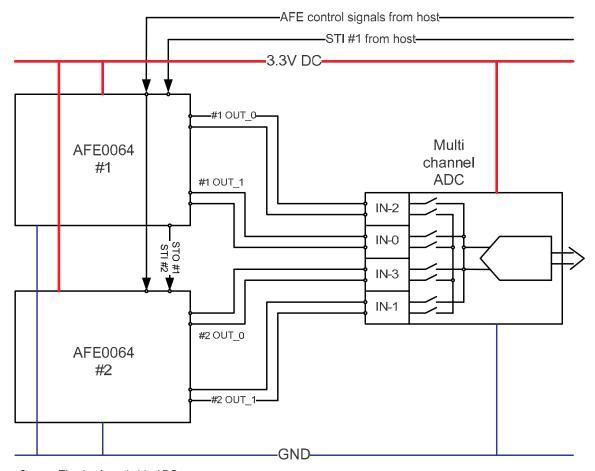

| 98                                                 | SMT-MD           | I           | High level selects simultaneous mode. Device outputs data simultaneously on both differential output drivers OUTP-OUTM<0> and OUTP-OUTM<1> in this mode.                                                                                                                                                                               |

|                                                    |                  |             | Low level on this input selects sequential mode. In this mode device output data for driver 0 is skewed by two clocks from driver 1. This is useful when a two channel multiplexed ADC is used after AFE.                                                                                                                              |

|                                                    | •                |             | POWER SUPPLY                                                                                                                                                                                                                                                                                                                           |

| 53, 55, 60,<br>61, 75, 81,<br>87, 100, 106,<br>108 | VDD              | I           | Device power supply                                                                                                                                                                                                                                                                                                                    |

### **PIN FUNCTIONS (continued)**

| PI                                                                                                                               | N     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER                                                                                                                           | NAME  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                          |

| 49, 51, 52,<br>54, 59, 62,<br>65, 71, 73,<br>74, 76, 79,<br>80, 82, 85,<br>86, 90, 91,<br>99, 101, 102,<br>103, 107,<br>109, 110 | VSS   | I   | Ground for device power supply                                                                                                                                                                                                                                                       |

|                                                                                                                                  |       |     | TFT CHARGE INJECTION COMPENSATION                                                                                                                                                                                                                                                    |

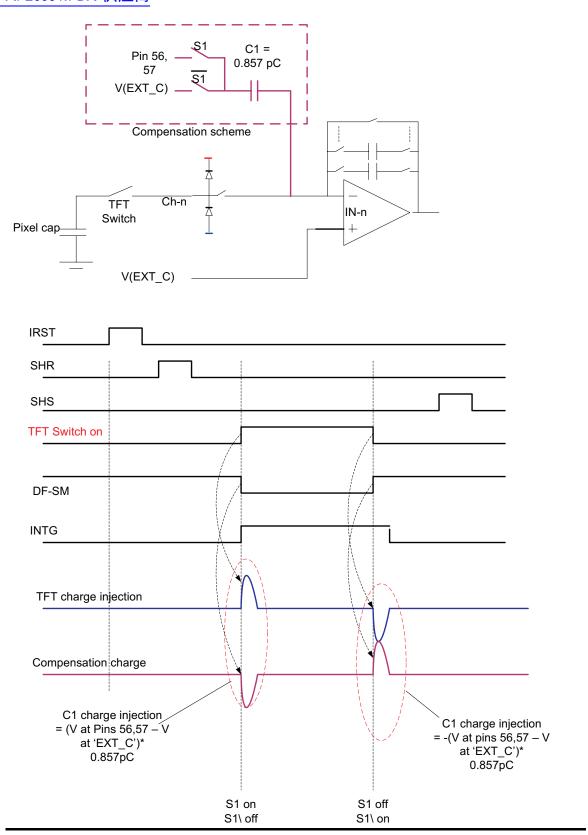

| 72                                                                                                                               | DF-SM | I   | Digital control to dump compensation charge on integrator capacitor; this is useful to nullify the effect of pixel TFT charge injection.                                                                                                                                             |

| 56                                                                                                                               | VT-A  | I   | External voltage to control the amount of charge dump for TFT charge injection compensation. Charge dump = (V-voltage at 'EXT_C')*0.857 pC where V is external voltage at pins 56, 57. Short pins 56 and 57 externally and apply external voltage for charge injection compensation. |

| 57                                                                                                                               | VT-B  | I   |                                                                                                                                                                                                                                                                                      |

|                                                                                                                                  |       |     | NC PINS                                                                                                                                                                                                                                                                              |

| 58, 111                                                                                                                          |       |     | These pins should be connected to VSS.                                                                                                                                                                                                                                               |

### **DESCRIPTIONS AND TIMING DIAGRAMS**

Figure 1. Integrator Channel Schematic

Figure 1 shows the typical schematic of an integrator channel. As shown, each integrator has a reset (IRST) switch which resets the integrator output to the 'reset-level'. The device integrates input current while this switch is open. There are two sample and hold circuits connected to each integrator output. SHR samples integrator reset level output and SHS samples integrator output post integration of signal charge. The device subtracts the SHR sample from the SHS sample. The difference is then available at device output in a differential format. This action is called 'Correlated Double Sampling' (CDS). CDS removes integrator offset and low frequency noise from device output.

Each sample and hold has a built-in low pass filter. This filter limits sampling bandwidth so as to limit sampled noise to an acceptable level. Detailed functioning of individual blocks is described further with timing diagrams.

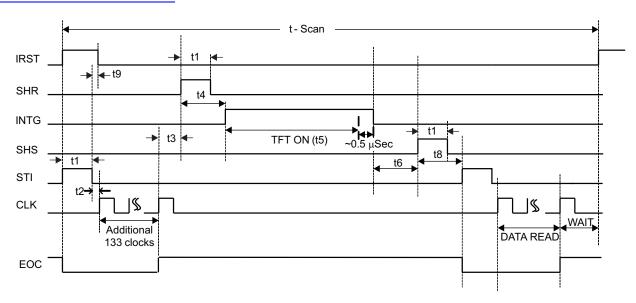

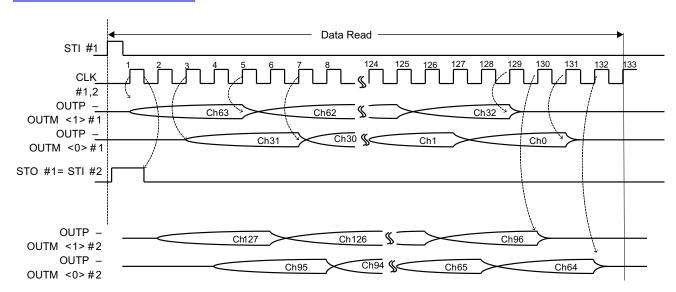

Figure 2. Integration and Data Read

As shown in Figure 2, the device performs two functions, 'Integration' and 'Data Read' during each scan (indicated by 't-Scan'). Signals IRST, SHR, SHS, INTG, CLK control 'Integration Function' and STI, CLK control 'Data Read Function'. EOC is a device output and a low level on the EOC pin indicates a data read is in progress.

### **Charge Integration**

Integration function consists of two phases namely 'Reset' and 'Integration'.

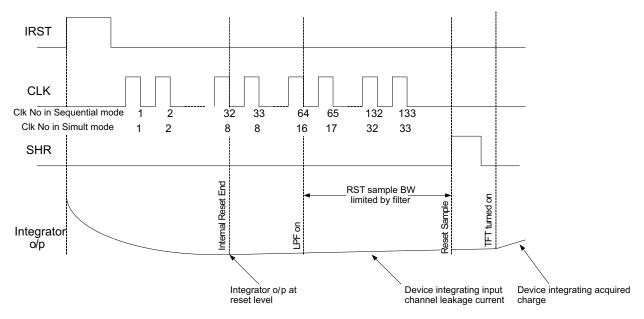

IRST rising edge starts the 'Reset' phase which ends with SHR rising edge. Figure 3 shows the detailed timing waveform for the reset phase.

Figure 3. Timing Diagram Showing Details of Reset Phase

In this phase the device resets all 64 integration capacitors. This reset-level voltage depends on the integration mode (selected by the INTUPz pin). Integrator output is reset to REFM for 'integration-up' mode and is reset to REFP in 'integration-down' mode. Note that the integrator reset switch is on from IRST rising edge to the end of the 32<sup>nd</sup> clock for sequential mode and up to the 8th clock for simultaneous mode. SHR and filter bypass switches (see Figure 1) are on right from IRST rising edge to the 64<sup>th</sup> clock falling edge.

In this period, the reset sample capacitor is tracking the integrator output voltage. On the 64th CLK falling edge, the filter bypass switch is opened. This kicks in the low pass filter. The filter has a fixed time constant of 1  $\mu$ Sec (160 kHz BW). The device samples and holds (SHR switch opens) the integrator reset output at rising edge of SHR. The low pass filter cuts off high frequency noise during sampling.

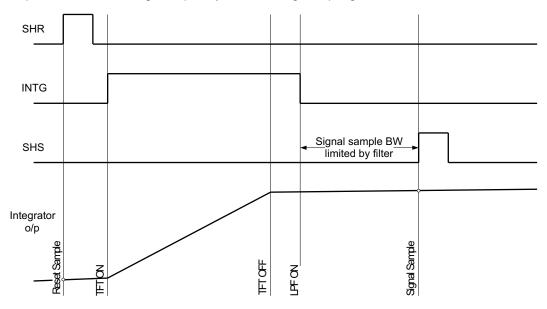

Figure 4. Timing Diagram Showing Details of Integration Phase

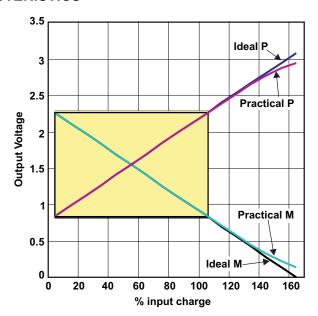

Here after the integration phase starts. The device integrates pixel charge during on time of the external TFT switch. The device integrates pixel charge starting from the reset level (as described previously).

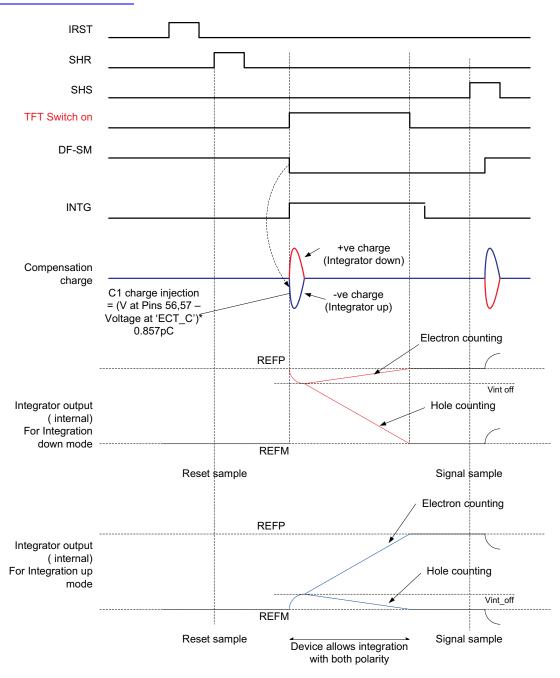

In integration up mode, the integrator output moves up from REFM (reset level). As shown in the Specifications table there are 8 different ranges for the integrator. For any range, the device can linearly integrate input charge until the integrator output reaches REFP.

In integration down mode, the integrator output moves down from REFP (reset level). For any analog input range, the device can linearly integrate input charge until the integrator output reaches REFM.