# **育前 1620/WW** 624 应商

## 16,384 x 4-Bit Static RAM

### **General Description**

The NM1620/NM1621 is a 65,536-bit fully-static, asynchronous, random access memory organized as 16,384 words by 4 bits per word. The NM1620/NM1621 is based on an advanced, isoplanar, oxide-isolation CMOS process. The process utilizes fully-implanted CMOS technology with sub-2 micron design rules and tantalum silicide gate electrodes for high performance. The combination of this high-performance technology, and speed-optimized circuitry results in a very high-speed memory device. The NM1621 is identical to the NM1620 with the additional feature of power down for low power battery backup applications.

#### Features

- Fast address access times: 25 ns/30 ns/35 ns (maximum)

- Enable read access faster than address access

- Minimum write cycle time, including moderate system timing skews, equal to minimum read cycle time

- No internal clocks—high speed achieved without address transition detection circuitry

- All inputs and outputs directly TTL compatible

- Common I/O (TRI-STATE® output)

- Available in 22-Pin DIP, PDIP or LCC

- Low power dissipation (data retention F1621).

I<sub>CCDR</sub> = 35 μA maximum (V<sub>DR</sub> = 2.0V)

- I<sub>CCDR</sub> = 50 μA maximum (V<sub>DR</sub> = 3.0V)

Data retention supply voltage NM1621:

2.0V to 5.5V

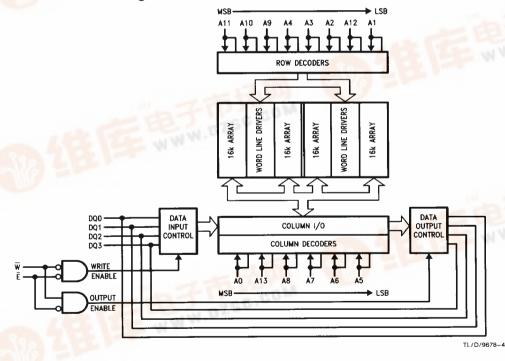

### **Functional Block Diagram**

© 1988 National Semiconductor Corporation

RRD-B20M88/Printed in U. S. A

TRI-STATE\* is a registered trademark of National Semiconductor Corporation

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

## **Recommended Operating**

#### Conditions $T_A = 0^{\circ}C \text{ to } + 70^{\circ}C$

|                          | Min        | Max            | Units |

|--------------------------|------------|----------------|-------|

| Input HIGH Voltage (VIH) | 2.2        | $V_{CC} + 0.5$ | V     |

| Input LOW Voltage (VIL)  | <b>-1*</b> | 0.8            | ٧     |

All Voltages are referenced to VSS pin = 0V.

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

<sup>\*</sup>The device will withstand undershoots to  $-3.0 \mathrm{V}$  of 20 ns duration.

| No. Symbol |                                | nbol              | DI Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | NM1620-25/255<br>NM1621-25/255 |          | NM1620-30<br>NM1621-30 |                                        | NM1620-35<br>NM1621-35 |     |

|------------|--------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|----------|------------------------|----------------------------------------|------------------------|-----|

| 杏          | Standard                       | Alternate         | B30"供应商                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min | Max                            | Min      | Max                    | Min                                    | Max                    |     |

| REA        | D CYCLE                        | <del>JDIVIQ</del> | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                                |          |                        |                                        |                        |     |

| 1          | TAVAX                          | TRC               | Address Valid to Address Invalid (Read Cycle Time)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25  |                                | 30       |                        | 35                                     |                        | ns  |

| 2          | TAVQV                          | TAA               | Address Valid to Output Valid (Address Access Time) (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 25                             |          | 30                     |                                        | 35                     | ns  |

| 3          | TAXQX                          | тон               | Address Invalid to Output Invalid (Output Hold Time)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5   |                                | 5        |                        | 5                                      |                        | ns  |

| 4          | TELEH                          | TRC               | Chip Enable LOW to Chip<br>Enable HIGH (Note 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22  |                                | 27       |                        | 30                                     |                        | ns  |

| 5          | TELQV                          | TACS              | Chip Enable LOW to Output Valid (Chip Enable Access Time) (Note 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 22                             |          | 27                     |                                        | 30                     | ns  |

| 6          | TELQX                          | TLZ               | Chip Enable LOW to Output Low Z<br>(Chip Enable to Output Active)<br>(Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5   |                                | 5        |                        | 5                                      |                        | ns  |

| 7          | TEHQZ                          | THZ               | Chip Enable HIGH to Output High Z<br>(Chip Disable to Output Disable)<br>(Note 9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | 10                             | 0        | 12                     | 0                                      | 15                     | ns  |

| 8          | TELICC                         | TPU               | Chip Enable LOW to Operating<br>Supply Current (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0   |                                | 0        |                        | 0                                      |                        | ns  |

| 9          | TEHISB                         | TPD               | Chip Enable HIGH to<br>Standby Current (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 25                             |          | 27                     |                                        | 30                     | ns  |

| A          | ccess is unde                  | we                | there is the terms of the terms | 11. | des.                           | DATA VAL | TAXQX(3                | ************************************** | TL/D/9678              | 1-7 |

| A          | ccess is unde<br>ansitions LOW | ır                | VES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |                                |          | DATA VALID TEHISB(9)   | HIGH-Z                                 | —<br>TL/D/9            |     |

| No. | Syn      | nbol      | Parameter                                                                               | NM1620-25/255<br>NM1621-25/255 |     | NM1620-30<br>NM1621-30 |     | NM1620-35<br>NM1621-35 |            | Units      |  |

|-----|----------|-----------|-----------------------------------------------------------------------------------------|--------------------------------|-----|------------------------|-----|------------------------|------------|------------|--|

|     | Standard | Alternete | MQB30"供应商                                                                               | Min                            | Max | Min                    | Max | Min                    | Max        | <u>.l.</u> |  |

| WRI | TE CYCLI | 102001    | VIGEOU IXIZED                                                                           |                                |     |                        |     |                        |            |            |  |

| 10  | TAVAX    | TWC       | Address Valid to Address Invalid (Write Cycle Time)                                     | 25                             |     | 30                     |     | 35                     | <u>.</u> . | ns         |  |

| 11  | TWLEH    | TWP       | Write LOW to Chip Enable HIGH (Write Pulse Width) (Notes 7 & 10)                        | 19                             |     | 22                     |     | 25                     |            | ns         |  |

| 12  | TAVWH    | TAW       | Address Valid to Write HIGH<br>(Address Setup to End of Write)<br>(Note 7)              | 19                             |     | 22                     |     | 25                     |            | ns         |  |

| 13  | TWHAX    | TAH       | Write HIGH to Address Don't Care<br>(Address Hold after End of Write)<br>(Notes 7 & 12) | o                              |     | 0                      |     | 0                      |            | ns         |  |

| 14  | TWLWH    | TWP       | Write LOW to Write HIGH (Write Pulse Width) (Notes 7 & 10)                              | 19                             |     | 22                     |     | 25                     |            | ns         |  |

| 15  | TAVWL    | TAS       | Address Valid to Write LOW<br>(Address Setup to Beginning of Write)<br>(Notes 7 & 8)    | 0                              |     | O                      |     | 0                      |            | ns         |  |

| 16  | TDVWH    | TDS       | Data Valid to Write HIGH<br>(Data Setup to End of Write)<br>(Notes 7 & 12)              | 10                             |     | 10                     |     | 12                     |            | ns         |  |

| 17  | TWHDX    | TDH       | Write HIGH to Data Don't Care<br>(Data Hold after End of Write)<br>(Notes 7 & 12)       | 0                              |     | 0                      |     | 0                      |            | ns         |  |

| 18  | TWLQZ    | TWZ       | Write LOW to Output High Z<br>(Write Enable to Output Disable)<br>(Note 9)              | 0                              | 9   | 0                      | 12  | 0                      | 12         | ns         |  |

| 19  | TWHQX    | TOW       | Write HIGH to Output Don't Care<br>(Output Active after End of Write)<br>(Note 4)       | 5                              |     | 5                      |     | 5                      |            | ns         |  |

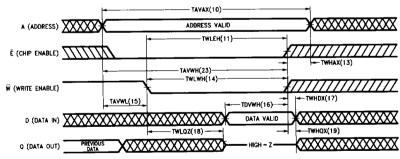

#### Write Cycle 1

TL/D/9678-9

$\overline{W}$  controlled, where  $\overline{E}$  is active (LOW) prior to  $\overline{W}$  becoming active (LOW). In this write cycle the data bus DQ may become active (Q), requiring observance of TWLQZ to avoid data bus contention. At the end of the write cycle the data bus may become active (Q) if  $\overline{W}$  becomes inactive (HIGH) prior to  $\overline{E}$  becoming inactive (HIGH).

| ļ   | AC Ele   | ctrical   | Characteristics T <sub>A</sub> = 0°C to                                                       | + 70°C, V | cc = V <sub>CCA</sub>          | MAX to V <sub>C</sub> | OMIN (Cont             | inued) |                |       |

|-----|----------|-----------|-----------------------------------------------------------------------------------------------|-----------|--------------------------------|-----------------------|------------------------|--------|----------------|-------|

| No. | Symbol   |           | Parameter                                                                                     |           | NM1620-25/255<br>NM1621-25/255 |                       | NM1620-30<br>NM1621-30 |        | 20-35<br>21-35 | Units |

| 本   | Standard | Alternate |                                                                                               | Min       | Max                            | Min                   | Max                    | Min    | Max            |       |

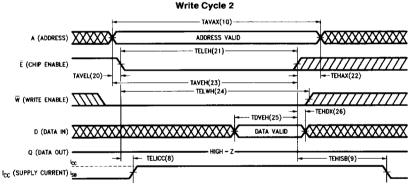

| WR  | TE CYCLI | E 2       | <del>1000                                    </del>                                           |           |                                |                       |                        |        |                |       |

| 20  | TAVEL    | TAS       | Address Valid to Chip Enable LOW (Address Setup) (Notes 7 & 8)                                | 0         |                                | 0                     |                        | 0      |                | ns    |

| 21  | TELEH    | TWP       | Chip Enable LOW to Chip Enable<br>HIGH (Write Pulse Width)<br>(Notes 7 & 10)                  | 19        |                                | 22                    |                        | 25     |                | ns    |

| 22  | TEHAX    | ТАН       | Chip Enable HIGH to Address Don't<br>Care (Address Hold after End of Write)<br>(Notes 7 & 12) | 0         |                                | 0                     |                        | 0      |                | ns    |

| 23  | TAVEH    | TAW       | Address Valid to Chip Enable HIGH (Address Setup to End of Write) (Note 7)                    | 19        |                                | 22                    |                        | 25     |                | ns    |

| 24  | TELWH    | TWP       | Chip Enable LOW to Write HIGH (Write Pulse Width) (Notes 7 & 10)                              | 19        |                                | 22                    |                        | 25     |                | ns    |

| 25  | TDVEH    | TDS       | Data Valid to Chip Enable HIGH<br>(Data Setup to End of Write)<br>(Notes 7 & 12)              | 10        |                                | 10                    |                        | 12     |                | ns    |

| 26  | TEHDX    | TDH       | Chip Enable HIGH to Data Don't<br>Care (Data Hold) (Notes 7 & 12)                             | 0         |                                | 0                     |                        | 0      |                | ns    |

TL/D/9678-10

This write cycle is  $\overline{E}$  controlled, where  $\overline{W}$  is active (LOW) prior to, or coincident with,  $\overline{E}$  becoming active (LOW). In this write cycle the data out remains in the high impedance state (3 state) at the beginning of the write cycle, precluding potential data bus contention.

| Symbol Parameter |                                  | ter    | Conditions                                                                                | NM1620-25/255<br>NM1621-25/255 |      |                      | NM1620-30<br>NM1621-30 |                      | NM1620-35<br>NM1621-35 |    |

|------------------|----------------------------------|--------|-------------------------------------------------------------------------------------------|--------------------------------|------|----------------------|------------------------|----------------------|------------------------|----|

| <b>2</b>         | i旬"1620D                         | MΩB    | 30"供应商                                                                                    | Min                            | Max  | Min                  | Max                    | Min                  | Max                    |    |

| l <sub>Ll</sub>  | input Leakage<br>Current (Except |        | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                       |                                | ±2   |                      | ±2                     |                      | ± 2                    | μА |

| lo               | Output Leakage<br>Current (DQ)   | 9      | $\overline{E} = V_{IH} \text{ or } \overline{W} = V_{IL}$ $V_{SS} \le V_{OUT} \le V_{CC}$ |                                | ± 10 |                      | ± 10                   |                      | ±10                    | μА |

| Icc              | Dynamic Opera<br>Supply Current  | iting  | Min Read Cycle Time<br>Duty Cycle = 100%<br>Output Open                                   |                                | 120  |                      | 100                    |                      | 90                     | mA |

| I <sub>SB1</sub> | Standby Supply<br>Current        | i      | Ē = V <sub>IH</sub> , (Note 1)                                                            |                                | 25   |                      | 25                     |                      | 25                     | mA |

| I <sub>SB2</sub> | Full Standby                     | NM1620 |                                                                                           |                                | 15   |                      | 15                     |                      | 15                     | mA |

|                  | Supply Current                   | NM1621 |                                                                                           |                                | 5    |                      | 5                      |                      | 5                      |    |

| V <sub>OL</sub>  | Output LOW Vo                    | oltage | I <sub>OL</sub> = 8.0 mA<br>All Outputs Under Load                                        |                                | 0.4  |                      | 0.4                    |                      | 0.4                    | V  |

| V <sub>OH1</sub> | Output HIGH V                    | oltage | $I_{OH1} = -4.0 \text{ mA}$ All Outputs Under Load                                        | 2.4                            |      | 2.4                  |                        | 2.4                  |                        | v  |

| V <sub>OH2</sub> | Output HIGH V                    | oltage | $I_{OH2} = -0.05 \text{mA}$                                                               | V <sub>CC</sub> -0.4           |      | V <sub>CC</sub> -0.4 |                        | V <sub>CC</sub> -0.4 |                        | V  |

| V <sub>CC</sub>  | Supply Voltage                   |        | Except Data                                                                               | -1                             | 25   |                      |                        |                      |                        |    |

|                  |                                  |        | Retention Mode                                                                            | 4.50                           | 5.5  | 4.5                  | 5.5                    | 4.5                  | 5.5                    | V  |

|                  |                                  |        |                                                                                           | -2                             | 55   |                      |                        |                      |                        |    |

|                  |                                  |        |                                                                                           | 4.75                           | 5.5  |                      |                        |                      |                        |    |

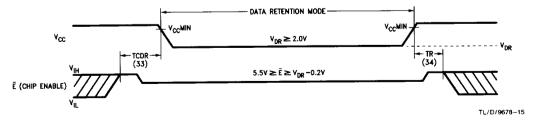

| Data Retention | Characteristics (NM1625 only) T <sub>C</sub> = 0°C to +70°C, V <sub>C</sub> | $c_0 = 2.0 \text{V to } 5.5 \text{V}$ |

|----------------|-----------------------------------------------------------------------------|---------------------------------------|

| Data Retention |                                                                             | $_{\rm CC} = 2.04 \times 0.04$        |

| No. | Symbol          | Parameter                                               | C                                                                                                                  | Min                      | Max   | Units |    |

|-----|-----------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------|-------|-------|----|

| 31  | V <sub>DR</sub> | V <sub>CC</sub> Voltage for Data<br>Retention (Note 15) | $\begin{aligned} V_{CC} - 0.2V &\leq \overline{E} \\ V_{CC} - 0.2V &\leq V \\ V_{SS} - 0.2V &\leq V \end{aligned}$ | 2.0                      | 5.5   | ٧     |    |

| 32  | ICCDR           | Data Retention Current                                  | $V_{DR} = 2.0V$                                                                                                    | $T_A = 0$ °C to $+70$ °C |       | 35    | μА |

|     |                 | (Note 14)                                               | $V_{DR} = 3.0V$                                                                                                    | $T_A = 0$ °C to $+70$ °C |       | 50    | ·  |

| 33  | TCDR            | Chip Disable to Data<br>Retention Time (Note 4)         |                                                                                                                    |                          | 0     |       | ns |

| 30  | TR              | Recovery Time<br>(Notes 4 & 13)                         |                                                                                                                    |                          | TAVAX |       | ns |

## **Data Retention Waveform**

Note 1: Standby supply current (TTL) is measured with E HIGH (chip deselected) and inputs steady state at valid VIL or VIH levels.

Note 2: Full standby supply current (CMOS) is measured with the enable bar input satisfying the condition: VCC -0.2V ≤ E ≤ VCC +0.2V, and all other inputs, (including the data inputs) at steady state and satisfying one of two conditions: Either, VCC -0.2V ≤ VIN ≤ VCC +0.2V or Vss -0.2V ≤ VIN ≤ Vss +0.2V. This condition results in a significant reduction in current in the input buffers and consequently a lower overall current level.

Note 3: Operation to specifications guaranteed 2.0 ms after V<sub>CC</sub> reaches minimum operating voltage.

Note 5: Address Access Time (Plead Gyole 14 assumes that E occurs before, or within 5 ns after addresses are valid. Timing considerations are referenced to the edges of Address Valid.

Note 6: Enable Access Time (Read Cycle 2) assumes that addresses are valid at least 5 ns prior to E transitioning LOW (active). Timing considerations are then referenced to the LOW (active) transitioning edge of E.

Note 7: A write condition exists only during intervals where both  $\overline{W}$  and  $\overline{E}$  are LOW (active). The internal Write starts when the second of these signals becomes LOW (active). The internal Write ends when either of these signals transitions HIGH (inactive).

Note 8: Address setup to beginning of write is measured from the time when the last address input becomes valid to the time when the second of the two signals (E or  $\overline{W}$ ) becomes LOW (active). The timing of the first signal ( $\overline{W}$  or  $\overline{E}$ ) to transition LOW (active) is a Don't Care.

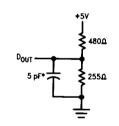

Note 9: Transition to the high-impedance state is measured at a ± 500 mV change from a valid V<sub>OH</sub> of V<sub>OL</sub> steady state voltage with the loading specified in Figure 2. This parameter is sampled, not 100% tested.

Note 10: Write pulse width is measured from the time when the last of the two signals E and W becomes LOW (active) to the time of the first of E or W to transition HIGH (inactive)

Note 11: For rise or fall times greater than 3 ns, the timing relationships can no longer be specified to the time when inputs cross the 1.5V level. This is a characteristic of any CMOS device operated outside specified switching levels or transition times.

Note 12: Timing specifications of Data Setup to End of Write, Data Hold After End of Write, and Address Hold After End of Write are all referenced to the time when the first of  $\overline{\mathbb{E}}$  or  $\overline{\mathbb{W}}$  transitions HIGH (inactive). The timing of the second signal ( $\overline{\mathbb{W}}$  or  $\overline{\mathbb{E}}$ ) to transition HIGH (inactive) is a Don't Care.

Note 13: TAVAX = Bead Cycle Timing.

Note 14:  $I_{CCDR}$  is tested with  $V_{IN} = 0V$  and  $V_{IN} = V_{DR}$ .

Note 15:  $V_{1N}$  applies to all inputs other than  $\overline{E}$  and  $DQ_0-DQ_3$ . Input conditions for  $DQ_0-DQ_3$  are  $V_{SS}=0.2V \le DQ \le V_{SS}+0.2V$  or  $V_{CC}=0.2V \le DQ \le DQ$ V<sub>CC</sub> + 0.2V.

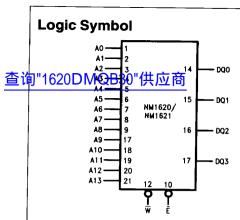

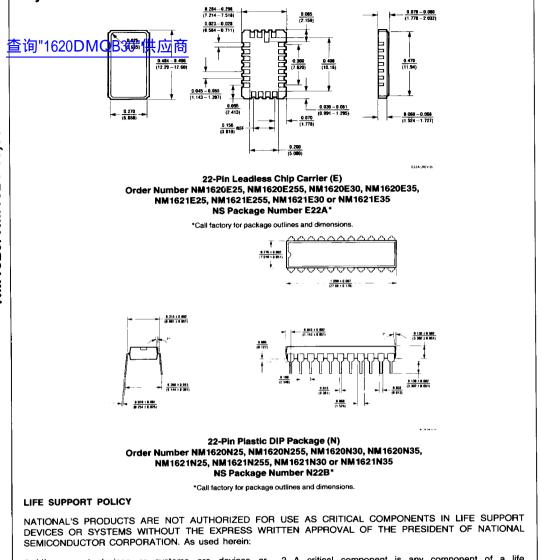

### **Connection Diagrams**

**Top View**

Order Number NM1620J25, NM1620J255, NM1620J30, NM1620J35, NM1620N25, NM1620N255, NM1620N30, NM1620N35, NM1621J25, NM1621J255, NM1621J30, NM1621J35, NM1621N25, NM 1621N255. NM 1621N30 or NM 1621N35

See NS Package Number D22D\* or N22B\*

TL/D/9678-2

Order Number. NM1620E25, NM1620E255, NM1620E30,

NM1620E35, NM1621E25, NM1621E255, NM1621E30 or NM1621E35

**Top View**

See NS Package Number E22A\*

\*Call factory for current package outlines and dimensions.

| Pin Names                        |                     |  |  |  |  |

|----------------------------------|---------------------|--|--|--|--|

| A <sub>0</sub> -A <sub>13</sub>  | Address Inputs      |  |  |  |  |

| Ē                                | Chip Enable Bar     |  |  |  |  |

| w                                | Write Enable Bar    |  |  |  |  |

| DQ <sub>O</sub> -DQ <sub>3</sub> | Data Inputs/Outputs |  |  |  |  |

| V <sub>CC</sub>                  | Power (+5.0V)       |  |  |  |  |

| V <sub>SS</sub>                  | Ground (0V)         |  |  |  |  |

|                                  |                     |  |  |  |  |

TL/D/9678-3

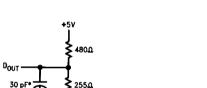

## AC Test Conditions (Notes 3 & 11)

Input Pulse Levels 0V to 3.0V Input Rise and Fall Times 3 ns

Input and Output Timing Reference Levels 1.5V **Output Load** (See Figures 1 and 2)

### Capacitance (Note 4)

| Symbol           | Parameter          | Max | Units |

|------------------|--------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance  | 6   | pF    |

| C <sub>OUT</sub> | Output Capacitance | 7   | pF    |

Effective capacitance calculated from the equation.

$$C = \frac{\Delta Q}{\Delta V} \text{ where } \Delta V = 3V$$

TL/D/9678-5

FIGURE 1. Output Load

## **Truth Table**

| Mode    | Ē | w | DQX    | Power Level |

|---------|---|---|--------|-------------|

| Standby | н | Х | HIGH Z | Standby     |

| Read    | L | Н | Q      | Active      |

| Write   | L | L | D      | Active      |

HIGH Z = High impedance

D = Valid data in X = Don't care

Q = Valid data out

FIGURE 2. Output Load (for TEHQZ, TELQX, TWLQZ, TWHQX)

TL/D/9678-6

\*including scope and jig.

####

TL/D/9678-11

The transition definitions used in this data sheet are:

I = transition to high state.

= transition to low state.

V = transition to valid state.

X = transition to invalid or don't care condition.

Z = transition to off (high impedance) condition.

#### TIMING VALUES

The AC Operating Conditions and Characteristics tables typically show either a minimum or maximum limit for each device parameter. Those timing parameters which state a minimum value do so because the system must supply at least that much time, even though most devices don't require that full amount. Thus, input requirements are specified from the external point of view. In contrast, responses from the memory (like access times) are specified as a maximum time because the device will never provide the data later than this stated value, and will usually provide it much sooner than this.

any time during this period.

TL/D/9678-13

INVALID or Don't Care.

Transition from HIGH to LOW level, may occur any time during this period.

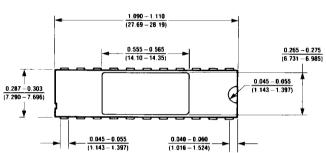

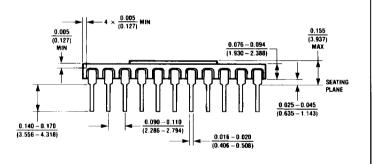

## Physical Dimensions inches (millimeters)

D22D (REV 0)

22-Pin Side-Brazed Package (J)

Order Number NM1620J25, NM1620J255, NM1620J30, NM1620J35,

NM1621J25, NM1621J250 or NM1621J35

NS Package Number D22D\*

\*Call factory for package outlines and dimensions.

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

Physical Dimensions inches (millimeters) (Continued)

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: (408) 721-5000 TWX: (910) 339-9240 National Semiconductor GmbH Westendstrasse 193-195 D-8000 Munchen 21 West Germany Tel: (089) 5 70 95 01 Telex: 522772 NS Japan Ltd. Sanseido Bldg. 5F 4-15 Nishi Shinjuku Shinjuku-Ku, Tokyo 160, Japan Tel: 3-299-7001 FAX: 3-299-7000 National Semiconductor Hong Kong Ltd. Southeast Asia Marketing Austin Tower, 4th Floor 22-26A Austin Avenue Tsimshatsui, Kowloon, H.K. Tel: 3-7231290, 3-7243645

Do Brasil Ltda. Av. Brig. Faria Lima, 830 8 Andar 01452 Sao Paulo, SP. Brasil Tet: (55/11) 212-5066 Telex: 391-1131931 NSBR BR National Semiconductor (Australia) PTY, Ltd. 21/3 High Street Bayswater, Victoria 3153 Australia Tel: (03) 729-6333 Telex: AA32096

Lit. # 112228

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications