# Serial Input 12-Bit DAC

<del>查询"AD7543AQ/+"供应商</del>

AD7543

### 1.1 Scope.

This specification covers the detail requirements for a monolithic CMOS 12-bit multiplying digital-to-analog converter designed for serial interface applications.

### 1.2 Part Number.

The complete part number per Table 1 of this specification is as follows:

| Device | Part Number <sup>1</sup> |

|--------|--------------------------|

| -1     | AD7543S(X)/883B          |

| -2     | AD7543T(X)/883B          |

| -3     | AD7543GT(X)/883B         |

### NOTE

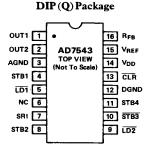

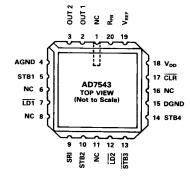

### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline:

| <b>(X)</b> | Package | Description    |

|------------|---------|----------------|

| Q          | Q-16    | 16-Pin Cerdip  |

| E          | E-20A   | 20-Contact LCC |

# 1.3 Absolute Maximum Ratings. (TA = 25°C unless otherwise noted. Pin numbers refer to DIP package.)

| V <sub>DD</sub> to AGND                       |

|-----------------------------------------------|

| V <sub>DD</sub> to DGND                       |

| AGND to DGND                                  |

| DGND to AGND                                  |

| Digital Input Voltage to DGND (Pins 4-11, 13) |

| $V_{PIN1}, V_{PIN2}$ to AGND                  |

| V <sub>REF</sub> to AGND                      |

| V <sub>RFB</sub> to AGND                      |

| Power Dissipation                             |

| Up to +75°C                                   |

| Derates above +75°C                           |

| Operating Temperature Range                   |

| Storage Temperature Range                     |

| Lead Temperature (Soldering 10sec)            |

### 1.5 Thermal Characteristics.

```

Thermal Resistance \theta_{JC}=35^{\circ}C/W for Q-16 and E-20A \theta_{JA}=120^{\circ}C/W for Q-16 and E-20A

```

REV. C

<sup>&</sup>lt;sup>1</sup>See paragraph 1.2.3 for package identifier.

# AD7543—SPECIFICATIONS

Table 1.

| 本治"A D7540 A                                        | 0/."/              | # 🕁 🗷     | Design<br>Limit                     | Sub<br>Group | Sub<br>Group                                     | Sub<br>Group |                                                                                                                                                        |               |

|-----------------------------------------------------|--------------------|-----------|-------------------------------------|--------------|--------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| <u>Test</u> 查询"AD7543A                              |                    |           | T <sub>min</sub> , T <sub>max</sub> | 1            | 2,3                                              | 4            | Test Condition <sup>1</sup>                                                                                                                            | Units         |

| Resolution                                          | RES                | -1,2,3    | 12                                  |              |                                                  |              |                                                                                                                                                        | Bits          |

| Relative Accuracy                                   | RA                 | - 1       | 1                                   | 1            | 1                                                |              |                                                                                                                                                        | ± LSB max     |

|                                                     |                    | -2,3      | 1/2                                 | 1            | 1/2                                              | 1/2          |                                                                                                                                                        |               |

| Differential Nonlinearity                           | DNL                | -1        | 2                                   | 2            | 2                                                |              | Monotonic to 11 Bit<br>from T <sub>min</sub> to T <sub>max</sub>                                                                                       | ± LSB max     |

|                                                     |                    | - 2, 3    | 1                                   | 2            | 1                                                | 1            | Monotonic to 12 Bit<br>from T <sub>min</sub> to T <sub>max</sub>                                                                                       |               |

| Gain Error <sup>2</sup>                             | AE                 | -1,2      | 14.5                                | 12.3         | 14.5                                             |              |                                                                                                                                                        | ± LSB max     |

|                                                     |                    | <b>-3</b> | 2                                   | 12.3         | 2                                                | 1            |                                                                                                                                                        |               |

| Gain Tempco                                         | TCAE               | -1,2,3    | 5                                   |              |                                                  |              |                                                                                                                                                        | ± ppm/°C max  |

| Supply Rejection ( $\Delta Gain/\Delta V_{DD}$ )    | PSRR               | -1,2,3    | 0.01                                | 0.005        | 0.01                                             |              | $\Delta V_{DD} = \pm 5\%$                                                                                                                              | ± % per % max |

| Output Leakage Current<br>I <sub>OUT1</sub> (Pin 4) | louri              | -1,2,3    | 200                                 | ± 10         | 200                                              |              | DAC Registers Loads with All 0's                                                                                                                       | ± nA max      |

| I <sub>OUT2</sub> (Pin 5)                           | I <sub>OUT2</sub>  | -1,2,3    | 200                                 | ± 10         | 200                                              |              | DAC Register Loads with All 1's                                                                                                                        |               |

| Output Current Settling Time                        | t <sub>St</sub> .  | -1,2,3    | 2                                   |              |                                                  |              | To $\pm$ 1/2LSB $R_{OUT}$ 1 = 100 $\Omega$ ,<br>$C_{OUT1}$ = 13pF DAC. Output Measured from Falling Edge of $\overline{LD1}$<br>and $\overline{LD2}$ . | μs max        |

| Feedthrough Error <sup>3</sup>                      | FTE                | -1,2,3    | 2.5                                 |              |                                                  |              | V <sub>REF</sub> = 10V, 10kHz Sinewave                                                                                                                 | mV p-p max    |

| Reference Input Resistance (Pin 15)                 | R <sub>IN</sub>    | -1,2,3    | 8                                   | 8            | 8                                                |              |                                                                                                                                                        | kΩ min        |

|                                                     |                    |           | 25                                  | 25           | 25                                               |              |                                                                                                                                                        | kΩ max        |

| Digital Input High Voltage                          | V <sub>IH</sub>    | -1,2,3    | 3.0                                 | 3.0          | 3.0                                              |              |                                                                                                                                                        | V min         |

| Digital Input Low Voltage                           | V <sub>II</sub> .  | -1,2,3    | 0.8                                 | 0.8          | 0.8                                              |              |                                                                                                                                                        | V max         |

| Digital Input Leakage Current                       | I <sub>IN</sub>    | -1,2,3    | 1                                   | 1            | ı                                                |              | $V_{IN} = 0V \text{ or } V_{DD}$                                                                                                                       | ± μA max      |

| Digital Input Capacitance                           | Cin                | -1,2,3    | 8                                   | 1            |                                                  |              |                                                                                                                                                        | pF max        |

| Output Capacitance<br>C <sub>OUT1</sub> (Pin 1)     | C <sub>OUT</sub>   | -1,2,3    | 260                                 |              |                                                  |              | Digital Inputs = V <sub>IH</sub> . DAC Register<br>Loaded with 1111 1111 1111                                                                          | pF max        |

| C <sub>OUT2</sub> (Pin 2)                           | C <sub>OUT2</sub>  | -1,2,3    | 75                                  |              |                                                  |              | Digital Inputs = V <sub>IH</sub> . DAC Register<br>Loaded with 1111 1111 1111                                                                          | pF max        |

| C <sub>OUT1</sub> (Pin 1)                           | C <sub>OUT</sub> 1 | -1,2,3    | 75                                  |              |                                                  |              | Digital Inputs = V <sub>IL</sub> . DAC Register Loaded with 0000 0000 0000                                                                             | pF max        |

| C <sub>OUT2</sub> (Pin 2)                           | C <sub>OUT2</sub>  | -1,2,3    | 260                                 |              |                                                  |              | Digital Inputs = V <sub>II.</sub> . DAC Register<br>Loaded with 0000 0000 0000                                                                         | pF max        |

| Serial Input to Strobe                              | t <sub>DS1</sub>   | -1,2,3    | 100                                 | T            |                                                  |              | STB1 Used as a Strobe                                                                                                                                  | ns min        |

| Setup Time <sup>4</sup>                             | t <sub>DS4</sub>   | -1,2,3    | 0                                   | <u> </u>     |                                                  |              | STB4 Used as a Strobe                                                                                                                                  |               |

|                                                     | t <sub>DS3</sub>   | -1,2,3    | 0                                   |              |                                                  |              | STB3 Used as a Strobe                                                                                                                                  |               |

|                                                     | t <sub>DS2</sub>   | -1,2,3    | 40                                  |              |                                                  |              | STB2 Used as a Strobe                                                                                                                                  |               |

| Serial Input to Strobe                              | toni               | -1,2,3    | 70                                  | 1            |                                                  |              | STB1 Used as a Strobe                                                                                                                                  | ns min        |

| Hold Time <sup>4</sup>                              | t <sub>DH4</sub>   | -1,2,3    | 250                                 | <u> </u>     |                                                  |              | STB4 Used as a Strobe                                                                                                                                  | I             |

|                                                     | t <sub>DH3</sub>   | -1,2,3    |                                     | 1            |                                                  |              | STB3 Used as a Strobe                                                                                                                                  |               |

|                                                     | t <sub>DH2</sub>   | -1,2,3    | +                                   |              |                                                  | †            | STB2 Used as a Strobe                                                                                                                                  | ĺ             |

|                                                     | t <sub>SR1</sub>   | -1,2,3    |                                     | <del></del>  | $\vdash$                                         |              | SR1 Data Pulse Width                                                                                                                                   | ]             |

|                                                     | t <sub>STB1</sub>  | -1,2,3    |                                     | † -          | <del>                                     </del> | 1            | STB1 Pulse Width4                                                                                                                                      | ]             |

|                                                     | t <sub>STB4</sub>  | -1,2,3    | 1                                   | t            | t                                                | 1            | STB4 Pulse Width <sup>4</sup>                                                                                                                          | 1             |

|                                                     | t <sub>STB3</sub>  | -1,2,3    |                                     | 1 -          | 1                                                |              | STB3 Pulse Width4                                                                                                                                      | [             |

|                                                     | t <sub>STB2</sub>  | -1,2,3    | +                                   | + -          | <del>                                     </del> | 1            | STB2 Pulse Width <sup>4</sup>                                                                                                                          | 1             |

|                                                     | t <sub>LD1</sub> , | -1,2,3    | <del></del>                         |              |                                                  |              | Min Time Between Strobing LSB into<br>Register A and Loading Register B <sup>4</sup>                                                                   |               |

|                                                     | t <sub>ASB</sub>   | -1,2,3    | 80                                  |              |                                                  | <u> </u>     | Min Time Between Strobing LSB into<br>Register A and Loading Register B <sup>4</sup>                                                                   | 1             |

|                                                     | 1                  | I         |                                     |              | <del></del>                                      | <b></b>      | CLK Pulse Width <sup>4</sup>                                                                                                                           | 1             |

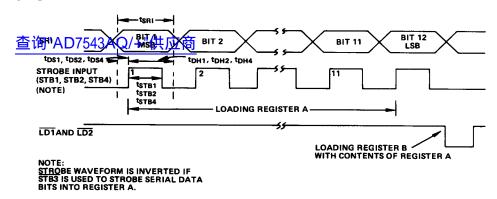

NOTES  $^{1}V_{DD} = +5V; V_{OUT1} = V_{OUT2} = 0V, V_{REF} = +10V$  unless otherwise stated.  $^{2}Messured$  using internal feedback resistor and includes the effect of 5ppm max gain TC.  $^{2}Teedthrough can be further reduced by connecting the metal lid to ground. <math>^{4}Timing$  per Figure 1.

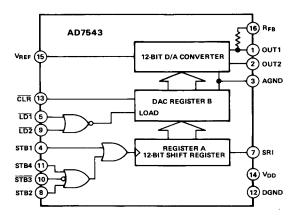

# 3.2.1 Functional Block Diagram and Terminal Assignments.

# 查询"AD7543AQ/+"供应商

LCC(E) Package

# 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (80).

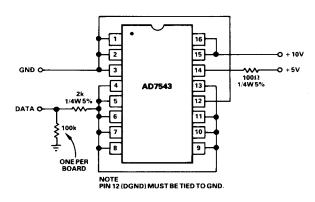

# 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).

REV. C

DIGITAL-TO-ANALOG CONVERTERS 8-147

Figure 1. Timing Diagram

Table 2. Truth Table

| AD7543 Logic Inputs                                 |      |          |              |          |         | 2 12.     |                                                             |          |  |  |  |  |

|-----------------------------------------------------|------|----------|--------------|----------|---------|-----------|-------------------------------------------------------------|----------|--|--|--|--|

| Register A Control Inputs Register B Control Inputs |      |          |              | Register | B Contr | ol Inputs | AD7543 Operation                                            | Notes    |  |  |  |  |

| STB4                                                | STB3 | STB2     | STB1         | CLR      | LD2     | LD1       | 1                                                           |          |  |  |  |  |

| 0                                                   | 1    | 0        | _ <b>_</b> _ | х        | х       | х         | Data Appearing At SRI Strobed Into Register A               | 2,3      |  |  |  |  |

| 0                                                   | 1    | <b>.</b> | 0            | х        | х       | х         | Data Appearing At SRI Strobed Into Register A               | 2,3      |  |  |  |  |

| 0                                                   | TL.  | 0        | 0            | х        | х       | х         | Data Appearing At SRI Strobed Into Register A               | 2,3      |  |  |  |  |

| <u>_</u>                                            | 1    | 0        | 0            | х        | х       | х         | Data Appearing At SRI Strobed Into Register A               | 2,3      |  |  |  |  |

| 1                                                   | x    | х        | х            |          |         |           |                                                             |          |  |  |  |  |

| X                                                   | 0    | x        | х            |          |         |           |                                                             | l        |  |  |  |  |

| х                                                   | х    | 1        | х            |          |         |           | No Operation (Register A)                                   |          |  |  |  |  |

| Х                                                   | х    | х        | 1            |          |         |           |                                                             |          |  |  |  |  |

|                                                     |      |          |              | 0        | х       | х         | Clear Register B To Code 0000 0000 (Asynchronous Operation) | 1,3      |  |  |  |  |

|                                                     |      |          |              | 1        | 1       | х         | No Operation (Register B)                                   | <u> </u> |  |  |  |  |

|                                                     |      |          |              | 1        | х       | 1         |                                                             | 3        |  |  |  |  |

|                                                     | •    |          |              | 1        | 0       | 0         | Load Register B With The Contents Of Register A             | 3        |  |  |  |  |

#### NOTES:

1. CLR = 0 Asynchronously resets Register B to 0000 0000 0000, but has no effect on Register A.

2. Serial data is loaded into Register A MSB first, on edges shown is positive edge. It is negative edge.

3. 0 = Logic LOW, 1 = Logic HIGH, X = Don't Care.