DATASHEET

Jitter Attenuating, Multiplying Phase Locked Loop, with Protection Switch, for OC-12/STM-4 and GbE

#### 查询"ACS8946T"供应商 ADVANCED COMMUNICATIONS

#### Introduction

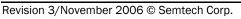

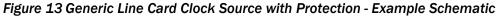

The ACS8946 JAM PLL is a Jitter-Attenuating, Multiplying differential Phase-Locked Loop, for generating low jitter output clocks compliant up to SONET OC-12 and STM-4 622.08 MHz specifications. Its primary function is to clean up clock jitter for high performance optical line cards with OC-12 framers and serializers. It also provides reference switching functionality for line card protection, and frequency translation.

SEMTECH

Typical output jitter generation is within OC-12/STM-4 specifications, at 2.8 ps rms, making it an ideal dejittering solution for use with Semtech clock and line card parts: ACS8510, ACS8520, ACS8522 and ACS8530. The ACS8946 can also be used as a basic line card protection device in some applications.

The ACS8946 JAM PLL has two differential, frequency programmable, LVPECL reference inputs and one differential sync input. It has four outputs, programmable as LVPECL or CML, and frequency programmable to any common SONET/SDH rate i.e. 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz and 622.08 MHz. Jitter cleaning of Gigabit Ethernet (GbE) 125 MHz and 156.25 MHz is also possible, with output frequency multiplication up to 625.00 MHz available.

The device's operating bandwidth (and consequently the jitter attenuation point relating to this bandwidth) is fully configurable, and is set by external passive components.

Note...For items marked <sup>[1],[2], etc.</sup> references are given in full in the Reference Section on page 38.

Block Diagram

df.dzsc.com

### **Features**

FINAL

- Meets rms jitter requirements of:

- Telcordia GR-253<sup>[8]</sup> for OC-3 and OC-12

- ITU-T G.813<sup>[4]</sup>/G.812<sup>[3]</sup> for STM-1 and STM-4 rates

- ETSI EN300-462-7<sup>[1]</sup>/EN302-084<sup>[2]</sup> up to STM-16 rates

- PLL bandwidth and jitter peaking fully adjustablesupports PLL loop bandwidths from 2 kHz for superior input jitter filtering

- Typical jitter generation down to:

- 0.3 ps rms for 250 kHz to 5 MHz band for G.813, or EN300 462, at STM-4 (OC-12) rates

- 2.8 ps rms for 12 kHz to 20 MHz band (against) 4.02 ps rms for GR-253-CORE at OC-48 rate)

- ITU, ETSI and Telcordia frequency band results shows exceptional performance in a "Real World" environment (low PLL bandwidth of 2 KHz and a typical input from an ACS8525 partner IC):

- 0.4 ps rms for 250 kHz to 5 MHz band for G.813, or EN300 462, at STM-4 (OC-12) rates

- 2.8 ps rms for 12 kHz to 20 MHz band

- Tracking range ±400 ppm about a wide range of input frequencies

- Manual or automatic control of reference selection

- External feedback option

- LOS alarms for each input, and for selected reference

- 3.3 V operation, 40 to +85°C temperature range

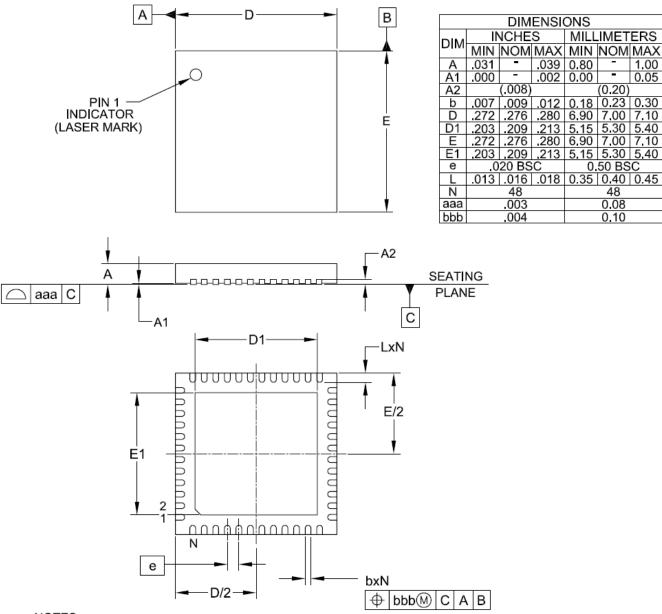

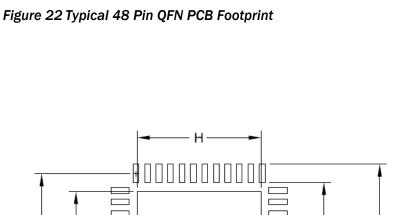

- Small outline leadless 7 mm x 7 mm OFN48 package

- Lead (Pb)-free version available (ACS8946T),  $RoHS^{[11]}$  and  $WEEE^{[12]}$  compliant

#### Loop RESETR Filte VC 1 x CMOS 1 x LVPECL Single-ended Sync Output **Differential Sync Input Re-timing** SYNC SYNC OUT 4 x LVPECL or CML 2 x LVPECL Output Clocks Input Differential CLK1 Independently Input References Selector CLK2 Frequency Programmable PFD Programmable: 2.5 GHz OUT[4:1] from: 625.00 MHz Dividers 19 44 MHz to Charge Divider 156.25 MHz VCO Pump 622.08 MHz Clock 311.04 MHz Drivers 155.52 MHz **Device Configuration Select** 77.76 MHz CFG\_IN[7:0] -**Control and Monitor** 38.88 MHz CFG\_OUT2 19.44 MHz Note: LOS alarm outputs are also used for device config. select 125 MHz 156.25 MHz Clock Input Configuration for-Lock Alarm (LOCKB) Frequency Select Others Ethernet rates • Manual selection • Auto Ref selection LOS Alarms for: (RATE[2:1]A, RATE[2:1]B) - CLK1 (ALARM1\_CO0) - CLK2 (ALARM2\_CO1) - Currently selected reference (ALARMC\_CO3) available using divider External feedback mode (SEL CLK2, AUTO SEL) F8946D\_004Bl PDF evision 3/November 2006 © Semtech Corp.

#### Figure 1 Simplified Block Diagram of the ACS8946 JAM PLL

DATASHEET

**ADVANCED COMMUNICATIONS**

**FINAL**

Page

|     | -  | -  | -            |     |     |

|-----|----|----|--------------|-----|-----|

| Tat |    | of | $\mathbf{C}$ | nto | nta |

| Tar | ле | U  | CO           | ne  |     |

Section

| Introduction                                                                           |   |

|----------------------------------------------------------------------------------------|---|

| Block Diagram                                                                          |   |

| Features                                                                               |   |

| Table of Contents                                                                      |   |

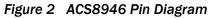

| Pin Diagram                                                                            |   |

| Pin Description                                                                        |   |

| Description                                                                            |   |

| Inputs                                                                                 | 8 |

| Outputs                                                                                | 8 |

| Clock Multiplication                                                                   | 9 |

| Voltage Controlled Oscillator                                                          | 9 |

| Jitter Filtering                                                                       |   |

| Jitter Filtering: Partnering with Semtech Line Card Protection Parts                   |   |

| Input Jitter Tolerance                                                                 |   |

| Jitter Transfer                                                                        |   |

| Phase Noise Performance                                                                |   |

| Lock Detector                                                                          |   |

| PLL Bandwidth Setting                                                                  |   |

| RC Components Required to Achieve Bandwidth at Given Input Frequencies (Tables 6 to 9) |   |

| Source Switching - State Diagram                                                       |   |

| Configuration                                                                          |   |

| Output Configuration                                                                   |   |

| Example Configuration                                                                  |   |

| Output Jitter                                                                          |   |

| System Reset                                                                           |   |

| Layout Recommendations                                                                 |   |

| Applications                                                                           |   |

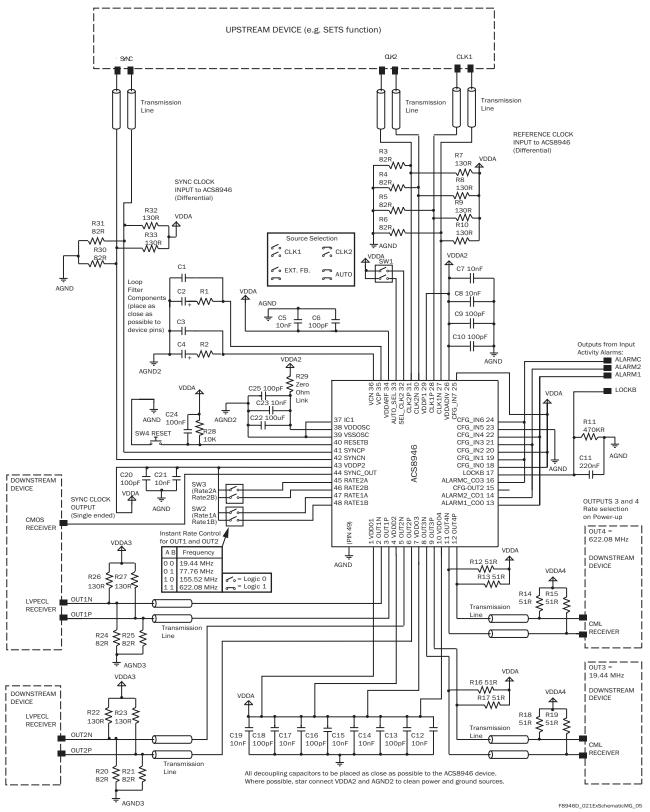

| Example Schematic                                                                      |   |

| Electrical Specifications                                                              |   |

| Maximum Ratings                                                                        |   |

| Operating Conditions                                                                   |   |

| Thermal Characteristics                                                                |   |

| AC Characteristics                                                                     |   |

| DC Characteristics                                                                     |   |

| Input and Output Interface Terminations                                                |   |

| Jitter Performance                                                                     |   |

| Input/Output Timing                                                                    |   |

| Package Information                                                                    |   |

| Thermal Conditions                                                                     |   |

| References and Related Standards                                                       |   |

| Abbreviations<br>Revision Status/History                                               |   |

|                                                                                        |   |

| Trademark Acknowledgements Notes                                                       |   |

| Ordering Information                                                                   |   |

| Disclaimers                                                                            |   |

| Contacts                                                                               |   |

| 00110013                                                                               |   |

FINAL

# ACS8946 JAM PLL

DATASHEET

Pin Diagram

### **Pin Description**

#### Table 1 Power Pins

| Pin No.        | Symbol                        | I/0 | Туре | Description                                                                                                                                                                                                      |  |

|----------------|-------------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 4,<br>7, 10 | VDD01, VDD02,<br>VDD03, VDD04 | Ρ   | -    | Supply Voltage: Independent supplies to power each clock output (differential pair of pins) OUT1N/P to OUT4N/P respectively. +3.3 Volts $\pm$ 5%. To disable an output and save power, tie associated VDD to OV. |  |

| 26             | VDDADIV                       | Р   | -    | Supply Voltage: Supply for internal Dividers in VCO loop, kept as an isolated supply to allow for low supply noise for the output divider stages. +3.3 Volts $\pm$ 5%.                                           |  |

| 29             | VDDP1                         | Р   | -    | Supply Voltage: Supply to differential inputs, alarm and config. pins. +3.3 Volts ±5%.                                                                                                                           |  |

| 43             | VDDP2                         | Р   | -    | Supply Voltage: Supply to Sync input and Sync output pins, rate selection pins, input selection pins and reset pin. +3.3 Volts ±5%.                                                                              |  |

| 34             | VDDARF                        | Р   | -    | Supply Voltage: Supply for phase and frequency detector (PFD), kept as an isolated supply to allow for low supply noise. +3.3 Volts $\pm 5\%$ .                                                                  |  |

| 38             | VDDOSC                        | Р   | -    | Supply Voltage: Supply input to the internal VCO. +3.3 Volts +5/-10%.                                                                                                                                            |  |

| 39             | VSSOSC                        | Р   | -    | Supply Ground: 0 V for the internal VCO.                                                                                                                                                                         |  |

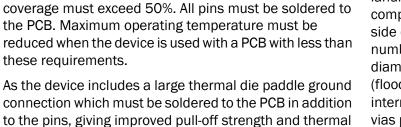

| 49             | VSSO                          | Р   | -    | Supply Ground: Common 0 V.<br>This is the central leadframe pad on the underneath of the package.                                                                                                                |  |

Note...A= Analog, I = Input, O = Output, P = Power,  $LVTTL/LVCMOS^{U} = LVTTL/LVCMOS$  input with pull-up resistor,  $LVTTL/LVCMOS_{D} = LVTTL/LVCMOS$  input with pull-down resistor.

# ADVANCED COMMUNICATIONS

SEMTECH

FINAL

# DATASHEET

### Table 2 Internally Connected (IC) Pin

| Pin No. | Symbol | I/0 | Туре | Description                              |

|---------|--------|-----|------|------------------------------------------|

| 37      | IC1    | -   | -    | Internally Connected: Connect to ground. |

#### Table 3 Functional Pins

| Pin No. | Symbol     | I/0 | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------|------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2       | OUT1N      | 0   | CML or<br>LVPECL | One of four CML or LVPECL differential outputs, partnered with pin 3; programmable at spot frequencies from 19.44 MHz up to 625.00 MHz. For outputs OUT1 and OUT2 only, output frequency can be instantly configured using Rate Selection pins (pins 47 and 48 for OUT1), from a set of four pre-configured "Available Rates". See "Configuration" on page 13. Output is on when VDD01 is supplied with 3.3 V, or off when VDD01 is tied to zero volts. If VDD01 is connected to 0 V remove external biasing resistors. |  |

| 3       | OUT1P      | 0   | CML or<br>LVPECL | CML or LVPECL differential output partnered with pin 2. See pin 2 description for more detail.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 5       | OUT2N      | 0   | CML or<br>LVPECL | One of four CML or LVPECL differential outputs, partnered with pin 6; programmable at spot frequencies from 19.44 MHz up to 625.00 MHz. For outputs OUT1 and OUT2 only output frequency can be instantly configured using Rate Selection pins (pins 45 and 46 for OUT2), from a set of four pre-configured "Available Rates". See "Configuration" on page 13. Output is on when VDD02 is supplied with 3.3 V, or off when VDD02 is tied to zero volts. If VDD02 is connected to 0 V remove external biasing resistors.  |  |

| 6       | OUT2P      | 0   | CML or<br>LVPECL | CML or LVPECL differential output partnered with pin 5. See pin 5 description for more detail.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 8       | OUT3N      | 0   | CML or<br>LVPECL | One of four CML or LVPECL differential outputs, partnered with pin 9; programmable at spot frequencies from 19.44 MHz up to 625.00 MHz. For outputs OUT3 and OUT4 only, the output frequency selection is controlled at power-up or on reset from a set of four pre-configured "Available Rates". See "Configuration" on page 13. Output is on when VDD03 is supplied with 3.3 V, or off when VDD03 is tied to zero volts. If VDD03 is connected to 0 V remove external biasing resistors.                              |  |

| 9       | OUT3P      | 0   | CML or<br>LVPECL | CML or LVPECL differential output partnered with pin 8. See pin 8 description for more detail.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 11      | OUT4N      | 0   | CML or<br>LVPECL | One of four CML or LVPECL differential outputs, partnered with pin 12; programmable a spot frequencies from 19.44 MHz up to 625.00 MHz. For outputs OUT3 and OUT4 only the output frequency selection is controlled at power-up or on reset from a set of four pre-configured "Available Rates". See "Configuration" on page 13. Output is on when VDD04 is supplied with 3.3 V, or off when VDD04 is tied to zero volts. If VDD04 is connected to 0 V remove external biasing resistors.                               |  |

| 12      | OUT4P      | 0   | CML or<br>LVPECL | CML or LVPECL differential output partnered with pin 11. See pin 11 description for more detail.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 13      | ALARM1_COO | 0   | LVTTL/<br>LVCMOS | Activity alarm output for the CLK1P/CLK1N input reference clock. Active high; high indicating clock failure. It is also used to configure the device at power-up, where it is used as a configuration output pin, that may be connected to CFG_IN[0:7] input pins as required. See "Configuration" on page 13.                                                                                                                                                                                                          |  |

| 14      | ALARM2_CO1 | 0   | LVTTL/<br>LVCMOS | Activity alarm output for the CLK2P/CLK2N input reference clock. Active high; high indicating clock failure. It is also used to configure the device at power-up time, where it is used as a configuration output pin, that may be connected to CFG_IN[0:7] input pins as required. See "Configuration" on page 13.                                                                                                                                                                                                     |  |

SEMTECH

# FINAL

#### Table 3 Functional Pins (cont...)

| Pin No. | Symbol     | I/0 | Туре                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------|------------|-----|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15      | CFG_OUT2   | 0   | LVTTL/<br>LVCMOS                                    | Configuration pin, used in the configuration on power-up of expected input clock frequency and Resync selection, by connecting to appropriate pin from the CFG_IN[0:7] pins as required. See "Configuration" on page 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 16      | ALARMC_CO3 | 0   | LVTTL/<br>LVCMOS                                    | Activity alarm output for the currently selected input reference clock. Active high; high indicating clock failure. It is also used to configure the device at power-up, where it is used as a configuration output pin that may be connected to CFG_IN[0:7] input pins as required. See "Configuration" on page 13.                                                                                                                                                                                                                                                                                                                                                                   |  |

| 17      | LOCKB      | 0   | Analog                                              | Lock detect output. This is a pulse-width modulated output current, with each pulse typically +10 $\mu$ A. The output produces a pulse with a width in proportion to the phase error seen at the internal phase detector. This pin should be connected via an externa parallel capacitor and resistor to ground. The pin voltage will then give an indication of phase lock: When low, the device is phase locked; when high the device has frequent large phase errors and so is not phase locked. The value of the RC components used determines the time and level of consistency required for lock indication. If LOCKB is disabled by configuration the LOCKB output is held low. |  |

| 18      | CFG_IN0    | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power, or one of the configuration outputs at pins 13 to 16. This pin is used with pin 19 to set the available output rates as shown in Table 11.                                                                                                                                                                                                                                                          |  |

| 19      | CFG_IN1    | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power, or one of the configuration outputs at pins 13 to 16. This pin is used with pin 18 to set the available output rates as shown in Table 11.                                                                                                                                                                                                                                                          |  |

| 20      | CFG_IN2    | I   | LVTTL/<br>LVCMOS <sub>D</sub><br>Schmitt<br>Trigger | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power, or one of the configuration outputs at pins 13 to 16. This pin is used with pin 21 to set the input divider and output pad mode (CML or LVPECL) configuration for OUT1 and OUT2 as in Table 10.                                                                                                                                                                                                     |  |

| 21      | CFG_IN3    | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power, or one of the configuration outputs at pins 13 to 16. This pin is used with pin 20 to set the input divider and output pad mode (CML or LVPECL) configuration for OUT1 and OUT2 as in Table 10.                                                                                                                                                                                                     |  |

| 22      | CFG_IN4    | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power or one of the configuration outputs at pins 13 to 16. This pin is used with pin 23 to set the clock edge used for SYNC sampling, and the output clock frequency of OUT3 (pins 8 and 9) and OUT4 (pins 11 and 12), as shown in Table 12.                                                                                                                                                              |  |

| 23      | CFG_IN5    | Ι   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power or one of the configuration outputs at pins 13 to 16. This pin is used with pin 22 to set the clock edge used for SYNC sampling, and the output clock frequency of OUT3 (pins 8 and 9) and OUT4 (pins 11 and 12), as shown in Table 12.                                                                                                                                                              |  |

# ACS8946 JAM PLL

# ADVANCED COMMUNICATIONS

SEMTECH

| FINAL |

|-------|

|-------|

# DATASHEET

Table 3 Functional Pins (cont...)

4

| Pin No. | Symbol   | I/0 | Туре                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------|----------|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 24      | CFG_IN6  | 1   | LVTTL/<br>LVCMOS <sub>D</sub> | Configuration pin for setting up the device just after power-up or after a system reset (via pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power or one of the configuration outputs at pins 13 to 16. This pin is used with pin 25 to to set the value of the odd divider, which applies a division of 1/3/5/7/9/11/13 or 15 to the otherwise selected spot frequency, on each of the four outputs OUTN/P[4:1]. It is also used to enable or disable the lock detector (pin 17 LOCKB), and to set the output pad mode (CML or PECL) for OUT3 and OUT4 as shown in Table 13. |  |

| 25      | CFG_IN7  | I   | LVTTL/<br>LVCMOS <sub>D</sub> | Configuration pin for setting up the device just after power-up or after a system reset (v pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just after power-up, so that the device works out whether this pin is connected to ground, power or one of the configuration outputs at pins 13 to 16. This pin is used with pin 24 to set the value of the odd divider, which applies a division of 1/3/5/7/9/11/13 or 15 the otherwise selected spot frequency on each of the four outputs OUTN/P[4:1]. It is also used to enable or disable the lock detector (pin 17 LOCKB) and to set the output pad mode (CML or PECL) for OUT3 and OUT4 as shown in Table 13.           |  |

| 27      | CLK1N    | I   | LVPECL                        | Input reference clock that the PLL will phase and frequency lock to. Can accept 19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz, and frequencies near to these so long as the chosen frequency remains stable to within the tracking range of $\pm$ 400 ppm. (See "Inputs" on page 8 and Table 10). Can accept LVPECL or LVDS or CML inputs given suitable external interface components. Partnered with pin 28. This clock or CLK2 can be automatically or manually selected as the reference clock, see Table 4.                                                                                                                                                                      |  |

| 28      | CLK1P    | I   | LVPECL                        | Input reference clock that the PLL will phase and frequency lock to. Can accept<br>19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz and<br>frequencies near to these so long as the chosen frequency remains stable to within the<br>tracking range of ±400 ppm. (See "Inputs" on page 8 and Table 10). Can accept LVPECL<br>or LVDS or CML inputs given suitable external interface components. Partnered with pin<br>27. This clock or CLK2 can be automatically or manually selected as the reference clock,<br>see Table 4.                                                                                                                                                          |  |

| 30      | CLK2N    | 1   | LVPECL                        | Second Input reference clock that the PLL will phase and frequency lock to. Input<br>reference clock that the PLL will phase and frequency lock to. Can accept 19.44 MHz,<br>38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz, and frequencies<br>near to these so long as the chosen frequency remains stable to within the tracking<br>range of ±400 ppm. (See "Inputs" on page 8 and Table 10). Can accept LVPECL or LVD<br>or CML inputs given suitable external interface components. Partnered with pin 31. This<br>clock or CLK1 can be automatically or manually selected as the reference clock, see<br>Table 4.                                                                           |  |

| 31      | CLK2P    | I   | LVPECL                        | Second Input reference clock that the PLL will phase and frequency lock to. Input reference clock that the PLL will phase and frequency lock to. Can accept 19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz, and frequencies near to these so long as the chosen frequency remains stable to within the tracking range of $\pm$ 400 ppm. (See "Inputs" on page 8 and Table 10). Can accept LVPECL or LVDS or CML inputs given suitable external interface components. Partnered with pin 30. This clock or CLK2 can be automatically or manually selected as the reference clock, see Table 4.                                                                                          |  |

| 32      | SEL_CLK2 | I   | LVTTL/<br>LVCMOS <sub>D</sub> | Used in combination with pin 33, AUTO_SEL, either to select the CLK2 clock (high) or CLK1 clock (low) in manual control mode, or to select automatic switching mode, as described in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

# ADVANCED COMMUNICATIONS

SEMTECH

FINAL

DATASHEET

#### Table 3 Functional Pins (cont...)

| Pin No. | Symbol   | I/0 | Туре                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------|----------|-----|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 33      | AUTO_SEL | Ι   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Used in combination with pin 32, SEL_CLK2, to select automatic switching mode, as described in Table 4.                                                                                                                                                                                                                                                                                                        |  |

| 35      | VCP      | A   | Analog                                              | Connection for external loop filter components. This is the differential control voltage input to the internal VCO and the internal differential charge pump output up to a level of 210 $\mu$ A.                                                                                                                                                                                                              |  |

| 36      | VCN      | A   | Analog                                              | Connection for external loop filter components. This is the differential control voltage input to the internal VCO and the internal differential charge pump output up to a level $210 \ \mu$ A.                                                                                                                                                                                                               |  |

| 40      | RESETB   | I   | LVTTL/<br>LVCMOS <sup>U</sup><br>Schmitt<br>Trigger | Active low reset signal with pull up and Schmitt type input. Used to apply an active-low<br>Power-on Reset (POR) signal during system initialization. Should be connected via a<br>capacitor to ground.                                                                                                                                                                                                        |  |

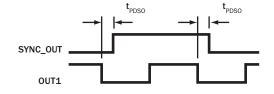

| 41      | SYNCP    | I   | LVPECL                                              | Additional differential input (2 kHz or 8 kHz) where the Sync signal on this input is sampled and resynchronized by clock output OUT1. The resynchronization can be configured via CFG_IN4 and CFG_IN5 to be with the rising or falling edge of output OUT see Table 12. Will also accept CML or LVDS signal types when used in conjunction with external biasing components as described in Figures 14 to 19. |  |

| 42      | SYNCN    | I   | LVPECL                                              | Additional differential input (2 kHz or 8 kHz) where the Sync signal on this input is sampled and resynchronized by clock output OUT1. The resynchronization can be configured via CFG_IN4 and CFG_IN5 to be with the rising or falling edge of output OUT see Table 12. Will also accept CML or LVDS signal types when used in conjunction with external biasing components as described in Figures 14 to 19. |  |

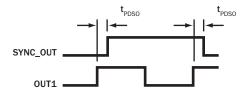

| 44      | SYNC_OUT | 0   | LVTTL/<br>LVCMOS                                    | A sampled and therefore lower jitter and resynchronized version of the SYNC signal selected from the SYNC1 input. The clock selected on OUT1 (see pins 2 and 3) is used perform the resynchronization. The resynchronization can be configured to be with the rising or falling edge of output OUT1; see Table 12. The maximum output frequency on OUT1 = 77.76 MHz when the Sync function is used.            |  |

| 45      | RATE2A   | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Inputs to control the frequency of the signal produced on pins 5 (OUT2P) and 6 (OUT2N). See Table 11.                                                                                                                                                                                                                                                                                                          |  |

| 46      | RATE2B   | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Inputs to control the frequency of signal that is produced on pins 5 (OUT2P) and 6 (OUT2N). See Table 11.                                                                                                                                                                                                                                                                                                      |  |

| 47      | RATE1A   | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Inputs to control the frequency of signal that is produced on pins 2 (OUT1P) and 3 (OUT1N). See Table 11.                                                                                                                                                                                                                                                                                                      |  |

| 48      | RATE1B   | I   | LVTTL/<br>LVCMOS <sub>D</sub>                       | Inputs to control the frequency of signal that is produced on pins 2 (OUT1P) and 3 (OUT1N). See Table 11.                                                                                                                                                                                                                                                                                                      |  |

Note...A= Analog, I = Input, O = Output, P = Power,  $LVTTL/LVCMOS^{U} = LVTTL/LVCMOS$  input with pull-up resistor,  $LVTTL/LVCMOS_{D} = LVTTL/LVCMOS$  input with pull-down resistor.

DATASHEET

# ADVANCED COMMUNICATIONS

EMTECH

**FINAL**

### Description

The ACS8946 is a low-jitter integrated PLL for dejittering and clock rate translation, meeting the jitter requirements for SONET up to and including OC-12 (622.08 MHz) systems. It is compliant to the relevant ITU, Telcordia/Bellcore and ETSI standards for at least OC-3 (155.52 MHz) and OC-12 (622.08 MHz) - equivalent to the corresponding STM1 and 4 rates. It may also be used as an initial clock clean-up device in, for example, in OC-48 systems, where the CMU PLL in the Serializer/Framer has a suitable bandwidth.

The ACS8946 can be configured for a range of applications using a minimal number of external components and is available in a small form factor QFN48 package at 7 mm x 7 mm x 0.9 mm outer dimensions.

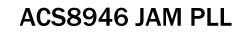

An evaluation board and GUI software is available on request for hands-on device assessment.

#### Figure 3 Example EVB GUI Software

### Inputs

The ACS8946 has two LVPECL differential inputs (CLK1N/P, pins 27 and 28, and CLK2N/P, pins 30 and 31). These are programmable to accept input frequencies of 19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz. Frequencies near to these spot frequencies can also be accepted (see Table 5) so long as the chosen frequency supplied to each input remains stable to within the  $\pm$ 400 ppm tracking range.

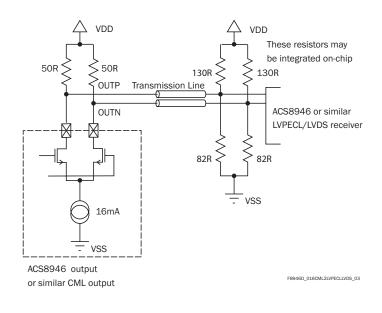

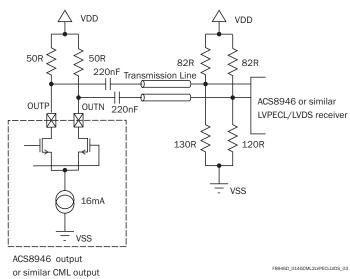

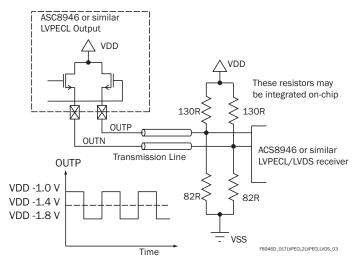

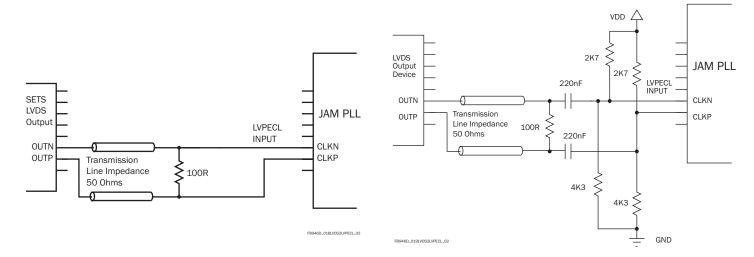

LVDS and CML inputs can be accepted given suitable passive resistive and capacitive interface components.

Phase comparisons are performed directly at the selected spot frequency rates in the internal Phase and Frequency Detector (PFD), unless GbE (Gigabit Ethernet) rates are selected for output rates, in which case the input frequencies are divided as required prior to the PFD. Either clock input may be manually or automatically selected as the reference based on the detection of clock activity at the inputs. The signals AUTO\_SEL and SEL\_CLK2, shown in Table 4, are used to control the input clock selection. In automatic mode the clock selection between CLK1 and CLK2 is non-revertive, i.e. if the PLL is locked onto CLK1 and CLK1 fails so that the PLL switches over to CLK2, then when CLK1 becomes operational again the PLL will not switch back to CLK1.

| AUTO_SEL | SEL_CLK2 | Selected<br>Reference                                      | Feedback Clock |

|----------|----------|------------------------------------------------------------|----------------|

| 0        | 0        | CLK1                                                       | Internal Path  |

| 0        | 1        | CLK2                                                       | Internal Path  |

| 1        | 0        | CLK1                                                       | CLK2           |

| 1        | 1        | AUTOMATIC<br>SELECTION<br>(Activity Monitor<br>determines) | Internal Path  |

Configuration of expected input clock frequency, which has to be the same for both clock inputs, is set by the wiring of configuration pins described in Table 10.

Unused differential inputs from CLK[2:1]N/P and SYNCN/P should be wired P to GND and N to VDD.

In addition to the main clock inputs CLK1, and CLK2, a single differential SYNC input is provided.

The permitted input frequency range either side of the selected spot frequency depends on the input clock rate. Table 5 presents the list of configurable input spot frequencies, and shows the maximum and minimum range about each input spot frequency that can be allowed as input to the device as a percentage of the configured input spot frequency.

An External Feedback mode is available and may be used for greater control of phase discrepancies for example when using external buffers. In External Feedback mode the external feedback signal is received at the CLK2 input, hence CLK1 can be the only input in this mode.

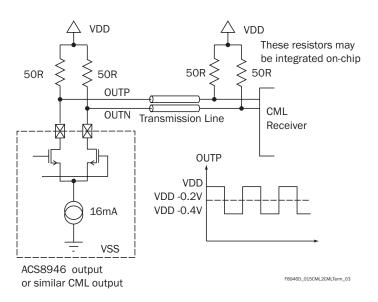

# Outputs

The ACS8946 has four, LVPECL or CML, differential outputs: OUT[4:1]N/P, pins 11/12, 8/9, 5/6, and 2/3. Outputs are produced in a CML or LVPECL output format on up to four outputs concurrently. Interfacing to LVDS is

### FINAL

#### Table 5 Permitted Input Frequency Range

EMTECH

| Selected Input<br>Spot<br>Frequency/<br>MHz | Selected FEC<br>Ratio (*or<br>Divider Ratio<br>using Odd<br>Divider) | Max and Min Permitted Input<br>Frequency Expressed as a<br>Percentage Above (+%) or Belo<br>(-%) the Selected Input Spot<br>Frequency |     |

|---------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                             |                                                                      | +%                                                                                                                                    | -%  |

| 19.44, 38.88<br>77.76, 155.52               | 1:1                                                                  | 12.0                                                                                                                                  | 3.0 |

| 125.00                                      | 5:4*                                                                 | 10.0                                                                                                                                  | 3.0 |

| 156.25                                      | 1:1                                                                  | 12.0                                                                                                                                  | 3.0 |

also possible using suitable passive components (see "Input and Output Interface Terminations" on page 27).

Output clock rates at 19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz, 156.25 MHz, 311.04 MHz, 622.08 MHz or 625.00 MHz are selectable. Additionally, odd number division of these frequencies up to divide-by-15 can also be configured. Note that if odd number division is used, the frequency adjustment factor will apply to all outputs, adjusting all selected output frequencies proportionally.

The output frequency of each output is determined by a combination of the wiring of the configuration pins CFG\_IN[7:0] read at power-up, and state of the asynchronously set RATE[2:1]A and RATE[2:1]B pins. The user configures a set of "Available Rates" (four frequencies that are available for selection at every Clock Output) and then configures each output individually to output one of these four rates. OUT1 and OUT2 are asynchronously controllable allowing the output frequency to be switched among the "Available Rates" under control from the rate selection pins (RATE[2:1]A and RATE[2:1]B).

To determine the correct wiring of configuration pins to configure the device involves the use of several look-up tables, and for completeness the datasheet includes all of these, with worked examples (See "Configuration" on page 13). However, to make configuring the device much more simple than this description and look-up tables suggest, Semtech provides a user-friendly Graphical User Interface (GUI) software package to accompany the ACS8946 in which the User enters the required I/O frequencies, dividers settings etc. as required for a particular application, and the GUI responds by displaying the interconnections required to achieve that configuration. Refer to the ACS8946 EVB Document and associated software.

Unused outputs should be left floating with their associated VDD connected to GND. For example, if OUT4 is not required, connect VDD04 to GND and leave OUT4N and OUT4P unconnected.

# **Clock Multiplication**

The ACS8946 provides options to multiply a 19.44 MHz input by 2, 4, 8, 16, or 32 for standard SONET SDH spot frequency configurations. 125.00 MHz dejittered output for Gigabit Ethernet (GbE/10 GbE) is also supported if 125.00 MHz is provided as the input reference, and 156.25 MHz input (for 12.5 GbE) is also supported. These rates are configured by the wiring of CFG\_IN[3:2], see Table 10.

If the input frequency used is a percentage away from the configured spot frequency, then the resulting output frequency will change by the same percentage. Refer back to Table 5 for permitted input frequencies.

Note... GbE rates are not directly available as conversions from SONET/SDH rates.

# **Voltage Controlled Oscillator**

The internal VCO operates at 2.48832 GHz when the device is configured for standard SONET/SDH spot frequencies. The VCO frequency is divided down to the selected rate giving a precise 50/50 balanced mark/space ratio for the output. For 125.00 MHz operation the VCO operates at 2.500 GHz.

# **Jitter Filtering**

Input jitter is attenuated by the PLL with the frequency cutoff point (Fc), at which jitter is either tracked or attenuated, defined by the -3 dB point i.e. the position of the first pole of the PLL loop filter. The bandwidth (frequency at which the first pole occurs) is defined by the component value selected for the filter in Tables 6 and 7.

For 19.44 MHz input, using a loop filter bandwidth of 2 kHz and damping factor of 1.2 gives:

- High input jitter attenuation and roll off:

- - 20 dB/decade from first loop filter pole, (Fc)

- - 40 dB/decade from 2<sup>nd</sup> pole (typically 10 x Fc)

- Jitter peaking is less than 1 dB (dependent on the loop filter components)

DATASHEET

## **ADVANCED COMMUNICATIONS**

# FINAL

• Typical final output jitter. e.g. 2.8 ps rms measured over the integration range of 12 kHz -20 MHz offset from carrier.

# Jitter Filtering: Partnering with Semtech Line Card Protection Parts

One possible line card solution is to use the ACS8946 on the line card to provide line card protection and direct jitter filtering of references received from a Semtech SETS device (ACS8520/30) on the sync card. If a Semtech LC/P part (ACS8525) is used on the line card, another possible solution uses the ACS8946 after the Semtech LC/P part to dejitter the LC/P device's output.

In the first solution, Master/Slave phase alignment on reference switchover is taken care of by a redundant pair arrangement of SETS devices, which use their output phase alignment features to ensure the ACS8946 is supplied with input clocks that are very closely tied in phase. Then, on a line card reference switch, the ACS8946 acts as a simple MUX adding negligible phase offset between the references, giving very low output disturbance for the combined system, as well as performing its dejittering function.

In the second, more sophisticated solution, the reference switching capability of ACS8946 is not used, as this is carried out by the SETS or LC/P part.

In both cases, the ACS8946 can be used as both an output jitter cleaner, and as a rate converter (19.44 MHz and above).

One "Real World" application for the ACS8946 is to use it to dejitter the 19.44 MHz output from a Semtech ACS8525 LC/P device. In this case it is recommended to set the ACS8946 PLL bandwidth to around 2 kHz to provide a low jitter total solution. The test results detailed in the Electrical Specifications section show the "Real World" performance of this combination of parts which is a superior solution to those traditionally using simple discrete PLLs, and has the following advantages:

- Low overall bandwidth, 18 Hz for example—dictated by the ACS8525.

- High input jitter attenuation and roll-off:

- First, second and third order roll-off points:

- - 20 dB/decade 18 Hz to 2 kHz,

- - 40 dB/decade 2 kHz to 200 kHz and

- - 60 dB/decade for >200 kHz.

- Typical final output jitter, e.g. 2.9 ps rms (measured over the integration range 12 kHz 20 MHz) dictated by the ACS8946.

- High frequency stability when all input clocks fail; holdover frequency control to Stratum 3—dictated by the ACS8525.

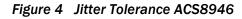

# **Input Jitter Tolerance**

Jitter tolerance is defined as the maximum amplitude of sinusoidal jitter that can exist on the input reference clock above which the device fails to acquire/maintain lock.

For the stand-alone device, the jitter tolerance is shown in Figure 4. for an undivided reference i.e. full rate PFD. For frequencies below the PLL bandwidth, jitter tolerance is seen to decrease at a rate of -20 dB per decade. For jitter frequencies above the PLL bandwidth, jitter tolerance is limited to 0.9 UI p-p.

Note... If the reference clock is divided, then the jitter tolerance will be improved.

When the ACS8946 follows an ACS8525, the input jitter tolerance is wholly defined by the ACS8525. The system jitter tolerance is dramatically increased due to the extended phase capture range of the digital PLL within the ACS8525.

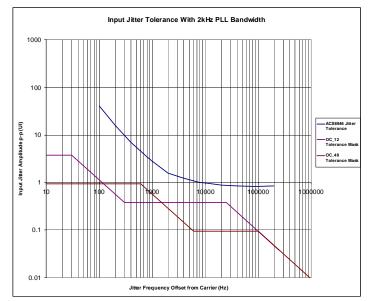

# **Jitter Transfer**

Jitter transfer is a ratio of input jitter present on the reference clock to the filtered jitter present on the output clock. Standalone, the ACS8946 Jitter Transfer

FINAL

#### DATASHEET

Characteristic is defined solely by the loop filter bandwidth and is shown in Figure 5, which shows the transfer characteristic using the recommended loop filter bandwidth of 2 kHz with a damping factor of 1.2.

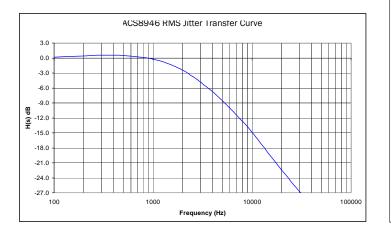

# Figure 5 Jitter Transfer Characteristic, ACS8946 Stand-alone

In the combined solution, the ACS8525 device provides additional low frequency jitter filtering. The Jitter Transfer Characteristic of the combined ACS8946 and ACS8525 is shown in Figure 6.

Figure 6 Jitter Transfer Characteristic, ACS8525 and ACS8946 combined

155.52 MHz output clock using an input reference of 19.44 MHz.

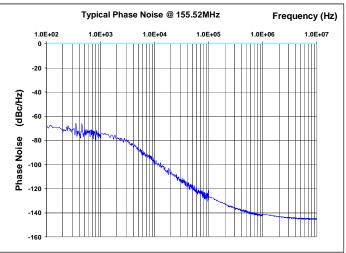

# Figure 7 Phase Noise Offset from Carrier of ACS8946 622.08 MHz output clock

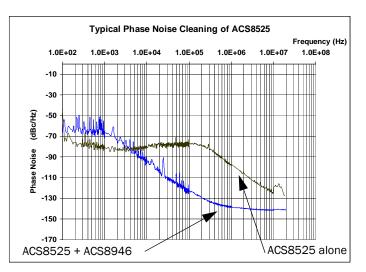

In the combined line card solution, the inherent jitter generated by the ACS8525 is attenuated by the ACS8946 as shown in the phase noise plot in Figure 8.

Figure 8 Phase Noise Offset from Carrier, ACS8525 155.52 MHz output clock, with and without ACS8946 Clock Cleaner

# **Phase Noise Performance**

The inherent jitter generation by the ACS8946 is shown in the phase noise plot in Figure 7 measured on a

# **Lock Detector**

A simple lock detector is incorporated which combines the plus and minus phase errors from the phase detector,

DATASHEET

### **ADVANCED COMMUNICATIONS**

such that if any phase error signal is present, the LOCKB output drives out a +10  $\mu$ A current, otherwise it is off.

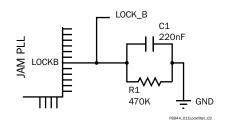

Consequently this output (LOCKB) is a pulse width modulated (PWM) pulse stream whose mark/space ratio indicates the current input phase error. Filtering this signal with a simple external RC parallel filter as shown in Figure 9 will give a signal whose output level indicates PLL phase and frequency lock.

#### Figure 9 Lock Filter Components

The filtering components are external so that the time to indicate lock or not locked can be optimized for the application. The output indicates both phase and frequency lock. During off-frequency conditions the LOCKB output will be predominately high in its PWM generation with the filtered version giving a constant high state.

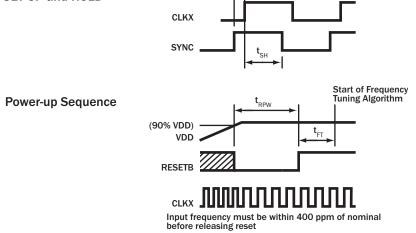

# **PLL Bandwidth Setting**

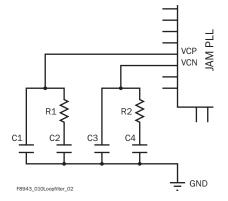

The bandwidth is set by two identical sets of passive RC components that connect to the differential charge pump outputs and internal VCO control inputs. Pins VCN and VCP are the combined differential charge pump outputs and VCO control voltage inputs. Figure 10 shows the arrangement.

#### Figure 10 Loop Filter Components

All capacitors should be low leakage and low ESR (Equivalent Series Resistance). Tantalum, or ceramic where possible, are suitable. Tables 6 to 9 are based on a

damping factor of 1.2 (phase margin 80.2°). Higher damping factors may be used if lower transfer peaking is required. Contact Semtech Sales Support for further details.

# RC Components Required to Achieve Bandwidth at Given Input Frequencies (Tables 6 to 9).

| Bandwidth<br>Closed Loop | <b>R1 &amp; R2/</b><br>Ω | <b>C2 &amp; C4</b> /<br>μ <b>F</b> | C1 & C3<br>nF |

|--------------------------|--------------------------|------------------------------------|---------------|

| 1500                     | 56                       | 33                                 | 200           |

| 2000                     | 75                       | 15                                 | 100           |

| 4000                     | 150                      | 4.7                                | 33            |

| 8000                     | 270                      | 0.68                               | 7.5           |

#### Table 6 77.76 MHz or 19.44 MHz Input Frequency

| Tahla 7 | 155 52 MHz ou  | - 38 88 MHz In | put Frequency  |

|---------|----------------|----------------|----------------|

|         | 133.32 WINZ UI | 30.00 MINZ III | ραι Γιεγμετική |

| Bandwidth<br>Closed Loop | <b>R1 &amp; R2/</b><br>Ω | <b>C2 &amp; C4/</b><br>μ <b>F</b> | C1 & C3<br>nF |

|--------------------------|--------------------------|-----------------------------------|---------------|

| 1500*                    | 110                      | 15                                | 91            |

| 2000                     | 150                      | 6.8                               | 47            |

| 4000                     | 300                      | 2.2                               | 15            |

| 8000                     | 560                      | 0.47                              | 3.9           |

Note...\* not available at 155.52 MHz input

#### Table 8 125 MHz Input Frequency

| Bandwidth<br>Closed Loop | <b>R1 &amp; R2/</b><br>Ω | <b>C2 &amp; C4/</b><br>μF | C1 & C3<br>nF |

|--------------------------|--------------------------|---------------------------|---------------|

| 1500                     | 68                       | 22                        | 150           |

| 2000                     | 91                       | 15                        | 91            |

| 4000                     | 180                      | 3.3                       | 20            |

| 8000                     | 360                      | 0.68                      | 6.2           |

Note...All bandwidths are subject to  $\pm$  20% variation due to component tolerancing.

**FINAL**

DATASHEET

# ADVANCED COMMUNICATIONS

EMTECH

FINAL

#### Table 9 156.25 MHz Input Frequency

| Bandwidth   | <b>R1 &amp; R2</b> /Ω | <b>C2 &amp; C4</b> /<br>μ <b>F</b> | C1 & C3    |  |

|-------------|-----------------------|------------------------------------|------------|--|

| Closed Loop | 52                    | μΓ                                 | μ <b>F</b> |  |

| 2000        | 75                    | 15                                 | 100        |  |

| 4000        | 150                   | 4.7                                | 33         |  |

| 8000        | 270                   | 0.68                               | 7.5        |  |

# Source Switching - State Diagram

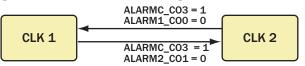

Figure 11 Simplified State Diagram of Source Switching

ALARM SIGNALS:

ALARMC\_CO3 – Activity alarm for the currently selected clock (from PFD) ALARM1\_CO0 – Activity alarm for CLK1

ALARM2\_CO1 – Activity alarm for CLK2 F8946D\_012SimpStateDiag\_01

The state diagram in Figure 11 shows a simplified view of the automatic switching behavior in the presence of activity alarms. The *ALARMC\_CO3* signal from the PFD is used to disqualify a clock, and the signals *ALARM1\_CO0* and *ALARM2\_CO1* representing no activity on input clocks CLK1 and CLK2 respectively, are used to determine whether or not to select the remaining clock.

Switching between CLK1 and CLK2 is non-revertive.

With *ALARMC\_CO3* providing a view of the currently selected clock that is independent to *ALARM1\_CO0* and *ALARM2\_CO1* signals, source selection behavior can be more complex when these alarm signals disagree, and so the state machine is necessarily more complex than the one shown here in order to accommodate such behavior e.g. when a clock signal is disconnected for a very short period of time, or when an input clock is running at the wrong frequency. If further details are required contact Semtech Sales Support.

# Configuration

A higher degree of flexibility and programmability is possible via the use of configuration pins on the device. Permanent connections made externally from CFG\_IN[7:0] pins to the configuration output pins ALARM1\_COO, ALARM2\_CO1, CFG\_OUT2, ALARMC\_CO3 or to ground or VDD set up the device. The ACS8946 GUI software presents the configuration information in the most user-friendly manner, though the following tables can be used instead to work out the connectivity required for a particular configuration. For example, the last five columns in Table 10 give the results of the wired connections shown in the second and third columns. E.g., taking the row 7, connecting pin CFG\_IN2 to VDD and CFG\_IN3 to ALARM2\_C01, gives an input frequency of 19.44 MHz, a highest output frequency of 622.08 MHz and configures the outputs as LVPECL.

### **Output Configuration**

The output spot frequency selection for OUT1 is asynchronously controlled by the RATE1A/B select pins (pins 47 and 48), which select one from a set of four "Available Rates" that have been pre-selected at powerup by the wiring configuration of pins 18 and 19 (CFG\_IN[1:0]). The wiring configuration of these two pins preselects a set of any four out of seven rates: 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz, 622.08 MHz and disabled, which means that each of the four outputs can run independently at any one of the four pre-selected rates - chosen by the AB value in Table 11 and odd divisions thereof as defined by the start-up configuration of CFG\_IN2/CFG\_IN3 and/or CFG\_IN6/CFG-IN7 respectively).

OUT2 is asynchronously controlled by the RATE2A/B select pins (pins 45 and 46) in the same way as OUT1. Outputs OUT3 and OUT4 cannot be controlled asynchronously; the output frequency selection is controlled at power-up or on reset by a combination of the connections of CFG\_IN[1:0] and CFG\_IN[5:4] to either VSS, VDD, ALARM1\_CO0 (pin 13) or ALARM2\_CO1 (pin 14). Given the four Available Rates have been configured as described previously, which one of these four rates is available on OUT3 is then dependent on the connections of the CFG\_IN5 pins to either VSS, VDD, ALARM1\_CO0 (pin 13) or ALARM2\_CO1 (pin 14)—see Table 12.

The method to configure the device is summarized as follows:

- Select the required "Available Rates" that will be made available for selection at all four outputs using CFG\_IN[1:0] (See Table 11).

- Define the frequencies of the fixed outputs OUT3/OUT4 using CFG\_IN[5:4] (See Table 12) and the required RESYNC Edge result.

DATASHEET

# ADVANCED COMMUNICATIONS

EMTECH

- Define/change the frequencies of the dynamically controllable outputs OUT1/OUT2 by driving the RATE[2:1]A/B pins high or low in accordance with the AB pattern for the required frequency as given in Table 11.

- Using CFG\_IN[3:2], select the output interface type (CML/LVPECL) for outputs OUT1 and OUT2. (See Table 10).

- Using CFG\_IN[7:6], enable/disable LOCKB, select the required output interface type for OUT3/OUT4 and set any odd division. If odd division is not required, set to 1. (See Table 13).

## **Example Configuration**

Decide which set of four output rates is most appropriate for the application and look for the configuration that provides these "Available Rates" in Table 11. E.g. If 77.76 MHz, 38.88 MHz, 19.44 MHz and Off are required, then configuration No. 34 in Table 11 will suffice, i.e. connect CFG\_INO to ALARMC\_CO3 and connect CFG\_IN1 to CFG\_OUT2.

To set OUT3 or OUT4 requires the additional configuration of CFG\_IN4 and CFG\_IN5 as given by Table 12 (which also configures RESYNC Edge). If OUT4 is required to be set to "Off", since "Off" has already been defined by previous selection as AB=00 in Table 11, then look up the 00 pattern in Table 12, under "resulting RATE 4[AB]" (giving rows 0 to3 and 16 to 19). Now refine the selection such that OUT 3 provides 19.44 MHz output (AB=01) and a rising RESYNC edge is required - this points to row 17 only, i.e. connect CFG\_IN4 to ALARM1\_CO0 and connect CFG\_IN5 to ALARMC-CO3.

Set each of OUT[2:1] to one of these four Available Rates, as required using the rate selection pins, e.g. to set Output OUT2 to output 38.88 MHz, set RATE2A =1 and RATE2B=0.

To configure an input to the required frequency of 77.76 MHz (and Output technology for OUT 1 and OUT2 only to CML), configure CFG\_IN2 to GND and CFG\_IN3 to CFG\_OUT2 as per row 2 in Table 10.

Table 13 provides the configuration information for using pins CFG\_IN[7:6] to configure whether LOCKB is enabled or disabled, the value of the odd divider, and the port interface type for OUT3 and OUT4. For example, assuming LVPECL interface type is required, LOCKB is to be enabled and the output rates (set previously according to Tables 11 and 12) are to be divided by 5 to give "Available Rates" of Off, 3.888 MHz,7.776 MHz, 15.552 MHz, then use the configuration in row 9 of Table 13, i.e. wire CFG\_IN6 to VDD and CFG\_IN7 to ALARM2\_CO1. The corresponding frequency selections made for OUT[4:1] will be divided by 5. The configuration of row 15 would be used if the odd divider is not required (i.e. set to divide-by-1).

| Row              | Wiring of Configuration Pins |            | Output Application | Required Input    | Resulting Highest                                                              | Output Interface          |

|------------------|------------------------------|------------|--------------------|-------------------|--------------------------------------------------------------------------------|---------------------------|

| no.              | CFG_IN2                      | CFG_IN3    |                    | Frequency/<br>MHz | Available Output<br>Frequency/MHz<br>(when no further<br>division is selected) | Type for OUT1 and<br>OUT2 |

| 0                | GND                          | ALARM1_CO0 | SONET/SDH          | 155.52            | 622.08                                                                         | CML                       |

| 1                | GND                          | ALARM2_CO1 | SONET/SDH          | 155.52            | 622.08                                                                         | LVPECL                    |

| 2                | GND                          | CFG_OUT2   | SONET/SDH          | 77.76             | 622.08                                                                         | CML                       |

| 3                | GND                          | ALARMC_CO3 | SONET/SDH          | 77.76             | 622.08                                                                         | LVPECL                    |

| 4                | VDD                          | GND        | SONET/SDH          | 38.88             | 622.08                                                                         | CML                       |

| 5                | VDD                          | VDD        | SONET/SDH          | 38.88             | 622.08                                                                         | LVPECL                    |

| 6                | VDD                          | ALARM1_CO0 | SONET/SDH          | 19.44             | 622.08                                                                         | CML                       |

| 7                | VDD                          | ALARM2_CO1 | SONET/SDH          | 19.44             | 622.08                                                                         | LVPECL                    |

| 8 <sup>(i)</sup> | CFG_OUT2                     | ALARM1_CO0 | Ethernet           | 125.00            | 625.00                                                                         | CML                       |

Page 14

**FINAL**

# Table 10 Input Divider, and OUT 1 and OUT2 Output Interface Type Configurations

# SEMTECH

# ACS8946 JAM PLL

DATASHEET

### ADVANCED COMMUNICATIONS

Table 10 Input Divider, and OUT 1 and OUT2 Output Interface Type Configurations (cont...)

| Row               | Wiring of Cont | ng of Configuration Pins Output Application |          | Required Input    | Resulting Highest                                                              | Output Interface          |  |

|-------------------|----------------|---------------------------------------------|----------|-------------------|--------------------------------------------------------------------------------|---------------------------|--|

| no.               | CFG_IN2        | CFG_IN3                                     |          | Frequency/<br>MHz | Available Output<br>Frequency/MHz<br>(when no further<br>division is selected) | Type for OUT1 and<br>OUT2 |  |

| 9 <sup>(i)</sup>  | CFG_OUT2       | ALARM2_CO1                                  | Ethernet | 125.00            | 625.00                                                                         | LVPECL                    |  |

| 10 <sup>(i)</sup> | GND            | ALARM1_COO                                  | Ethernet | 156.25            | 625.00                                                                         | CML                       |  |

| 11 <sup>(i)</sup> | GND            | ALARM2_CO1                                  | Ethernet | 156.25            | 625.00                                                                         | LVPECL                    |  |

**FINAL**

Note: (i) Use odd divider to divide output by 5 to get 125.00 MHz output.

(ii) It is not possible to have 125.00 MHz and 625.00 MHz concurrently on separate outputs.

Table 11 Output Configuration and Selection

| Row | Wiring of Configuration Pins |            | "Ava    | "Available Rates" and Associated "AB" Values (see note <sup>[1]</sup> ) |         |         |  |  |  |

|-----|------------------------------|------------|---------|-------------------------------------------------------------------------|---------|---------|--|--|--|

| no. | CFG_INO                      | CFG_IN1    | AB = 11 | AB = 10                                                                 | AB = 01 | AB = 00 |  |  |  |

| 0   | GND                          | GND        | 622.08  | 311.04                                                                  | 155.52  | 77.76   |  |  |  |

| 1   | GND                          | VDD        | 622.08  | 311.04                                                                  | 155.52  | 38.88   |  |  |  |

| 2   | GND                          | ALARM1_CO0 | 622.08  | 311.04                                                                  | 155.52  | 19.44   |  |  |  |

| 3   | GND                          | ALARM2_C01 | 622.08  | 311.04                                                                  | 155.52  | Off     |  |  |  |

| 4   | GND                          | CFG_OUT2   | 622.08  | 311.04                                                                  | 77.76   | 38.88   |  |  |  |

| 5   | GND                          | ALARMC_CO3 | 622.08  | 311.04                                                                  | 77.76   | 19.44   |  |  |  |

| 6   | VDD                          | GND        | 622.08  | 311.04                                                                  | 77.76   | Off     |  |  |  |

| 7   | VDD                          | VDD        | 622.08  | 311.04                                                                  | 38.88   | 19.44   |  |  |  |

| 8   | VDD                          | ALARM1_CO0 | 622.08  | 311.04                                                                  | 38.88   | Off     |  |  |  |

| 9   | VDD                          | ALARM2_C01 | 622.08  | 311.04                                                                  | 19.44   | Off     |  |  |  |

| 10  | VDD                          | CFG_OUT2   | 622.08  | 155.52                                                                  | 77.76   | 38.88   |  |  |  |

| 11  | VDD                          | ALARMC_CO3 | 622.08  | 155.52                                                                  | 77.76   | 19.44   |  |  |  |

| 12  | ALARM1_COO                   | GND        | 622.08  | 155.52                                                                  | 77.76   | Off     |  |  |  |

| 13  | ALARM1_COO                   | VDD        | 622.08  | 155.52                                                                  | 38.88   | 19.44   |  |  |  |

| 14  | ALARM1_CO0                   | ALARM1_CO0 | 622.08  | 155.52                                                                  | 38.88   | Off     |  |  |  |

| 15  | ALARM1_CO0                   | ALARM2_C01 | 622.08  | 155.52                                                                  | 19.44   | Off     |  |  |  |

| 16  | ALARM1_COO                   | CFG_OUT2   | 622.08  | 77.76                                                                   | 38.88   | 19.44   |  |  |  |

| 17  | ALARM1_CO0                   | ALARMC_CO3 | 622.08  | 77.76                                                                   | 38.88   | Off     |  |  |  |

| 18  | ALARM2_CO1                   | GND        | 622.08  | 77.76                                                                   | 19.44   | Off     |  |  |  |

| 19  | ALARM2_CO1                   | VDD        | 622.08  | 38.88                                                                   | 19.44   | Off     |  |  |  |

# ADVANCED COMMUNICATIONS

SEMTECH

Table 11 Output Configuration and Selection (cont...)

| Row | Wiring of Configuration Pins |            | "Ava    | "Available Rates" and Associated "AB" Values (see note <sup>[1]</sup> ) |         |         |  |  |

|-----|------------------------------|------------|---------|-------------------------------------------------------------------------|---------|---------|--|--|

| no. | CFG_IN0                      | CFG_IN1    | AB = 11 | AB = 10                                                                 | AB = 01 | AB = 00 |  |  |

| 20  | ALARM2_CO1                   | ALARM1_COO | 311.04  | 155.52                                                                  | 77.76   | 38.88   |  |  |

| 21  | ALARM2_CO1                   | ALARM2_C01 | 311.04  | 155.52                                                                  | 77.76   | 19.44   |  |  |

| 22  | ALARM2_CO1                   | CFG_OUT2   | 311.04  | 155.52                                                                  | 77.76   | Off     |  |  |

| 23  | ALARM2_CO1                   | ALARMC_CO3 | 311.04  | 155.52                                                                  | 38.88   | 19.44   |  |  |

| 24  | CFG_OUT2                     | GND        | 311.04  | 155.52                                                                  | 38.88   | Off     |  |  |

| 25  | CFG_OUT2                     | VDD        | 311.04  | 155.52                                                                  | 19.44   | Off     |  |  |

| 26  | CFG_OUT2                     | ALARM1_COO | 311.04  | 77.76                                                                   | 38.88   | 19.44   |  |  |

| 27  | CFG_OUT2                     | ALARM2_C01 | 311.04  | 77.76                                                                   | 38.88   | Off     |  |  |

| 28  | CFG_OUT2                     | CFG_OUT2   | 311.04  | 77.76                                                                   | 19.44   | Off     |  |  |

| 29  | CFG_OUT2                     | ALARMC_CO3 | 311.04  | 38.88                                                                   | 19.44   | Off     |  |  |

| 30  | ALARMC_CO3                   | GND        | 155.52  | 77.76                                                                   | 38.88   | 19.44   |  |  |

| 31  | ALARMC_CO3                   | VDD        | 155.52  | 77.76                                                                   | 38.88   | Off     |  |  |

| 32  | ALARMC_CO3                   | ALARM1_COO | 155.52  | 77.76                                                                   | 19.44   | Off     |  |  |

| 33  | ALARMC_CO3                   | ALARM2_C01 | 155.52  | 38.88                                                                   | 19.44   | Off     |  |  |

| 34  | ALARMC_CO3                   | CFG_OUT2   | 77.76   | 38.88                                                                   | 19.44   | Off     |  |  |

**FINAL**