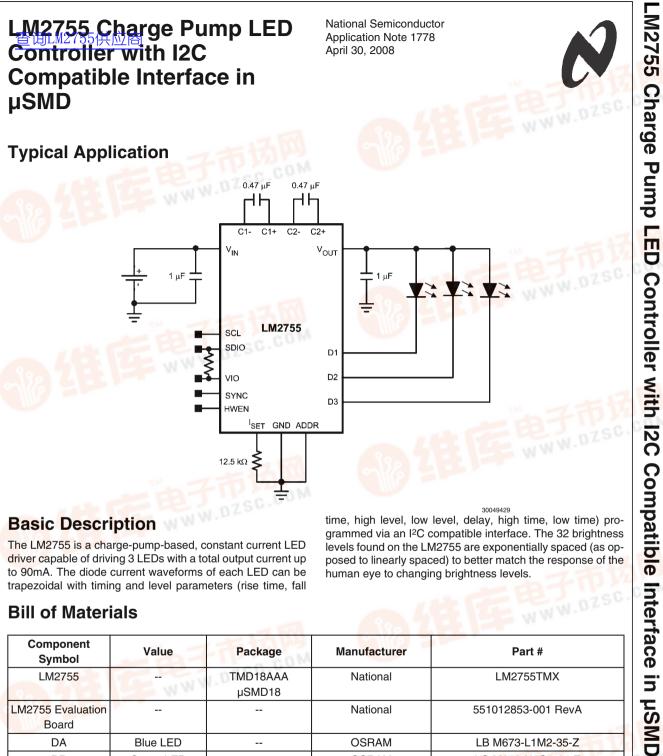

## **Basic Description**

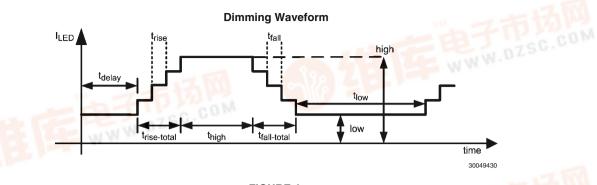

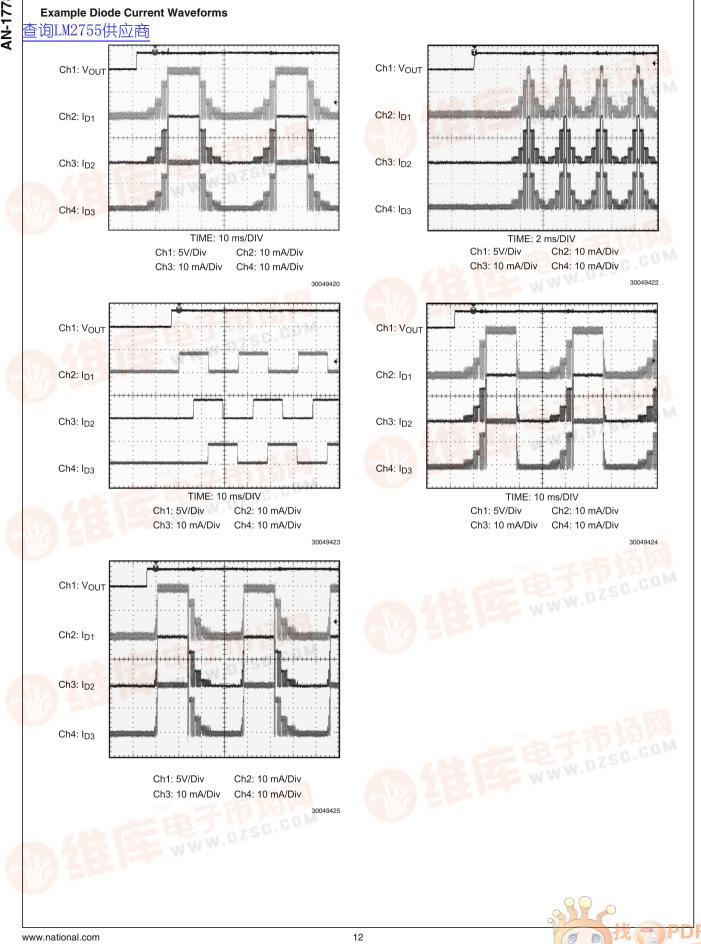

The LM2755 is a charge-pump-based, constant current LED driver capable of driving 3 LEDs with a total output current up to 90mA. The diode current waveforms of each LED can be trapezoidal with timing and level parameters (rise time, fall time, high level, low level, delay, high time, low time) programmed via an I<sup>2</sup>C compatible interface. The 32 brightness levels found on the LM2755 are exponentially spaced (as opposed to linearly spaced) to better match the response of the human eye to changing brightness levels.

## **Bill of Materials**

| Component<br>Symbol            | Value                 | Package            | Manufacturer                                 | Part #             |

|--------------------------------|-----------------------|--------------------|----------------------------------------------|--------------------|

| LM2755                         | WWW                   | TMD18AAA<br>µSMD18 | National                                     | LM2755TMX          |

| M2755 Evaluation<br>Board      |                       |                    | National                                     | 551012853-001 RevA |

| DA                             | Blue LED              |                    | OSRAM                                        | LB M673-L1M2-35-Z  |

| DB                             | Green LED             |                    | OSRAM                                        | LG M676-N2Q1-24-Z  |

| DC                             | Amber LED             |                    | OSRAM                                        | LA M676-Q2S1-1-Z   |

| DRGB                           | RGB LED               | 古田网                | TT El <mark>ect</mark> ronics /<br>OptekTech | OVSTRGBAC6         |

| C <sub>IN</sub>                | 1.0uF 10V X5R         | 0603               | TDK                                          | C1005X5R1A105M     |

| C <sub>OUT</sub>               | 1.0uF 10V X5R         | 0603               | TDK                                          | C1005X5R1A105M     |

| C <sub>1</sub> ,C <sub>2</sub> | 0.47uF 10V X5R        | 0603               | TDK                                          | C1005X5R1A474M     |

| R <sub>SET</sub>               | 12.4K OHM<br>1/10W 1% | 0603               | Vishay Dale                                  | CRCW060312K4FKEA   |

PZ-1

# AN-1778

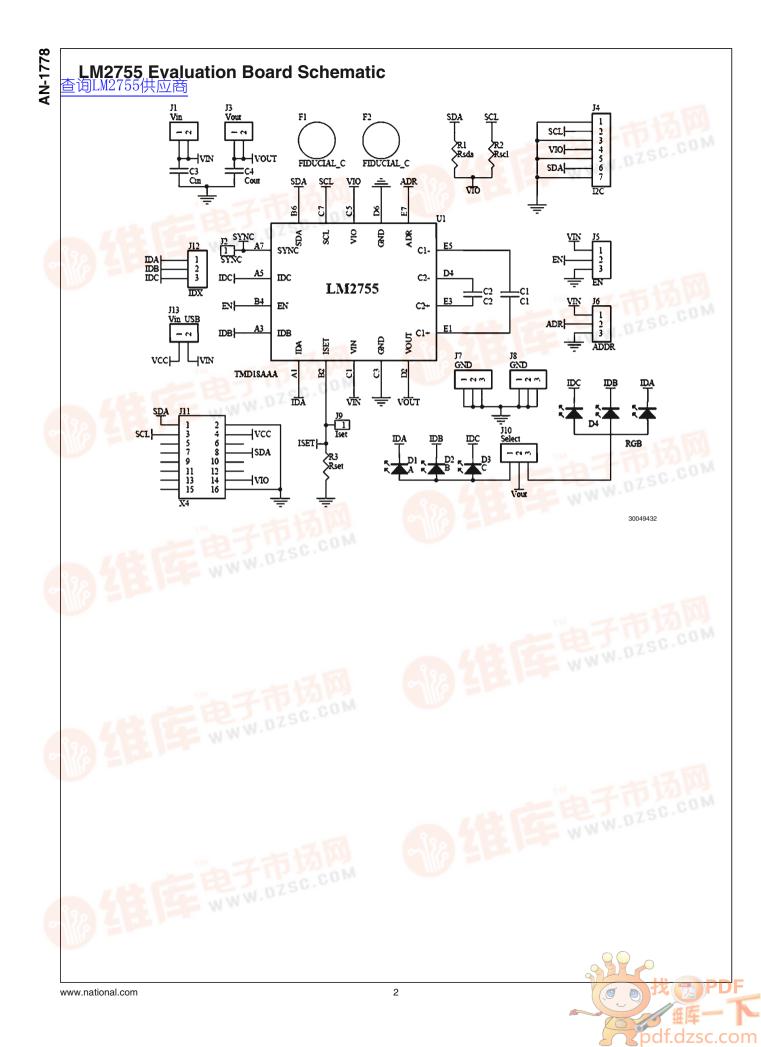

## Board Operation 查询LM2755供应商

#### BASIC CONNECTIONS

To operate the LM2755 Charge Pump LED Controller with I2C Compatible Interface in  $\mu$ SMD, connect a supply voltage (2.7V-5.5V) between board connectors VIN and GND and attach an I<sup>2</sup>C interface using one of the methods described in the *EXTERNAL CONTROL INTERFACE SECTION* of this document.

Default Jumper Connections:

- EN: Connects the "+" post to the middle post of the header strip. This connects VIN to the EN pin of the LM2755, enabling the part.

- ADDR: Connects the "-" post to the middle post of the header strip. This selects the I2C chip id to a 0x18 while the "+" sets the I2C chip ID to a 0x67.

- SELECT: This connects POUT to the anodes of the LEDs. Connecting the center post to the LEFT pin connects the individual Red, Green, and Blue LEDs while the RIGHT pin connects the combination RGB LED

- Vin\_USB: Connects the adjustable voltage supply of the USB Docking board to the VIN of the LM2755. If the USB board is not used, this jumper does not need to be placed. If the USB Docking board is going to be used for the I2C interface, but not for VIN, make sure the Vin\_EXT jumper is removed.

With the default jumper connections made, the board will be ready to operate once an input voltage and an I2C interface generator (external or USB docking board) are connected.

#### **HWEN Pin**

The LM2755 has a hardware enable/reset pin (HWEN) that allows the device to be disabled by an external controller without requiring an I<sup>2</sup>C write command. Under normal operation, the HWEN pin should be held high (logic '1') to prevent an unwanted reset. When the HWEN is driven low (logic '0'), all internal control registers reset to the default states and the part becomes disabled. Please see the *Electrical Characteristics* section of the datasheet for required voltage thresholds.

#### SYNC Pin

The SYNC pin allows the LM2755 to use an external clock to generate the timing within. This allows the LM2755's currentsinks to pulse-width modulate (PWM) and transition at a user controlled frequency. The PWM frequency and the step-time increment can be set by feeding a clock signal into the sync pin and enabling bit '6' in the general purpose register (See the I2C Compatible Interface section for more details.). The maximum frequency allowed to ensure current level accuracy is 1MHz. This external clock is divided down by 32x to create the minimum time-step and PWM frequency. For a 1MHz external clock, the PWM frequency becomes 31.25KHz and the minimum step time becomes 32 µseconds. If not used, it is recommended that the SYNC pin be tied to ground.

#### ADDR Pin

The ADDR pin allows the user to chose between two different I2C chip addresses for the LM2755. Tying the ADDR pin high sets the chip address to hex 67 (0x67 or 67h), while tying the ADDR pin low sets the chip address to hex 18(0x18 or 18h). This feature allows multiple LM2755's to be used within a system in addition to providing flexibility in the event another chip in the system has a chip address similar to the default LM2755 address (0x18).

#### EXTERNAL CONTROL INTERFACE CONNECTION

The LM2755 Evaluation Board provides two ways to connect an I<sup>2</sup>C compatible interface to the LM2755 IC. The first method to connect the interface is through a set of connectors on the bottom of the evaluation board that allow the board to plug into National's USB interface board directly. The second method of interface connection is through a header strip located on the left hand side of the evaluation board. There are pins available to connect VIO (contoller reference voltage), SCL (Interface Clock Line), and SDIO (Interface Data Line) each separated by a ground pin. The evaluation board has two external pull-ups that connect both SCL and SDIO to VIO to compliment the open drain inputs found on the LM2755. The *OPERATION DESCRIPTION* section of this application note describes the internal registers and I<sup>2</sup>C compatible interface in greater detail.

#### **OPERATION DESCRIPTION**

#### **Application Information**

#### SETTING FULL-SCALE LED CURRENT

The current through the LEDs connected to D1, D2 and D3 can be set to a desired level simply by connecting an appropriately sized resistor ( $R_{SET}$ ) between the  $I_{SET}$  pin of the LM2755 and GND. The LED currents are proportional to the current that flows through the  $I_{SET}$  pin and are a factor of 200 times greater than the  $I_{SET}$  currents. The feedback loop of the internal amplifier sets the voltage of the  $I_{SET}$  pin to 1.25V (typ.). The statement above is simplified in the equation below:

#### $I_{Dx (Full-Scale)} = 200 \times (V_{ISET} / R_{SET})$

Please refer to the I<sup>2</sup>C Compatible Interface section of this datasheet for detailed instructions on how to adjust the brightness control registers.

#### BRIGHTNESS LEVEL CONTROL

Once the desired  $R_{SET}$  value has been chosen, the LM2755 has the ability to internally dim the LEDs by modulating the currents with an internally set 20kHz PWM signal. The PWM duty cycle percentage is independently set for each LED through the I<sup>2</sup>C compatible interface. The 32 brightness levels follow a exponentially increasing pattern rather than a linearly increasing one in order to better match the human eyes response to changing brightness. The brightness level response is modeled in the following equations.:

$$I_{Dx LOW} = (0.9)^{(31-n_{LOW})} \times I_{Dx Fullscale}$$

$$I_{Dx HIGH} = (0.9)^{(31-n_{HIGH})} \times I_{Dx Fullscale}$$

$n_{HGH}$  and  $n_{LOW}$  are numbers between 0 and 31 stored in the brightness level registers. When the waveform enable bits are set to '1',  $n_{HIGH}$  and  $n_{LOW}$  are the brightness level boundries. These equations apply to all Dx outputs and their corresponding registers. A '0' code in the brightness control register sets the current to an "off-state" (0mA).

#### TIME STEP CONTROL

Bit 0-Bit 2: The value of the 3 bits is equal to N, which is used in the timing control equations.  $0 \le N \le 7$ . The minimum internal time step (N=0) is 50µs. Setting the time-step to N=7 results in a minimum time step of 400µsec. Time step =  $50µsec \times (N+1)$

Bit 3-Bit 7: Not used

#### DELAY CONTROL

The LM2755 allows the programmed current waveform on each diode pin to independantly start with a delay upon en-

www.national.com

AN-1778

abling the waveform dimming bits in the general purpose register.7 There are 256 delay levels available. The delay time set by the following equation:

$t_{delay} = N \times n_{delay}$  n\_{delay} is stored in the Dx delay registers and N is stored in the Time Step Control register.

By default,  $n_{delay} = 0$  with a range of  $0 \le n_{delay} \le 255$ .

#### TIMING CONTROL

T<sub>PWM INTERNAL</sub> =50µs, N is a value stored in the Time Step register, and  $n_{Trise}$   $n_{Tfall}$ ,  $n_{Thigh}$ ,  $n_{Tlow}$  are numbers between 0 and 255, stored in the timing control registers. The durations of the rise, high, fall and low times are given by:

$t_{rise/tall Total} = t_{PWM INTERNAL} \times 2^{N} \times (n_{high} - n_{low}) \times n_{Trise/fall}$ where  $0 \le n_{Trise/fall} \le 255$

$t_{rise \text{ or fall Total}} = 50 \mu s x (n_{high}-n_{low}) \text{ when } n_{Trise/fall} = 0$

$t_{high or low} = t_{PWM INTERNAL} \times 2^N \times (n_{high/low} + 1)$ where  $0 \le n_{\text{Thigh/low}} \le 255$

#### SYNC PIN TIMING CONTROL

It is possible to replace the internal clock with an external one placed on the external SYNC pin. Writing a '1' to bit6 in the general purpose register switches the system clock from being internally generated to externally generated. The period of the PWM modulating signal becomes:

#### $t_{PWM} = t_{SYNC} / 32$

The maximum recommended SYNC frequency is 1MHz. This frequency yields a PWM frequency of 31.25KHz and the minimum step time of 32 µsec.

## I<sup>2</sup>C Compatible Interface

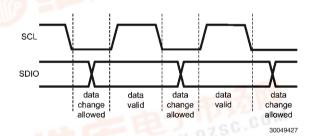

#### DATA VALIDITY

The data on SDIO line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

FIGURE 1. Data Validity Diagram

A pull-up resistor between VIO and SDIO must be greater than [ $(VIO-V_{OI})/3mA$ ] to meet the V<sub>OI</sub> requirement on SDIO. Using a larger pull-up resistor results in lower switching current with slower edges, while using a smaller pull-up results in higher switching currents with faster edges.

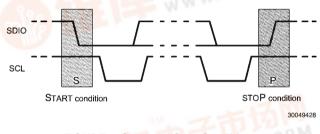

#### START AND STOP CONDITIONS

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as SDIO signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDIO transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I2C bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise. The data on SDIO line must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when CLK is LOW.

FIGURE 2. Start and Stop Conditions

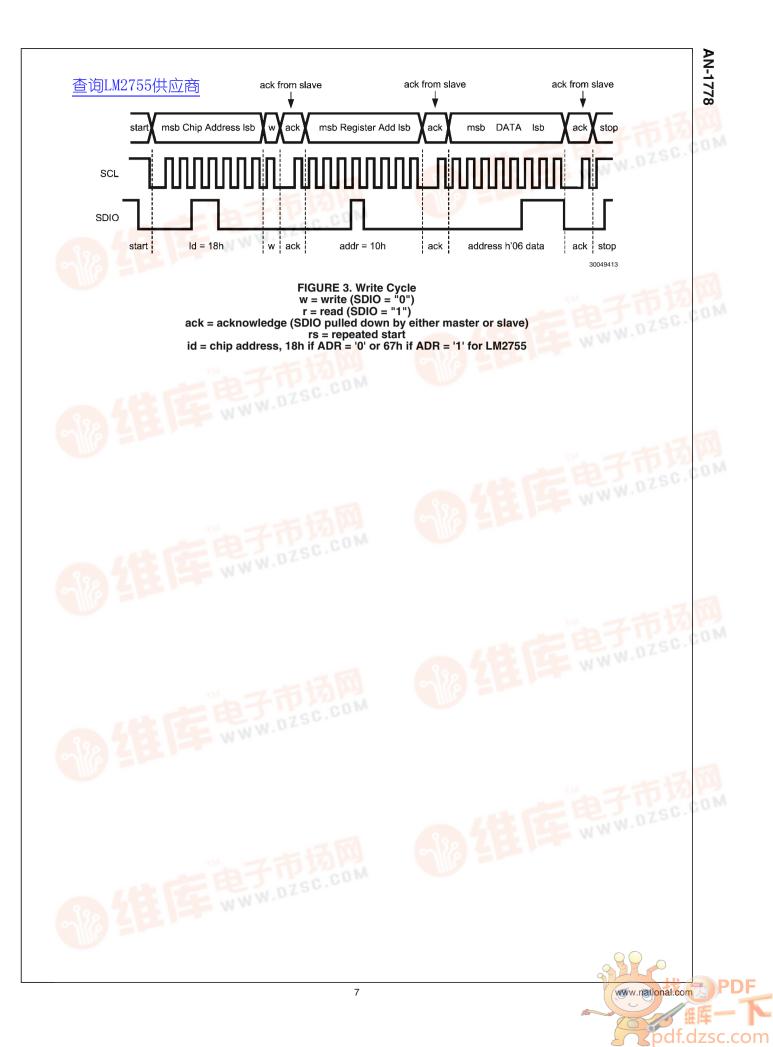

#### TRANSFERING DATA

Every byte put on the SDIO line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDIO line (HIGH) during the acknowledge clock pulse. The LM2755 pulls down the SDIO line during the 9th clock pulse, signifying an acknowledge. The LM2755 generates an acknowledge after each byte has been received

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM2755 address is 18h is ADR is tied low and 67h if ADR is tied high . For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

## I<sup>2</sup>C COMPATIBLE CHIP ADDRESS

her wip address top M2755 is 0011000 (0x18) when ADDR = '0' or 1100111(0x67) when ADR = '1'.

FIGURE 4.

#### **INTERNAL REGISTERS OF LM2755**

| Register Name                             | Internal Hex<br>Address | Power On Value |  |

|-------------------------------------------|-------------------------|----------------|--|

| General Purpose                           | x10                     | 0000 0000      |  |

| Time Step                                 | x20                     | 1000 1000      |  |

| D1 High Level                             | xA9                     | 1110 0000      |  |

| D1 Low Level                              | xA8                     | 1110 0000      |  |

| D1 Delay: t <sub>delay</sub>              | xA1                     | 0000 0000      |  |

| D1 Ramp-Up Step Time: t <sub>rise</sub>   | xA5                     | 0000 0000      |  |

| D1 Time High: t <sub>high</sub>           | xA3                     | 0000 0000      |  |

| D1 Ramp-Down Step Time: t <sub>fall</sub> | xA4                     | 0000 0000      |  |

| D1 Timing: t <sub>low</sub>               | xA2                     | 0000 0000      |  |

| D2 High Level                             | xB9                     | 1110 0000      |  |

| D2 Low Level                              | xB8                     | 1110 0000      |  |

| D2 Delay: tdelay                          | xB1                     | 0000 0000      |  |

| D2 Ramp-Up Step Time: t <sub>rise</sub>   | xB5                     | 0000 0000      |  |

| D2 Time High: t <sub>high</sub>           | xB3                     | 0000 0000      |  |

| D2 Ramp-Down Step Time: t <sub>fall</sub> | xB4                     | 0000 0000      |  |

| D2 Timing: t <sub>low</sub>               | xB2                     | 0000 0000      |  |

| D3 High Level                             | xC9                     | 1110 0000      |  |

| D3 Low Level                              | xC8                     | 1110 0000      |  |

| D3 Delay: tdelay                          | xC1                     | 0000 0000      |  |

| D3 Ramp-Up Step Time: t <sub>rise</sub>   | xC5                     | 0000 0000      |  |

| D3 Time High: t <sub>high</sub>           | xC3                     | 0000 0000      |  |

| D3 Ramp-Down Step Time: t <sub>fall</sub> | xC4                     | 0000 0000      |  |

| D3 Timing: t <sub>low</sub>               | xC2                     | 0000 0000      |  |

### **General Purpose Register Description**

- Bit 0: enable output D1 with high current level. ٠

- Bit 1: enable output D2 with high current level.

- Bit 2: enable output D3 with high current level. •

- Bit 3: enable dimming waveform on output D1.

- Bit 4: enable dimming waveform on output D2.

- Bit 5: enable dimming waveform on output D3.

- Bit 6: enable external clock. '1' = External Clock Sync, '0' = Internal

- Bit 7: If Bit 7 = 0 the charge pump is powered on before any dim oled. If Bit7 = 1 the dimming waveform can be enabled before charge pump is powered on.

| rnal Clock Used        |

|------------------------|

| nming waveform is enab |

|                        |

0

zsc.com

# Software Interface Information

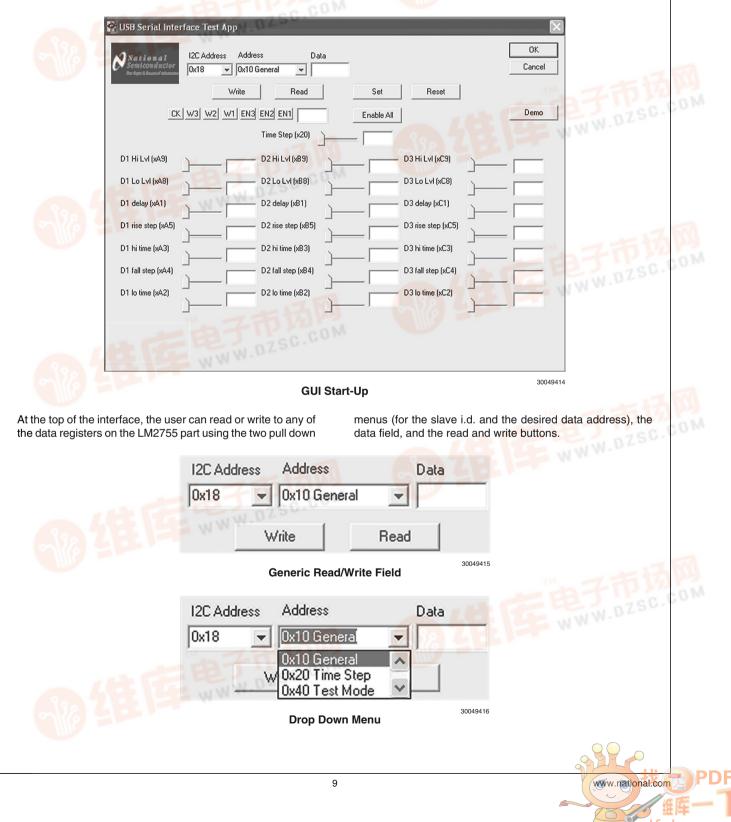

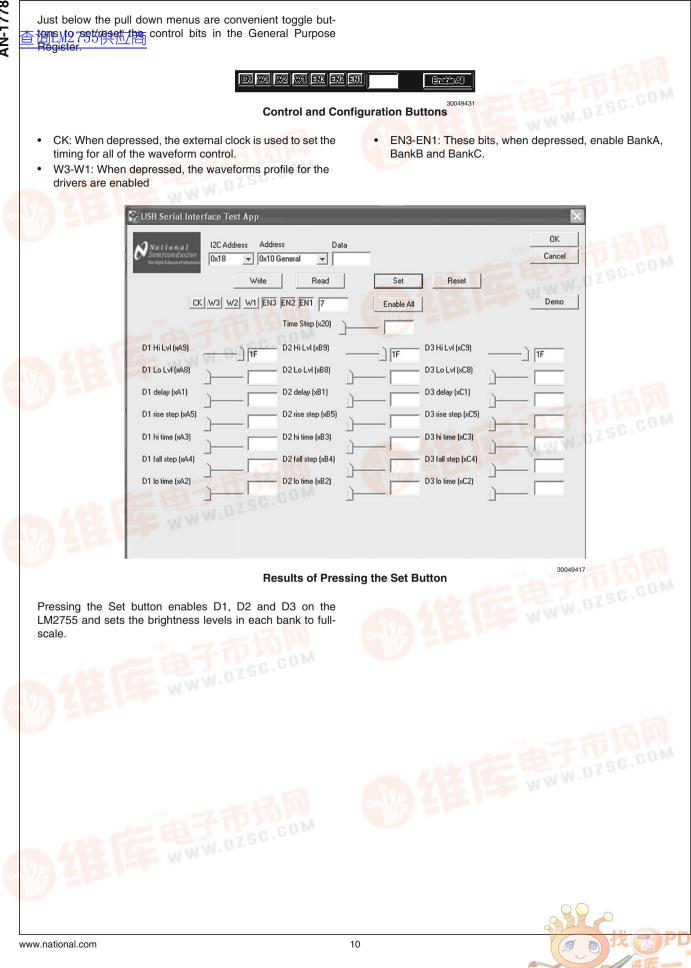

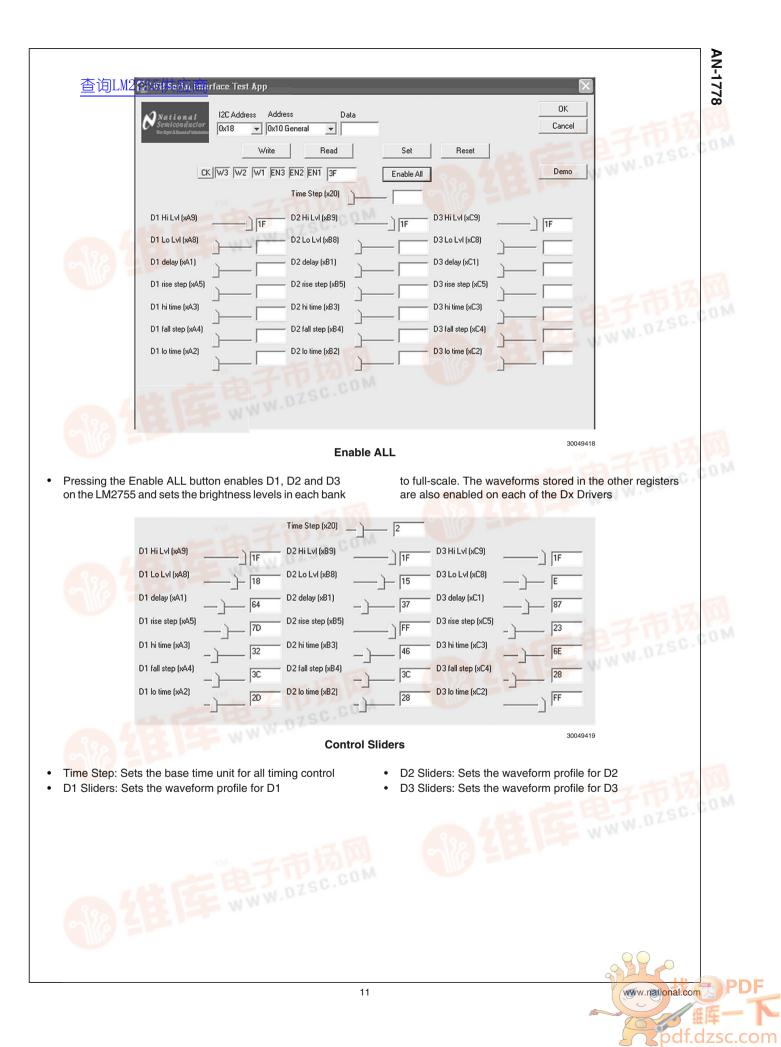

In order of uity evaluate the M2755 part, an "I<sup>2</sup>C Compatible" interface must be used for any functionality to occur. A detailed description of the interface control is described in the LM2755 datasheet.

National has created an I<sup>2</sup>C compatible interface generation program and USB docking board that can help exercise the part in a simple way. Contained in this document is a description of how to use the USB docking board and interface software. The LM2755 evaluation board has the means to "plug into" the USB docking board. The USB docking board can provide all of the control signals and power required to operate the evaluation board. A standard USB cable must be connected to the board from a PC.

AN-1778

The I<sup>2</sup>C compatible interface program provides all of the control that the LM2755 part requires. For proper operation, the USB docking board should be plugged into the PC before the interface program is opened. Once connected, and the program is executed, a basic interface window will open.

zsc.com

AN-1778

AN-1778

dzsc.com

# 查询LM2755供应商

# Notes

| Pi                             | roducts                      | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         | - BTIP                         |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         | WW.DZSU                        |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

AN-1778

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

0

www.national.com