### LM1771 and LM3880 Based FPGA Power Supply **Reference Design**

#### Introduction

The Xilinx Virtex™-5 FPGA is a family of advanced FPGAs that combine various platforms and speed grades enabling a high level of performance and flexibility<sup>[1-3]</sup>. This application note discusses the Virtex-5 FPGA power supply prerequisites in terms of the multiple voltage rail and current level requirements, output sequencing, and startup characteristics. Exemplarily, a power supply solution based on National Semiconductor LM1771 power supply controller and LM3880 sequencer is designed that combines high performance, power density and efficiency.

#### **FPGA Power Supply Requirements**

Nanoscale process technology used in the Virtex-5 FPGA enables the dynamic power dissipation (CV<sup>2</sup>f) to be reduced by means of lower parasitic capacitances and lower core voltage rail<sup>[6]</sup>, V<sub>CCINT</sub>. Static power dissipation modes, via subthreshold and gate leakage[5,6], have been minimized by adding a third gate oxide thickness to the process. Fortunately, this is a net benefit in terms of the current levels demanded from the power supply solution.

The Virtex-5 generally requires at least three different voltage rails. The recommended core voltage is 1.0V ±5%. The I/O bank voltage supply, V<sub>CCO</sub>, can vary from 1.14V to 3.45V depending on the I/O standard being implemented<sup>[2]</sup>. Thus, V<sub>CCO</sub> voltage rails of 1.2V, 1.5V, 1.8V, 2.5V and 3.3V are feaNational Semiconductor Application Note 1677 Tim Hegarty January 14, 2008

sible. Consequently, the overall power dissipation is application dependent and conditioned by ratios of static and dynamic power loss components. Additionally, Xilinx defines an auxiliary voltage, V<sub>CCAUX</sub>, which is recommended to operate at 2.5V ±5% to supply FPGA clock rails related to the clock management tile blocks, e.g. the digital clock manager (DCM) resources<sup>[2]</sup>.

The power-on sequence recommended by Xilinx is V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub>. Although any monotonic power-on sequence is tolerated, use of the recommended sequence allows Xilinx to define the minimum inrush current required from the FPGA core, auxiliary and I/O supplies - denoted ICCINT-MIN, IAUXMIN, and ICCOMIN, respectively - to ensure correct power-on and configuration. It is possible that the power supplies must transiently handle larger currents during startup with relatively lower static and dynamic current levels during normal operation. The power-up ramp time specification normally defined as the time from 10% to 90% of the nominal output voltage during startup - for all three voltage rails is 0.2 ms to 50.0 ms.

Note that the steady-state power supply demand can be derived pre-implementation by use of the Xilinx XPower Estimator (XPE) power estimation spreadsheet tool<sup>[4]</sup>. The junction temperature, frequency, device utilization and I/O types are included as parameters in this calculation so that designers can predict the power consumed by their system and design the power supply accordingly.

#### FPGA Power Supply Design Outline

The proposed FPGA power supply solution uses three National Semiconductor LM1771<sup>[9]</sup> PWM buck controllers with power-up and power-down of the individual voltage rails sequenced by a National Semiconductor LM3880<sup>[10]</sup> power sequencer.

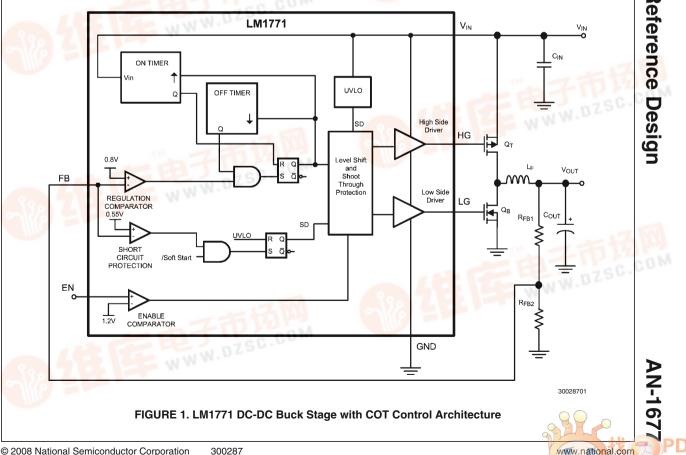

The LM1771 block diagram with typical external connected components is presented in Figure 1. The LM1771 is an efficient buck converter switching controller available in MSOP-8 and LLP-6 packages and capable of converting an input voltage between 2.8V and 5.5V into a regulated output voltage as low as 0.8V. It drives an external high side PFET and low side NFET complementarily with duty cycle D and (1-D) respectively at switching frequency, fs. A constant on-time (COT) control architecture is utilized which eliminates the need for an error amplifier and external compensation components. Thus, extremely fast transient load current response is possible. Additionally, the LM1771 features a precision enable pin to facilitate supply sequencing and/or flexibility in setting the operating input voltage range of the power supply. Three LM1771 timing options - designated S, T and U in the part numbering specification - are available which translate to three possible switching frequency options for a given output voltage. For a given timing option, the switching frequency is largely independent of input voltage level as the controller input feed-forward feature varies high side switch on-time as a function of input voltage to maintain constant volt-seconds at the switch node.

By virtue of the small-sized package options, the LM1771 allows for a complete power supply design to occupy very little PCB real estate without sacrificing efficiency.

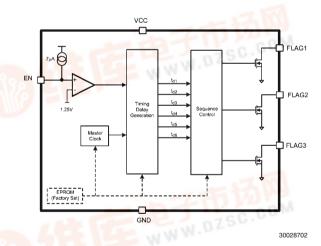

#### FIGURE 2. LM3880 Sequencer Block Diagram

The LM3880 sequencer block diagram is presented in Figure 2. It is available in a SOT23-6 package and it has three opendrain flag outputs which allow control of the three LM1771 enable pins. Upon enabling the LM3880, the three output flags will sequentially release, after individual time delays, permitting the connected power supplies to startup. The output flags will follow a reverse sequence during power down to avoid latch conditions. Standard timing options of 10 ms, 30 ms, 60 ms and 120 ms are available. Further, the LM3880 is factory programmable to attain customized timing options combined with six possible power down sequences. The LM3880 operating supply voltage range, 2.7V to 5.5V, is compatible with that of the LM1771 controller.

#### FPGA Power Supply Implementation

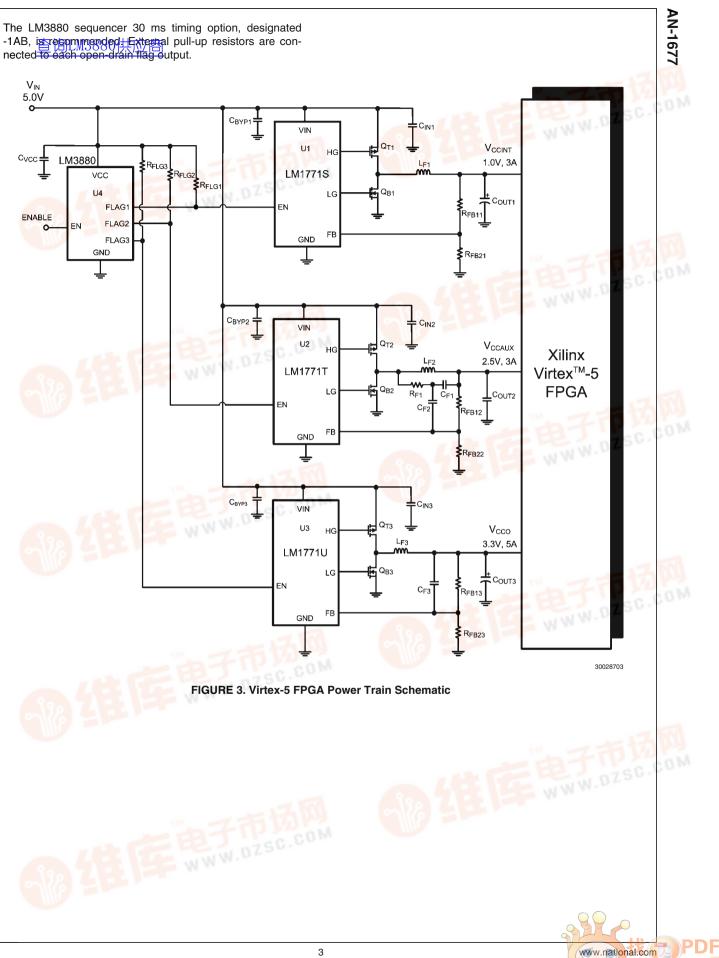

The power train schematic based on the LM1771 controller and LM3880 sequencer is shown in Figure 3. The associated bill of materials is presented in Table 1.

The LM1771 based application board was designed with the input voltage nominally set at 5.0V, but can theoretically be varied over the entire operating range of the LM1771 (2.8V-5.5V). The entire power supply occupies less than 2.0" x 2.0" on a two layer FR4 PCB. For this design, the three buck regulator channels are capable of delivering maximum continuous load currents of 5A, 3A and 3A ( $I_{CCO}$ ,  $I_{CCAUX}$ , and  $I_{CCINT}$ , respectively).

The I/O voltage is set at 3.3V, but can be easily varied by modifying one of the feedback resistors, RFB13 or RFB23. In the case of a buck converter to maintain regulation at 3.3V, the input voltage should not be allowed to fall below approximately 3.6V. The core and auxiliary rails are set at 1.0V and 2.5V, respectively, according to the FPGA specification.

The core, auxiliary and I/O regulators use the LM1771S (U1), LM1771T (U2) and LM1771U (U3) controllers which yield switching frequencies of 606 kHz, 758 kHz and 500 kHz, respectively. Each supply has its own input filter capacitor located as close as possible to the p-channel and n-channel buck and synchronous power FETs. Additionally, a small 0603 input bypass capacitor is placed local to each LM1771 IC.

The output filter capacitances on the core and I/O supplies are tantalum based and chosen to present the necessary ESR to maintain sufficient in-phase voltage ripple at the FB pin<sup>[9, 11, 12]</sup>. In the case of the I/O channel, feed-forward capacitor C<sub>F3</sub> increases the magnitude of the FB ripple seen by its LM1771. This capacitor is not used in the core channel feedback circuit as it has minimal effect when the output voltage is close to the FB pin voltage. The output filter capacitance of the auxiliary voltage regulator is ceramic based to minimize the noise level of this rail. A current sense network comprising resistor R<sub>F1</sub> and capacitor C<sub>F1</sub> across filter inductor L<sub>E2</sub> creates a triangular voltage waveform which is ac coupled by capacitor C<sub>F2</sub> to the FB node<sup>[9]</sup>. A comprehensive discussion of the selection process for these components is available in National Semiconductor Application Note AN-1481.

This circuit can also be utilized in the core and I/O channels if tantalum capacitors are deemed unsuitable and/or low ESR ceramic capacitors are required either local to the regulator or downstream adjacent to the FPGA.

The filter inductors are designed for large current handling capability with low DC and AC effective resistance to maximize efficiency. The inductance value is conditioned to attain peak-to-peak ripple current of approximately 30% of the rated load current<sup>[13]</sup>. Further, the inductors chosen boast a relatively soft inductance-current saturation characteristic. This represents an ideal component characteristic when faced with short duration high current transient events in excess of the rated load current.

TSOP6 packages are used for the power FETs in the auxiliary rail supply while SO-8 FETs are implemented for the I/O channel regulator. The core voltage supply, given its low duty cycle operating point, has a high side TSOP6 FET,  $Q_{T1}$ , and a low side SO-8 FET,  $Q_{B1}$ . Note that by employing more thermally efficient packages and/or lower on-resistance switches, the possibility exists to increase maximum load current capability and thermal performance.

f.dzsc.com

# Virtex-5 LM1771 Based Power Supply Bill of Materials

| Ref. Des.         | Description                                   | Part Number        | Manufacturer           |

|-------------------|-----------------------------------------------|--------------------|------------------------|

| U1                | LM1771S, 500 ns, PWM Controller               | LM1771SMMX         | National Semiconductor |

| U2                | LM1771T, 1000 ns, PWM Controller              | LM1771TMMX         | National Semiconductor |

| U3                | LM1771U, 2000 ns, PWM Controller              | LM1771UMMX         | National Semiconductor |

| U4                | LM3880 Power Sequencer                        | LM3880MFX-1AB      | National Semiconductor |

| Q <sub>T1</sub>   | High Side PFET, TSOP6                         | Si3867DV           | Vishay Siliconix       |

| Q <sub>B1</sub>   | Low Side NFET, SO-8                           | Si4394BDY          | Vishay Siliconix       |

| Q <sub>T2</sub>   | High Side PFET, TSOP6                         | Si3867DV           | Vishay Siliconix       |

| Q <sub>B2</sub>   | Low Side NFET, TSOP6                          | Si3460DV           | Vishay Siliconix       |

| Q <sub>T3</sub>   | High Side PFET, SO-8                          | Si9424BDY          | Vishay Siliconix       |

| Q <sub>B3</sub>   | Low Side NFET, SO-8                           | Si4394BDY          | Vishay Siliconix       |

| C <sub>IN1</sub>  | 22 µF 6.3V X5R Ceramic Capacitor, 0805        | C2012X5R0J226M     | TDK                    |

| C <sub>IN2</sub>  | 22 µF 6.3V X5R Ceramic Capacitor, 0805        | C2012X5R0J226M     | TDK                    |

| C <sub>IN3</sub>  | 47 μF 6.3V X5R Ceramic Capacitor, 1206        | C3216X5R0J476M     | TDK                    |

| C <sub>BYP1</sub> | 1 μF 10V X5R Ceramic Capacitor, 0603          | C1608X5R1A105M     | TDK                    |

| C <sub>BYP2</sub> | 1 µF 10V X5R Ceramic Capacitor, 0603          | C1608X5R1A105M     | TDK                    |

| C <sub>BYP3</sub> | 1 μF 10V X5R Ceramic Capacitor, 0603          | C1608X5R1A105M     | TDK                    |

| C <sub>OUT1</sub> | 150 μF 6.3V Tantalum Capacitor, 50 mΩ, D-Case | TPSD157M006R0050   | AVX                    |

| C <sub>OUT2</sub> | 100 μF 6.3V X5R Ceramic Capacitor, 1210       | C3225X5R0J107M     | TDK                    |

| C <sub>OUT3</sub> | 150 μF 6.3V Tantalum Capacitor, 50 mΩ, D-Case | TPSD157M006R0050   | AVX                    |

| L <sub>F1</sub>   | 2.2 µH Inductor, 6.86mm x 6.47mm x 3.0mm      | IHLP2525CZER2R2M01 | Vishay Dale            |

| L <sub>F2</sub>   | 2.2 µH Inductor, 6.86mm x 6.47mm x 3.0mm      | IHLP2525CZER2R2M01 | Vishay Dale            |

| L <sub>F3</sub>   | 2.2 μH Inductor, 11.5mm x 10.3mm x 4.0mm      | IHLP4040DZER2R0M11 | Vishay Dale            |

| R <sub>FB11</sub> | 2.32 kΩ Resistor, 0603                        | CRCW06032321F      | Vishay                 |

| R <sub>FB21</sub> | 10 kΩ Resistor, 0603                          | CRCW06031002F      | Vishay                 |

| R <sub>FB12</sub> | 21 kΩ Resistor, 0603                          | CRCW06032102F      | Vishay                 |

| R <sub>FB22</sub> | 10 kΩ Resistor, 0603                          | CRCW06031002F      | Vishay                 |

| R <sub>FB13</sub> | 30.9kΩ Resistor, 0603                         | CRCW06033092F      | Vishay                 |

| R <sub>FB23</sub> | 10 kΩ Resistor, 0603                          | CRCW06031002F      | Vishay                 |

| C <sub>F1</sub>   | 1 nF Capacitor, X7R, 0603                     | VJ0603102KXXA      | Vishay                 |

| C <sub>F2</sub>   | 22 nF Capacitor, X7R, 0603                    | VJ0603223KXXA      | Vishay                 |

| C <sub>F3</sub>   | 1 nF Capacitor, X7R, 0603                     | VJ0603102KXXA      | Vishay                 |

| C <sub>VCC</sub>  | 1 µF 10V Ceramic Capacitor, 0603              | C1608X5R1A105M     | TDK                    |

| R <sub>F1</sub>   | 49.9 kΩ Resistor, 0603                        | CRCW06034992F      | Vishay                 |

| R <sub>FLG1</sub> | 49.9 kΩ Resistor, 0603                        | CRCW06034992F      | Vishay                 |

| R <sub>FLG2</sub> | 49.9 kΩ Resistor, 0603                        | CRCW06034992F      | Vishay                 |

| R <sub>FLG3</sub> | 49.9 kΩ Resistor, 0603                        | CRCW06034992F      | Vishay                 |

| . 200             |                                               |                    | WWW.DZSC.COM           |

00

zsc.com

#### FPGA Power Supply performance

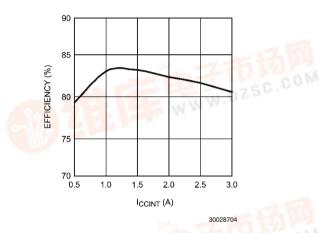

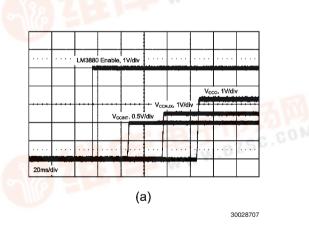

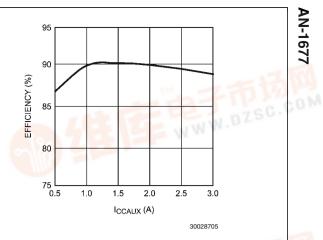

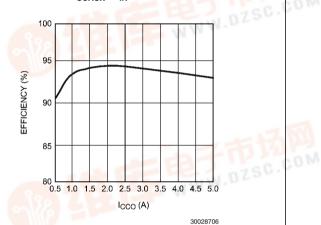

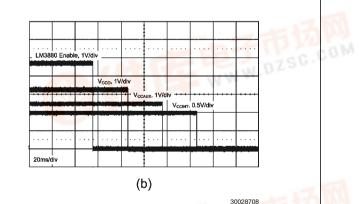

查询LM3880供应商"· channels, operating independently at 5V input, as a function of current are shown in Figure 4, Figure 5 and Figure 6, respectively. Likewise, typical full load efficiencies are 80.6%, 89.1% and 93.2%. Global conversion efficiency with the three regulators operating at full load, including LM3880 related bias power, is 90.5%. This constitutes a total output power of 27W with 2.85W dissipation. When the LM3880 is disabled (EN pin less than 1.25V), the total quiescent current is approximately 1.5mA. Finally, Figure 7(a) and (b) demonstrate the sequenced monotonic power up and power down characteristics of each voltage rail as controlled by the LM3880. The time delays between enable transitioning and subsequent output voltages in regulation - defined as 90% V<sub>EN-</sub> ABLE to 90% V<sub>CCINT</sub>, or 90% V<sub>CCINT</sub> to 90% V<sub>CCAUX</sub>, etc. - are 30 ms.

FIGURE 5. Auxiliary Channel Efficiency vs. Current, I<sub>CCAUX</sub>; V<sub>IN</sub> = 5.0V

# AN-1677

#### References

fication, DS100 (v3.0) February 2, 2007, direct.xilinx.com/ bvdocs/publications/ds100.pdf

[2] Xilinx Virtex-5 Datasheet: DC and Switching Characteristics, Advance Product Specification, DS202 (v3.0) February 2, 2007, direct.xilinx.com/bvdocs/publications/ds202.pdf

[3] Xilinx Virtex-5 User Guide, Advance Product Specification, UG190 (v3.0) February 2, 2007 direct.xilinx.com/bvdocs/ userguides/ug190.pdf

[4] Xilinx Virtex-5 XPower Estimator (XPE) 9.1, Spreadsheet Power Estimation Tool, www.xilinx.com/products/design\_resources/power\_central/index.htm

[5] Xilinx Application Note XAPP158, Powering Virtex FPGAs, www.xilinx.com/products/design\_resources/power\_central/ index.htm

[6] Xilinx White Paper WP246 (v1.2) "Power Consumption in 65nm FPGAs", February 1, 2007 direct.xilinx.com/bvdocs/ whitepapers/wp246.pdf

[7] National Semiconductor, Power Recommendations for Xilinx FPGAs, www.national.com/xilinx/power.html [8] National Semiconductor, Design Guide for FPGAs, www.national.com/xilinx/files/

national\_xilinx\_design\_guide.pdf

[9] National Semiconductor, LM1771 Datasheet, www.national.com/pf/LM/LM1771.html

[10] National Semiconductor, LM3880 Datasheet, www.national.com/pf/LM/LM3880.html

[11] National Semiconductor, AN-1414: Application Note 1414 LM1770 Design Reference, www.national.com/an/AN/ AN-1414.pdf

[12] National Semiconductor, AN-1477: Application Note 1477 LM1771 Evaluation Board, www.national.com/an/AN/ AN-1477.pdf

[13] National Semiconductor, AN-1197: Application Note 1197 Selecting Inductors for Buck Converters, www.national.com/an/AN/AN-1197.pdf

[14] National Semiconductor, AN-1481: Application Note 1481 Controlling Output Ripple and Achieving ESR Independence in Constant On-Time (COT) Regulator Designs, www.national.com/an/AN/AN-1481.pdf

zsc.com

www.national.com

#### 查询LM3880供应商

## Notes

| Р                              | roducts                      | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   | (m/6 1-1                |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         | 1                              |

| Temperature Sensors            | www.national.com/tempsensors |                         | ~~ <b>Z</b> 70 14              |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         | 2256.                          |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

N

AN-1677

National Semiconductor Americas Technical Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

O 0

www.national.com