### LP5551 Evaluation Board

National Semiconductor Application Note 1467 Mark Hartman June 2007

#### LP5551 Overview

The LP5551 is a PWI 1.0 compliant Energy Management Unit for reducing power consumption of stand-alone mobile phone processors such as base-band or applications processors.

The LP5551 contains two advanced, digitally controlled switching regulators for supplying variable voltage to processor core and memory. Two regulators provide P- and N- well biasing for threshold scaling applications. The device also integrates 4 programmable LDO-regulators for powering I/O, PLLs and maintaining memory retention in sleep-mode.

The device is controlled via the PWI 1.0 open-standard interface. The LP5551 operates cooperatively with PowerWise™ technology compatible processors to optimize supply voltages adaptively over process and temperature variations or dynamically using frequency/voltage pre-characterized lookup tables and provides P- and N-well biasing for threshold scaling.

#### **Evaluation Board Overview**

The LP5551 Evaluation Board can be operated standalone or from a motherboard such as the PowerWise Evaluation Kit (PEK) or USB interface board.

The evaluation board ships with the USB interface board and a graphical user interface (GUI) to easily control the features of the LP5551 from a PC. See AN-1535 for information on the GUI.

The LP5551 is configured to operate with the following conditions:

| Parameter | Default                | <b>Programming</b>        | I <sub>OUT</sub> |

|-----------|------------------------|---------------------------|------------------|

| 9.0       | Voltage                | Range                     |                  |

| VBATT     | 3.6 V                  |                           |                  |

| VAVS      | 1.2 V                  | 0.6 - 1.2 V               | 300 mA           |

| VDVS      | 1.2 V                  | 0.6 - 1.2 V               | 300 mA           |

| VO1       | 1.2 V                  | 0.7 - 2.2 V               | 100 mA           |

| VO2       | 3.3 V                  | 1.5 - 3.3 V               | 250 mA           |

| VO3       | Tracks                 | V <sub>AVS</sub> + 0.04 V | 50 mA            |

|           | V <sub>AVS</sub>       |                           | LD N             |

|           | (Active                |                           | DZSC             |

| 0         | State)                 | WWW                       |                  |

| ~ 3       | 1.2 V                  | 0.6 - 1.35 V              | 5 mA             |

|           | (Sleep                 |                           |                  |

| 1111      | State)                 |                           |                  |

| VO4       | 3.3 V                  | 1.5 - 3.3 V               | 250 mA           |

| VPWELL    | 0 V                    | -1 ~ 0.3 V                | 20 uA            |

| VNWELL    | V <sub>AVS</sub> + 0 V | VAVS + (-0.3 ~ 1) V       | 7 mA             |

Note that all the regulators can be programmed to different output voltages once the part starts up.

20190901

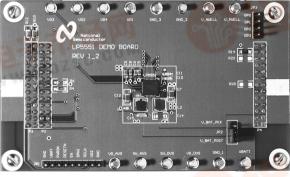

FIGURE 1. LP5551 Evaluation Board

The LP5551 can be powered externally (bench supply), or from the PEK or USB interface board (depending on motherboard being the language of the set the appropriate power source.

| JUMPER | PURPOSE                 | NOTE                               |  |

|--------|-------------------------|------------------------------------|--|

| JP2    | Input voltage selection | V_BAT_POST: LP5551 powered from    |  |

|        |                         | external supply                    |  |

|        |                         | V_BAT_PEK: LP5551 powered from PEK |  |

|        | 990 74 =                | or from USB interface board        |  |

# Connecting the LP5551 to the USB2PWI interface board

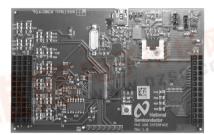

The LP5551 evaluation board can be connected to the US-B2PWI interface board for convenient control of the PWI and all the LP5551 functions via a GUI. *Figure 2* shows the US-B2PWI interface board. See AN-1535 for instructions on how to use the GUI.

20100003

FIGURE 2. USB Interface Board

# Connecting the LP5551 Evaluation Board to an External Controller

Jumper J1 allows for external control of the PWI, used to communicate with the LP5551. It is a SIP-9 footprint. The pin list of J1 is shown in Table 1. VBAT and VO2 are provided on J1 as sense outputs to determine the drive levels for the inputs RESETN, EN, SPWI, and SCLK. The external controller should drive EN and RESETN to VBAT and ground, while SPWI and SCLK should be driven between VO2 and ground.

| Pin | Function | Туре         | Description                        |

|-----|----------|--------------|------------------------------------|

| 1   | GND      | GND          | Ground                             |

| 2   | VBAT     | Output       | VBAT Sense                         |

| 3   | PWROK    | Output       | PWROK<br>Sense                     |

| 4   | RESETN   | Input        | VBAT: On<br>GND: RESET<br>LP5551   |

| 5   | EN       | Input        | VBAT: On<br>GND: Disable<br>LP5551 |

| 6   | SPWI     | Input        | PWI Data                           |

| 7   | SCLK *** | Input/Output | PWI Clock                          |

| 8   | VO2      | Output       | VO2 Sense                          |

| 9   | GND      | GND          | Ground                             |

## Connecting the LP5551 Evaluation Board to the PEK

The PEK is designed to quickly and easily control the LP5551 for PowerWise Interface (PWI) compliance testing. *Figure 3* shows the PEK. See the PEK User's Guide for more information.

20190902

FIGURE 3. PowerWise Evaluation Kit (PEK)

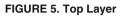

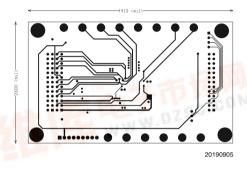

### **PCB Layout Considerations**

The evaluation board layers from top to bottom are:

- 1. Top, component side

- 2. Ground plane

- 3. Power plane

- 4. Bottom

See Figure 5, Figure 6, and Figure 7 for layout diagrams.

For good performance of the circuit, it is essential to place the input and output capacitors very close to the circuit and use wide routing for the traces allowing high currents. Decoupling capacitors should be close to circuit's VIN pins.

Sensitive components should be placed far from those components with high pulsating current.

It's a good practice to minimize high current and switching current paths.

#### LOW DROP OUT (LDO) REGULATORS

Place the filter capacitors very close to the input and output pins. Use large trace width for high current carrying traces and the returns to ground.

#### **BUCK REGULATORS**

Place the supply bypass, filter capacitor, and inductor close together and keep the traces short. The traces between these

www.national.com 2

www.national.com

components carry relatively high switching current and act as antennas, replaying these reduces radiated noise.

Arrange the components so that the switching current loops curl in the same direction.

Connect the buck ground and the ground of the capacitors together using generous component-side copper fill as a pseudo-ground plane. Then connect this back to the general board system ground plane at a single point. Place the pseudo-ground plane below these components and then have it tied to system ground of the output capacitor outside of the current loops. This prevents the switched current from injecting noise into the system ground. These components along with the inductor and output should be placed on the same side of the circuit board, and their connections should be made on the same layer.

Route noise sensitive traces such as the voltage feedback path away from the inductor. This is done by routing it on the bottom layer or by adding a grounded copper area between switching node and feedback path. To reduce noisy traces between the power components, keep any digital lines away from this section. Keep the Feedback node as small as possible so that the ground pin and ground traces will shield it from the SW or buck output.

Use wide traces between the power components and for power connections to the DC-DC converter circuit to reduce voltage errors caused by resistive losses.

For the sense lines, make sure to use a Kelvin contact connection.

# Bill of Materials 查询LP5551供应商

| 到 <u>阿下L9991 并                                 </u> |           | T          |           |               |                           |

|-----------------------------------------------------|-----------|------------|-----------|---------------|---------------------------|

| P/N                                                 | Part Type | Designator | Footprint | Description   | MNF                       |

| VJ0805X7R475MX<br>AA                                | 0.47uF    | C15        | 805       | Capacitor     | Vishay                    |

| D251001501F                                         | 1.5K      | R14        | 1206      | Resistor      | Vishay                    |

| D251001501F                                         | 1.5K      | R13        | 1206      | Resistor      | Vishay                    |

| VJ0805X7R102MX<br>AA                                | 1nF       | C11        | 805       | Capacitor     | Vishay                    |

| VJ0805X7R102MX<br>AA                                | 1nF       | C10        | 805       | Capacitor     | Vishay                    |

| EMK212BJ475MG                                       | 4.7uF     | C5         | 805       | Capacitor     | Taiyo Yuden               |

| EMK212BJ475MG                                       | 4.7uF     | C6         | 805       | Capacitor     | Taiyo Yuden               |

| CRCW12061002F                                       | 10k       | R6         | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R4         | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R2         | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R5         | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R12        | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R7         | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R11        | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R10        | 1206      | Resistor      | Vishay                    |

| CRCW12061002F                                       | 10k       | R9         | 1206      | Resistor      | Vishay                    |

| LMK316BJ226ML                                       | 22 uF     | C14        | 1206      | Capacitor     | Taiyo Yuden               |

| JMK316BJ226KL                                       | 22 uF     | C7         | 805       | Capacitor     | Taiyo Yuden               |

| JMK316BJ226KL                                       | 22 uF     | C12        | 805       | Capacitor     | Taiyo Yuden               |

| LMK212BJ105KG                                       | 1 uF      | C9         | 805       | Capacitor     | Taiyo Yuden               |

| LMK212BJ225KG                                       | 2.2 uF    | C8         | 805       | Capacitor     | Taiyo Yuden               |

| - 11 C                                              | LP5551    | SC.COM     | SQA36A    | PowerWise EMU | National<br>Semiconductor |

| A CHILL                                             | NL        | R22        | 1206      | Resistor      |                           |

| 22 14 - 91-                                         | NL        | R18        | 1206      | Resistor      |                           |

|                                                     | NL        | R20        | 1206      | Resistor      | 7 57                      |

|                                                     | NL        | R21        | 1206      | Resistor —    | TELL LON INS              |

| NR4012T4R7M                                         | 4.7 uH    | L2         | NR4012    | Inductor      | Taiyo Yuden               |

| NR4012T4R7M                                         | 4.7 uH    | L1         | NR4012    | Inductor      | Taiyo Yuden               |

www.national.com 4

www.national.com

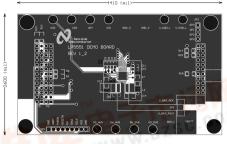

### Layout Diagrams 查询LP5551供应商

20190904

FIGURE 7. Bottom Layer

FIGURE 6. Mid Layer

### **Notes**

AN-1467

≦询LP5551供应商

### **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS, NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center new.feedback@nsc.com Tel: 1-800-272-9959

**National Semiconductor Europe** Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

0