# EM78P5840N /41N/42N 8-Bit Microcontrollers Product

# Product Specification

Doc. Version 1.0

ELAN MICROELECTRONICS CORP. April 2006

**Trademark Acknowledgments:** IBM is a registered trademark and PS/2 is a trademark of IBM. Windows is a trademark of Microsoft Corporation ELAN and ELAN logo *full* are trademarks of ELAN Microelectronics Corporation

# Copyright © 2006 by ELAN Microelectronics Corporation **All Rights Reserved**

Printed in Taiwan

The contents of this specification are subject to change without further notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible for any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising from the use of such information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited. NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESSED WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

# ELAN MICROELECTRONICS CORPORATION

#### **Headquarters:**

No. 12, Innovation Road 1 Hsinchu Science Park Hsinchu, TAIWAN 30077 Tel: +886 3 563-9977 Fax: +886 3 563-9966 http://www.emc.com.tw

#### Europe:

#### Elan Microelectronics Corp. (Europe)

Siewerdtstrasse 105 8050 Zurich, SWITZERLAND Tel: +41 43 299-4060 Fax: +41 43 299-4079 http://www.elan-europe.com

#### Hong Kong: Elan (HK) Microelectronics

Corporation, Ltd.

Rm. 1005B, 10/F Empire Centre 68 Mody Road, Tsimshatsui Kowloon, HONG KONG Tel: +852 2723-3376 Fax: +852 2723-7780 elanhk@emc.com.hk

#### Shenzhen:

#### **Elan Microelectronics** Shenzhen, Ltd.

Shenzhen Hi-Tech Industrial Park Shenzhen, Guandong, CHINA Tel: +86 755 2601-0565 Fax: +86 755 2601-0500

#### USA:

## **Elan Information** Technology Group (U.S.A.)

1821 Saratoga Ave., Suite 250 Saratoga, CA 95070 USA Tel: +1 408 366-8225 Fax: +1 408 366-8220

#### Shanghai:

#### **Elan Microelectronics** Shanghai, Ltd.

SSMEC Bldg., 3F, Gaoxin S. Ave. 23/Bldg. #115 Lane 572, Bibo Road Zhangjiang Hi-Tech Park Shanghai, CHINA Tel: +86 21 5080-3866 Fax: +86 21 5080-4600

# Contents

| 1 | Gen  | eral De | scription1                                             |

|---|------|---------|--------------------------------------------------------|

| 2 | Feat | ures    |                                                        |

|   | 2.1  | CPU     | 1                                                      |

|   | 2.2  | Opera   | ting Frequency Mode2                                   |

|   | 2.3  | PWM.    |                                                        |

|   | 2.4  | ADC     |                                                        |

|   | 2.5  | POR     |                                                        |

|   | 2.6  |         | ge Type2                                               |

| 3 | App  |         | s                                                      |

| 4 | •••  |         | nent                                                   |

| 5 |      | •       | tion                                                   |

| 6 |      | •       | ram5                                                   |

| 7 | Fund | ction D | escription6                                            |

|   | 7.1  |         | er Configuration6                                      |

|   |      | 7.1.1   | R Page Register Configuration                          |

|   |      | 7.1.2   | IOC Page Register Configuration                        |

|   | 7.2  | Regist  | er Operations7                                         |

|   |      | 7.2.1   | R0 (Indirect Addressing Register)7                     |

|   |      | 7.2.2   | R1 (TCC)                                               |

|   |      | 7.2.3   | R2 (Program Counter)8                                  |

|   |      | 7.2.4   | R3 (Status, Page Selection)9                           |

|   |      | 7.2.5   | R4 (RAM Selection for Common Registers R20 ~ R3F)10    |

|   |      | 7.2.6   | R5 (Program Page Selection, PWM Control)10             |

|   |      | 7.2.7   | R6 (Port 6 I/O Data, PWM Control)11                    |

|   |      | 7.2.8   | R7 (Port 7 I/O Data, ADC, PWM Duty Cycle)12            |

|   |      | 7.2.9   | R8 (PWM1 Period)                                       |

|   |      | 7.2.10  | R9 (Port 9 I/O Data, DT2L)                             |

|   |      | 7.2.11  | RA (PLL, Main Clock Selection, Watchdog Timer, DT2H)14 |

|   |      |         | RB (ADC Input Data Buffer)                             |

|   |      |         | RC (Port C I/O Data, Counter 1 Data)16                 |

|   |      |         | RE (Interrupt Flag)                                    |

|   |      |         | RF (Interrupt Status)                                  |

|   |      | 1.2.10  | R TO~R3F (General Purpose Register)                    |

|    | 7.3  | Specia  | al Function Registers                                      | 18 |

|----|------|---------|------------------------------------------------------------|----|

|    |      | 7.3.1   | A (Accumulator)                                            | 18 |

|    |      | 7.3.2   | CONT (Control Register)                                    | 18 |

|    |      | 7.3.3   | IOC6 (Port 6 I/O Control, P6 Pin Switch Control)           | 20 |

|    |      | 7.3.4   | IOC7 (Port 7 I/O Control, Port 7 Pull-high Control)        | 22 |

|    |      | 7.3.5   | IOC9 (Port 9 I/O Control, Port 9 Switches)                 |    |

|    |      | 7.3.6   | IOCA (Port 9 PMS Switch Control)                           |    |

|    |      | 7.3.7   | IOCB (ADC Control)                                         |    |

|    |      | 7.3.8   | IOCC (Port C I/O Control, ADC Control)                     |    |

|    |      | 7.3.9   | IOCD (Tone 1 Control, Clock Source, CN1 Prescaler)         |    |

|    |      |         | IOCE (Interrupt Mask)                                      |    |

|    |      |         | IOCF (Interrupt Mask)                                      |    |

|    | 7.4  |         | ction Set                                                  |    |

|    | 7.5  | Code    | Option Register                                            | 32 |

|    | 7.6  | I/O Po  | vrt                                                        | 33 |

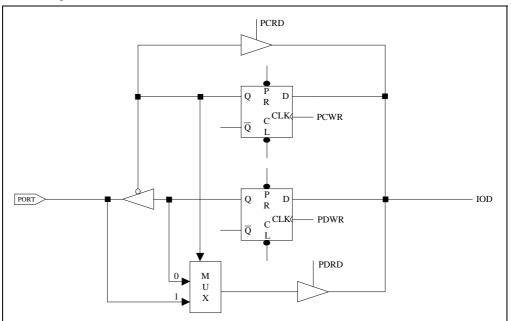

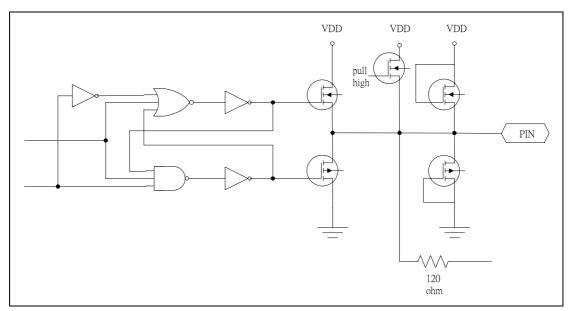

|    |      | 7.6.1   | I/O Structure                                              | 33 |

|    |      | 7.6.2   | I/O Description                                            | 34 |

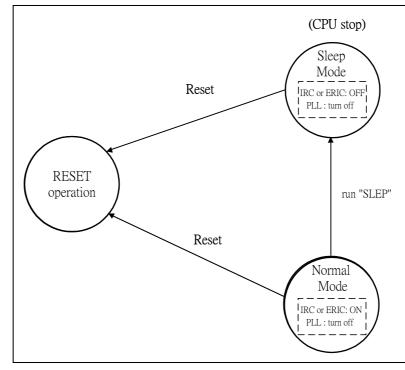

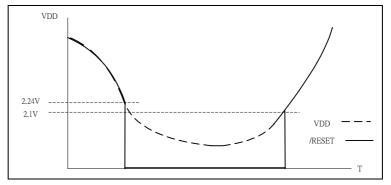

|    | 7.7  | Reset.  |                                                            | 36 |

|    | 7.8  | Wake-   | up                                                         | 36 |

|    | 7.9  | Interru | ıpt                                                        | 37 |

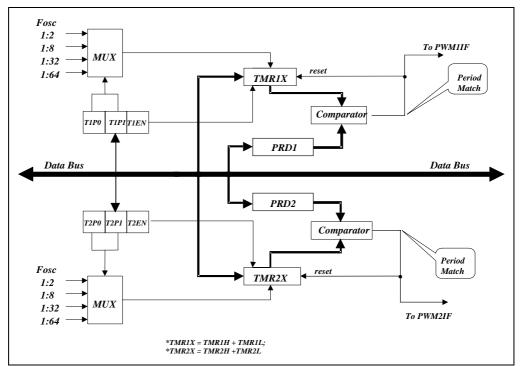

|    | 7.10 | PWM     | (Pulse Width Modulation)                                   | 38 |

|    |      | 7.10.1  | Overview                                                   | 38 |

|    |      | 7.10.2  | Relative Register Description                              | 39 |

|    |      | 7.10.3  | Increment Timer Counter (TMRX: TMR1H/TMR1L or TMR2H/TMR2L) | 40 |

|    |      | 7.10.4  | PWM Period (PRDX: PRD1 or PRD2)                            | 40 |

|    |      | 7.10.5  | PWM Duty Cycle (DTX: DT1H/ DT1L; DTL: DL1H/DL1L)           | 41 |

|    |      | 7.10.6  | PWM Programming Procedure/Steps                            | 41 |

|    |      | 7.10.7  | Timer (TMRX)                                               | 41 |

|    | 7.11 | Oscilla | ator                                                       | 43 |

|    |      | 7.11.1  | Crystal Mode                                               | 43 |

|    |      |         | IRC Mode                                                   |    |

|    |      | 7.11.3  | ERIC Mode                                                  | 44 |

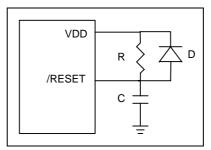

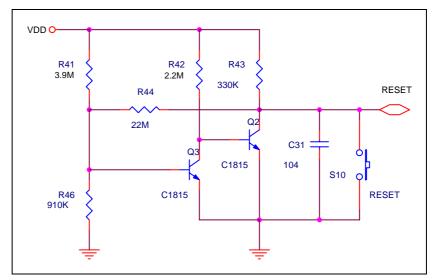

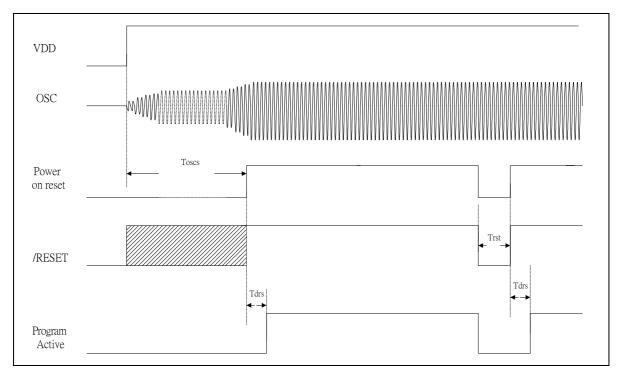

|    | 7.12 | Power   | -on Considerations                                         | 46 |

|    | 7.13 | Extern  | al Power-on Reset Circuit                                  | 46 |

| 8  | Abso | olute M | aximum Ratings                                             | 48 |

| 9  | DC E | lectric | al Characteristics                                         | 48 |

|    | 9.1  | Device  | e Characteristic Graphics                                  | 49 |

| 10 | AC E | lectric | al Characteristics                                         | 50 |

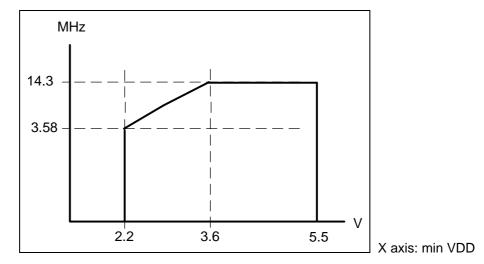

|    | 10.1 | Opera   | ting Voltage vs Main CLK                                   | 51 |

|    | 10.2 | 10-Bit  | ADC Characteristics                                        | 52 |

| 11 | Timi | ng Diag | grams                                                      | 53 |

| 12 | ОТР  | ROM E   | Burning Pins                                               | 54 |

# APPENDIX

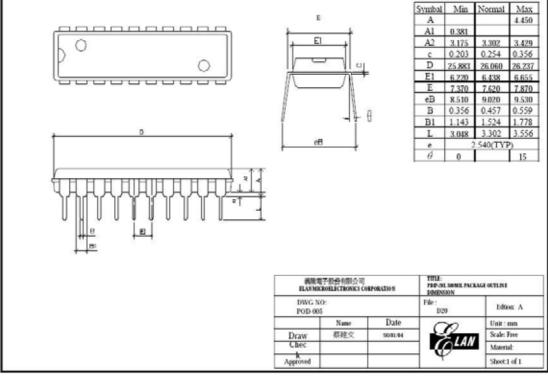

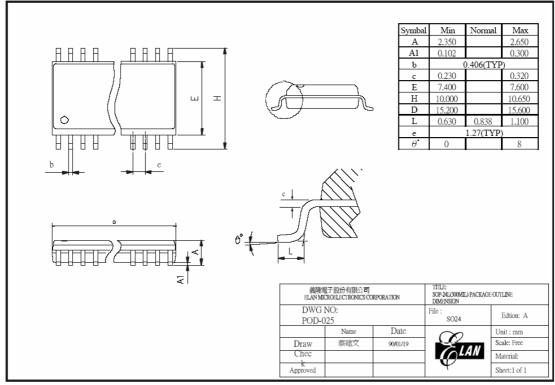

| Α | Pack | аде Туре                                                         | 55  |

|---|------|------------------------------------------------------------------|-----|

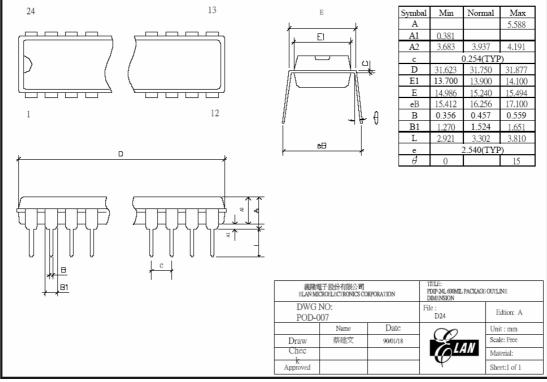

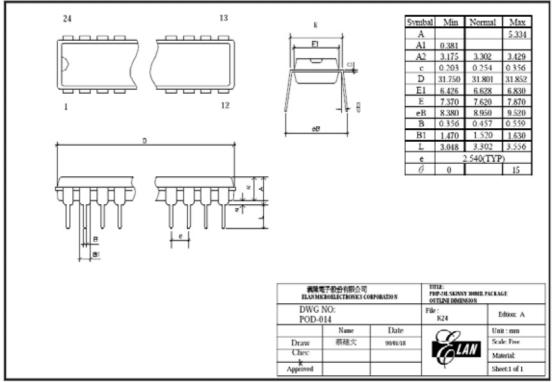

| в | Pack | age Information                                                  | 55  |

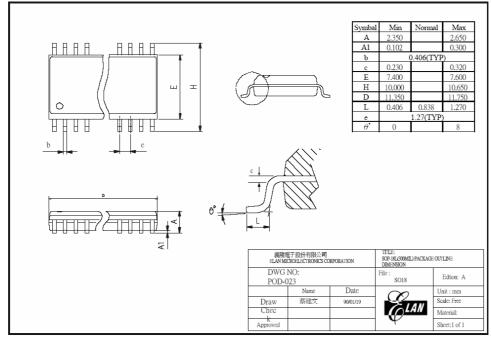

|   | B.1  | EM78P5840NM                                                      | .55 |

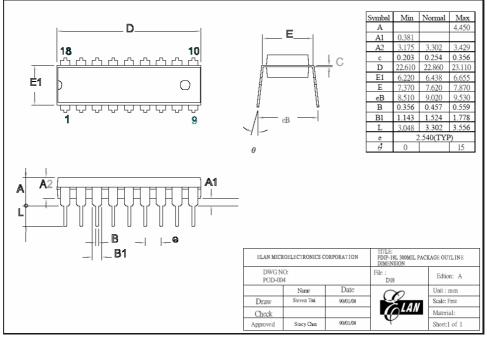

|   | B.2  | EM78P5840NP                                                      | .56 |

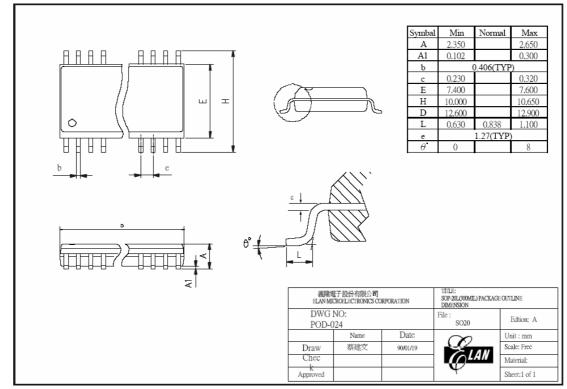

|   | B.3  | EM78P5841NM                                                      | .56 |

|   | B.4  | EM78P5841NP                                                      | .57 |

|   | B.5  | EM78P5842NM                                                      | .57 |

|   | B.6  | EM78P5842NP                                                      | .58 |

|   | B.7  | EM78P5842NK                                                      | .58 |

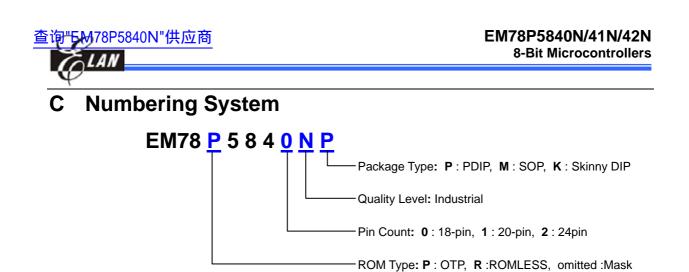

| С | Num  | bering System                                                    | 59  |

| D |      | 8P5840N Series                                                   |     |

|   | D.1  | EM78P5840N Series Category                                       | .59 |

|   |      | D.1.1 Differences between ICE5840, EM78P5840N and EM785840N      | .59 |

|   | D.2  | EM78P5840N Series Package Type                                   | .59 |

|   |      | D.2.1 Differences between EM78P5840N, EM78P5841N, and EM78P5842N | .60 |

| Е | Appl | ication Notes                                                    | 61  |

# **Specification Revision History**

| Doc. Version | Revision Description | Date       |

|--------------|----------------------|------------|

| 1.0          | Initial version      | 2006/04/25 |

# **1** General Description

The EM78P5840N/41N/42N series are 8-bit RISC architecture microcontroller devices designed and developed with low-power, high-speed CMOS technology. Each of these devices has on-chip 4K×13-bit Electrical One Time Programmable Read Only Memory (OTP-ROM). It provides a protection bit to prevent intrusion of user's OTP memory code as well as from unwanted external accesses. A number of one-time programmable option bits are also available to meet user's application requirements.

Functional flexibility of these integrated ICs is enhanced with their internal special features such as watchdog timer (WDT), program OTP-ROM, RAM, programmable real-time clock/counter, internal interrupt, power down mode, dual PWM (Pulse Width Modulation), 8-channel 10-bit A/D converter, and tri-state I/O.

#### NOTE

Refer to the Application Notes provided in the Appendix for important reminders before using the microcontroller described herein. Convention on tables used to describe register attributes (bit number, bit name, type, etc.), are also provided in the Appendix.

# 2 Features

# 2.1 CPU

- Operating voltage: 2.2V~5.5V at the main CLK (less than 3.58MHz)

Main CLK f<sub>SYS</sub> < 3.58MHz: 2.2V</li>

Main CLK f<sub>SYS</sub> = 14.3MHz: 3.6V

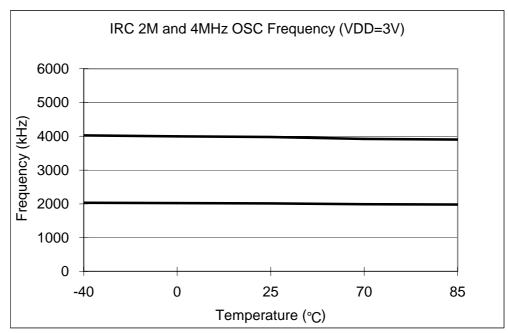

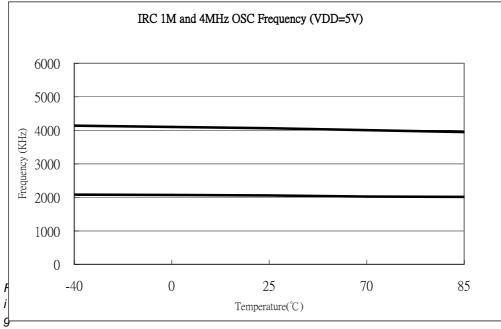

- IRC mode: 4MHz, 2MHz

Voltage deviation: ±5% (2.3V~5.5V) Process deviation: Typ. ±3%, Max. ±5% Temperature deviation: ±5% (-40°C~85°C)

- 4K x 13 OTP-ROM

- 144 x 8 general propose RAM

- 19 bi-directional and three input-only general purpose I/O

- 8-level stack for subroutine nesting

- 8-bit real time clock/counter (TCC)

- One 8-bit counter interrupt

- On-chip watchdog timer (WDT)

- Single-instruction cycle commands

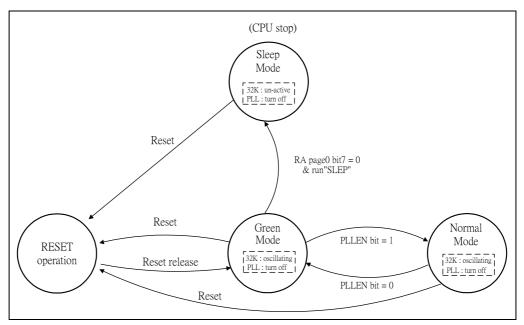

Three operation modes using crystal oscillator (Main clock can be programmed to 3.58 MHz or 14.3 MHz):

| Mode   | CPU Status | Main Clock | 32.768kHz Clock Status |

|--------|------------|------------|------------------------|

| Sleep  | Off        | Off        | Off                    |

| Green  | On         | Off        | On                     |

| Normal | On         | On         | On                     |

- Two Normal mode frequency levels: 3.58 MHz and 14.3 MHz

- Input port interrupt function

- Dual-clock operation (Internal PLL main clock, External 32.768kHz)

# 2.2 Operating Frequency Mode

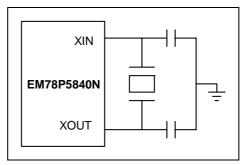

- Crystal mode (the XIN and XOUT pins are connected to the external crystal and capacitor)

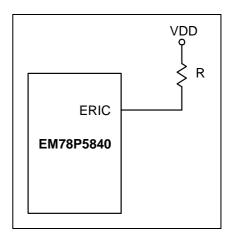

- ERIC mode (the ERCI pin connects the resistor to VDD)

- IRC mode

## 2.3 PWM

- Dual PWM (Pulse Width Modulation) with 10-bit resolution

- Programmable period (or baud rate)

- Programmable duty cycle

# 2.4 ADC

■ Operating voltage: 2.5V~5.5V

| Converter Rate          | 74.6K | 37.4K | 18.7K | 9.3K |

|-------------------------|-------|-------|-------|------|

| Operating Voltage (min) | 3.5V  | 3.0V  | 2.5V  | 2.5V |

- 8-channel 10-bit successive approximation A/D converter

- Internal (VDD) reference voltage

## 2.5 POR

Power-on reset

# 2.6 Package Type

| EM78P5840NM: 18-pin SOP  | EM78P5840NP: 18-pin PDIP       |

|--------------------------|--------------------------------|

| EM78P5841NM: 20-pin SOP  | EM78P5841NP: 20-pin PDIP       |

| EM78P5842NP: 24-pin PDIP | EM78P5842NK: 24-pin Skinny DIP |

# 3 Applications

General purpose I/O product applications A/D applications

# 4 Pin Assignment

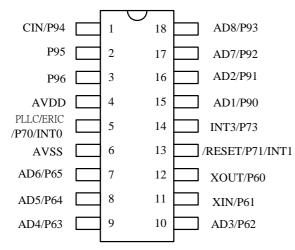

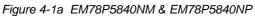

Figure 4-1b EM78P5841NM & EM78P5841NP

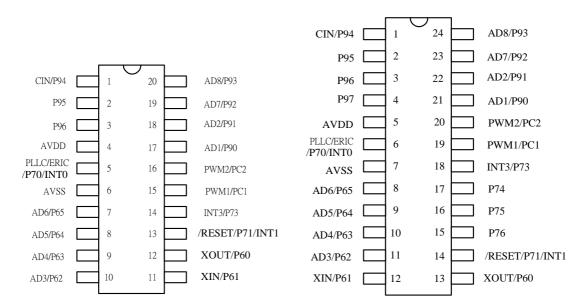

Figure 4-1c EM78P5842NM & EM78P5842NP

8-Bit Microcontrollers

# 5 Pin Description

| Pin Name     | I/O                                                   | Description                                                                                                                    |  |  |  |  |  |

|--------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Power        |                                                       |                                                                                                                                |  |  |  |  |  |

| AVDD         | -                                                     | Power supply                                                                                                                   |  |  |  |  |  |

| AVSS         | -                                                     | Ground                                                                                                                         |  |  |  |  |  |

| Clock        |                                                       |                                                                                                                                |  |  |  |  |  |

| XIN          | I                                                     | Input pin for the 32.768 kHz oscillator                                                                                        |  |  |  |  |  |

| XOUT         | 0                                                     | Output pin for the 32.768 kHz oscillator                                                                                       |  |  |  |  |  |

| PLLC         | Ι                                                     | Phase lock loop capacitor. Connect a capacitor (0.047 $\mu F$ to 0.1 $\mu F$ ) to ground                                       |  |  |  |  |  |

| OSC          | Ι                                                     | ERIC mode clock signal input. This pin is shared with PLLC.                                                                    |  |  |  |  |  |

| CIN          | Ι                                                     | Counter 1 external CLK input. This pin is shared with P94.<br>Note that the frequency of the input CLK must be less than 1MHz. |  |  |  |  |  |

| 10-Bit 8 Cha | nnel A/D                                              |                                                                                                                                |  |  |  |  |  |

| AD1          | -                                                     | ADC Input Channel 1. This pin is shared with Port 90.                                                                          |  |  |  |  |  |

| AD2          | Ι                                                     | ADC Input Channel 2. This pin is shared with Port 91.                                                                          |  |  |  |  |  |

| AD3          | -                                                     | ADC Input Channel 3. This pin is shared with Port 62.                                                                          |  |  |  |  |  |

| AD4          | Ι                                                     | ADC Input Channel 4. This pin is shared with Port 63.                                                                          |  |  |  |  |  |

| AD5          | -                                                     | ADC Input Channel 5. This pin is shared with Port 64.                                                                          |  |  |  |  |  |

| AD6          | -                                                     | ADC Input Channel 6. This pin is shared with Port 65.                                                                          |  |  |  |  |  |

| AD7          | ADC Input Channel 7. This pin is shared with Port 92. |                                                                                                                                |  |  |  |  |  |

| AD8 I        |                                                       | ADC Input Channel 8. This pin is shared with Port 93.                                                                          |  |  |  |  |  |

| PWM          |                                                       |                                                                                                                                |  |  |  |  |  |

| PWM1         | 0                                                     | Pulse width modulation output. This pin is shared with Port C1.                                                                |  |  |  |  |  |

| PWM2         | 0                                                     | Pulse width modulation output. This pin is shared with Port C2.                                                                |  |  |  |  |  |

| 10           |                                                       |                                                                                                                                |  |  |  |  |  |

| P60 ~ P61    | I/O                                                   | Each bit in Port 60 and Port 61 can be an input or output port. These two pins can be used for the ERIC and IRC modes.         |  |  |  |  |  |

| P62 ~P65     | I/O                                                   | Each bit in Port 62 to Port 65 can be an input or output port.                                                                 |  |  |  |  |  |

| P70          | I/O                                                   | Each bit in Port 70 can be an input or output port.                                                                            |  |  |  |  |  |

| P71          | I                                                     | Port 71 is input only                                                                                                          |  |  |  |  |  |

| P73 ~ P76    | I/O                                                   | Each bit in Port 7 can be an input or output port.                                                                             |  |  |  |  |  |

| P90 ~ P97    | I/O                                                   | Each bit in Port 9 can be an input or output port.                                                                             |  |  |  |  |  |

| PC1 ~ PC2    | I/O                                                   | Each bit in Port C can be an input or output port.                                                                             |  |  |  |  |  |

| INT0         | (Port 70)                                             | Interrupt sources. A falling or rising edge signal (controlled by the CONT register) in Port 70 will generate an interrupt.    |  |  |  |  |  |

| INT1         | (Port 71)                                             | Interrupt sources with the same interrupt flag. A falling edge signal on any pin in Port 71 will generate an interrupt.        |  |  |  |  |  |

| INT3         | Port 73                                               | Interrupt sources with the same interrupt flag. A falling edge signal on any pin<br>Port 73 will generate an interrupt.        |  |  |  |  |  |

| /RESET       | I                                                     | Low reset                                                                                                                      |  |  |  |  |  |

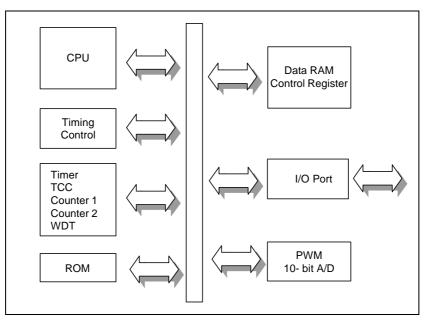

# 6 Block Diagram

Figure 5-1a EM78P5840N/41N/42N Block Diagram

Figure 5-1b EM78P5840N/41N/42N Block Diagram

# 7 Function Description

# 7.1 Register Configuration

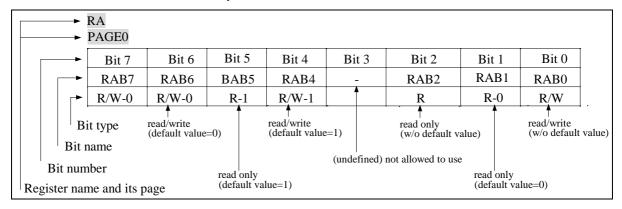

# 7.1.1 R Page Register Configuration

|               | R Page Registers                                 |                     |      |                                            |                                                  |  |  |  |

|---------------|--------------------------------------------------|---------------------|------|--------------------------------------------|--------------------------------------------------|--|--|--|

| Addr          | R Page 0                                         | R Page 1            |      | R Page 2                                   | R Page 3                                         |  |  |  |

| 00            | Indirect addressing                              | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 01            | TCC                                              | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 02            | PC                                               | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 03            | Page, Status                                     | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 04            | RAM bank, RSR                                    | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 05            | Program ROM page                                 | Reserve             |      | Reserve                                    | PWM Control                                      |  |  |  |

| 06            | Port 6 I/O data                                  | Reserve             |      | Reserve                                    | PWM1 Duty                                        |  |  |  |

| 07            | Port 7 I/O data                                  | ADC MSB output dat  | а    | Reserve                                    | PWM1 Control<br>Duty of PWM1                     |  |  |  |

| 08            | Reserve                                          | Reserve             |      | Reserve                                    | PWM1 Period                                      |  |  |  |

| 09            | Port 9 I/O data                                  | Reserve             |      | Reserve                                    | PWM2 Duty                                        |  |  |  |

| 0A            | PLL, Main clock,<br>WDTE                         | Reserve             |      | Reserve                                    | PWM2 Control<br>PWM2 Duty                        |  |  |  |

| 0B            | Reserve                                          | ADC output data bu  | ffer | Reserve                                    | PWM2 Period                                      |  |  |  |

| 0C            | Port C I/O data                                  | Counter 1 data      |      | Reserve                                    | Reserve                                          |  |  |  |

| 0D            | Reserve                                          | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 0E            | Interrupt flag                                   | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 0F            | Interrupt flag                                   | Reserve             |      | Reserve                                    | Reserve                                          |  |  |  |

| 10<br>:<br>1F | 16 bytes<br>Common registers                     |                     |      |                                            |                                                  |  |  |  |

| 20<br>:<br>3F | Bank 0<br>Common registers<br>32x8 for each bank | Common registers Co |      | nk 2<br>mmon registers<br>‹8 for each bank | Bank 3<br>Common registers<br>32x8 for each bank |  |  |  |

Addresses 00~0F with Page 0~Page 3 are special registers. Addresses 10~1F are global with general purpose memory. Use the MOV instruction to set the MCU to read data from or write data to these registers directly. This will ignore the RAM bank select bits (RB1, RB0 in R4 Page 0). Addresses 20~3F are general purpose RAM, but the bank number must be indicated before accessing data.

| IOC Page Registers |                    |                                       |  |  |  |  |  |

|--------------------|--------------------|---------------------------------------|--|--|--|--|--|

| Addr               | IOC Page 0         | IOC Page 1                            |  |  |  |  |  |

| 00                 | Reserve            | Reserve                               |  |  |  |  |  |

| 01                 | Reserve            | Reserve                               |  |  |  |  |  |

| 02                 | Reserve            | Reserve                               |  |  |  |  |  |

| 03                 | Reserve            | Reserve                               |  |  |  |  |  |

| 04                 | Reserve            | Reserve                               |  |  |  |  |  |

| 05                 | Reserve            | Reserve                               |  |  |  |  |  |

| 06                 | Port 6 I/O control | Port 6 switches                       |  |  |  |  |  |

| 07                 | Port 7 I/O control | Port 7 pull high                      |  |  |  |  |  |

| 08                 | Reserve            | Reserve                               |  |  |  |  |  |

| 09                 | Port 9 I/O control | Reserve                               |  |  |  |  |  |

| 0A                 | Reserve            | Port 9 switches                       |  |  |  |  |  |

| 0B                 | Reserve            | ADC control                           |  |  |  |  |  |

| 0C                 | Reserve            | Reserve                               |  |  |  |  |  |

| 0D                 | Reserve            | Clock source (CN1)<br>Prescaler (CN1) |  |  |  |  |  |

| 0E                 | Interrupt mask     | Reserve                               |  |  |  |  |  |

| 0F                 | Interrupt mask     | Reserve                               |  |  |  |  |  |

# 7.1.2 IOC Page Register Configuration

The IOC registers are special registers. User can use the "IOW" instruction to write data and the "IOR" instruction to read data.

# 7.2 Register Operations

## 7.2.1 R0 (Indirect Addressing Register)

R0 is not a physically implemented register. It is used as an indirect addressing pointer. Any instruction using R0 as a register actually accesses data pointed by the RAM Select Register (R4).

#### Example:

Mov A, @0x20 ; store an address at R4 for indirect addressing

Mov 0x04, A

Mov A, @0xAA ; write data 0xAA to R20 at Bank0 through R0

Mov 0x00, A

# 7.2.2 R1 (TCC)

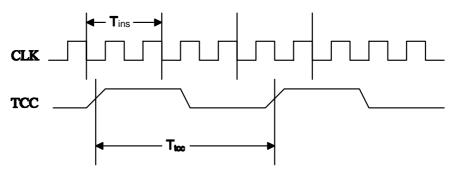

The TCC data buffer is Increased by 16.384kHz or by the instruction clock cycle (controlled by the CONT register). It is written and read by the program as with any other register.

# 7.2.3 R2 (Program Counter)

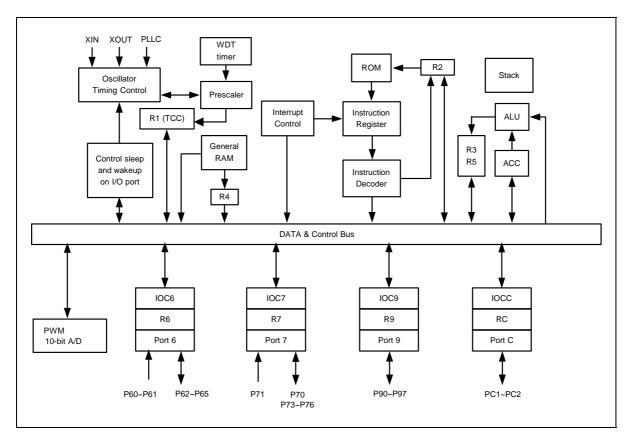

The R2 structure is depicted in the Figure 7-1 below. The configuration structure generates  $4K \times 13$  external ROM addresses to the corresponding program instruction codes.

The "JMP" instruction allows direct loading of the low 10 program counter bits.

The "CALL" instruction loads the low 10 bits of the PC, PC+1, and then pushes the data onto the stack.

"RET" ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack.

"MOV R2, A" allows the loading of an address from the A register to the PC, and the contents of the ninth and tenth bits are cleared to "0."

"ADD R2,A" allows a relative address to be added to the current PC, and the contents of the ninth and tenth bits are cleared to "0."

"TBL" allows a relative address to be added to the current PC, and the contents of the ninth and tenth bits don't change. The most significant bit (A10~A11) will be loaded with the contents of bits PS0~PS1 in the status register (R5 Page 0) upon execution of a "JMP", "CALL", "ADD R2, A", or "MOV R2, A" instruction.

If an interrupt is triggered, the program ROM will jump to Address 0x08 at Page 0. The CPU will store ACC, the status of R3, and R5 Page automatically; and they will be restored after instruction RETI.

Figure 7-1 Program Counter Organization

# 7.2.4 R3 (Status, Page Selection)

#### ■ (Status Flag, Page Selection Bits)

| Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|---------|-------|-------|-------|-------|-------|

| RPAGE1 | RPAGE0 | IOCPAGE | Т     | Р     | Z     | DC    | С     |

| R/W-0  | R/W-0  | R/W-0   | R     | R     | R/W   | R/W   | R/W   |

#### Bit 0 (C): Carry flag

Bit 1(DC): Auxiliary carry flag

Bit 2 (Z): Zero flag

Bit 3 (P): Power down bit

Set to "1" during power on or by a "WDTC" command and reset to "0" by a "SLEP" command.

#### Bit 4 (T): Time-out bit

Set to 1 by the "SLEP" and "WDTC" command, or during power up and reset to 0 by WDT timeout.

| Event                             | Т | Р | Remarks        |

|-----------------------------------|---|---|----------------|

| WDT wakes up from sleep mode      | 0 | 0 |                |

| WDT times out (not in sleep mode) | 0 | 1 |                |

| /RESET wakes up from sleep        | 1 | 0 |                |

| Power up                          | 1 | 1 |                |

| Low pulse on /RESET               | х | х | x = don't care |

Bit 5 (IOCPAGE): Change IOC pages between Page 0 and Page 1

"0" : IOC Page 0

"1" : IOC Page 1

See Section 7.1.2 "IOC Page Register Configuration" for further details.

#### Bits 6~7 (RPAGE0 ~ RPAGE1): Change R pages between Page 0 ~ Page 3

| (RPAGE1, RPAGE0) | R Page # Selected |

|------------------|-------------------|

| (0, 0)           | R Page 0          |

| (0, 1)           | R Page 1          |

| (1, 0)           | R Page 2          |

| (1, 1)           | R Page 3          |

Refer to Section 7.1.1 "R Page Register Configuration" for further details.

# 7.2.5 R4 (RAM Selection for Common Registers R20 ~ R3F)

#### ■ (RAM Selection Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RB1   | RB0   | RSR5  | RSR4  | RSR3  | RSR2  | RSR1  | RSR0  |

| R/W-0 | R/W-0 | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

**Bit 0 ~ Bit 5 (RSR0 ~ RSR5):** Indirect addressing for common Registers R20 ~ R3F RSR bits are used to select up to 32 registers (R20 to R3F) in indirect addressing mode.

Bit 6 ~ Bit 7 (RB0 ~ RB1): Bank selection bits for common Registers R20 ~ R3F

These selection bits are used to determine which bank is activated among the 4 banks for the 32 registers (R20 to R3F).

Refer to Section 7.1.1 "*R Page Register Configuration*" for further details.

## 7.2.6 R5 (Program Page Selection, PWM Control)

#### ■ Page 0 (Port 5 I/O Data Register, Program Page Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | -     | -     | -     | 0     | 0     | PS1   | PS0   |

| -     | -     | -     | -     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

#### Bit 0 ~ Bit 1 (PS0 ~ PS1): Program page selection bits

| PS1 | PS0 | Program Memory Page (Address) |

|-----|-----|-------------------------------|

| 0   | 0   | Page 0                        |

| 0   | 1   | Page 1                        |

| 1   | 0   | Page 2                        |

| 1   | 1   | Page 3                        |

The PAGE instruction can be used to maintain the program page.

Bit 2 ~ Bit 3 (undefined): These two bits must be set to "0." Otherwise, the MCU will access an incorrect program code.

#### Bit 4 ~ Bit 7 (undefined): not used

#### Page 3 (PWMCON)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PWM2E | PWM1E | T2EN  | T1EN  | T2P1  | T2P0  | T1P1  | T1P0  |

| R/W-0 |

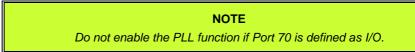

#### Bit 0 ~ Bit 1 (T1P0 ~ T1P1): TMR1 clock prescaler option bits

| T1P1 | T1P0 | Prescaler     |

|------|------|---------------|

| 0    | 0    | 1:2 (Default) |

| 0    | 1    | 1:8           |

| 1    | 0    | 1:32          |

| 1    | 1    | 1:64          |

Bit 2 ~ Bit 3 (T2P0 ~ T2P1): TMR2 clock prescaler option bits

| T2P1 | T2P0 | Prescaler     |

|------|------|---------------|

| 0    | 0    | 1:2 (Default) |

| 0    | 1    | 1:8           |

| 1    | 0    | 1:32          |

| 1    | 1    | 1:64          |

Bit 4 (T1EN): TMR1 enable bit

"0" : TMR1 is off (default value)

"1" : TMR1 is on

- Bit 5 (T2EN): TMR2 enable bit

- "0" : TMR2 is off (default value)

- "1" : TMR2 is on

#### Bit 6 (PWM1E): PWM1 enable bit

- **"0**" : PWM1 is off (default value), and the corresponding pin carries out the PC1 function

- "1" : PWM1 is on, and the corresponding pin will be automatically set as output pin

#### Bit 7 (PWM2E): PWM2 enable bit

- "0" : PWM2 is off (default value), and the corresponding pin carries out the PC2 function

- "1" : PWM2 is on, and the corresponding pin will be automatically set as output pin

## 7.2.7 R6 (Port 6 I/O Data, PWM Control)

#### ■ Page 0 (Port 6 I/O Data Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | -     | P65   | P64   | P63   | P62   | P61   | P60   |

| -     | -     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

Bit 0 ~ Bit 1 (P60 ~ P61): Ports 60 ~ 61 are used in IRC and ERIC mode. In these modes, Ports 60 ~ 61 are defined as general purpose IO. In Crystal mode, Ports 60 ~ 61 are defined as crystal input (XIN and XOUT) pins.

- Bit 2 ~ Bit 6 (P62 ~ P65): 4-bit Port 6 I/O data register. The IOC register can be used to set each bit either as input or output.

- Bit 6 ~ Bit 7 (undefined): These bits are not used

#### ■ Page 3 (DT1L: The Least Significant Byte (Bits 0 ~ 7) of PWM1 Duty Cycle)

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PWM1[7] | PWM1[6] | PWM1[5] | PWM1[4] | PWM1[3] | PWM1[2] | PWM1[1] | PWM1[0] |

| R/W-0   |

A specified value keeps the output of PWM1 to remain at high until such value matches the value of TMR1.

# 7.2.8 R7 (Port 7 I/O Data, ADC, PWM Duty Cycle)

#### ■ Page 0 (Port 7 I/O Data Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | P76   | P75   | P74   | P73   | -     | P71   | P70   |

| -     | R/W   | R/W   | R/W   | R/W   | -     | R     | R/W   |

- **Bit 0 (P70):** Port 70 is a multi-function pin. In Crystal mode, set P70S in code option to define Port 70 as a general purpose I/O or PLLC. Do not enable the PLL function if Port 70 is defined as an I/O. In IRC or ERIC mode, this pin (Port 70) is defined as general purpose I/O and P70S will be ignored. P70 is Port 70 I/O data register and the IOC7 register can be used to set each bit either as input or output.

- Bit1 (P71): Port 71 is shared with the /RESET pin. Set the code option for P71S and define Port 71 as an input pin or /RESET pin. This register is a read-only bit. P71 does not does not have an internal pull high function. If you want to use the interrupt at P71, external pull high is necessary.

- Bit 2 & Bit 7 (undefined): These bits are not used

- Bit 3 ~ Bit 6 (P73 ~ P76): 4-bit Port 7 I/O data register. The IOC register can be used to set each bit either as input or output.

- Page 1 (ADC Resolution Selection Bit and ADC MSB Output Data)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | -     | AD9   | AD8   | -     | ADRES | 0     | 0     |

| -     | -     | R     | R     | -     | R/W-0 | R-0   | R-0   |

- Bit 0 ~ Bit 1 (undefined): These two bits are not used. However, these bits must be cleared to "0" to avoid possible error.

- Bit 2 (ADRES): Resolution selection for ADC

- "0": ADC is 8-bit resolution. When 8-bit resolution is selected, the most significant (MSB) 8-bit data output of the internal 10-bit ADC will be latched and mapped to RB PAGE1 only (see Section 7.2.12). Hence, R7 PAGE1 Bits 4 ~5 are not implemented.

- "1" : ADC is 10-bit resolution. When 10-bit resolution is selected, the 10-bit data output of the internal 10-bit ADC will be mapped to RB PAGE1 (see Section 7.2.12), plus R7 PAGE1 Bits 4 ~5 to meet the 10 bits requirement.

#### Bit 3 (undefined): This bit is not used

- **Bit 4 ~ Bit 5 (AD8 ~ AD9):** The most significant 2 bits of the 10-bit ADC conversion output data. Combine these two bits with the RB PAGE1 into a complete 10-bit ADC conversion output data.

- Bit 6 ~ Bit 7 (undefined): These bits are not used

#### ■ Page 3 (DT1H: Most Significant Byte (Bit 0 ~ Bit 1) of PWM1 Duty Cycle)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   |

|-------|-------|-------|-------|-------|-------|---------|---------|

| 0     | 0     | 0     | 0     | 0     | 0     | PWM1[9] | PWM1[8] |

| R-0   | R-0   | R-0   | R-0   | R-0   | R-0   | R/W-0   | R/W-0   |

Bit 0 ~ Bit 1 (PWM1[8] ~ PWM1[9]): The Most Significant two bits of PWM1 Duty Cycle

#### 7.2.9 R8 (PWM1 Period)

#### ■ Page 3 (PRD1: PWM1 Period)

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PRD1[7] | PRD1[6] | PRD1[5] | PRD1[4] | PRD1[3] | PRD1[2] | PRD1[1] | PRD1[0] |

| R/W-0   |

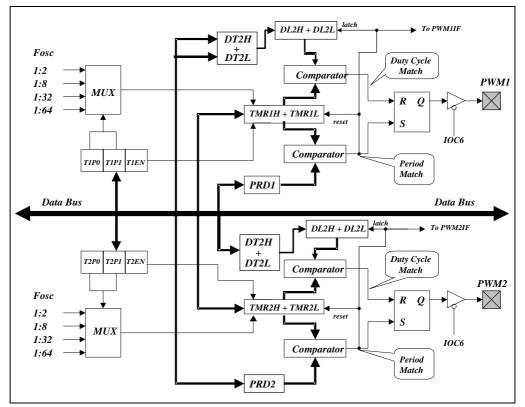

The contents of this register is PWM1 time base period. The PWM1 frequency is the inverse of the time base period.

## 7.2.10 R9 (Port 9 I/O Data, DT2L)

#### ■ Page 0 (Port 9 I/O Data Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P97   | P96   | P95   | P94   | P93   | P92   | P91   | P90   |

| R/W   |

Bit 0 ~ Bit 7 (P90 ~ P97): 8-bit Port 9 (0~7) I/O data register. The IOC register can be used to set each bit either as input or output.

#### ■ Page 3 (DT2L: Least Significant Byte (Bit 0 ~ Bit 7) of PWM2 Duty Cycle)

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PWM2[7] | PWM2[6] | PWM2[5] | PWM2[4] | PWM2[3] | PWM2[2] | PWM2[1] | PWM2[0] |

| R/W-0   |

A specified value keeps the PWM2 output to remain high until the it matches with the value of TMR2.

Bit 2 ~ Bit 7 (undefined): These bits are not used. However, these bits must be cleared to "0" to avoid possible error.

## 7.2.11 RA (PLL, Main Clock Selection, Watchdog Timer, DT2H)

#### ■ Page 0 (PLL Enable Bit, Main Clock Selection Bits, Watchdog Timer Enable Bit)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | PLLEN | CLK2  | CLK1  | CLK0  | -     | -     | WDTEN |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | -     | -     | R/W-0 |

#### Bit 0 (WDTEN): Watchdog control bit

"0" : Disable watchdog

"1" : Enable watchdog

The WDTC instruction can be used to clear the watchdog counter. The watchdog counter is a free-running on-chip RC oscillator. The WDT will keep on running even after the oscillator driver has been turned off (i.e., in Sleep mode). During normal operation or Sleep mode, a WDT time-out (if enabled) will cause the device to reset. The WDT can be enabled or disabled any time during Green mode or Normal mode. Without the presacler, the WDT time-out period is approximately 18 ms.

#### Bit 1 ~ Bit 2 (undefined): These bits are not used

Bit 3 ~ Bit 5 (CLK0 ~ CLK2): Main clock selection bits in Crystal mode. These three bits are NOT used in IRC and ERIC mode.

#### In Crystal Mode:

Different frequencies for the main clock can be chosen with the CLK0, CLK1 and CLK2 bits. All available clock selections are listed below:

| PLLEN | CLK2       | CLK1       | CLK0       | Sub Clock | Main Clock | CPU Clock             |

|-------|------------|------------|------------|-----------|------------|-----------------------|

| 1     | 0          | 0          | 0          | 32.768kHz | 3.582MHz   | 3.582MHz (Normal mode |

| 1     | 0          | 0          | 1          | 32.768kHz | 3.582MHz   | 3.582MHz (Normal mode |

| 1     | 0          | 1          | 0          | 32.768kHz | 3.582MHz   | 3.582MHz (Normal mode |

| 1     | 0          | 1          | 1          | 32.768kHz | 3.582MHz   | 3.582MHz (Normal mode |

| 1     | 1          | 0          | 0          | 32.768kHz | 14.3MHz    | 14.3MHz (Normal mode) |

| 1     | 1          | 0          | 1          | 32.768kHz | 14.3MHz    | 14.3MHz (Normal mode) |

| 1     | 1          | 1          | 0          | 32.768kHz | 14.3MHz    | 14.3MHz (Normal mode) |

| 1     | 1          | 1          | 1          | 32.768kHz | 14.3MHz    | 14.3MHz (Normal mode) |

| 0     | don't care | don't care | don't care | 32.768kHz | don't care | 32.768kHz (Green mode |

**Bit 6 (PLLEN):** PLL's power control bit is the CPU mode control register. This bit is only used under Crystal mode. Under RC mode, this bit will be ignored.

- "0" : Disable PLL

- "1" : Enable PLL

If PPL is enabled, CPU will operate in Normal mode (high frequency). Otherwise, it will run in Green mode (low frequency, 32768 Hz).

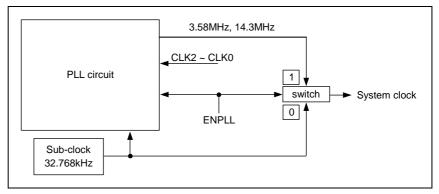

Figure 6-2 Correlation between 32.768kHz and PLL

Bit 7 (undefined): This bit is not used. However, always keep this bit at "0" to preclude possible error.

When Bit 7 and Bit 6 are set to "0" and are included in the SLEP instruction, the following table shows the status after wake up and the wake-up sources.

| Wake-up Signal                     | Sleep Mode                  |

|------------------------------------|-----------------------------|

|                                    | RA(7,6)=(0,0)               |

| -                                  | + SLEP                      |

| TCC time out<br>IOCF Bit 0 =1      | No effect                   |

| Counter 1 time out<br>IOCF Bit 1=1 | No effect                   |

| WDT time out                       | Reset and jump to Address 0 |

| Port 7 (0, 1, 3)*                  | Reset and Jump to Address 0 |

\* Port 70 wake-up function is controlled by IOCF Bit 3. It is a falling edge or rising edge trigger (controlled by CONT register Bit 7).

- Port 71 wake-up function is controlled by IOCF Bit 4. It is a falling edge trigger.

- Port 73 wake-up function is controlled by IOCF Bit 7. It is a falling edge trigger.

#### ■ Page 3 DT2H: Most Significant Bit (Bit 1 ~ Bit 0) of PWM2 Duty Cycle

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   |

|-------|-------|-------|-------|-------|-------|---------|---------|

| -     | -     | -     | -     | -     | -     | PWM2[9] | PWM2[8] |

| -     | -     | -     | -     | -     | -     | R/W-0   | R/W-0   |

Bit 0 ~ Bit 1 (PWM2[8] ~ PWM2[9]): Most Significant bit of PWM2 Duty Cycle A specified value keeps the PWM2 output to remain high until the it matches with the value of TMR2.

Bit 2 ~ Bit 7 (undefined): These bits are not used

# 7.2.12 RB (ADC Input Data Buffer)

#### Page 1 (ADC Output Data Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AD7   | AD6   | AD5   | AD4   | AD3   | AD2   | AD1   | AD0   |

| R     | R     | R     | R     | R     | R     | R     | R     |

Bit 0 ~ Bit 7 (AD0 ~ AD7): The last significant 8 bits of the 10-bit or the 8-bit resolution ADC conversion output data. Combine these 8 bits with the R7 PAGE1 Bit 4 ~ Bit 5 (see Section 7.2.8) to have a complete 10-bit ADC conversion output data in 10-bit resolution mode.

#### Page 3 (PRD2: PWM2 Period)

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PRD2[7] | PRD2[6] | PRD2[5] | PRD2[4] | PRD2[3] | PRD2[2] | PRD2[1] | PRD2[0] |

| R/W-0   |

Bit 0 ~ Bit 7 (PRD2[0] ~ PRD2[7]): All the contents of this register are PWM2 timebase period. The PWM2 frequency is the inverse of the period.

## 7.2.13 RC (Port C I/O Data, Counter 1 Data)

#### ■ Page 0 (Port 9 I/O Data Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | -     | -     | -     | -     | PC2   | PC1   | -     |

| -     | -     | -     | -     | -     | R/W   | R/W   | -     |

Bit 0 (undefined): This bit is not used.

Bit 1 ~ Bit 2 (PC1 ~ PC2): Port C1, Port C2 I/O data register

The IOC register can be used to define each bit either as input or output.

Bit 3 ~ Bit 7 (undefined): These bits are not used.

#### Page 1 (Counter 1 Data Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CN17  | CN16  | CN15  | CN14  | CN13  | CN12  | CN11  | CN10  |

| R/W-0 |

Bit 0 ~ Bit 7 (CN10 ~ CN17): Counter 1 buffer that's readable and writable. Counter 1 is an 8-bit up-counter with 8-bit prescaler that allows the device to preset (write → preset) and read the counter by using RC PAGE1. After an interrupt, the preset value will be reloaded.

Examples of Write & Read Instructions:

| MOV | 0x0C, A | ; write the data at accumulator to Counter 1 (preset) |

|-----|---------|-------------------------------------------------------|

| MOV | A, 0x0C | ; read & move the data at Counter 1 to accumulator    |

# 7.2.14 RE (Interrupt Flag)

#### Page 0 (Interrupt Flag)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PWM2  | 0     | ADI   | PWM1  | 0     | 0     | 0     | 0     |

| R/W-0 |

Bit 0 ~ Bit 3 (undefined): Not used. However, these four bits must be cleared to "0" to prevent possible error.

- **Bit 4 (PWM1):** One PWM1 (Pulse Width Modulation Channel 1) period upon reaching interrupt flag.

- Bit 5 (ADI): ADC interrupt flag after each sampling

- Bit 6 (undefined): This bit must be cleared to "0." Otherwise, errors may occur.

- **Bit 7 (PWM2):** PWM2 (Pulse Width Modulation Channel 2) interrupt flag Set when a selected period is reached, reset by software.

#### 7.2.15 RF (Interrupt Status)

#### Interrupt Status Register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| INT3  | -     | -     | INT1  | INT0  | -     | CNT1  | TCIF  |

| R/W-0 | -     | -     | R/W-0 | R/W-0 | -     | R/W-0 | R/W-0 |

Bit 0 (TCIF): TCC timer overflow interrupt flag. Set when TCC timer overflows.

- "**0**" : With Interrupt request

- "1" : No Interrupt request. Hence no interrupt occurs.

- Bit 1 (CNT1): Counter1 timer overflow interrupt flag. Set when Counter1 timer overflows.

- "0" : With Interrupt request

- "1" : No Interrupt request. Hence no interrupt occurs.

- Bit 2 (undefined): This bit is not used

- **Bit 3 (INT0):** By setting Port 70 to general IO, INT0 will become Port 70 pin's interrupt flag. If Port 70 has a falling edge/rising edge (controlled by the CONT register) trigger signal, the CPU will set this bit. If the pin is set to PLLC or OSCI, no interrupt will occur at Port 70 and INT0 register will be ignored.

- "0" : With Interrupt request

- "1" : No Interrupt request. Hence no interrupt occurs.

- Bit 4 (INT1): By setting Port 71 to general IO, INT1 will become Port 71 pin's interrupt flag. External pull high circuit is needed to trigger an interrupt at Port 71. If Port 71 has a falling edge trigger signal, the CPU will set this bit. If the pin is set to /RESET, no interrupt will occur at Port 71 and INT1 register will be ignored.

- "0" : With Interrupt request

- "1" : No Interrupt request. Hence no interrupt occurs.

- Bit 5 ~ Bit 6 (undefined): These bits are not used

- **Bit 7 (INT3):** External Port 73 pin interrupt flag. If Port 73 has a falling edge trigger signal (see table below), the CPU will set this bit.

- "0" : With Interrupt request

- "1" : No Interrupt request. Hence no interrupt occurs.

**NOTE** IOCF is the interrupt mask register which can be read from and cleared.

The following shows the trigger edge signals.

| Signal    | Trigger               |  |  |  |  |

|-----------|-----------------------|--|--|--|--|

| TCC       | Time out              |  |  |  |  |

| Counter 1 | Time out              |  |  |  |  |

| INTO      | Falling / Rising edge |  |  |  |  |

| INT1      | Falling edge          |  |  |  |  |

| INT3      | Falling edge          |  |  |  |  |

## 7.2.16 R10~R3F (General Purpose Register)

## ■ R10~ R3F (Banks 0 ~ 3)

These are all general purpose registers.

# 7.3 Special Function Registers

# 7.3.1 A (Accumulator)

Internal data transfer operation, or instruction operand holding usually involves the temporary storage function of the Accumulator, which is not an addressable register.

## 7.3.2 CONT (Control Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P70EG | INT   | TS    | RETBK | PAB   | PSR2  | PSR1  | PSR0  |

| R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

Note: The CONT register is readable (CONTR) and writable (CONTW).

| PSR2 | PSR1 | PSR0 | TCC Ratio | WDT Ratio |

|------|------|------|-----------|-----------|

| 0    | 0    | 0    | 1:2       | 1:1       |

| 0    | 0    | 1    | 1:4       | 1:2       |

| 0    | 1    | 0    | 1:8       | 1:4       |

| 0    | 1    | 1    | 1:16      | 1:8       |

| 1    | 0    | 0    | 1:32      | 1:16      |

| 1    | 0    | 1    | 1:64      | 1:32      |

| 1    | 1    | 0    | 1:128     | 1:64      |

| 1    | 1    | 1    | 1:256     | 1:128     |

#### Bit 0 ~ Bit 2 (PSR0 ~ PSR2): TCC/WDT prescaler bits

Bit 3 (PAB): Prescaler assigned bit

"**0**" : TCC

"**1**" : WDT

Bit 4 (RETBK): Return the backed-up control value for the interrupt routine

- "**0**" : Disable

- "1" : Enable

When this bit is set to "1", the CPU will store ACC, R3 status, and R5 PAGE automatically after an interrupt is triggered. This bit will be restored after the RETI instruction. When this bit is set to "0", user needs to store ACC, R3 status, and R5 PAGE in the program.

- Bit 5 (TS): TCC signal source

- "0" : Internal instruction clock cycle

- "1" : IRC output

#### Bit 6 (INT): INT enable flag

- "0" : Interrupt masked by DISI or hardware interrupt

- "1" : Interrupt enabled by ENI/RETI instructions

- **Bit 7 (P70EG):** If Port 70 is set to INT0 input, P70EG can select the interrupt toggle type.

- "0" : P70 's interrupt source is a rising edge signal and falling edge signal

- "1" : P70 's interrupt source is a falling edge signal

#### TCC and WDT

An 8-bit counter is available as the prescaler for the TCC or WDT. The prescaler is available for either TCC or WDT at a time. Availability of the 8-bit counter for TCC or WDT is contingent on the status of Bit 3 (PAB) of the CONT register as shown above.

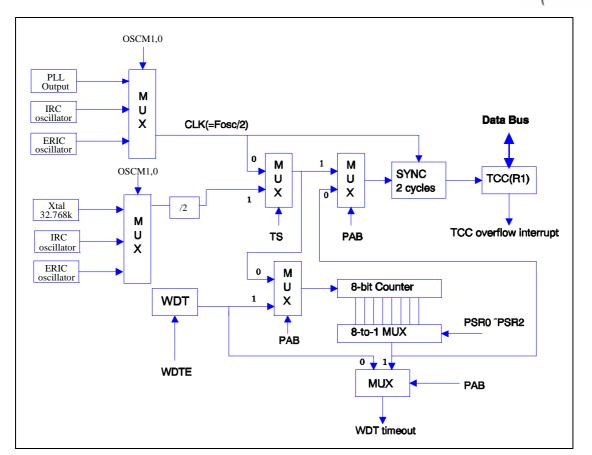

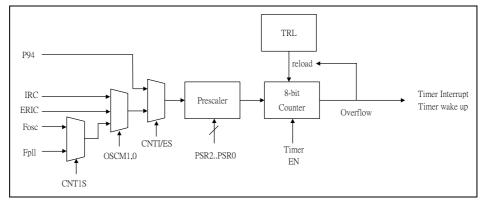

See the prescaler ratio for TCC/WDT in the table above. Figure 6-3 below depicts the block diagram of TCC/WDT.

8-Bit Microcontrollers

Figure 7-3 TCC/WDT Block Diagram

# 7.3.3 IOC6 (Port 6 I/O Control, P6 Pin Switch Control)

#### Page 0 (Port 6 I/O Control Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | IOC65 | IOC64 | IOC63 | IOC62 | IOC61 | IOC60 |

| -     | -     | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

- Bit 0 ~ Bit 1 (IOC60 ~ IOC61): In IRC or ERIC mode, Port 60 and Port 61 are I/O direction control registers. In Crystal mode, these two bits are unused.

- Bit 2 ~ Bit 5 (IOC62 ~ IOC65): Port 62 ~ Port 65 I/O direction control register

"0" : Set the corresponding I/O pin as output

- "1" : Set the corresponding I/O pin to high impedance

- Bit 6 ~ Bit 7 (undefined): These bits are not used. However, these two bits must be cleared to "0." Otherwise, the MCU power consumption will increase.

#### NOTE

The default value of these bits is "1." Clear them to "0" when initializing the MCU.

#### Page 1 (Port 6 Pins Switch Control Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | 0     | P65S  | P64S  | P63S  | P62S  | P91S  | P90S  |

| -     | -     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

Bit 0 (P90S): Select normal I/O Port90 pin or ADC Channel 1 input AD1 pin

"0" : P90 (I/O Port 90) pin is selected

"1" : AD1 (ADC Channel 1 input) pin is selected

Bit 1 (P91S): Select normal I/O Port 91 pin or Channel 2 input AD2 pin of ADC

"0" : P91 (I/O Port 91) pin is selected

"1" : AD2 (ADC Channel 2 input) pin is selected

Bit 2 (P62S): Select normal I/O Port 62 pin or Channel 3 input AD3 pin of ADC

"0" : P62 (I/O Port 62) pin is selected

"1" : AD3 (ADC Channel 3 input) pin is selected

Bit 3 (P63S): Select normal I/O Port 63 pin or Channel 4 input AD4 pin of ADC

"0" : P63 (I/O Port 63) pin is selected

"1" : AD4 (ADC Channel 4 input) pin is selected

Bit 4 (P64S): Select normal I/O Port 64 pin or Channel 5 input AD5 pin of ADC

"0" : P64 (I/O Port 64) pin is selected

"1" : AD5 (ADC Channel 5 input) pin is selected

Bit 5 (P65S): Select normal I/O Port 65 pin or Channel 6 input AD6 pin of ADC

"0" : P65 (I/O Port 65) pin is selected

"1" : AD5 (ADC Channel 6 input) pin is selected

**Bit 6 (undefined):** This bit is not used. However, it must be cleared to "0" to prevent possible error from occuring.

Bit 7 (undefined): This bit is not used

#### NOTE

1. ADC Channel 1 and Channel 2 are shared with Port 90 and Port 91.

2. ADC Channel 3 and Channel 6 are shared with Port 62 and Port 65.

# 7.3.4 IOC7 (Port 7 I/O Control, Port 7 Pull-high Control)

| ■ Page u | Page 0 (Port 7 1/0 Control Register) |       |       |       |       |       |       |  |  |  |  |

|----------|--------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Bit 7    | Bit 6                                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

| 0        | IOC76                                | IOC75 | IOC74 | IOC73 | 0     | 0     | IOC70 |  |  |  |  |

| -        | R/W-1                                | R/W-1 | R/W-1 | R/W-1 | -     | -     | R/W-1 |  |  |  |  |

Page 0 (Port 7 I/O Control Register)

Bit 0 (IOC70): Port 70 pin is defined as general purpose IO, PLLC, or OSC through code option setting. In IRC mode or Crystal mode (only at code option P70S =0), Port 70 pin is a general purpose IO, while IOC70 is I/O direction control register of Port 70 pin.

"0" : Set the corresponding I/O pin as output

- "1" : Set the corresponding I/O pin to high impedance

- **Bit 1 (undefined):** This bit is not used. However, by setting P71S = 1 through code option, Port 71 pin will become an input-only pin.

- **Bit 2 (undefined):** This bit is not used but must be cleared to "0." Otherwise, the MCU power consumption will increase.

| NOTE                                                                          |  |

|-------------------------------------------------------------------------------|--|

| The default value of this bit is "1." Clear to "0" when initializing the MCU. |  |

- Bit 3 ~ Bit6 (IOC73~IOC76): Port 7 I/O direction control register

- "0" : Set the corresponding I/O pin as output

- "1" : Set the corresponding I/O pin to high impedance

- **Bit 7 (undefined):** This bit is not used but must be cleared to "0." Otherwise, the MCU power consumption will increase.

| NOTE                                                                          |

|-------------------------------------------------------------------------------|

| The default value of this bit is "1." Clear to "0" when initializing the MCU. |

#### Page 1 (Port 7 Pull-high Control Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | PH76  | PH75  | PH74  | PH73  | 0     | 0     | PH70  |

| -     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | -     | -     | R/W-0 |

**Bit 0 (PH70):** Port 70 pull high control register. This bit only exists whe you set Port 70 as a general purpose IO.

"0" : disable pull high function

- "1" : enable pull high function

- Bits 1 ~ 2 & Bit 7 (undefined): These bits are not used but must be cleared to "0." Otherwise, the MCU power consumption will increase.

- Bit 3 ~ Bit 6 (PH73 ~ PH76): Port 7 pull high control register

- "0" : disable pull high function

- "1" : enable pull high function

# 7.3.5 IOC9 (Port 9 I/O Control, Port 9 Switches)

#### Page 0 (Port 9 I/O Control Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC97 | IOC96 | IOC95 | IOC94 | IOC93 | IOC92 | IOC91 | IOC90 |

| R/W-1 |

Bit 0 ~ Bit 7 (IOC90 ~ IOC97): Port 9 (0~7) I/O direction control register

"0" : Set the corresponding I/O pin as output

"1" : Set the corresponding I/O pin to high impedance

## 7.3.6 IOCA (Port 9 PMS Switch Control)

#### Page 1 (Port 9 Pin Switch Control Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | 0     | -     | -     | 0     | -     | AD8S  | AD7S  |

| -     | R/W   | -     | -     | R/W   | -     | R/W-0 | R/W-0 |

Bit 0 (AD7S): Select normal I/O Port 92 pin or ADC Channel 7 input AD7 pin

"0" : P92 (I/O Port 92) pin is selected

"1" : AD7 (ADC Channel 7 input ) pin is selected

Bit 1 (AD8S) : Select normal I/O Port 93 pin or ADC Channel 8 input AD8 pin

"0" : P93 (I/O Port 93) pin is selected

"1" : AD8 (ADC Channel 8 input ) pin is selected

Bit 2 (undefined): This bit is not used

**Bit 3 (undefined):** This bit is not used. However, it must be cleared to "0." Otherwise, the MCU power consumption will increase.

Bit 4 ~ Bit 5 (undefined): These bits are not used.

**Bit 6 (undefined):** This bit is not used. However, this bit must be cleared to "0." Otherwise, the MCU power consumption will increase.

Bit 7 (undefined): This bit is not used.

# 7.3.7 IOCB (ADC Control)

#### Page 1 (ADC Control Bits)

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|--------|--------|-------|-------|-------|

| IN2   | IN1   | IN0   | ADCLK1 | ADCLK0 | ADPWR | 0     | ADST  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | -     | R/W-0 |

Bit 0 (ADST): Start sampling at the AD converter

By setting this bit to "1", the AD will start to sample data. This bit will be cleared by hardware automatically after each sampling.

Bit 1 (undefined): This bit is not used. However, it must be cleared to "0" to preclude possible error.

#### Bit 2 (ADPWR): AD converter power control

"0" : disable

"**1**" : enable

Bit 3 ~ Bit 4 (ADCLK0 ~ ADCLK1): AD circuit's sampling clock source.

#### In Crystal mode:

| ADCLK1 | ADCLK0 | Sampling Rate | Operating Voltage |

|--------|--------|---------------|-------------------|

| 0      | 0      | 74.6K         | >=3.5V            |

| 0      | 1      | 37.4K         | >=3.0V            |

| 1      | 0      | 18.7K         | >=2.5V            |

| 1      | 1      | 9.3K          | >=2.5V            |

#### In IRC or ERIC mode:

In these modes, the AD converter rate is set by the oscillator. The formula for the input frequency and the AD converter rate is:

AD Converter rate =

$$\frac{Oscillator/4}{(2^{ADCLK})/12}$$

For example, if input CLK = 4MHz:

| ADCLK1 | ADCLK0 | Sampling Rate | <b>Operation Voltage</b> |

|--------|--------|---------------|--------------------------|

| 0      | 0      | 83.3K         | >=3.5V                   |

| 0      | 1      | 41.7K         | >=3.0V                   |

| 1      | 0      | 20.8K         | >=2.5V                   |

| 1      | 1      | 10.4K         | >=2.5V                   |

**Note:** The AD converter (ADC) rate must not be over 50kHz. Otherwise, the ADC resolution will decrease.

This is a CMOS multi-channel 10-bit successive approximation of the A/D converter. Its features are as follows:

- 74.6kHz maximum conversion speed (Crystal mode) at 5V

- Adjustable full scale input

- Internal (VDD) reference voltage

- Eight analog inputs multiplexed into one AD converter

- Power-down mode for power saving

- Complete AD conversion interrupt

- Interrupt register, AD control, and status register, and AD data register

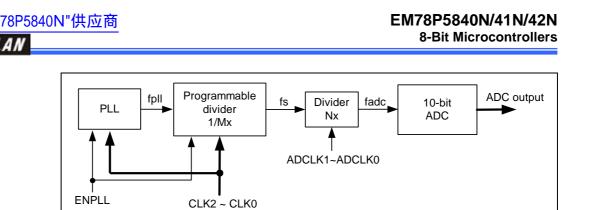

Figure 7-4 ADC Voltage Control Logic

Bit 5 ~ Bit 7 (IN0~ IN2) : Input channel selection of the AD converter. These two bits can choose one of the following three AD inputs.

| IN2 | IN1 | INO | Input | Pin |

|-----|-----|-----|-------|-----|

| 0   | 0   | 0   | AD1   | P90 |

| 0   | 0   | 1   | AD2   | P91 |

| 0   | 1   | 0   | AD3   | P62 |

| 0   | 1   | 1   | AD4   | P63 |

| 1   | 0   | 0   | AD5   | P64 |

| 1   | 0   | 1   | AD6   | P65 |

| 1   | 1   | 0   | AD7   | P92 |

| 1   | 1   | 1   | AD8   | P93 |

**NOTE** Before switching to the AD channel, the corresponding pin must be set as an AD input.

## 7.3.8 IOCC (Port C I/O Control, ADC Control)

#### ■ Page 0 (Port C I/O Control)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | IOCC2 | IOCC1 | 0     |

| -     | -     | -     | -     | -     | R/W-1 | R/W-1 | -     |

- **Bit 0 (undefined):** This bit is not used. However, it must be cleared to "0." Otherwise, the MCU power consumption will increase.

- Bit 1 ~ Bit 2 (IOCC1 ~ IOCC2): PORTC (1~2) I/O direction control register

- "0" : Set the corresponding I/O pin as output

- "1" : Set the corresponding I/O pin to high impedance

- **Bit 3 ~ Bit 7 (undefined):** This bit is not used. However, it must be cleared to "0." Otherwise, the MCU power consumption will increase.

#### NOTE

The default value of Bit 0 and Bits 3~7 is "1." Clear to "0" when initializing the MCU

# 7.3.9 IOCD (Tone 1 Control, Clock Source, CN1 Prescaler)

#### ■ Page 1 (Clock Source and Counter 1 Prescaler)

| Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0   |

|---------|-------|-------|-------|-------|---------|---------|---------|

| CNTI/ES | -     | -     | -     | CNT1S | C1_PSC2 | C1_PSC1 | C1_PSC0 |

| R/W-0   | -     | -     | -     | R/W-0 | R/W-0   | R/W-0   | R/W-0   |

Bit 0 ~ Bit 2 (C1\_PSC0 ~ C1\_PSC2): Counter 1 prescaler ratio

| C1_PSC2 | C1_PSC1 | C1_PSC0 | Counter 1 |

|---------|---------|---------|-----------|

| 0       | 0       | 0       | 1:2       |

| 0       | 0       | 1       | 1:4       |

| 0       | 1       | 0       | 1:8       |

| 0       | 1       | 1       | 1:16      |

| 1       | 0       | 0       | 1:32      |

| 1       | 0       | 1       | 1:64      |

| 1       | 1       | 0       | 1:128     |

| 1       | 1       | 1       | 1:256     |

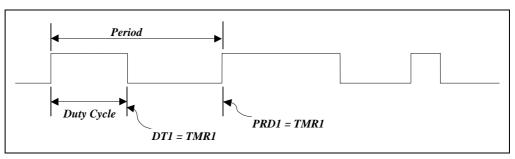

**Bit 3 (CNT1S):** Counter 1 clock source. This bit will be unchanged under RC mode (RC mode CLK is always equal to the oscillator's frequency).

"**0**" : 16.384kHz

"1" : System clock

Figure 6-5 Timer CLK Source Diagram

Bit 4 ~ Bit 6 (undefined): These bits are not used

Bit 7 (CNTI/ES): Counter source select

- "0" : Timer counter CLK is sourced from the system CLK or Crystal output, and P94 is set as a general purpose I/O

- "1" : P94 is defined as input, and the Timer counter CLK is sourced from P94's falling edge

## 7.3.10 IOCE (Interrupt Mask)

#### Page 0 (Interrupt Mask)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PWM2  | 0     | ADI   | PWM1  | -     | -     | -     | -     |

| R/W-0 | -     | R/W-0 | R/W-0 | -     | -     | -     | -     |

Bit 1 ~ Bit 3 (undefined): These bits are not used.

Bit 4 (PWM1) : One PWM1 one period for each interrupt mask.

Bit 5 (ADI) : ADC conversion complete interrupt mask

"0" : Disable interrupt

"1" : Enable interrupt

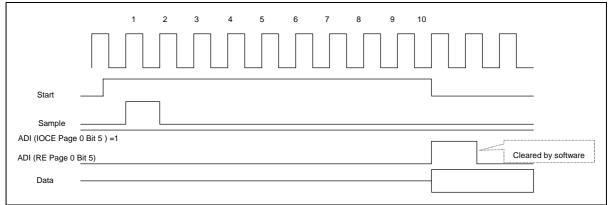

There are four registers for the AD converter. Use one bit of the interrupt control register (IOCE Page 0 Bit 5) to signal an interrupt when the AD conversion is completed. The status and control register of AD (IOCB Page 1 and RE Page 0 Bit 5) indicate the A/D conversion status or AD control. The AD data register (RB PAGE1) stores the result of the AD conversion.

The ADI bit can be enabled or disabled in the IOCE PAGE 0 register to signal the completion of the A/D conversion. The ADI flag is then enabled or disabled in the RE register when AD conversion is completed. The ADI flag indicates the end of an AD conversion. The AD converter sets the interrupt flag (ADI) in the RE Page 0 register when a conversion is completed. The interrupt can be disabled by setting the ADI bit in IOCE Page 0 Bit 5 to "0."

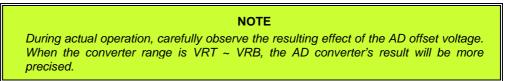

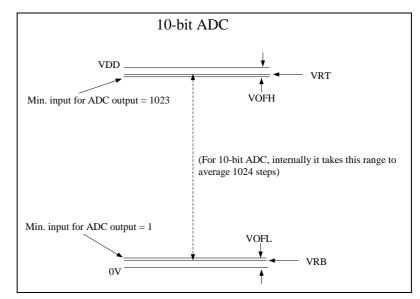

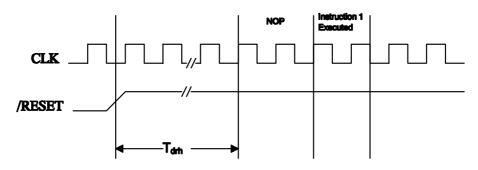

The AD converter has eight analog input channels (AD1 ~ AD8) multiplexed into one sample and hold to AD module. The reference voltage can be driven from the internal power. The AD converter itself is a 10-bit successive approximation type and produces the last significant 8-bit result in the RB Page 1 and the most significant 2 bits to R7 Page 1 Bit 4, Bit 5. A conversion is initiated by setting a control bit ADST in IOCB Page 1 Bit 0. Prior to conversion, the appropriate channel must be selected by setting IN0 ~ IN2 bits in the RE register. Enough time must be allowed to sample data. Every AD data conversion needs 12-clock cycle time. The minimum conversion time required is 13  $\mu$ s (73K sample rate). The ADST Bit in IOCB Page 1 Bit 0 must be set to begin a conversion.

It will be automatically reset in the hardware when a conversion is completed. At the end of the conversion, the Start bit is cleared and the the AD interrupt is activated if ADI in IOCE Page 0 Bit 5 = 1. ADI will be set when the conversion is completed. It can be reset in the software.

If ADI = 0 in IOCE Page 0 Bit 5 and AD starts data conversion by setting ADST(IOCB Page 1 Bit 0) = 1, then AD will continue the conversion non-stop and the hardware

won't reset the ADST bit. In this condition, ADI is deactived. After ADI in IOCE Page 0 Bit 5 is set, ADI in RE Page 0 Bit 5 will beactivated again.

To minimize the operating current, all biasing circuits in the A/D module that consume DC current, are powered down when the ADPWR bit in IOCB Page 1 Bit 2 register is "0." When ADPWR bit is "1," the A/D converter module is operating.

Figure 7-6 A/D Converter Timing

Bit 6 (undefined): This bit is not used. However, you must clear this bit to "0" to avoid possible error.

| Bit 7 (PWM2) : | PWM2 interrupt enable bit |

|----------------|---------------------------|

|                | "0" : Disable interrupt   |

|                |                           |

# "1" : Enable interrupt

#### 7.3.11 IOCF (Interrupt Mask)

#### Page 0 (Interrupt Mask Register)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| INT3  | 0     | 0     | INT1  | INT0  | 0     | CNT1  | TCIF  |

| R/W-0 | -     | -     | R/W-0 | R/W-0 | -     | R/W-0 | R/W-0 |

Bit 0 ~ Bit 1 (TCIF ~ CNT1): Interrupt enable bits

"0" : Disable interrupt

"1" : Enable interrupt

- Bit 2 (undefined): This bit is not used. However, this bit must be cleared to "0" to avoid unpredicted interrupts to occur.

- Bits 3 ~ Bit 4 (INT0 ~ INT1): Interrupt enable bits

- "0" : Disable interrupt

- "1" : Enable interrupt

- Bit 5 ~ Bit 6 (undefined): These bits are not used. However, these bits must be cleared to "0" to avoid unpredicted interrupts to occur.

- Bits 7 (INT3): Interrupt enable bit

- "0" : Disable interrupt

- "1" : Enable interrupt

The following table shows the interrupt sources and the resulting status after an interrupt.

| Interrupt Si                                                           | ignal  | Sleep Mode                            | Green Mode                                    | Normal Mode                                   |

|------------------------------------------------------------------------|--------|---------------------------------------|-----------------------------------------------|-----------------------------------------------|

| TCC time out                                                           | ENI    | RESET and Jump to<br>Address 0        | Interrupt (Jump to Address<br>8 at Page 0)    | Interrupt (Jump to Address<br>8 at Page 0)    |

| And "ENI"                                                              | DISI   | No function                           | No function                                   | No function                                   |

| Counter 1 time<br>IOCF Bit 1=1<br>And "ENI"                            | e out  | No function                           | Interrupt (Jump to Address<br>8 at Page 0)    | Interrupt (Jump to Address<br>8 at Page 0)    |

| Port 70 <sup>1</sup><br>Only at IRC m<br>Crystal mode<br>(at P70S = 0) | ode or | RESET and Jump to<br>Address 0        | Interrupt<br>(Jump to Address 8 at<br>Page 0) | Interrupt<br>(Jump to Address 8 at<br>Page 0) |

| Port 71 <sup>2</sup><br>Only at P71S                                   | ··     |                                       | Interrupt<br>(Jump to Address 8 at<br>Page 0) | Interrupt<br>(Jump to Address 8 at<br>Page 0) |

| Port 73 <sup>3</sup><br>IOCF Bit3 Bit<br>And "ENI"                     | 7 =1   | RESET and Jump to<br>Address 0        | Interrupt<br>(Jump to Address 8 at<br>Page 0) | Interrupt<br>(jump to Address 8 at<br>Page0)  |

| ADI <sup>4</sup><br>IOCE Bit5 = 1<br>And "ENI                          |        | No function                           | No function                                   | Interrupt<br>(Jump to Address 8 at<br>Page 0) |

| PWM1<br>IOCE Bit4 = 1<br>And "ENI                                      |        | PWM1       OCE Bit4 = 1   No function |                                               | Interrupt<br>(Jump to Address 8 at<br>Page 0) |

<sup>1</sup> Port 70 interrupt function is controlled by IOCF Bit 3. It is a falling edge or rising edge trigger (controlled by CONT register Bit 7).

<sup>2</sup> Port 71 interrupt function is controlled by IOCF Bit 4. It is a falling edge trigger.

<sup>3</sup> Port 73 interrupt function is controlled by IOCF Bit 7. It is a falling edge trigger.

<sup>4</sup> ADI interrupt source function is controlled by RE Page 0 Bit 5. It is a rising edge trigger after an ADC sampling is completed.

# 7.4 Instruction Set

The Instruction set has the following features:

- 1) Every bit of any register can be set, cleared, or tested directly.

- 2) The I/O register can be regarded as general register. That is, the same instruction can operate on the I/O register.

#### Convention:

- **R** = Register designator that specifies which one of the registers (including operation and general purpose registers) is to be utilized by the instruction.

- Bits 6 and 7 in R4 determine the selected register bank.

- **b** = Bit field designator that selects the value for the bit located in register R and which affects the operation.

| k = 8 or 10-bit constant or literal v | alue |

|---------------------------------------|------|

|---------------------------------------|------|

| Binary Instruction | Hex  | Mnemonic | Operation                                     | Status<br>Affected | Instruction<br>Cycle |

|--------------------|------|----------|-----------------------------------------------|--------------------|----------------------|

| 0 0000 0000 0000   | 0000 | NOP      | No Operation                                  | None               | 1                    |

| 0 0000 0000 0001   | 0001 | DAA      | Decimal Adjust A                              | С                  | 1                    |

| 0 0000 0000 0010   | 0002 | CONTW    | $A \rightarrow CONT$                          | None               | 1                    |

| 0 0000 0000 0011   | 0003 | SLEP     | $0 \rightarrow WDT$ , Stop oscillator         | Τ, Ρ               | 1                    |

| 0 0000 0000 0100   | 0004 | WDTC     | $0 \rightarrow WDT$                           | Τ, Ρ               | 1                    |