## THIS PRODUCT IS NOT RECOMMENDED FOR NEW DESIGNS. PLEASE REFER TO THE M2 PRODUCT SERIES.

- AT-strip crystal in a miniature ceramic surface mount package

- TTL and HCMOS compatible

- · Tri-state output is optional

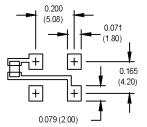

## SUGGESTED SOLDER PAD LAYOUT

**NOTE:** A capacitor of value 0.01  $\mu$ F or greater between Vdd and Ground is recommended.

|                                                      | М3            | 1     | 3 | Ţ | Α | N | 00.000<br>MHz |

|------------------------------------------------------|---------------|-------|---|---|---|---|---------------|

| Product Series Temperature Range 1: 0°C to +70°C     | 2: -40°C to + | -85°C |   |   |   |   |               |

| 6: -20°C to +70°C  Stability                         |               |       |   |   |   |   |               |

| 3: ±100 ppm<br>5: ±35 ppm<br>8: ±20 ppm              |               |       |   |   |   |   |               |

| Output Type ———<br>F: Fixed                          | T: Tristate   |       |   |   |   |   |               |

| Symmetry/Logic Con A: 40/60 HCMOS/TTI C: 45/55 HCMOS | patibility —  |       |   |   |   |   |               |

| Package/Lead Config<br>N: Leadless                   | urations —    |       |   |   |   |   |               |

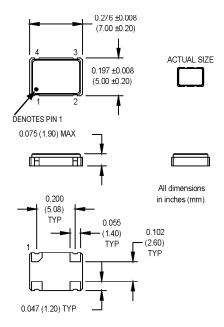

| PIN | FUNCTION        |  |  |  |  |

|-----|-----------------|--|--|--|--|

| 1   | N/C orTri-state |  |  |  |  |

| 2   | Gro und         |  |  |  |  |

| 3   | Output          |  |  |  |  |

| 4   | +Vdd            |  |  |  |  |

## **Tri-state Control Logic**

Pin 1 high or floating: clock signal output. Pin 1 low: output disabled to high impedance.

## **Electrical Specifications**

Standard Operating Conditions • 0°C to +70°C; Vdd = 3.3 ±10% VDC

Storage Temperature • -55°C to +125°C

| Storage lemperature • -55°C to +125°C |          |        |         |         |          |  |  |  |  |  |

|---------------------------------------|----------|--------|---------|---------|----------|--|--|--|--|--|

|                                       | TTL Load |        | нсмо    |         |          |  |  |  |  |  |

| PARAMETERS                            | MIN.     | MAX.   | MIN.    | MAX.    | UNITS    |  |  |  |  |  |

| Frequency Range <sup>1</sup>          | 1.500    | 67.000 | 1.500   | 67.000  | MHz      |  |  |  |  |  |

| Output Load <sup>2</sup>              |          | 2      |         | 15      | TTL/pF   |  |  |  |  |  |

| Symmetry <sup>3</sup>                 | 40/60    | 60/40  | 40/60   | 60/40   | %        |  |  |  |  |  |

| Logic "0" Level                       |          | 0.4    |         | 10% Vdd | >        |  |  |  |  |  |

| Logic "1" Level                       | Vdd-0.4  |        | 90% Vdd |         | <b>V</b> |  |  |  |  |  |

| Rise/Fall Time <sup>4</sup>           |          | 6      |         | 6       | nS       |  |  |  |  |  |

| Supply Current                        |          |        |         |         |          |  |  |  |  |  |

| 1.500 to 20.000 MHz                   |          | 25     |         | 25      | mA       |  |  |  |  |  |

| 20.001 to 67.000 MHz                  |          | 40     |         | 40      | mA       |  |  |  |  |  |

Because this product is based on AT-strip technology, not all frequencies in the range stated are available Contact the factory for availability of specific frequencies.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

<sup>&</sup>lt;sup>2</sup> TTL load - See load circuit diagram #1. HCMOS load - See load circuit diagram #2.

<sup>&</sup>lt;sup>3</sup>Symmetry is measured at 1.4 V with TTL load, and at 50% Vdd with HCMOS load.

$<sup>^4\</sup>text{Rise/Fall}$  times are measured between 0.4 V and 2.4 V with TTL load, and between 10% Vdd and 90% Vdd with HCMOS load.