www.ti.com SLVS849-JULY 2008

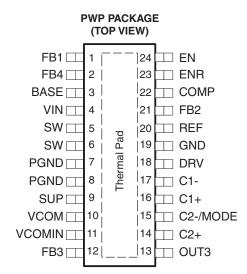

# TRIPLE-OUTPUT LCD SUPPLY WITH LINEAR REGULATOR AND VCOM BUFFER

#### **FEATURES**

- Qualified for Automotive Applications

- 2.7-V to 5.8-V Input Voltage Range

- 1.6-MHz Fixed Switching Frequency

- Three Independently Adjustable Outputs

- Main Output of up to 15 V With < 1% Output Voltage Accuracy

- Virtual Synchronous Converter Technology

- Negative Regulated Charge Pump Driver V<sub>0</sub>2

- Positive Charge Pump Converter V<sub>O</sub>3

- Integrated VCOM Buffer

- Auxiliary 3.3-V Linear Regulator Controller

- Internal Soft Start

- Internal Power-On Sequencing

- Fault Detection of all Outputs

- Thermal Shutdown

- Available in TSSOP-24 PowerPAD™ Package

## **APPLICATIONS**

- TFT LCD Displays for Notebooks

- TFT LCD Displays for Monitors

- Portable DVD Players

- Tablet PCs

- Car Navigation Systems

- Industrial Displays

#### DESCRIPTION

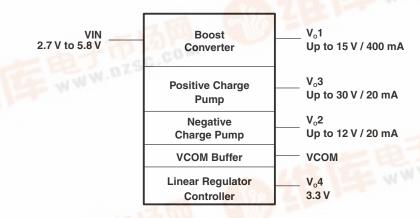

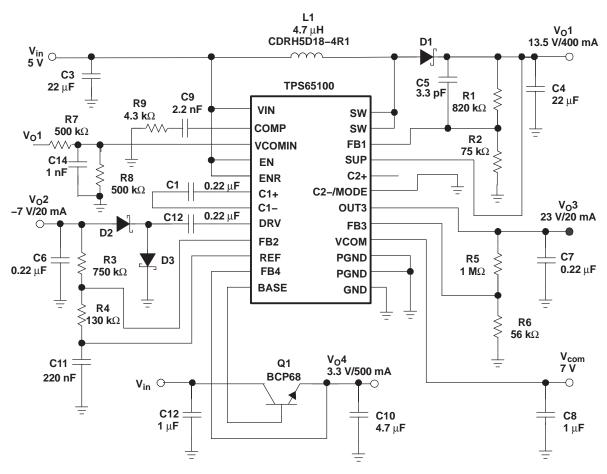

The TPS65100 offers a compact and small power supply solution that provides all three voltages required by thin-film transistor (TFT) LCD displays. The auxiliary linear regulator controller can be used to generate a 3.3-V logic power rail for systems powered by a 5-V supply rail only.

The main output,  $V_O1$ , is a 1.6-MHz fixed-frequency PWM boost converter providing the source-drive voltage for the LCD display. The TPS65100 has a typical switch current limit of 2.3 A. A fully integrated adjustable charge pump doubler/tripler provides the positive LCD gate-drive voltage. An externally adjustable negative charge pump provides the negative gate-drive voltage. Due to the high 1.6-MHz switching frequency of the charge pumps, inexpensive and small 220-nF capacitors can be used.

The TPS65100 has an integrated VCOM buffer to power the LCD backplane. For LCD panels powered by 5 V only, the TPS65100 has a linear regulator controller using an external transistor to provide a regulated 3.3-V output for the digital circuits. For maximum safety, the TPS65100 goes into shutdown as soon as one of the outputs is out of regulation. The device can be enabled again by toggling the input or the enable (EN) pin to GND.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

df.dzsc.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

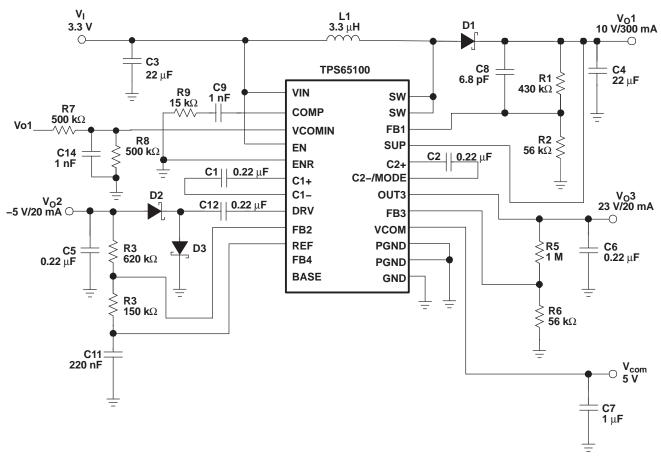

## **TYPICAL APPLICATION CIRCUIT**

## ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> |              | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|--------------|-----------------------|------------------|

| -40°C to 125°C | TSSOP – PWP            | Reel of 2000 | TPS65100QPWPRQ1       | 65100Q           |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- (2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

SLVS849-JULY 2008

<u>₩豐物\*PS65100 Q1"供应商</u>

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

| Voltage range on pin VIN <sup>(2)</sup>                        | -0.3 V to 6 V                 |                                  |

|----------------------------------------------------------------|-------------------------------|----------------------------------|

| Voltage range on pins V <sub>O</sub> 1, SUP, PG <sup>(2)</sup> |                               | –0.3 V to 15.5 V                 |

| Voltage range on pins EN, MODE, ENR (2)                        |                               | –0.3 V to V <sub>I</sub> + 0.3 V |

| Voltage on pin VCOMIN                                          |                               | 14 V                             |

| Voltage on pin SW <sup>(2)</sup>                               | 20 V                          |                                  |

| Continuous power dissipation                                   | See Dissipation Ratings Table |                                  |

| Operating junction temperature range                           | -40°C to 150°C                |                                  |

| Storage temperature range                                      |                               | –65°C to 150°C                   |

| Lead temperature (soldering, 10 seconds)                       |                               | 260°C                            |

|                                                                | Human-Body Model (HBM)        | 2000 V                           |

| Electrostatic discharge (ESD) rating                           | Machine Model (MM)            | 100 V                            |

|                                                                | Charged-Device Model (CDM)    | 1000 V                           |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **DISSIPATION RATINGS**

| PACKAGE      | $R\theta_{JA}$           | T <sub>A</sub> ≤ 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|--------------|--------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 24-pin TSSOP | 30.13°C/W (PWP soldered) | 3.3 W                                 | 1.83 W                                | 1.32 W                                |

## RECOMMENDED OPERATING CONDITIONS

|                |                                        | MIN | TYP | MAX | UNIT |

|----------------|----------------------------------------|-----|-----|-----|------|

| VIN            | Input voltage                          | 2.7 |     | 5.8 | V    |

| L              | Inductor <sup>(1)</sup>                |     | 4.7 |     | μН   |

| T <sub>A</sub> | Operating free-air temperature         | -40 |     | 125 | °C   |

| $T_J$          | Operating virtual-junction temperature | -40 |     | 125 | °C   |

<sup>(1)</sup> See the Application Information section for further information.

Copyright © 2008, Texas Instruments Incorporated

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

**INSTRUMENTS**

## **ELECTRICAL CHARACTERISTICS**

$V_{in} = 3.3 \text{ V}$ , EN = VIN,  $V_{O}1 = 10 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ , typical values are at  $T_{A} = 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                                   | PARAMETER                                  | TEST CONDITIONS                                                                                                                          | MIN   | TYP   | MAX   | UNIT    |  |

|-----------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------|--|

| SUPPLY (                          | CURRENT                                    |                                                                                                                                          |       |       |       |         |  |

| V <sub>i</sub>                    | Input voltage                              |                                                                                                                                          | 2.7   |       | 5.8   | V       |  |

| I <sub>Q</sub>                    | Quiescent current into VIN                 | ENR = VCOMIN = GND, V <sub>O</sub> 3 = 2 × V <sub>O</sub> 1,<br>Boost converter not switching                                            |       | 0.7   | 0.9   | mA      |  |

|                                   | Charge pump quiescent current              | $V_{O}1 = SUP = 10 \text{ V}, V_{O}3 = 2 \times V_{O}1$                                                                                  |       | 1.7   | 2.7   | A       |  |

| <sup>I</sup> QCharge              | into ŠUP                                   | $V_01 = SUP = 10 \text{ V}, V_03 = 3 \times V_01$                                                                                        |       | 3.9   | 6     | mA      |  |

| I <sub>QVCOM</sub>                | VCOM quiescent current into SUP            | ENR = GND, V <sub>O</sub> 1 = SUP = 10 V                                                                                                 |       | 750   | 1300  | μΑ      |  |

| I <sub>QEN</sub>                  | LDO controller quiescent current into VIN  | ENR = VIN, EN = GND                                                                                                                      |       | 300   | 800   | μΑ      |  |

| I <sub>SD</sub>                   | Shutdown current into VIN                  | EN = ENR = GND                                                                                                                           |       | 1     | 10    | μΑ      |  |

| V <sub>UVLO</sub>                 | Undervoltage lockout threshold             | VIN falling                                                                                                                              |       | 2.2   | 2.4   | V       |  |

|                                   | Thermal shutdown                           | Temperature rising                                                                                                                       |       | 160   |       | °C      |  |

| LOGIC SI                          | GNALS EN, ENR                              |                                                                                                                                          |       |       |       |         |  |

| V <sub>IH</sub>                   | High-level input voltage                   |                                                                                                                                          | 1.5   |       |       | V       |  |

| $V_{IL}$                          | Low-level input voltage                    |                                                                                                                                          |       |       | 0.4   | V       |  |

| I <sub>lleak</sub>                | Input leakage current                      | EN = GND or VIN                                                                                                                          |       | 0.01  | 0.1   | μΑ      |  |

| MAIN BO                           | OST CONVERTER                              |                                                                                                                                          |       |       |       |         |  |

| V <sub>O</sub> 1                  | Output voltage range                       |                                                                                                                                          | 5     |       | 15    | V       |  |

| V <sub>O</sub> 1 – V <sub>I</sub> | Minimum input to output voltage difference |                                                                                                                                          | 1     |       |       | V       |  |

| $V_{REF}$                         | Reference voltage                          |                                                                                                                                          | 1.205 | 1.213 | 1.223 | V       |  |

| $V_{FB}$                          | Feedback regulation voltage                |                                                                                                                                          | 1.133 | 1.146 | 1.154 | V       |  |

| I <sub>FB</sub>                   | Feedback input bias current                |                                                                                                                                          |       | 10    | 100   | nA      |  |

|                                   | N-MOSFET on-resistance (Q1)                | V <sub>O</sub> 1 = 10 V, I <sub>sw</sub> = 500 mA                                                                                        |       | 195   | 290   |         |  |

| r <sub>DS(ON)</sub>               |                                            | V <sub>O</sub> 1 = 5 V, I <sub>sw</sub> = 500 mA                                                                                         |       | 285   | 420   | mΩ      |  |

| I <sub>LIM</sub>                  | N-MOSFET switch current limit (Q1)         |                                                                                                                                          | 1.6   | 2.3   | 2.7   | Α       |  |

|                                   | D MOCFET on resistance (OO)                | V <sub>O</sub> 1 = 10 V, I <sub>sw</sub> = 100 mA                                                                                        |       | 9     | 15    | - Ω     |  |

| r <sub>DS(ON)</sub>               | P-MOSFET on-resistance (Q2)                | V <sub>O</sub> 1 = 5 V, I <sub>sw</sub> = 100 mA                                                                                         |       | 14    | 22    |         |  |

| I <sub>MAX</sub>                  | Maximum P-MOSFET peak switch current       |                                                                                                                                          |       |       | 1     | Α       |  |

| I <sub>leak</sub>                 | Switch leakage current                     | V <sub>sw</sub> = 15 V                                                                                                                   |       | 1     | 10    | μΑ      |  |

| _                                 | On sillator for successive                 | 0°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                             | 1.295 | 1.6   | 2.1   | N 41 1- |  |

| f <sub>SW</sub>                   | Oscillator frequency                       | -40°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                           | 1.191 | 1.6   | 2.1   | MHz     |  |

|                                   | Line regulation                            | $2.7 \text{ V} \le \text{V}_{\text{I}} \le 5.7 \text{ V}, \text{I}_{\text{load}} = 100 \text{ mA}$                                       |       | 0.012 |       | %/V     |  |

|                                   | Load regulation                            | 0 mA ≤ I <sub>O</sub> ≤ 300 mA                                                                                                           |       | 0.2   |       | %/A     |  |

| NEGATIV                           | E CHARGE PUMP V <sub>O</sub> 2             |                                                                                                                                          |       |       |       |         |  |

| V <sub>O</sub> 2                  | Output voltage range                       |                                                                                                                                          | -2    |       |       | V       |  |

| $V_{ref}$                         | Reference voltage                          |                                                                                                                                          | 1.205 | 1.213 | 1.219 | V       |  |

| $V_{FB}$                          | Feedback regulation voltage                |                                                                                                                                          | -36   | 0     | 36    | mV      |  |

| $I_{FB}$                          | Feedback input bias current                |                                                                                                                                          |       | 10    | 100   | nA      |  |

|                                   | Q8 P-channel switch r <sub>DS(ON)</sub>    | I <sub>O</sub> = 20 mA                                                                                                                   |       | 4.3   | 8     | Ω       |  |

| r <sub>DS(ON)</sub>               | Q9 N-channel switch r <sub>DS(ON)</sub>    | 10 = 20 IIIA                                                                                                                             |       | 2.9   | 4.4   | 12      |  |

| I <sub>O</sub>                    | Maximum output current                     |                                                                                                                                          | 20    |       |       | mA      |  |

|                                   | Line regulation                            | $7 \text{ V} \le \text{V}_{\text{O}} 1 \le 15 \text{ V}, \text{ I}_{\text{load}} = 10 \text{ mA}, \text{ V}_{\text{O}} 2 = -5 \text{ V}$ |       | 0.09  |       | %/V     |  |

| -                                 | Load regulation                            | $1 \text{ mA} \le I_O \le 20 \text{ mA}, V_O 2 = -5 \text{ V}$                                                                           |       | 0.126 | -     | %/m/    |  |

www.描omps65100 Q1"供应商

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{in} = 3.3 \text{ V}$ , EN = VIN,  $V_{O}1 = 10 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ , typical values are at  $T_{A} = 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                        | PARAMETER                                                                                                      | TEST CONDITIONS                                                                                                                           | MIN   | TYP                        | MAX          | UNIT |

|------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|--------------|------|

| POSITIVE               | CHARGE PUMP V <sub>O</sub> 3                                                                                   |                                                                                                                                           |       |                            |              |      |

| V <sub>O</sub> 3       | Output voltage range                                                                                           |                                                                                                                                           |       |                            | 30           | V    |

| $V_{ref}$              | Reference voltage                                                                                              |                                                                                                                                           | 1.205 | 1.213                      | 1.219        | V    |

| V <sub>FB</sub>        | Feedback regulation voltage                                                                                    |                                                                                                                                           | 1.187 | 1.214                      | 1.238        | V    |

| I <sub>FB</sub>        | Feedback input bias current                                                                                    |                                                                                                                                           |       | 10                         | 100          | nA   |

|                        | Q3 P-channel switch r <sub>DS(ON)</sub>                                                                        |                                                                                                                                           |       | 9.9                        | 15.5         |      |

| _                      | Q4 N-channel switch r <sub>DS(ON)</sub>                                                                        |                                                                                                                                           |       | 1.1                        | 1.8          | _    |

| r <sub>DS(ON)</sub>    | Q5 P-channel switch r <sub>DS(ON)</sub>                                                                        | I <sub>O</sub> = 20 mA                                                                                                                    |       | 4.6                        | 8.5          | Ω    |

|                        | Q6 N-channel switch r <sub>DS(ON)</sub>                                                                        |                                                                                                                                           |       | 1.2                        | 2.2          |      |

| V <sub>d</sub>         | D1–D4 Shottky diode forward voltage                                                                            | I <sub>D1-D4</sub> = 40 mA                                                                                                                |       | 610                        | 720          | mV   |

| lo                     | Maximum output current                                                                                         |                                                                                                                                           | 20    |                            |              | mA   |

|                        | Line regulation                                                                                                | $10 \text{ V} \le \text{V}_{\text{O}} 1 \le 15 \text{ V}, \text{ I}_{\text{load}} = 10 \text{ mA}, \text{ V}_{\text{O}} 3 = 27 \text{ V}$ |       | 0.56                       |              | %/V  |

|                        | Load regulation                                                                                                | 1 mA $\leq$ I <sub>O</sub> $\leq$ 20 mA, V <sub>O</sub> 3 = 27 V                                                                          |       | 0.05                       |              | %/mA |

| LINEAR F               | REGULATOR CONTROLLER V <sub>0</sub> 4                                                                          | ·                                                                                                                                         |       |                            |              | Į.   |

| V <sub>O</sub> 4       | Output voltage                                                                                                 | $4.5 \text{ V} \le \text{V}_1 \le 5.5 \text{ V}, 10 \text{ mA} \le \text{I}_0 \le 500 \text{ mA}$                                         | 3.2   | 3.3                        | 3.4          | V    |

| I <sub>BASE</sub>      | Maria de la compania | $V_1 - V_0 4 - V_{BE} \ge 0.5 \text{ V}^{-(1)}$                                                                                           | 13.5  | 19                         |              | A    |

|                        | Maximum base drive current                                                                                     | $V_1 - V_0 4 - V_{BE} \ge 0.75 \text{ V}^{(1)}$                                                                                           | 20    | 27                         |              | mA   |

|                        | Line regulation                                                                                                | 4.75 V ≤ V <sub>I</sub> ≤ 5.5 V, I <sub>load</sub> = 500 mA                                                                               |       | 0.186                      |              | %/V  |

|                        | Load regulation                                                                                                | 1 mA ≤ I <sub>O</sub> ≤ 500 mA, V <sub>I</sub> = 5 V                                                                                      |       | 0.064                      |              | %/A  |

|                        | Start up current                                                                                               | V <sub>O</sub> 4 ≤ 0.8 V                                                                                                                  | 11    | 20                         | 25           | mA   |

| VCOM BU                | JFFER                                                                                                          |                                                                                                                                           | 1     |                            |              |      |

| $V_{cm}$               | Common mode input range                                                                                        |                                                                                                                                           | 2.25  |                            | $(V_01) - 2$ | V    |

| V <sub>os</sub>        | Input offset voltage                                                                                           | I <sub>O</sub> = 0 mA                                                                                                                     | -25   |                            | +25          | mV   |

|                        |                                                                                                                | I <sub>O</sub> = ±25 mA                                                                                                                   | -30   |                            | 37           |      |

|                        | DO Las describation                                                                                            | I <sub>O</sub> = ±50 mA                                                                                                                   | -45   |                            | 55           |      |

|                        | DC Load regulation                                                                                             | I <sub>O</sub> = ±100 mA                                                                                                                  | -72   |                            | 85           | mV   |

|                        |                                                                                                                | I <sub>O</sub> = ±150 mA                                                                                                                  | -97   |                            | 110          |      |

| I <sub>B</sub>         | VCOMIN Input bias current                                                                                      |                                                                                                                                           | -300  | -30                        | 300          | nA   |

|                        |                                                                                                                | V <sub>O</sub> 1 = 15 V                                                                                                                   | 1.2   |                            |              | Α    |

| I <sub>peak</sub>      | Peak output current                                                                                            | V <sub>O</sub> 1 = 10 V                                                                                                                   | 0.65  |                            |              | Α    |

|                        |                                                                                                                | V <sub>O</sub> 1 = 5 V                                                                                                                    | 0.15  |                            |              | Α    |

| FAULT PI               | ROTECTION THRESHOLDS                                                                                           |                                                                                                                                           |       |                            |              |      |

| V <sub>(th, Vo1)</sub> |                                                                                                                | V <sub>O</sub> 1 Rising                                                                                                                   | -12   | −8.75%<br>V <sub>O</sub> 1 | -6           | V    |

| V <sub>(th, Vo2)</sub> | Shutdown threshold                                                                                             | V <sub>O</sub> 2 Rising                                                                                                                   | -13   | -9% V <sub>O</sub> 2       | -5           | V    |

| V <sub>(th, Vo3)</sub> |                                                                                                                | V <sub>O</sub> 3 Rising                                                                                                                   | -11   | -8% V <sub>O</sub> 3       | -5           | V    |

<sup>(1)</sup> With  $V_I$  = supply voltage of the TPS65100,  $V_O4$  = output voltage of the regulator,  $V_{BE}$  = basis emitter voltage of external transistor

Copyright © 2008, Texas Instruments Incorporated

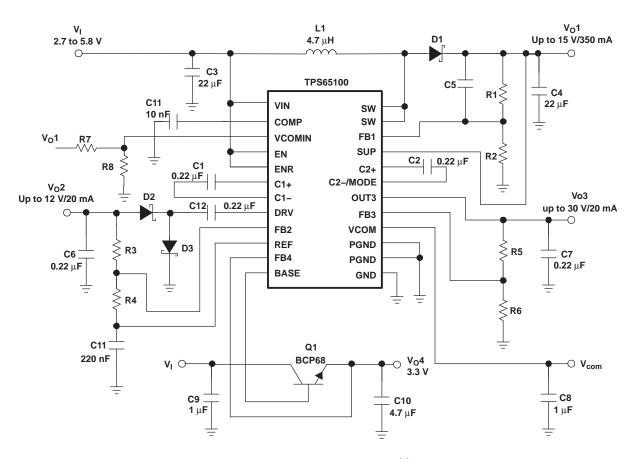

## **Terminal Functions**

| TERMIN      | AL   |     | DECORPTION                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |  |  |

| VIN         | 4    | I   | Input voltage pin of the device                                                                                                                                                                                                                                                                                                     |  |  |

| EN          | 24   | I   | Enable pin of the device. This pin should be terminated and not be left floating. A logic high enables the device and a logic low shuts down the device.                                                                                                                                                                            |  |  |

| COMP        | 22   |     | Compensation pin for the main boost converter. A small capacitor is connected to this pin.                                                                                                                                                                                                                                          |  |  |

| VCOMIN      | 11   | I   | Positive input terminal of the VCOM buffer. When the VCOM buffer is not used, this terminal can be connected to GND to reduce the overall quiescent current of the IC.                                                                                                                                                              |  |  |

| ENR         | 23   | I   | Enable pin of the linear regulator controller. This pin should be terminated and not be left floating. Logic high enables the regulator and a logic low puts the regulator in shutdown.                                                                                                                                             |  |  |

| C1+         | 16   |     | Positive terminal of the charge pump flying capacitor                                                                                                                                                                                                                                                                               |  |  |

| C1-         | 17   |     | Negative terminal of the charge pump flying capacitor                                                                                                                                                                                                                                                                               |  |  |

| DRV         | 18   | 0   | External charge pump driver                                                                                                                                                                                                                                                                                                         |  |  |

| FB2         | 21   | I   | Feedback pin of negative charge pump                                                                                                                                                                                                                                                                                                |  |  |

| REF         | 20   | 0   | Internal reference output typically 1.23 V                                                                                                                                                                                                                                                                                          |  |  |

| FB4         | 2    | I   | Feedback pin of the linear regulator controller. The linear regulator controller is set to a fixed output voltage of 3.3 V or 3 V depending on the version.                                                                                                                                                                         |  |  |

| BASE        | 3    | 0   | Base drive output for the external transistor                                                                                                                                                                                                                                                                                       |  |  |

| GND         | 19   |     | Ground                                                                                                                                                                                                                                                                                                                              |  |  |

| PGND        | 7, 8 |     | Power ground                                                                                                                                                                                                                                                                                                                        |  |  |

| VCOM        | 10   | 0   | VCOM buffer output                                                                                                                                                                                                                                                                                                                  |  |  |

| FB3         | 12   | I   | Feedback pin of positive charge pump                                                                                                                                                                                                                                                                                                |  |  |

| OUT3        | 13   | 0   | Positive charge pump output                                                                                                                                                                                                                                                                                                         |  |  |

| C2-/MODE    | 15   |     | Negative terminal of the charge pump flying capacitor and charge pump MODE pin. If the flying capacitor is connected to this pin, the converter operates in a voltage tripler mode. If the charge pump needs to operate in a voltage doubler mode, the flying capacitor is removed and the C2–/MODE pin should be connected to GND. |  |  |

| C2+         | 14   |     | Positive terminal for the charge pump flying capacitor. If the device runs in voltage doubler mode, this pin should be left open.                                                                                                                                                                                                   |  |  |

| SUP         | 9    | I   | Supply of the positive and negative charge pump, boost converter gate-drive circuit, and VCOM buffer. Should be connected to the output of the main boost converter and cannot be connected to any other voltage source. For performance reasons, do not connect a bypass capacitor directly to this pin.                           |  |  |

| FB1         | 1    | I   | Feedback pin of the boost converter                                                                                                                                                                                                                                                                                                 |  |  |

| SW          | 5, 6 | I   | Switch pin of the boost converter                                                                                                                                                                                                                                                                                                   |  |  |

| Thermal pad |      |     | The exposed thermal pad should be connected to the power ground (PGND).                                                                                                                                                                                                                                                             |  |  |

<u>₩實特學 PS65100 Q1"供应商</u>

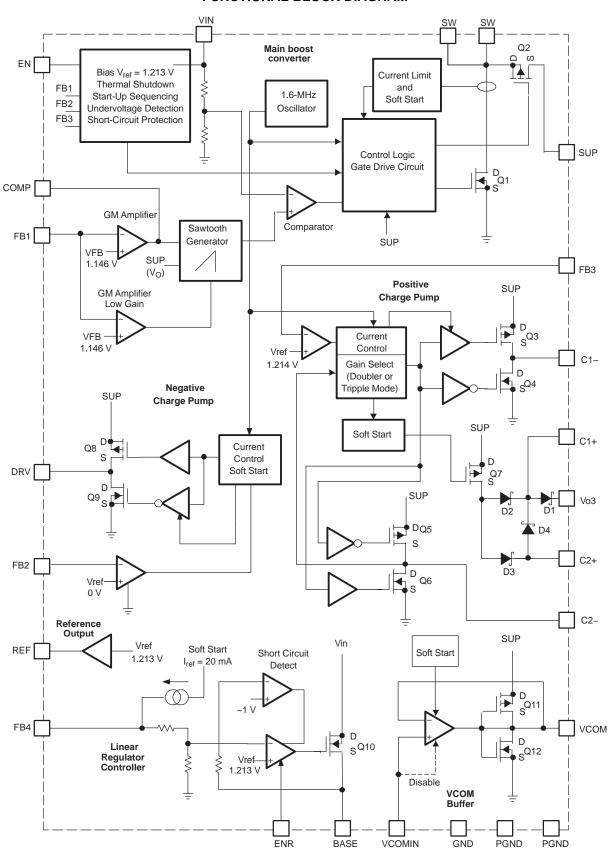

#### **FUNCTIONAL BLOCK DIAGRAM**

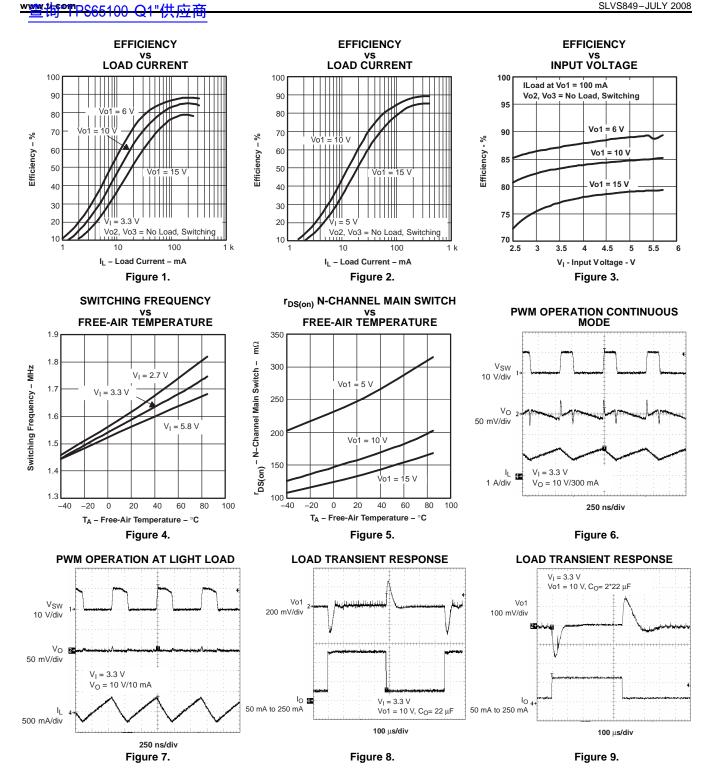

## TYPICAL CHARACTERISTICS

# **Table of Graphs**

|                     |                                                    |                                                   | FIGURE |

|---------------------|----------------------------------------------------|---------------------------------------------------|--------|

| Main Boo            | ost Converter                                      |                                                   |        |

|                     | Efficiency, main boost converter V <sub>O</sub> 1  | vs Load current                                   | 1      |

| η                   | Efficiency, main boost converter V <sub>O</sub> 1  | vs Load current                                   | 2      |

|                     | Efficiency                                         | vs Input voltage                                  | 3      |

| f <sub>sw</sub>     | Switching frequency                                | vs Free-air temperature                           | 4      |

| r <sub>DS(on)</sub> | r <sub>DS(on)</sub> N-channel main switch Q1       | vs Free-air temperature                           | 5      |

|                     | PWM operation, continuous mode                     |                                                   | 6      |

|                     | PWM operation at light load                        |                                                   | 7      |

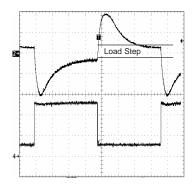

|                     | Load transient response, $C_0 = 22 \mu F$          |                                                   | 8      |

|                     | Load transient response, $C_0 = 2 \times 22 \mu F$ |                                                   | 9      |

|                     | Power-up sequencing                                |                                                   | 10     |

|                     | Soft start V <sub>O</sub> 1                        |                                                   | 11     |

| Negative            | Charge Pump                                        |                                                   |        |

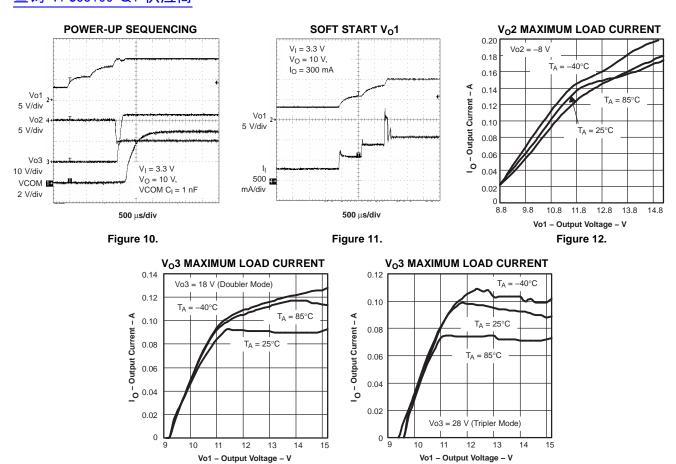

| I <sub>max</sub>    | V <sub>O</sub> 2 Maximum load current              | vs Output voltage V <sub>O</sub> 1                | 12     |

| Positive            | Charge Pump                                        |                                                   |        |

| I <sub>max</sub>    | V <sub>O</sub> 3 Maximum load current              | vs Output voltage V <sub>O</sub> 1 (doubler mode) | 13     |

| I <sub>max</sub>    | V <sub>O</sub> 3 Maximum load current              | vs Output voltage V <sub>O</sub> 1 (tripler mode) | 14     |

Figure 14.

Figure 13.

<del>"≝悔"PS65100 Q1"供应商</del>

SLVS849-JULY 2008

#### DETAILED DESCRIPTION

The TPS65100 consists of a main boost converter operating with a fixed switching frequency of 1.6 MHz to allow for small external components. The boost converter output voltage Vo1 is also the input voltage, connected via the pin SUP, for the positive and negative charge pumps and the bias supply for the VCOM buffer. The linear regulator controller is independent from this system with its own enable pin. This design allows the linear regulator controller to continue to operate while the other supply rails are disabled or in shutdown due to a fault condition on one of their outputs. See the functional block diagram for more information.

## **Main Boost Converter**

The main boost converter operates with PWM and a fixed switching frequency of 1.6 MHz. The converter uses a unique fast-response voltage-mode controller scheme with input voltage feedforward. This achieves excellent line and load regulation (0.2%/A load regulation typical) and allows the use of small external components. To add higher flexibility to the selection of external component values the device uses external loop compensation. Although the boost converter looks like a nonsynchronous boost converter topology operating in discontinuous mode at light load, the TPS65100 maintains continuous conduction even at light load currents. This is accomplished using the Virtual Synchronous Converter Technology for improved load transient response. This architecture uses an external Schottky diode and an integrated MOSFET in parallel connected between SW and SUP (see the functional block diagram). The integrated MOSFET Q2 allows the inductor current to become negative at light load conditions. For this purpose, a small integrated P-channel MOSFET with typically 10-Ω r<sub>DSon</sub> is sufficient. When the inductor current is positive, the external Schottky diode with the lower forward voltage conducts the current. This causes the converter to operate with a fixed frequency in continuous conduction mode over the entire load current range. This avoids the ringing on the switch pin as seen with a standard nonsynchronous boost converter and allows a simpler compensation for the boost converter.

#### **VCOM Buffer**

VCOMIN is the input of the VCOM buffer. If the VCOM buffer is not required for certain applications, it is possible to shut down the VCOM buffer by connecting VCOMIN to ground, reducing the overall guiescent current. The VCOM buffer features soft start, avoiding a large voltage drop at V<sub>0</sub>1 during start-up. The VCOMIN cannot be pulled dynamically to ground during operation.

## Enable and Power On Sequencing (EN, ENR)

The device has two enable pins. These pins should be terminated and should not be left floating to prevent unpredictable operation. Pulling the enable pin (EN) high enables the device and starts the power-on sequencing with the main boost converter V<sub>O</sub>1 coming up first, then the negative and positive charge pump and the VCOM buffer. If the VCOMIN pin is held low, the VCOM buffer remains disabled. The linear regulator has an independent enable pin (ENR). Pulling this pin low disables the regulator, and pulling this pin high enables this regulator.

If the enable pin EN is pulled high, the device starts its power on sequencing. The main boost converter starts up first with its soft start. If the output voltage has reached 91.25% of its output voltage, the negative charge pump comes up next. The negative charge pump starts with a soft start and when the output voltage has reached 91% of the nominal value, the positive charge pump comes up with a soft start. The VCOM buffer is enabled as soon as the positive charge pump has reached its nominal value and VCOMIN is greater than typically 1.0 V. Pulling the enable pin low shuts down the device. Depended on load current and output capacitance, each of the outputs goes down.

## **Positive Charge Pump**

The TPS65100 has a fully regulated integrated positive charge pump generating V<sub>O</sub>3. The input voltage for the charge pump is applied to the SUP pin that is equal to the output of the main boost converter V<sub>O</sub>1. The charge pump is capable of supplying a minimum load current of 20 mA. Depending on the voltage difference between V<sub>0</sub>1 and V<sub>0</sub>3 higher load currents are possible (see Figure 13 and Figure 14).

Copyright © 2008, Texas Instruments Incorporated

SL塗額\*\*件%889100 Q1"供应商

www.ti.com

## **Negative Charge Pump**

The TPS65100 has a regulated negative charge pump using two external Schottky diodes. The input voltage for the charge pump is applied to the SUP pin that is connected to the output of the main boost converter  $V_O1$ . The charge pump inverts the main boost converter output voltage and is capable of supplying a minimum load current of 20 mA. Depending on the voltage difference between  $V_O1$  and  $V_O2$ , higher load currents are possible (see Figure 12).

## **Linear Regulator Controller**

The TPS65100 includes a linear regulator controller to generate a 3.3-V rail which is useful when the system is powered from a 5-V supply. The regulator is independent from the other voltage rails of the device and has its own enable (ENR). Since most of the systems require this voltage rail to come up first it is recommended to use a R-C delay on EN. This delays the start-up of the main boost converter which will reduce the inrush current as well.

#### **Soft Start**

The main boost converter as well as the charge pumps, linear regulator, and VCOM buffer have an internal soft start. This avoids heavy voltage drops at the input voltage rail or at the output of the main boost converter  $V_01$  during start-up caused by high inrush currents (see Figure 10 and Figure 11). During softstart of the main boost converter  $V_01$ , the internal current limit threshold is increased in three steps. The device starts with the first step, where the current limit is set to 2/5 of the typical current limit (2/5 of 2.3 A) for 1024 clock cycles, then increased to 3/5 of the current limit for 1024 clock cycles, and finally raised to the full current limit.

#### **Fault Protection**

All the outputs of the TPS65100 have short-circuit detection that can force the device into shutdown. The main boost converter has overvoltage and undervoltage protection. If the output voltage Vo1 rises above the overvoltage protection threshold of 5% of V<sub>0</sub>1 (typical), the device stops switching but remains operational. When the output voltage falls below this threshold again, the converter continues operation. When the output voltage falls below power good threshold of 8.75% of  $V_01$  (typical), in case of a short-circuit condition, then the TPS65100 goes into shutdown. Because there is a direct pass from the input to the output through the diode, the short-circuit condition remains. If this condition needs to be avoided, a fuse at the input or an output disconnect using a single transistor and resistor is required. The negative and positive charge pumps have an undervoltage lockout to protect the LCD panel from possible latchup conditions in the event of a short-circuit condition or faulty operation. When the negative output voltage is above 9.5% (typical) of its output voltage (closer to ground), the device enters shutdown. When the positive charge pump output voltage V<sub>O</sub>3 is below 8% (typical) of its output voltage, the device goes into shutdown as well. See the electrical characteristics table under fault protection thresholds. The device can be enabled again by toggling the enable pin (EN) below 0.4 V or by cycling the input voltage below the UVLO of 1.7 V. The linear regulator reduces the output current to typical 20 mA under a short-circuit condition when the output voltage is < 1 V (typical). See the functional block diagram. The linear regulator does not go into shutdown under a short-circuit condition.

#### **Thermal Shutdown**

A thermal shutdown is implemented to prevent damage due to excessive heat and power dissipation. Typically, the thermal shutdown threshold is  $160^{\circ}$ C. If this temperature is reached, the device goes into shutdown. The device can be enabled by toggling the enable pin to low and back to high or by cycling the input voltage to GND and back to  $V_{I}$  again.

SLVS849-JULY 2008

#### **APPLICATION INFORMATION**

#### **BOOST CONVERTER DESIGN PROCEDURE**

The first step in the design procedure is to calculate the maximum possible output current of the main boost converter under certain input and output voltage conditions. This example is for a 3.3-V to 10-V conversion:  $V_{in} = 3.3 \text{ V}$ ,  $V_{out} = 10 \text{ V}$ , Switch voltage drop  $V_{sw} = 0.5 \text{ V}$ , Schottky diode forward voltage  $V_D = 0.8 \text{ V}$

1. Duty cycle

$$D = \frac{V_{out} + V_{D} - V_{in}}{V_{out} + V_{D} - V_{sw}} = \frac{10 \text{ V} + 0.8 \text{ V} - 3.3 \text{ V}}{10 \text{ V} + 0.8 \text{ V} - 0.5 \text{ V}} = 0.73$$

2. Average inductor current

$$I_L = \frac{I_{out}}{1 - D} = \frac{300 \text{ mA}}{1 - 0.73} = 1.11 \text{ A}$$

3. Inductor peak-to-peak ripple current

$$\Delta i_L = \frac{\left[V_{in} - V_{SW}\right] \times D}{f_S \times L} = \frac{\left(3.3 \text{ V} - 0.5 \text{ V}\right) \times 0.73}{1.6 \text{ MHz} \times 4.2 \text{ }\mu\text{H}} = 304 \text{ mA}$$

4. Peak switch current

$$I_{\text{swpeak}} = I_{\text{L}} + \frac{\Delta i_{\text{L}}}{2} = 1.11 \text{ A} + \frac{304 \text{ mA}}{2} = 1.26 \text{ A}$$

The integrated switch, the inductor, and the external Schottky diode must be able to handle the peak switch current. The calculated peak switch current must be equal to or lower than the minimum N-MOSFET switch current limit specified in *electrical characteristics*. If the peak switch current is higher, the converter cannot support the required load current. This calculation must be done for the minimum input voltage, where the peak switch current is highest. The calculation includes conduction losses like switch  $r_{DSon}$  (0.5 V) and diode forward drop voltage losses (0.8 V). Additional switching losses, inductor core and winding losses, etc., require a slightly higher peak switch current in the actual application. This calculation still allows for good design and component selection.

#### Inductor Selection

Several inductors work with the TPS65100 and, particularly with the external compensation, performance can be adjusted to application requirements. The main parameter for inductor selection is the saturation current of the inductor, which should be higher than the peak switch current as previously calculated, with additional margin to allow for heavy load transients and extreme start-up conditions. Another method is to choose an inductor with a saturation current at least as high as the minimum switch current limit of 1.6 A. The different switch-current limits allow selection of a physically smaller inductor when less output current is required. Another important parameter is inductor dc resistance. Usually, the lower the dc resistance, the higher the efficiency. However, inductor dc resistance is not the only parameter determining the efficiency. Especially for a boost converter where the inductor is the energy storage element, the type and material of the inductor influences the efficiency as well. At the high switching frequency of 1.6 MHz, inductor core losses, proximity effects, and skin effects are more important. Usually, an inductor with a larger form factor yields higher efficiency. The efficiency difference between different inductors can vary between 2% to 10%. Inductor values between 3.3  $\mu$ H and 6.8  $\mu$ H are a good choice, but other values can be used. Possible inductors are shown in Table 1.

**Table 1. Inductor Selection**

| INDUCTOR VALUE | COMPONENT SUPPLIER          | DIMENSIONS (mm)             | ISAT/DCR                         |

|----------------|-----------------------------|-----------------------------|----------------------------------|

| 4.7 μΗ         | Coilcraft DO1813P-472HC     | 8,89 × 6,1 × 5              | 2.6 A/54 mΩ                      |

| 4.2 μΗ         | Sumida CDRH5D28 4R2         | $5,7\times5,7\times3$       | $2.2~\text{A}/23~\text{m}\Omega$ |

| 4.7 μΗ         | Sumida CDC5D23 4R7          | $6 \times 6 \times 2,5$     | 1.6 A/48 mΩ                      |

| 3.3 μΗ         | Wuerth Elektronik 744042003 | $4.8 \times 4.8 \times 2$   | 1.8 A/65 mΩ                      |

| 4.2 μΗ         | Sumida CDRH6D12 4R2         | $6.5 \times 6.5 \times 1.5$ | 1.8 A/60 mΩ                      |

| 3.3 μΗ         | Sumida CDRH6D12 3R3         | 6,5 × 6,5 × 1,5             | 1.9 A/50 mΩ                      |

Copyright © 2008, Texas Instruments Incorporated

## **Output Capacitor Selection**

For the best output voltage filtering, a low ESR output capacitor is recommended. Ceramic capacitors have a low ESR value, but depending on the application, tantalum capacitors can be used as well. A  $22-\mu F$  ceramic output capacitor works for most of the applications. Higher capacitor values can be used to improve the load transient regulation. See Table 2 for selection of the output capacitor. The output voltage ripple can be calculated as:

$$\Delta V_{out} = \frac{I_{out}}{C_{out}} \times \left[ \frac{1}{f_s} - \frac{I_p \times L}{V_{out} + V_d - V_{in}} \right] + I_p \times ESR$$

with:

IP = Peak switch current as calculated in the previous section with I<sub>SW(peak)</sub>.

L = Selected inductor value

I<sub>OUT</sub> = Normal load current

f<sub>s</sub> = Switching frequency

V<sub>d</sub> = Rectifier diode forward voltage (typical 0.3 V)

$C_{OUT}$  = Selected output capacitor

ESR = Output capacitor ESR value

## **Input Capacitor Selection**

For good input voltage filtering, low ESR ceramic capacitors are recommended. A 22-μF ceramic input capacitor is sufficient for most of the applications. For better input voltage filtering, this value can be increased. See Table 2 and the typical applications for input capacitor recommendations.

**Table 2. Input and Output Capacitors Selection**

| CAPACITOR  | VOLTAGE RATING | COMPONENT SUPPLIER        | COMMENTS         |

|------------|----------------|---------------------------|------------------|

| 22 μF/1210 | 16 V           | Taiyo Yuden EMK325BY226MM | C <sub>out</sub> |

| 22 μF/1206 | 6.3 V          | Taiyo Yuden JMK316BJ226   | C <sub>in</sub>  |

#### **Rectifier Diode Selection**

To achieve high efficiency, a Schottky diode should be used. The voltage rating should be higher than the maximum output voltage of the converter. The average forward current should be equal to the average inductor current of the converter. The main parameter influencing the efficiency of the converter is the forward voltage and the reverse leakage current of the diode; both should be as low as possible. Possible diodes are: On Semiconductor MBRM120L, Microsemi UPS120E, and Fairchild Semiconductor MBRS130L.

## **Converter Loop Design and Stability**

The TPS65100 converter loop can be externally compensated and allows access to the internal transconductance error amplifier output at the COMP pin. A small feedforward capacitor across the upper feedback resistor divider speeds up the circuit as well. To test the converter stability and load transient performance of the converter, a load step from 50 mA to 250 mA is applied, and the output voltage of the converter is monitored. Applying load steps to the converter output is a good tool to judge the stability of such a boost converter.

**\*\*室街\*\*\*PS**65100 Q1"供应商

SLVS849-JULY 2008

## **Design Procedure Quick Steps**

- 1. Select the feedback resistor divider to set the output voltage.

- 2. Select the feedforward capacitor to place a zero at 50 kHz.

- 3. Select the compensation capacitor on pin COMP. The smaller the value, the higher the low frequency gain.

- 4. Use a  $50\text{-}k\Omega$  potentiometer in series to  $C_c$  and monitor  $V_{out}$  during load transients. Fine tune the load transient by adjusting the potentiometer. Select a resistor value that comes closest to the potentiometer resistor value. This needs to be done at the highest Vin and highest load current since the stability is most critical at these conditions.

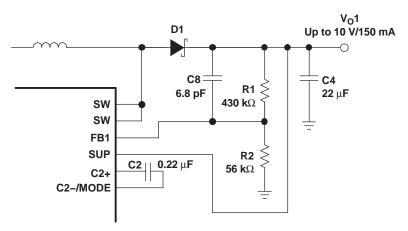

## Setting the Output Voltage and Selecting the Feedforward Capacitor

The output voltage is set by the external resistor divider and is calculated as:

$$V_{out} = 1.146 \text{ V} \times \left[ 1 + \frac{R1}{R2} \right]$$

Across the upper resistor a bypass capacitor is required to speed up the circuit during load transients as shown in Figure 15.

Figure 15. Feedforward Capacitor

Together with R1 the bypass capacitor C8 sets a zero in the control loop at approximately 50 kHz:

$$f_{Z} = \frac{1}{2 \times \pi \times C8 \times R1}$$

A value closest to the calculated value should be used. Larger feedforward capacitor values reduce the load regulation of the converter and cause load steps as shown in Figure 16.

Figure 16. Load Step Caused By A Too Large Feedforward Capacitor Value

Copyright © 2008, Texas Instruments Incorporated

## Compensation

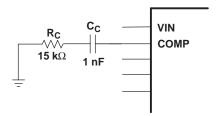

The regulator loop can be compensated by adjusting the external components connected to the COMP pin. The COMP pin is connected to the output of the internal transconductance error amplifier. A typical compensation scheme is shown in Figure 17.

Figure 17. Compensation Network

The compensation capacitor  $C_C$  adjusts the low frequency gain and the resistor value adjusts the high frequency gain. The formula below calculates at what frequency the resistor increases the high frequency gain.

$$f_Z = \frac{1}{2 \times \pi \times Cc \times Rc}$$

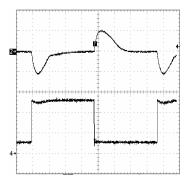

Lower input voltages require a higher gain and therefore a lower compensation capacitor value. A good start is  $C_C = 1$  nF for a 3.3-V input and  $C_C = 2.2$  nF for a 5-V input. If the device operates over the entire input voltage range from 2.7 V to 5.8 V, a large compensation capacitor up to 10 nF is recommended. Figure 18 shows the load transient with a larger compensation capacitor, and Figure 19 shows a smaller compensation capacitor.

Figure 18.  $C_c = 4.7 \text{ nF}$

Figure 19.  $C_c = 1 \text{ nF}$

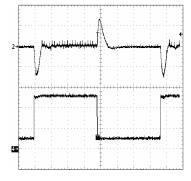

Finally,  $R_c$  needs to be selected. A good practice is to use a 50-k $\Omega$  potentiometer and adjust the potentiometer for best load transient where no oscillations should occur. These tests have to be done at the highest  $V_{in}$  and highest load current because converter stability is most critical under these conditions. Figure 20, Figure 21, and Figure 22 show the fine tuning of the loop with  $R_c$ .

Figure 20. Overcompensated (Damped Oscillation),  $\rm R_{\rm c}$  Is Too Large

Figure 21. Undercompensated (Loop Is Too Slow),  $R_{\text{\tiny C}}$  Is Too Small

Figure 22. Optimum,  $R_{\text{c}}$  Is Ideal

## **Negative Charge Pump**

The negative charge pump provides a regulated output voltage by inverting the main output voltage  $V_0$ 1. The negative charge pump output voltage is set with external feedback resistors.

The maximum load current of the negative charge pump depends on the voltage drop across the external Schottky diodes, the internal on resistance of the charge pump MOSFETS Q8 and Q9, and the impedance of the flying capacitor C12. When the voltage drop across these components is larger than the voltage difference from  $V_O1$  to  $V_O2$ , the charge pump is in dropout, providing the maximum possible output current. Therefore, the higher the voltage difference between  $V_O1$  and  $V_O2$ , the higher the possible load current. See Figure 12 for the possible output current versus boost converter voltage  $V_O1$ .

$$V_{O(min)} = -(V_O - 2 V_D - I_o (2 \times r_{DS(on)Q8} + 2 \times r_{DS(on)Q9} + X_{cflv}))$$

Setting the output voltage:

$$V_{OUT} = -V_{REF} \times \frac{R3}{R4} = -1.213 \text{ V } \times \frac{R3}{R4}$$

R3 = R4 x

$$\frac{|V_{OUT}|}{V_{REF}}$$

= R4 x  $\frac{|V_{OUT}|}{1.213}$

The lower feedback resistor value R4 should be in a range between 40 k $\Omega$  to 120 k $\Omega$  or the overall feedback resistance should be within 500 k $\Omega$  to 1 M $\Omega$ . Smaller values load the reference too heavily and larger values may cause stability problems. The negative charge pump requires two external Schottky diodes. The peak current rating of the Schottky diode has to be twice the load current of the output. For a 20-mA output current, the dual Schottky diode BAT54 or similar is a good choice.

## **Positive Charge Pump**

The positive charge pump can be operated in a voltage doubler mode or a voltage tripler mode depending on the configuration of the C2+ and C2-/MODE pins. Leaving the C2+ pin open and connecting C2-/MODE to GND forces the positive charge pump to operate in a voltage doubler mode. If higher output voltages are required, the positive charge pump can be operated as a voltage tripler. To operate the charge pump in the voltage tripler mode, a flying capacitor needs to be connected to C2+ and C2-/MODE.

The maximum load current of the positive charge pump depends on the voltage drop across the internal Schottky diodes, the internal on resistance of the charge pump MOSFETS, and the impedance of the flying capacitor. When the voltage drop across these components is larger than the voltage difference  $V_O1 \times 2$  to  $V_O3$  (doubler mode) or  $V_O1 \times 3$  to  $V_O3$  (tripler mode), then the charge pump is in dropout, providing the maximum possible output current. Therefore, the higher the voltage difference between  $V_O1 \times 2$  (doubler) or  $V_O1 \times 3$  (tripler) to  $V_O3$ , the higher the possible load current. See Figure 13 and Figure 14 for the output current versus boost converter voltage  $V_O1$  and the following calculations.

Voltage doubler:

$$V_O 3_{max} = 2 \times V_O 1 - (2 V_D + 2 \times Io \times (2 \times r_{DS(on)Q5} + r_{DS(on)Q3} + r_{DS(on)Q4} + X_{C1}))$$

Voltage tripler:

$$V_O 3_{max} = 3 \times V_O 1 - (3 \times V_D + 2 \times Io \times (3 \times r_{DS(on)Q5} + r_{DS(on)Q3} + r_{DS(on)Q4} + X_{C1} + X_{C2}))$$

The output voltage is set by the external resistor divider and is calculated as:

$$V_{out} = 1.214 \times \left[1 + \frac{R5}{R6}\right]$$

$$R5 = R6 \times \left[ \frac{V_{out}}{V_{FB}} - 1 \right] = R6 \times \left[ \frac{V_{out}}{1.214} - 1 \right]$$

**\*\*室街\*\*\*PS65100 Q1"供应商**

SLVS849-JULY 2008

#### **VCOM Buffer**

The VCOM buffer is typically used to drive the backplane of a TFT panel. The VCOM output voltage is typically set to half of the main output voltage  $V_{\rm O}1$  plus a small shift to implement the specific compensation voltage. The TFT video signal gets coupled through the TFT storage capacitor plus the LCD cell capacitance to the output of the VCOM buffer. Because of these, short current pulses in the positive and negative direction appear at the output of the VCOM buffer. To minimize the output voltage ripple caused by the current pulses, a transconductance amplifier having a current source output and an output capacitor is used. The output capacitor supports the high frequency part of the current pulses drawn from the LCD panel. The VCOM buffer only needs to handle the low frequency portion of the current pulses. A 1- $\mu$ F ceramic output capacitor is sufficient for most of the applications. When using other output capacitor values it is important to keep in mind that the output capacitor is part of the VCOM buffer loop stabilization.

The VCOM buffer has an integrated soft start to avoid voltage drops on  $V_{\rm O}1$  during start-up. The soft start is implemented as such that the VCOMIN is held low until the VCOM buffer is fully biased and the common mode range is reached. Then the positive input is released and the VCOM buffer output slowly comes up. Usually a 1-nF capacitor on VCOMIN to GND is used to filter high frequency noise coupled in from  $V_{\rm O}1$ . The size of this capacitor together with the upper feedback resistor value determines the start-up time. The larger the capacitor from VCOMIN to GND, the slower the soft start.

## **Linear Regulator Controller**

The TPS65100 includes a linear regulator controller to generate a 3.3-V rail when the system is powered from a 5-V supply. Because an external npn transistor is required, the input voltage of the TPS65100 applied to VIN needs to be higher than the output voltage of the regulator. To provide a minimum base drive current of 13.5 mA, a minimum internal voltage drop of 500 mV from  $V_{in}$  to  $V_{base}$  is required. This can be translated into a minimum input voltage on VIN for a certain output voltage as the following calculation shows:

$$VIN_{min} = V_O4 + V_{BE} + 0.5 V$$

The base drive current together with the  $h_{FE}$  of the external transistor determines the possible output current. Using a standard npn transistor like the BCP68 allows an output current of 1 A and using the BCP54 allows a load current of 337 mA for an input voltage of 5 V. Other transistors can be used as well depending on the required output current, power dissipation, and PCB space. The device is stable with a 4.7- $\mu$ F ceramic output capacitor. Larger output capacitor values can be used to improve the load transient response when higher load currents are required.

## **Layout Considerations**

For all switching power supplies, the layout is an important step in the design, especially at high-peak currents and switching frequencies. If the layout is not carefully designed, the regulator might show stability and EMI problems. Therefore, the traces carrying high-switching currents should be routed first using wide and short traces. The input filter capacitor should be placed as close as possible to the input pin VIN of the IC. See the evaluation module (EVM) for a layout example.

#### **Thermal Information**

An influential component of thermal performance of a package is board design. To take full advantage of the heat dissipation abilities of the PowerPAD package with exposed thermal die, a board that acts similar to a heat sink and allows the use of an exposed (and solderable) deep downset pad should be used. For further information, see the Texas Instruments application reports *PowerPAD Thermally Enhanced Package* (SLMA002) and *PowerPAD Made Easy* (SLMA004).

Copyright © 2008, Texas Instruments Incorporated

Figure 23. Typical Application, Notebook supply

Figure 24. Typical Application, Monitor Supply

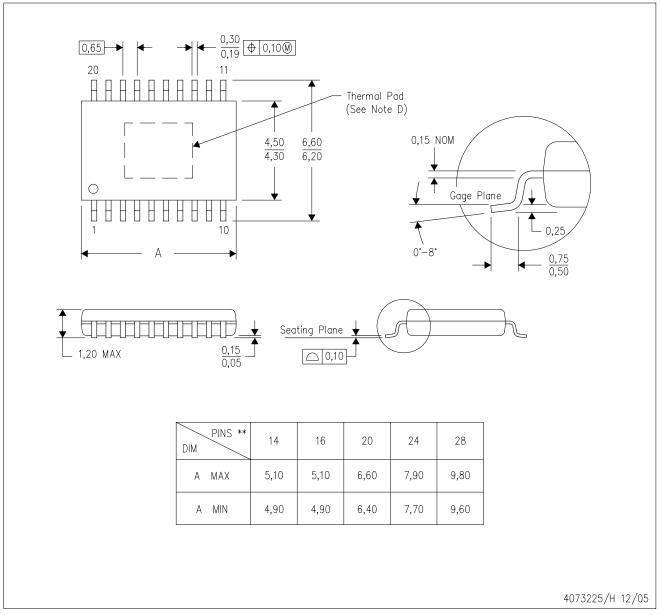

PWP (R-PDSO-G\*\*) PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE 20 PIN SHOWN

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

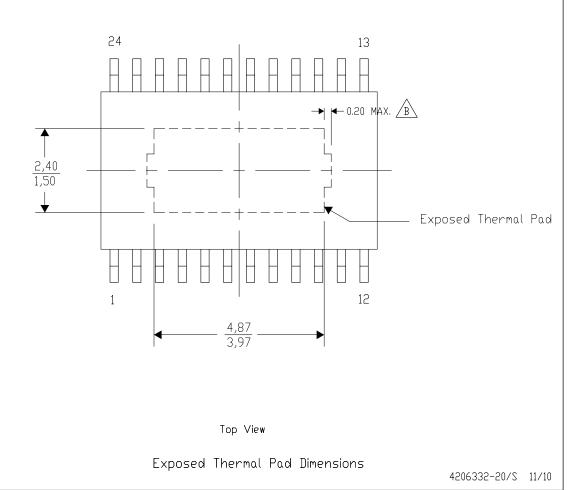

## PWP (R-PDSD-G24)

# PowerPAD™ SMALL PLASTIC DUTLINE

#### THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

B. Exposed tie strap features may not be present.

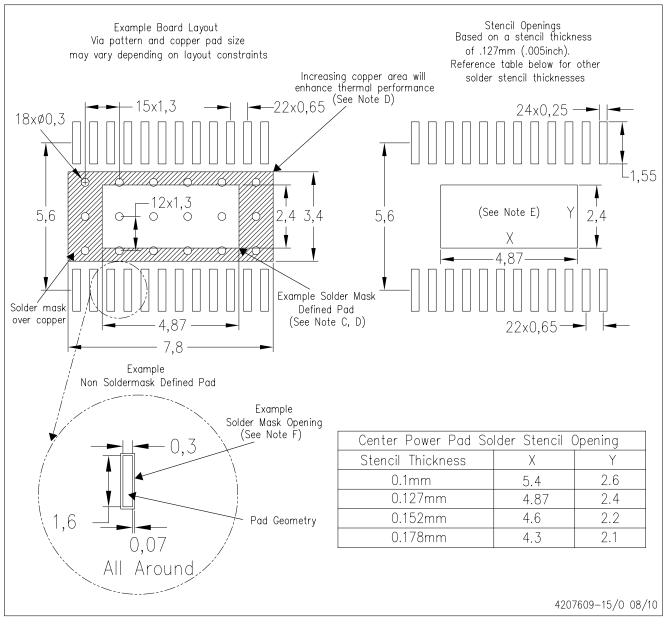

# PWP (R-PDSO-G24)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

## 查询"TPS65100-Q1"供应商

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                 |                                   |

|-----------------------------|------------------------|------------------------------|-----------------------------------|