# 4559 Group

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

REJ03B0188-0104 - Rev.1.04 Aug 23, 2007

## **DESCRIPTION**

The 4559 Group is a 4-bit single-chip microcomputer designed with CMOS technology. Its CPU is that of the 4500 Series using a simple, high-speed instruction set. The computer is equipped with two 8-bit timers (each timer has one or two reload registers), a 16-bit timer for clock count, interrupts, and oscillation circuit switch function.

The various microcomputers in the 4559 Group include variations of type as shown in the table below.

## **FEATURES**

| • Interrupt                    | 4 sources |

|--------------------------------|-----------|

| Key-on wakeup function pins    | 17        |

| • I/O port                     | 22        |

| Output port                    |           |

| LCD control circuit            |           |

| Segment output                 | 32        |

| Common output                  | 4         |

| Voltage drop detection circuit |           |

|                                |           |

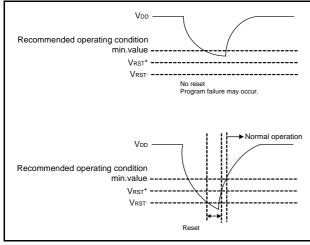

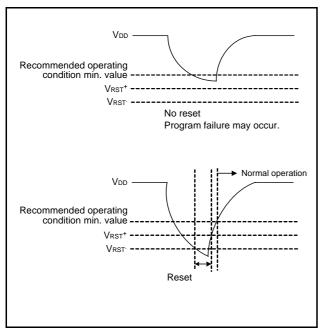

- Reset occurrence.......Typ. 1.7 V (Ta = 25 °C)

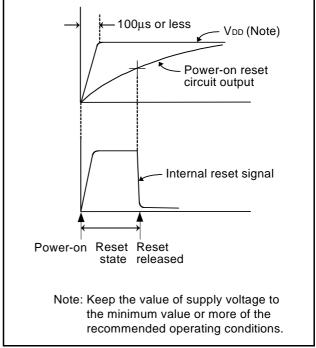

- Power-on reset circuit

- · Watchdog timer

- Clock generating circuit

Built-in clock (on-chip oscillator)

Main clock (ceramic resonator/RC oscillation)

Sub-clock (quartz-crystal oscillation)

- LED drive directly enabled (port D)

## **APPLICATION**

Remote control transmitter

#### Table 1 Support Product

| Part number         | ROM size (× 10 bits) | RAM size (× 4 bits) | Package      | ROM type |

|---------------------|----------------------|---------------------|--------------|----------|

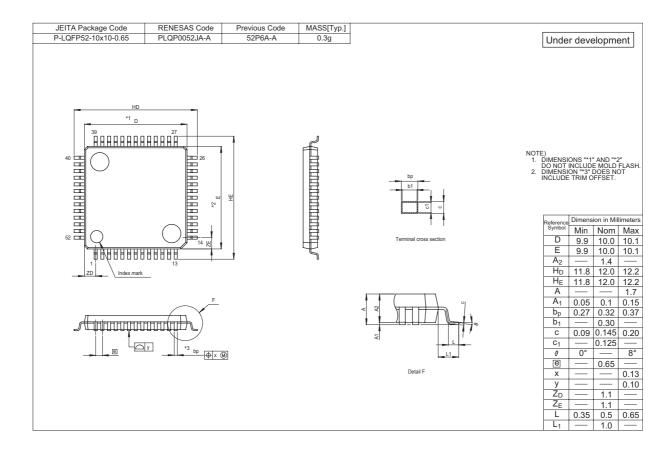

| M34559G6FP (Note 1) | 6144 words           | 288 words           | PLQP0052JA-A | QzROM    |

| M34559G6-XXXFP      | 6144 words           | 288 words           | PLQP0052JA-A | QzROM    |

Note 1: Shipped in blank

Page 1 of 146

## **PIN CONFIGURATION**

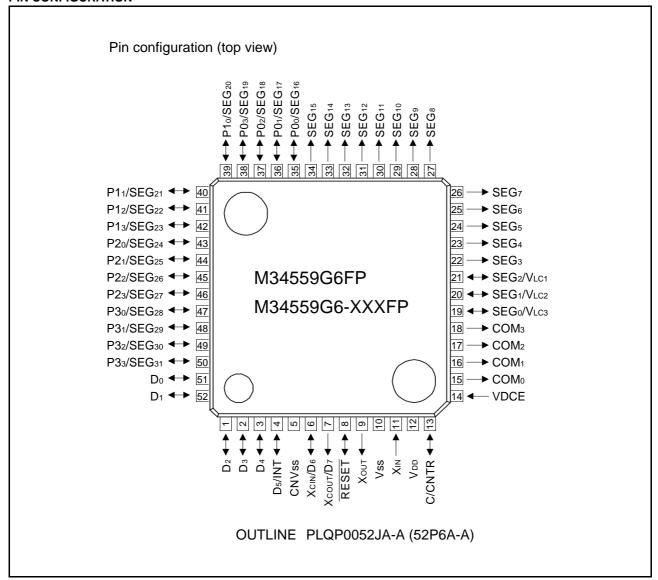

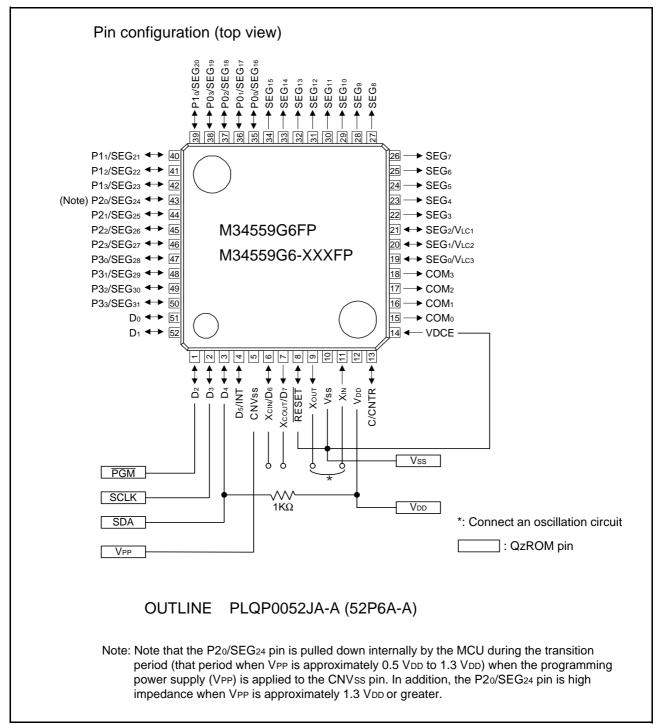

Fig 1. Pin configuration (PLQP0052JA-A type)

## **FUNCTIONAL BLOCK DIAGRAM**

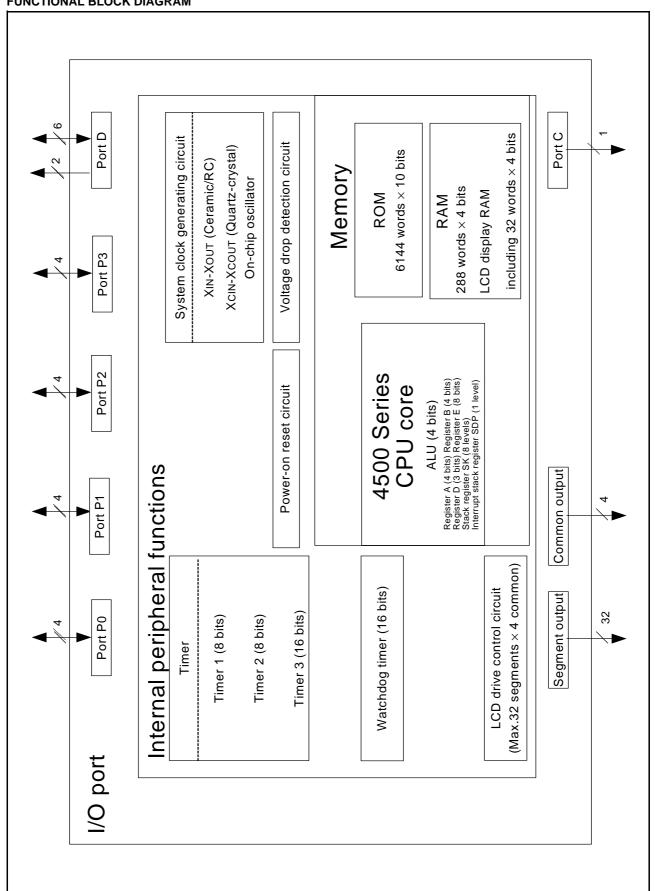

Fig 2. Functional block diagram (PLQP0052JA-A type)

# PERFORMANCE OVERVIEW

# Table 2 Performance overview

|                                     | F                                      | Parameter                          |                                                         | Function                                                                                                                                                                  |  |  |  |  |  |

|-------------------------------------|----------------------------------------|------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Number of I                         | basic ins                              | tructions                          |                                                         | 135                                                                                                                                                                       |  |  |  |  |  |

| Minimum in                          | struction                              | execution                          | time                                                    | 0.5 μs (Oscillation frequency 6 MHz: high-speed through mode)                                                                                                             |  |  |  |  |  |

| Memory siz                          | es                                     | ROM                                |                                                         | 6144 words × 10 bits                                                                                                                                                      |  |  |  |  |  |

|                                     |                                        | RAM                                |                                                         | 288 words × 4 bits (including LCD display RAM 32 words × 4 bits)                                                                                                          |  |  |  |  |  |

| I/O port                            |                                        | D0-D5                              | I/O                                                     | Six independent I/O ports.                                                                                                                                                |  |  |  |  |  |

| no por                              |                                        |                                    | (Input is examined by skip decision.)                   | The output structure can be switched by software. Port D <sub>5</sub> is also used as INT pin.                                                                            |  |  |  |  |  |

|                                     |                                        | D6, D7                             | Output                                                  | Two independent output ports. Ports D6 and D7 are also used as XCIN and XCOUT, respectively.                                                                              |  |  |  |  |  |

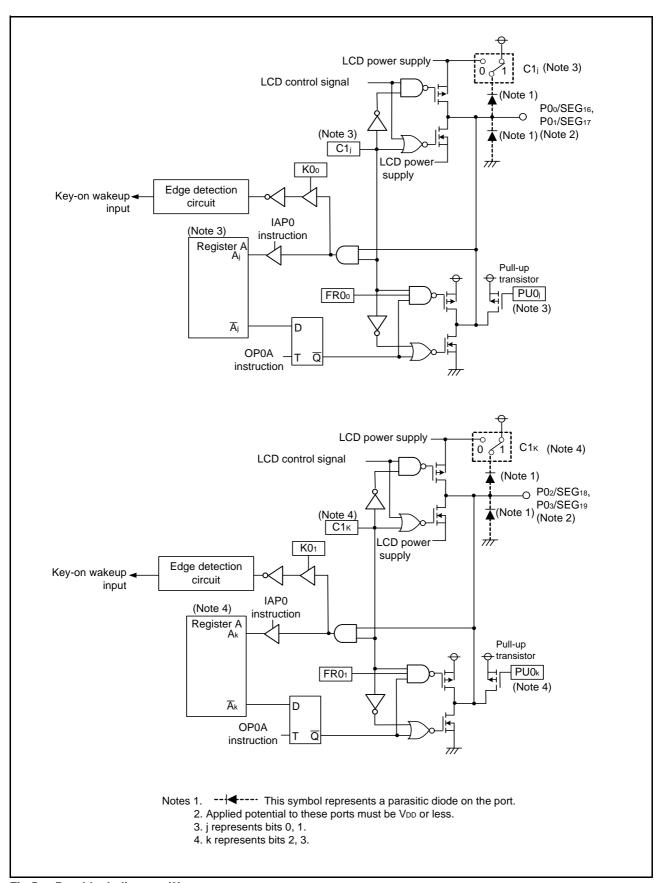

|                                     |                                        | P00-P03                            | I/O                                                     | 4-bit I/O port; A pull-up function, a key-on wakeup function and output structure can be switched by software.  Ports P00–P03 are also used as SEG16–SEG19, respectively. |  |  |  |  |  |

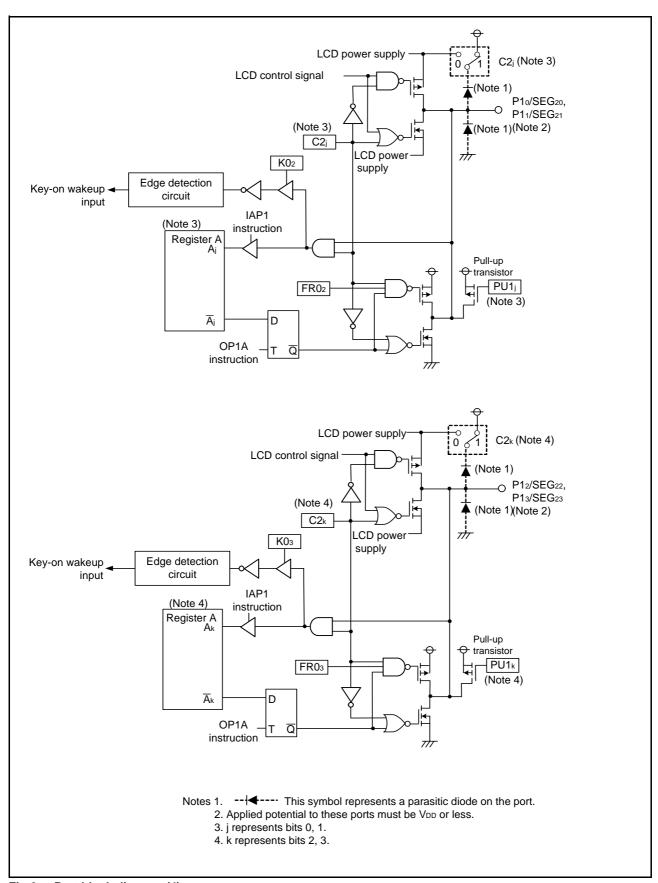

|                                     |                                        | P10-P13                            | I/O                                                     | 4-bit I/O port; A pull-up function, a key-on wakeup function and output structure can be switched by software.  Ports P10–P13 are also used as SEG20–SEG23, respectively. |  |  |  |  |  |

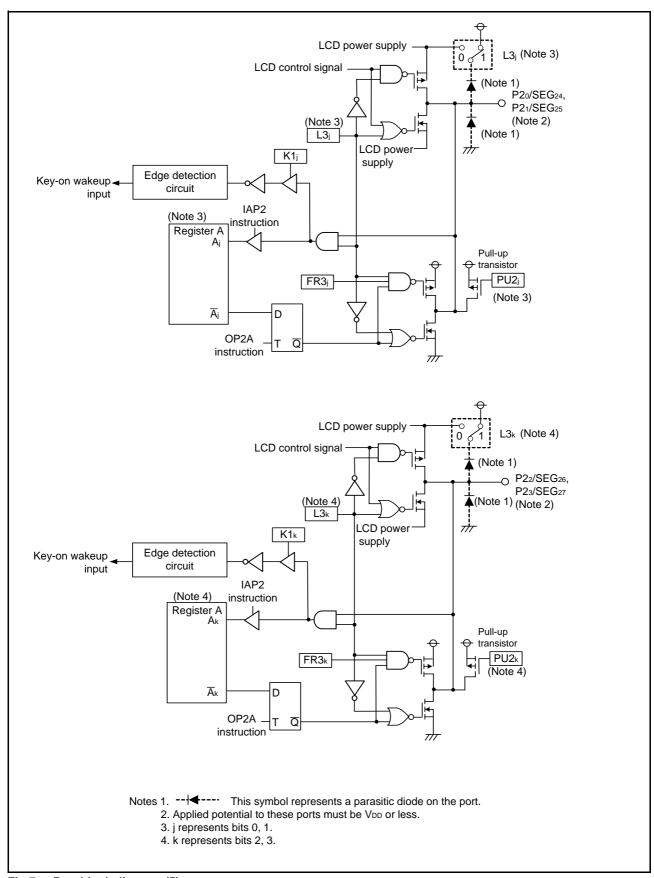

|                                     |                                        | P20-P23                            | I/O                                                     | 4-bit I/O port; A pull-up function, a key-on wakeup function and output structure carbe switched by software.  Ports P20–P23 are also used as SEG24–SEG27, respectively.  |  |  |  |  |  |

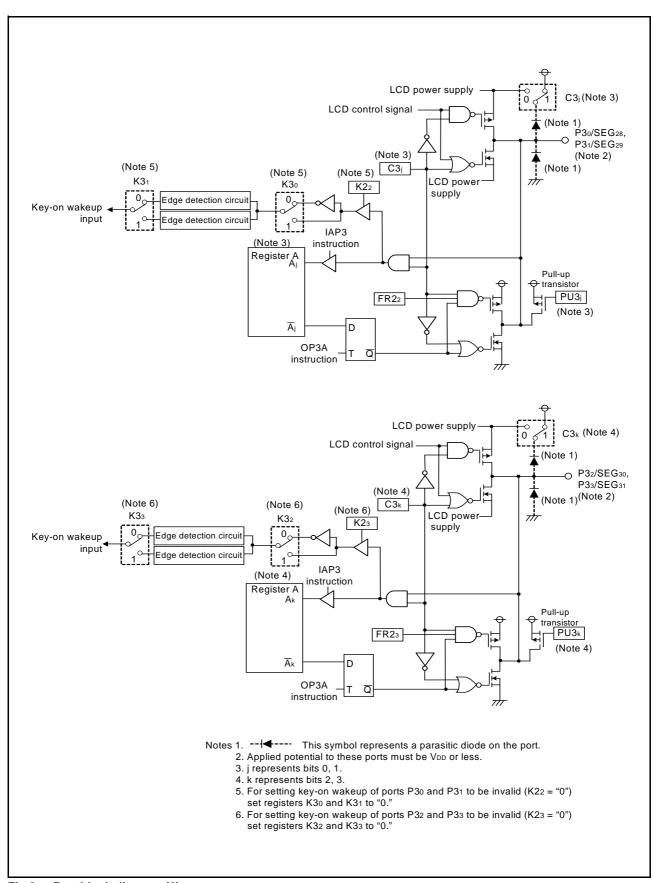

|                                     |                                        | P30-P33                            | I/O                                                     | 4-bit I/O port; A pull-up function, a key-on wakeup function and output structure car be switched by software.  Ports P30–P33 are also used as SEG28–SEG31, respectively. |  |  |  |  |  |

|                                     |                                        | С                                  | Output                                                  | 1-bit output; Port C is also used as CNTR pin.                                                                                                                            |  |  |  |  |  |

| Timer                               |                                        | Timer 1                            |                                                         | 8-bit timer with a reload register and carrier wave output auto-control function, and has an event counter.                                                               |  |  |  |  |  |

|                                     |                                        | Timer 2                            |                                                         | 8-bit timer with two reload registers and carrier wave generation function.                                                                                               |  |  |  |  |  |

|                                     |                                        | Timer 3                            |                                                         | 16-bit timer, fixed dividing frequency (timer for clock count)                                                                                                            |  |  |  |  |  |

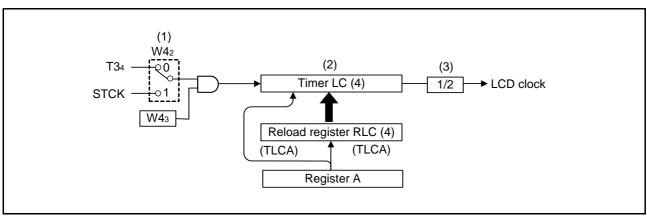

|                                     |                                        | Timer LC                           |                                                         | 4-bit programmable timer with a reload register (for LCD clock generating)                                                                                                |  |  |  |  |  |

|                                     |                                        | Watchdog                           | timer                                                   | 16-bit timer, fixed dividing frequency (timer for monitor)                                                                                                                |  |  |  |  |  |

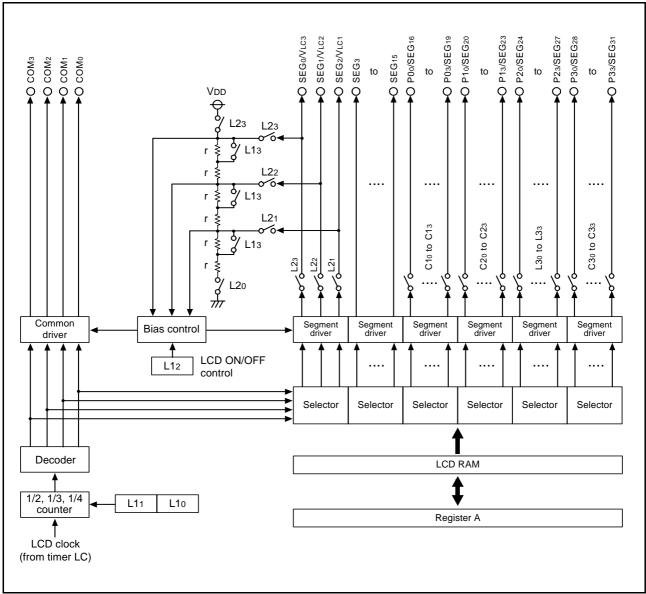

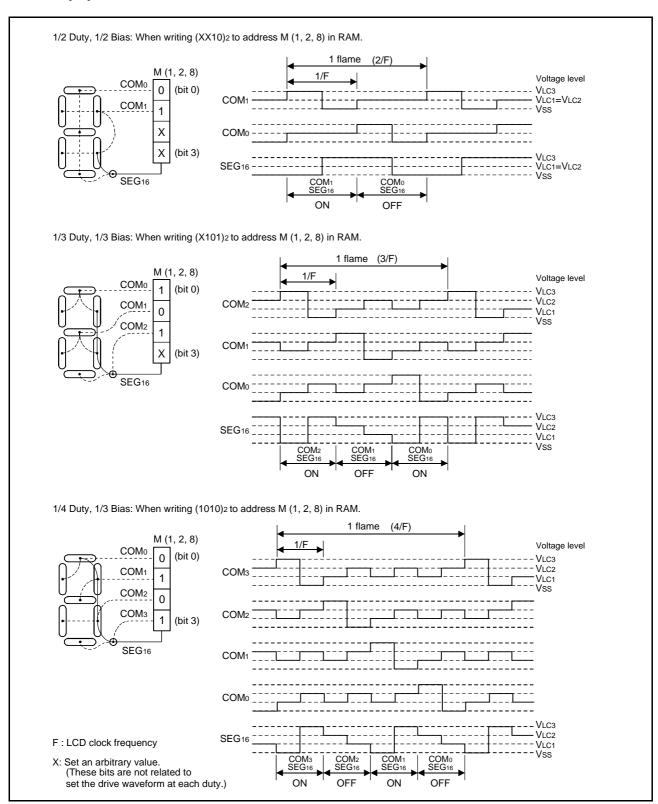

| LCD contro                          | l circuit                              | Selective I                        | bias value                                              | 1/2, 1/3 bias                                                                                                                                                             |  |  |  |  |  |

|                                     |                                        | Selective duty value               |                                                         | 2, 3, 4 duty                                                                                                                                                              |  |  |  |  |  |

|                                     |                                        | Common                             | output                                                  | 4                                                                                                                                                                         |  |  |  |  |  |

|                                     |                                        | Segment output                     |                                                         | 32                                                                                                                                                                        |  |  |  |  |  |

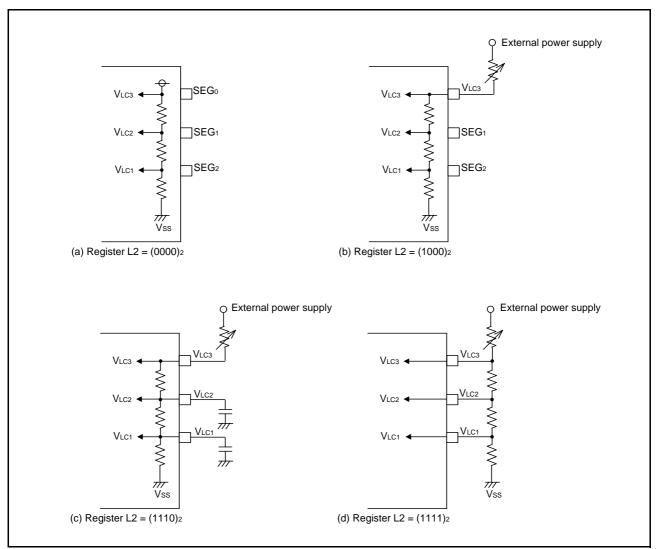

|                                     |                                        | Internal resistor for power supply |                                                         | $2r \times 3$ , $2r \times 2$ , $r \times 3$ , $r \times 2$ ( $r = 100 \text{ k}\Omega$ , (Ta = 25 °C, Typical value))                                                    |  |  |  |  |  |

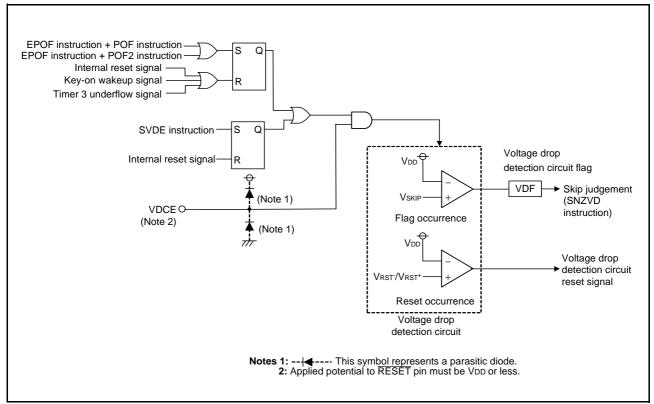

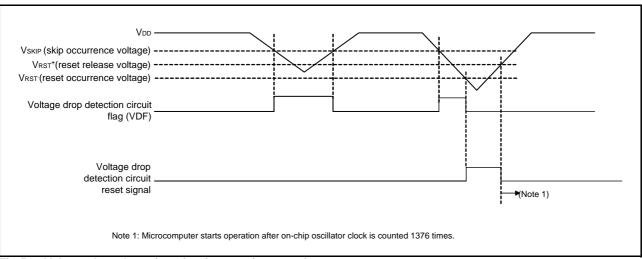

| Voltage dro                         | р                                      | Reset occ                          | urrence                                                 | Typ. 1.7 V (Ta=25 °C)                                                                                                                                                     |  |  |  |  |  |

| detection ci                        | rcuit                                  | Reset rele                         | ase                                                     | Typ. 1.8 V (Ta=25 °C)                                                                                                                                                     |  |  |  |  |  |

|                                     |                                        | Skip occur                         | rrence                                                  | Typ. 2.0 V (Ta=25 °C)                                                                                                                                                     |  |  |  |  |  |

| Power-on re                         | eset circu                             | uit                                |                                                         | Built-in                                                                                                                                                                  |  |  |  |  |  |

| Interrupt                           |                                        | Source                             |                                                         | 4 sources (one for external, three for timers)                                                                                                                            |  |  |  |  |  |

|                                     |                                        | Nesting                            |                                                         | 1 level                                                                                                                                                                   |  |  |  |  |  |

| Subroutine                          | nestina                                |                                    |                                                         | 8 levels                                                                                                                                                                  |  |  |  |  |  |

| Device stru                         |                                        |                                    |                                                         | CMOS silicon gate                                                                                                                                                         |  |  |  |  |  |

| Package Operating temperature range |                                        |                                    | 52-pin plastic molded LQFP (PLQP0052JA-A)  -20 to 85 °C |                                                                                                                                                                           |  |  |  |  |  |

|                                     |                                        |                                    |                                                         |                                                                                                                                                                           |  |  |  |  |  |

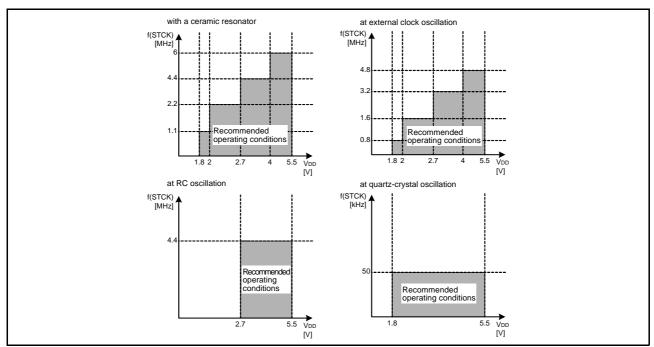

| Power sour                          |                                        |                                    |                                                         | 1.8 to 5.5 V (It depends on operation source clock, oscillation frequency an operation mode)                                                                              |  |  |  |  |  |

| Power dissipation                   | At active                              | e mode                             |                                                         | 0.3 mA (Ta = 25 °C, VDD = 3 V, $f(XIN) = 4$ MHz, $f(XCIN) = stop$ , $f(RING) = stop$<br>f(STCK) = f(XIN)/8                                                                |  |  |  |  |  |

|                                     | At clock                               | operating i                        | mode                                                    | $5 \mu A (Ta = 25 °C, VDD = 3 V, f(XCIN) = 32 kHz)$                                                                                                                       |  |  |  |  |  |

|                                     | At clock operating mode At RAM back-up |                                    |                                                         | $0.1 \mu A$ (Ta = 25 °C, VDD = 5 V, n(ACIN) = 32 KHZ)                                                                                                                     |  |  |  |  |  |

# **PIN DESCRIPTION**

Table 3 Pin description

| Pin                                | Name                                                   | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------|--------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd                                | Power source                                           | _            | Connected to a plus power supply.                                                                                                                                                                                                                                                                                                                                                       |

| Vss                                | Power source                                           | -            | Connected to a 0 V power supply.                                                                                                                                                                                                                                                                                                                                                        |

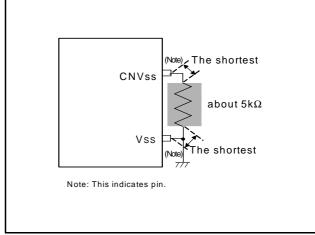

| CNVss                              | CNVss                                                  | _            | This pin is shared with the VPP pin which is the power source input pin for programming the built-in QzROM. Connect to Vss through a resistor about 5 k $\Omega$ .                                                                                                                                                                                                                      |

| VDCE                               | Voltage drop<br>detection circuit<br>enable            | Input        | This pin is used to operate/stop the voltage drop detection circuit.  When "H" level is input to this pin, the circuit starts operating.  When "L" level is input to this pin, the circuit stops operating.                                                                                                                                                                             |

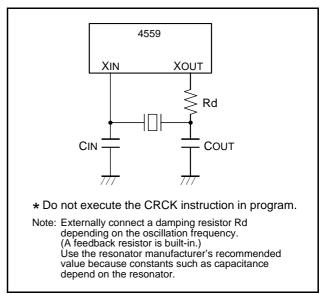

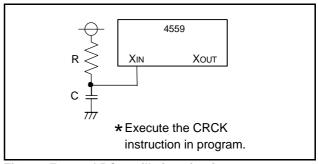

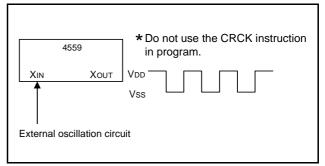

| XIN                                | Main clock input                                       | Input        | I/O pins of the main clock generating circuit. When using a ceramic resonator,                                                                                                                                                                                                                                                                                                          |

| Хоит                               | Main clock output                                      | Output       | connect it between pins XIN and XOUT. A feedback resistor is built-in between them. When using the RC oscillation, connect a resistor and a capacitor to XIN, and leave XOUT pin open.                                                                                                                                                                                                  |

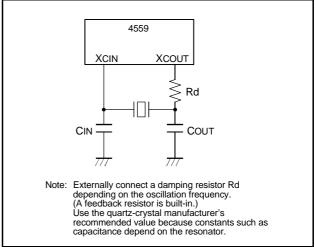

| Xcin                               | Sub clock input                                        | Input        | I/O pins of the sub-clock generating circuit. Connect a 32.768 kHz quartz-crystal                                                                                                                                                                                                                                                                                                       |

| Хсоит                              | Sub clock output                                       | Output       | oscillator between pins Χcιν and Χcουτ. A feedback resistor is built-in between them.<br>Χcιν and Χcουτ pins are also used as ports D <sub>6</sub> and D <sub>7</sub> , respectively.                                                                                                                                                                                                   |

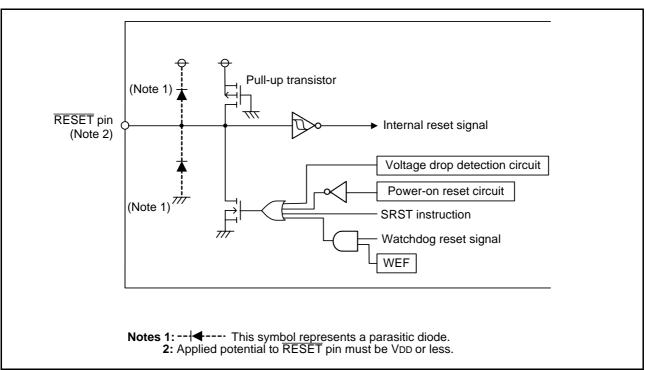

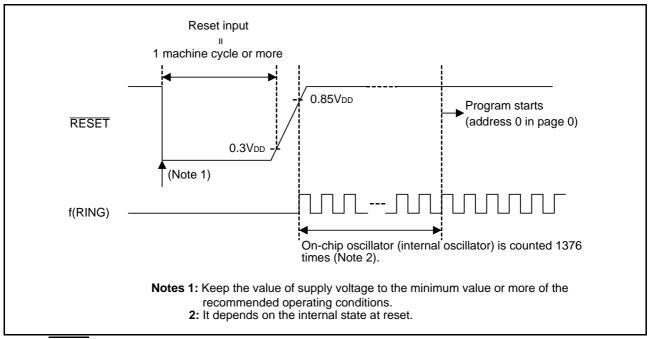

| RESET                              | Reset I/O                                              | I/O          | An N-channel open-drain I/O pin for a system reset. When the SRST instruction, watchdog timer, the built-in power-on reset or the voltage drop detection circuit causes the system to be reset, the RESET pin outputs "L" level.                                                                                                                                                        |

| D0-D5                              | I/O port D<br>(Input is examined<br>by skip decision.) | I/O          | Each pin of port D has an independent 1-bit wide I/O function. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port D <sub>5</sub> is also used as INT pin.                                                                                             |

| D6, D7                             | Output port D                                          | Output       | Each pin of port D has an independent 1-bit wide output function. The output structure is N-channel open-drain. Ports D6 and D7 are also used as XCIN pin and XCOUT pin, respectively.                                                                                                                                                                                                  |

| P00-P03                            | I/O port P0                                            | I/O          | Port P0 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port P0 has a key-on wakeup function and a pull-up function. Both functions can be switched by software.  Ports P00-P03 are also used as SEG16-SEG19, respectively. |

| P10-P13                            | I/O port P1                                            | I/O          | Port P1 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port P1 has a key-on wakeup function and a pull-up function. Both functions can be switched by software.  Ports P10-P13 are also used as SEG20-SEG23, respectively. |

| P20-P23                            | I/O port P2                                            | I/O          | Port P2 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port P2 has a key-on wakeup function and a pull-up function. Both functions can be switched by software.  Ports P20-P23 are also used as SEG24-SEG27, respectively. |

| P30-P33                            | I/O port P3                                            | I/O          | Port P3 serves as a 4-bit I/O port. The output structure can be switched to N-channel open-drain or CMOS by software. For input use, set the latch of the specified bit to "1" and select the N-channel open-drain. Port P3 has a key-on wakeup function and a pull-up function. Both functions can be switched by software.  Ports P30-P33 are also used as SEG28-SEG31, respectively. |

| С                                  | Output port C                                          | Output       | 1-bit output port. The output structure is CMOS. Port C is also used as CNTR pin.                                                                                                                                                                                                                                                                                                       |

| COM <sub>0</sub> –COM <sub>3</sub> | Common output                                          | Output       | LCD common output pins. Pins COMo and COM1 are used at 1/2 duty, pins COM0-COM2 are used at 1/3 duty and pins COM0-COM3 are used at 1/4 duty.                                                                                                                                                                                                                                           |

| SEG0-SEG31                         | Segment output                                         | Output       | LCD segment output pins. SEG0-SEG2 pins are used as VLc3-VLc1 pins, respectively. SEG16-SEG31 pins are used as Ports P00-P03, Ports P10-P13, Ports P20-P23, and Ports P30-P33, respectively.                                                                                                                                                                                            |

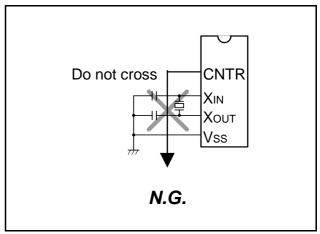

| CNTR                               | Timer I/O                                              | I/O          | CNTR pin has the function to input the clock for the timer 1 event counter and to output the PWM signal generated by timer 2. CNTR pin is also used as Port C.                                                                                                                                                                                                                          |

| INT                                | Interrupt input                                        | Input        | INT pin accepts external interrupts. They have the key-on wakeup function which can be switched by software. INT pin is also used as Port D <sub>5</sub> .                                                                                                                                                                                                                              |

| VLC3-VLC1                          | LCD power source                                       | _            | These are the LCD power supply pins. If an internal resistor is used, connect the VLC3 pin to the VDD pin. (If brightness adjustment is required, connect via a resistor.) When using an external power supply, apply voltage such that Vss $\leq$ VLC1 $\leq$ VLC2 $\leq$ VLC3 $\leq$ VDD. Pins VLC3 to VLC1 also function as pins SEG0 to SEG2.                                       |

## **MULTIFUNCTION**

Table 4 Pin description

| Pin             | Multifunction     | Pin               | Multifunction   | Pin              | Multifunction     | Pin               | Multifunction    |

|-----------------|-------------------|-------------------|-----------------|------------------|-------------------|-------------------|------------------|

| P0 <sub>0</sub> | SEG <sub>16</sub> | SEG <sub>16</sub> | P0 <sub>0</sub> | P30              | SEG <sub>28</sub> | SEG <sub>28</sub> | P30              |

| P01             | SEG <sub>17</sub> | SEG <sub>17</sub> | P01             | P31              | SEG29             | SEG29             | P31              |

| P02             | SEG <sub>18</sub> | SEG <sub>18</sub> | P02             | P32              | SEG <sub>30</sub> | SEG <sub>30</sub> | P32              |

| P03             | SEG19             | SEG19             | P03             | P3 <sub>3</sub>  | SEG31             | SEG31             | P3 <sub>3</sub>  |

| P10             | SEG <sub>20</sub> | SEG <sub>20</sub> | P10             | D5               | INT               | INT               | D5               |

| P1 <sub>1</sub> | SEG21             | SEG <sub>21</sub> | P11             | D6               | XCIN              | XCIN              | D <sub>6</sub>   |

| P12             | SEG22             | SEG22             | P12             | D7               | Хсоит             | Хсоит             | D7               |

| P13             | SEG23             | SEG23             | P13             | С                | CNTR              | CNTR              | С                |

| P20             | SEG24             | SEG24             | P20             | SEG <sub>0</sub> | VLC3              | VLC3              | SEG <sub>0</sub> |

| P21             | SEG <sub>25</sub> | SEG <sub>25</sub> | P21             | SEG1             | VLC2              | VLC2              | SEG <sub>1</sub> |

| P22             | SEG <sub>26</sub> | SEG <sub>26</sub> | P22             | SEG <sub>2</sub> | VLC1              | VLC1              | SEG <sub>2</sub> |

| P23             | SEG27             | SEG27             | P23             |                  |                   |                   |                  |

# **PORT FUNCTION**

Table 5 Port function

| Port    | Pin                                                  | Input<br>Output | Output<br>structure              | I/O unit | Control instructions | Control registers       | Remark                                                                             |

|---------|------------------------------------------------------|-----------------|----------------------------------|----------|----------------------|-------------------------|------------------------------------------------------------------------------------|

| Port D  | D0-D4,<br>D5/INT                                     | I/O<br>(6)      | N-channel<br>open-drain/<br>CMOS | 1 bit    | SD, RD<br>SZD, CLD   | FR1, FR2,<br>I1, K2     | Programmable output structure selection function                                   |

|         | D6/XCIN,<br>D7/XCOUT                                 | Output<br>(2)   | N-channel open-drain             |          |                      | RG                      | _                                                                                  |

| Port P0 | P00/SEG16,<br>P01/SEG17,<br>P02/SEG18,<br>P03/SEG19  | I/O<br>(4)      | N-channel<br>open-drain/<br>CMOS | 4 bits   | OP0A<br>IAP0         | PU0, K0,<br>FR0, C1     | Programmable pull-up, key-<br>on wakeup and output<br>structure selection function |

| Port P1 | P10/SEG20,<br>P11/SEG21,<br>P12/SEG22,<br>P13/SEG23  | I/O<br>(4)      | N-channel<br>open-drain/<br>CMOS | 4 bits   | OP1A<br>IAP1         | PU1, K0,<br>FR0, C2     | Programmable pull-up, key-<br>on wakeup and output<br>structure selection function |

| Port P2 | P20/SEG24,<br>P21/SEG25,<br>P22/SEG26,<br>P23/SEG27, | I/O<br>(4)      | N-channel<br>open-drain/<br>CMOS | 4 bits   | OP2A<br>IAP2         | PU2, K1,<br>FR3, L3     | Programmable pull-up, key-<br>on wakeup and output<br>structure selection function |

| Port P3 | P30/SEG28,<br>P31/SEG29,<br>P32/SEG30,<br>P33/SEG31  | I/O<br>(4)      | N-channel<br>open-drain/<br>CMOS | 4 bits   | OP3A<br>IAP3         | PU3, K2, K3,<br>FR2, C3 | Programmable pull-up, key-<br>on wakeup and output<br>structure selection function |

| Port C  | C/CNTR                                               | Output<br>(1)   | CMOS                             | 1 bit    | RCP<br>SCP           | W1, W2, W4              | _                                                                                  |

Note 1. Pins except above have just single function.

Note 2. The input/output of Ds can be used even when INT is selected.

Be careful when using inputs of both INT and Ds since the input threshold value of INT pin is different from that of port Ds.

Note 3. "H" output function of port C can be used even when the CNTR (output) is used.

## **DEFINITION OF CLOCK AND CYCLE**

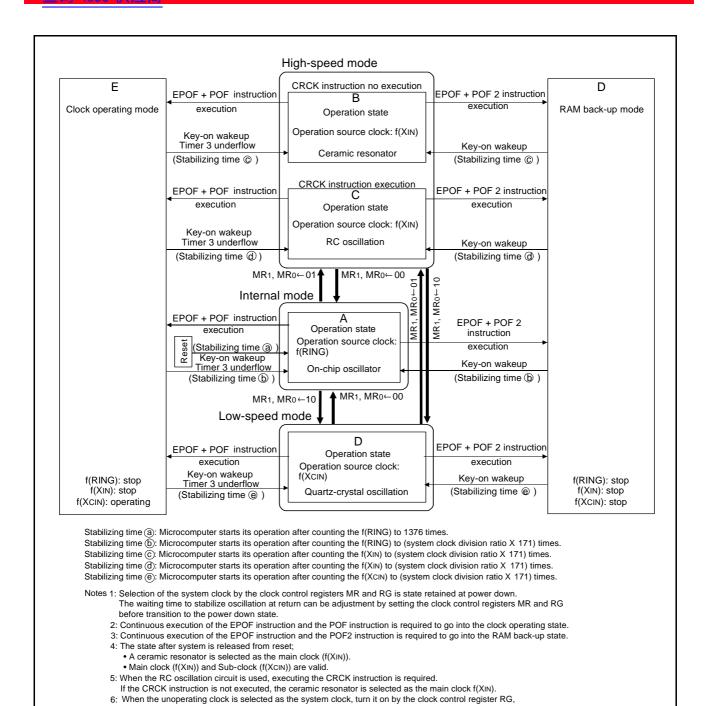

# Operation source clock

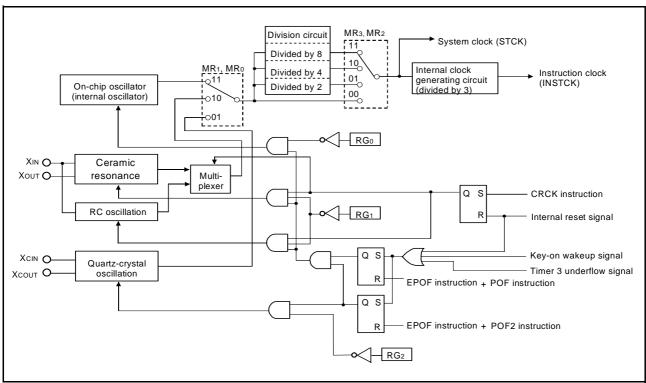

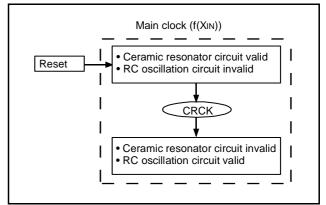

The operation source clock is the source clock to operate this product. In this product, the following clocks are used.

- $\bullet$  Clock (f(XIN)) by the external ceramic resonator

- ullet Clock (f(XIN)) by the external RC oscillation

- $\bullet$  Clock (f(XIN)) by the external input

- ullet Clock (f(RING)) of the on-chip oscillator which is the internal oscillator

- $\bullet$  Clock (f(Xcin)) by the external quartz-crystal oscillation

## • System clock (STCK)

The system clock is the basic clock for controlling this product. The system clock is selected by the clock control register MR shown as the table below.

## · Machine cycle

The machine cycle is the standard cycle required to execute the instruction.

## • Instruction clock (INSTCK)

The instruction clock is the basic clock for controlling CPU. The instruction clock (INSTCK) is a signal derived by dividing the system clock (STCK) by 3. The one instruction clock cycle generates the one machine cycle.

Table 6 Table Selection of system clock

| Register MR |     |     |                 | System clock        | Operation mode                         |  |  |

|-------------|-----|-----|-----------------|---------------------|----------------------------------------|--|--|

| MRз         | MR2 | MR1 | MR <sub>0</sub> | System clock        | Operation mode                         |  |  |

| 1           | 1   | 0   | 0               | f(STCK) = f(RING)/8 | Internal frequency divided by 8 mode   |  |  |

| 1           | 0   | 0   | 0               | f(STCK) = f(RING)/4 | Internal frequency divided by 4 mode   |  |  |

| 0           | 1   | 0   | 0               | f(STCK) = f(RING)/2 | Internal frequency divided by 2 mode   |  |  |

| 0           | 0   | 0   | 0               | f(STCK) = f(RING)   | Internal frequency through mode        |  |  |

| 1           | 1   | 0   | 1               | f(STCK) = f(XIN)/8  | High-speed frequency divided by 8 mode |  |  |

| 1           | 0   | 0   | 1               | f(STCK) = f(XIN)/4  | High-speed frequency divided by 4 mode |  |  |

| 0           | 1   | 0   | 1               | f(STCK) = f(XIN)/2  | High-speed frequency divided by 2 mode |  |  |

| 0           | 0   | 0   | 1               | f(STCK) = f(XIN)    | High-speed through mode                |  |  |

| 1           | 1   | 1   | 0               | f(STCK) = f(Xcin)/8 | Low-speed frequency divided by 8 mode  |  |  |

| 1           | 0   | 1   | 0               | f(STCK) = f(Xcin)/4 | Low-speed frequency divided by 4 mode  |  |  |

| 0           | 1   | 1   | 0               | f(STCK) = f(XCIN)/2 | Low-speed frequency divided by 2 mode  |  |  |

| 0           | 0   | 1   | 0               | f(STCK) = f(Xcin)   | Low-speed through mode                 |  |  |

Note 1. The f(RING)/8 is selected after system is released from reset

# **CONNECTIONS OF UNUSED PINS**

# Table 7 Port function

| Pin                                | Connection      | Usage condition                                                                                                                                                 |

|------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN                                | Connect to Vss. | RC oscillator is not selected                                                                                                                                   |

| Хоит                               | Open.           | -                                                                                                                                                               |

| Xcin/D6                            | Connect to Vss. | -                                                                                                                                                               |

| XCOUT/D7                           | Open.           | -                                                                                                                                                               |

| D0-D4                              | Open.           | -                                                                                                                                                               |

|                                    | Connect to Vss. | N-channel open-drain is selected for the output structure.                                                                                                      |

| D <sub>5</sub> /INT                | Open.           | INT pin input is disabled.                                                                                                                                      |

|                                    | Connect to Vss. | N-channel open-drain is selected for the output structure.                                                                                                      |

| P00/SEG16-                         | Open.           | The key-on wakeup function is invalid.                                                                                                                          |

| P03/SEG19                          | Connect to Vss. | Segment output is not selected.  N-channel open-drain is selected for the output structure.  Pull-up transistor is OFF.  The key-on wakeup function is invalid. |

| P10/SEG20-                         | Open.           | The key-on wakeup function is invalid.                                                                                                                          |

| P13/SEG23                          | Connect to Vss. | Segment output is not selected.  N-channel open-drain is selected for the output structure.  Pull-up transistor is OFF.  The key-on wakeup function is invalid. |

| P20/SEG24-                         | Open.           | The key-on wakeup function is invalid.                                                                                                                          |

| P23/SEG27                          | Connect to Vss. | Segment output is not selected.  N-channel open-drain is selected for the output structure.  Pull-up transistor is OFF.  The key-on wakeup function is invalid. |

| P30/SEG28-                         | Open.           | The key-on wakeup function is invalid.                                                                                                                          |

| P33/SEG31                          | Connect to Vss. | Segment output is not selected.  N-channel open-drain is selected for the output structure.  Pull-up transistor is OFF.  The key-on wakeup function is invalid. |

| C/CNTR                             | Open.           | CNTR input is not selected for timer 1 count source.                                                                                                            |

| COM <sub>0</sub> -COM <sub>3</sub> | Open.           | -                                                                                                                                                               |

| SEG <sub>0</sub> /V <sub>LC3</sub> | Open.           | SEG <sub>0</sub> pin is selected.                                                                                                                               |

| SEG1/VLC2                          | Open.           | SEG1 pin is selected.                                                                                                                                           |

| SEG <sub>2</sub> /V <sub>LC1</sub> | Open.           | SEG <sub>2</sub> pin is selected.                                                                                                                               |

| SEG3-SEG15                         | Open.           | -                                                                                                                                                               |

|                                    | +               |                                                                                                                                                                 |

(Note when connecting to Vss or VDD)

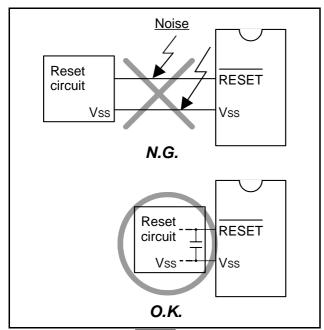

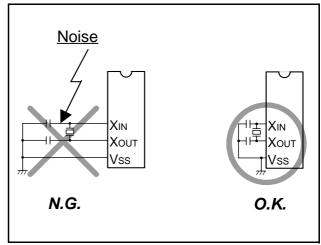

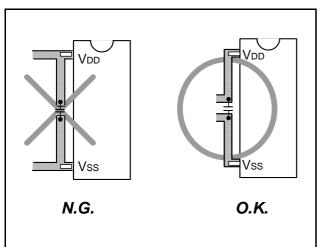

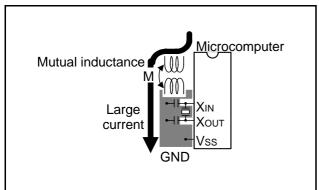

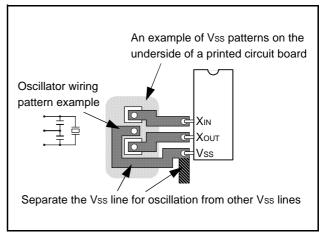

Connect the unused pins to Vss using the thickest wire at the shortest distance against noise.

## PORT BLOCK DIAGRAM

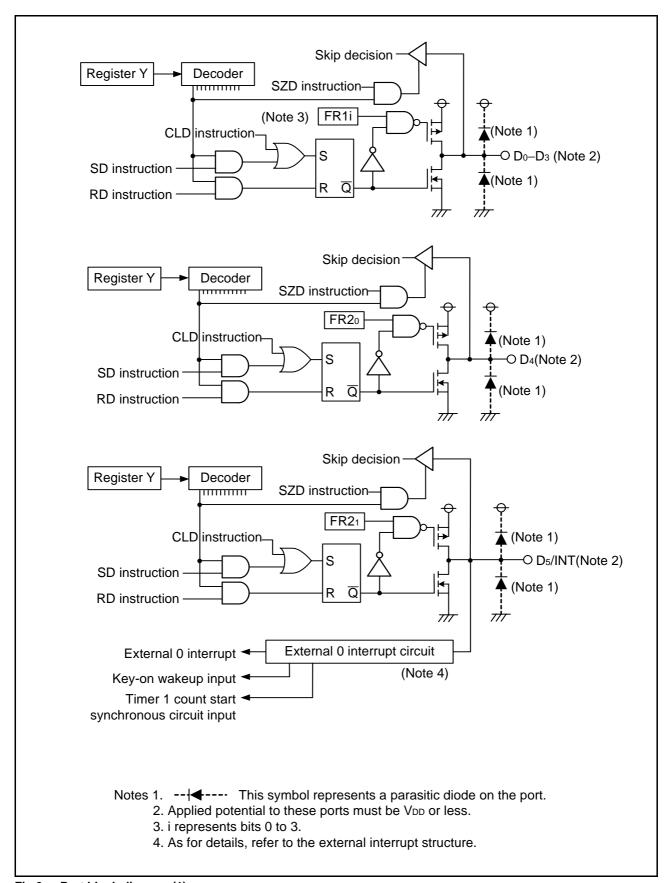

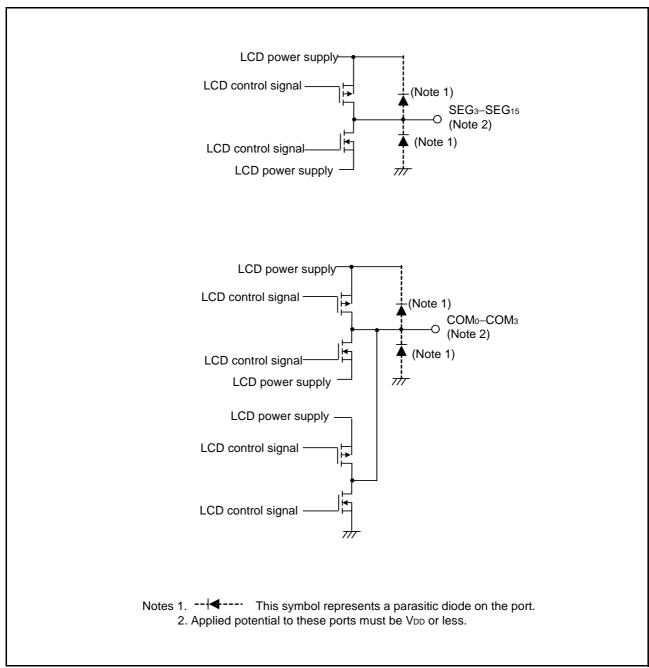

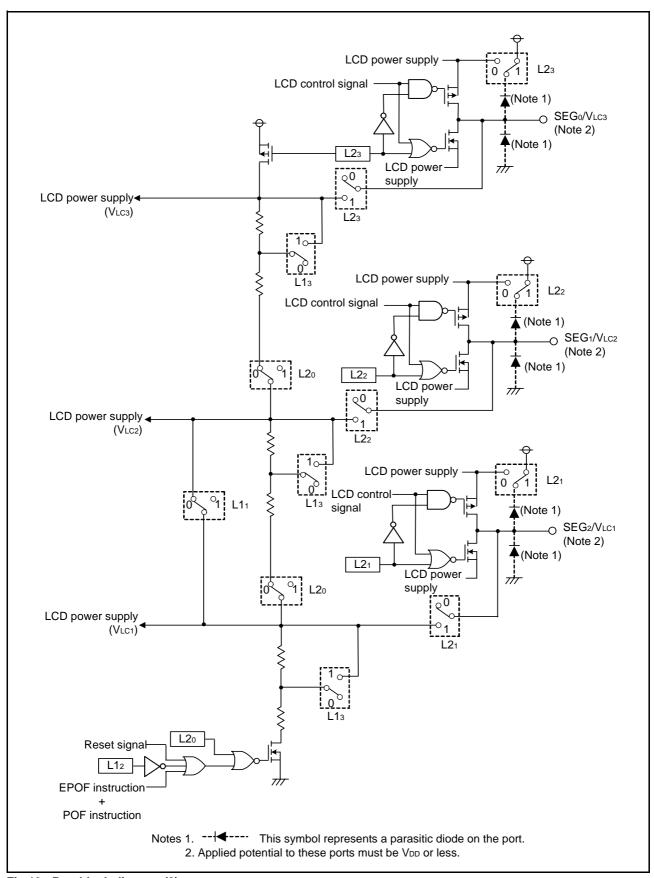

Fig 3. Port block diagram (1)

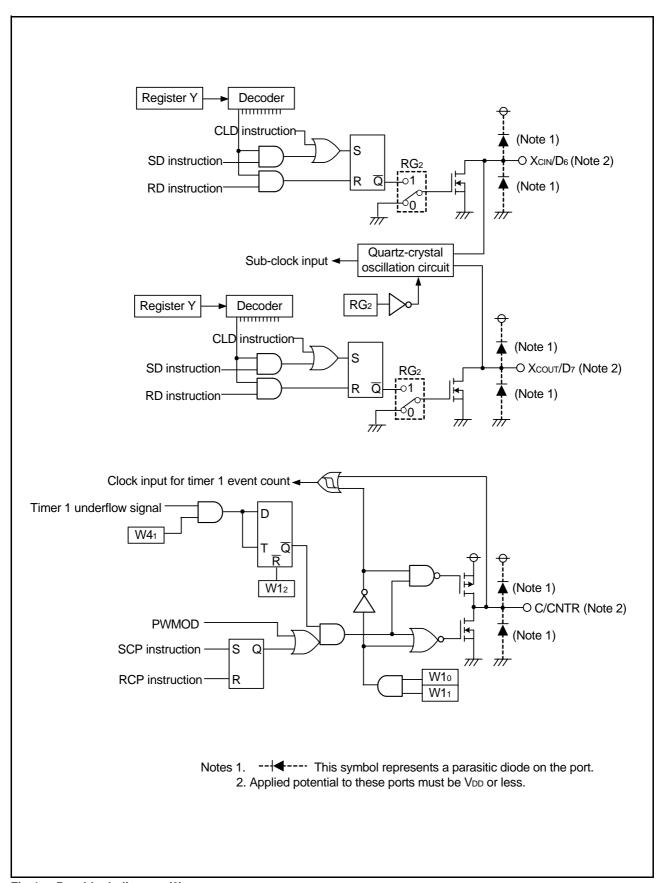

Fig 4. Port block diagram (2)

Fig 5. Port block diagram (3)

Fig 6. Port block diagram (4)

Fig 7. Port block diagram (5)

Fig 8. Port block diagram (6)

Fig 9. Port block diagram (7)

Fig 10. Port block diagram (8)

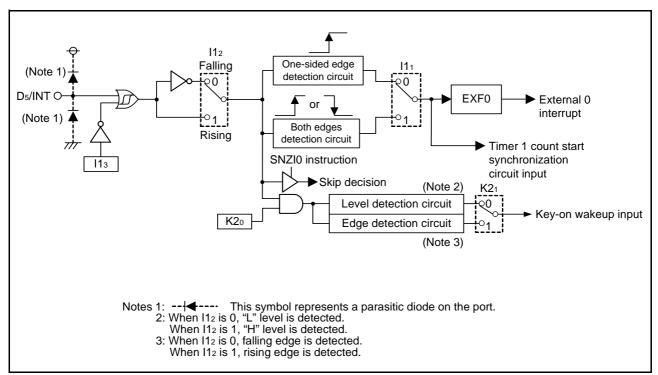

Fig 11. External interrupt circuit structure

#### **FUNCTION BLOCK OPERATIONS**

#### **CPU**

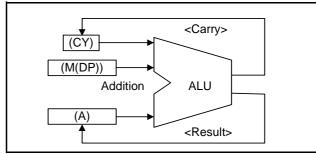

## (1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as 4-bit data addition, comparison, AND operation, OR operation, and bit manipulation.

## (2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer, exchange, and I/O operation.

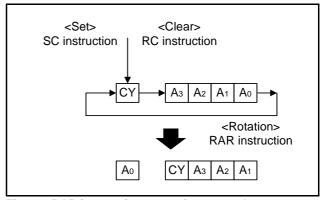

Carry flag CY is a 1-bit flag that is set to "1" when there is a carry with the AMC instruction (Figure 12).

It is unchanged with both A n instruction and AM instruction. The value of A0 is stored in carry flag CY with the RAR instruction (Figure 13).

Carry flag CY can be set to "1" with the SC instruction and cleared to "0" with the RC instruction.

## (3) Registers B and E

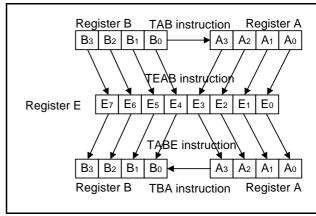

Register B is a 4-bit register used for temporary storage of 4-bit data, and for 8-bit data transfer together with register A.

Register E is an 8-bit register. It can be used for 8-bit data transfer with register B used as the high-order 4 bits and register A as the low-order 4 bits (Figure 14).

Register E is undefined after system is released from reset and returned from the power down mode. Accordingly, set the initial value.

## (4) Register D

Register D is a 3-bit register.

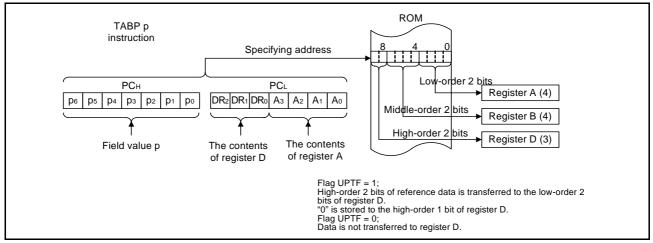

It is used to store a 7-bit ROM address together with register A and is used as a pointer within the specified page when the TABP p, BLA p, or BMLA p instruction is executed (Figure 15).

Also, when the TABP p instruction is executed at UPTF flag = "1", the high-order 2 bits of ROM reference data is stored to the low-order 2 bits of register D, the high-order 1 bit of register D is "0".

When the TABP p instruction is executed at UPTF flag = "0", the contents of register D remains unchanged. The UPTF flag is set to "1" with the SUPT instruction and cleared to "0" with the RUPT instruction.

The initial value of UPTF flag is "0".

Register D is undefined after system is released from reset and returned from the power down mode. Accordingly, set the initial value.

Fig 12. AMC instruction execution example

Fig 13. RAR instruction execution example

Fig 14. Registers A, B and register E

Fig 15. TABP p instruction execution example

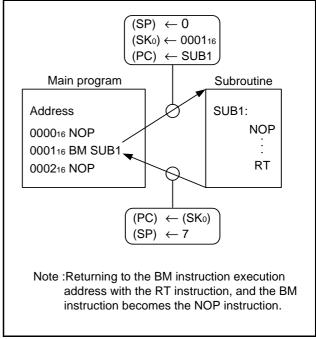

#### (5) Stack registers (SKs) and stack pointer (SP)

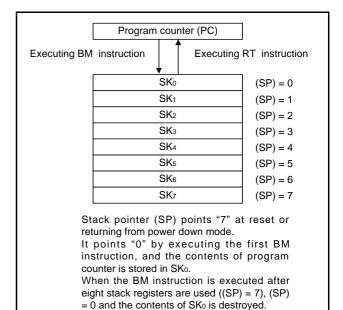

Stack registers are 14-bit registers.

Stack registers (SKs) are used to temporarily store the contents of program counter (PC) just before branching until returning to the original routine when;

- branching to an interrupt service routine (referred to as an interrupt service routine),

- performing a subroutine call, or

- executing the table reference instruction (TABP p).

Stack registers (SKs) are eight identical registers, so that subroutines can be nested up to 8 levels. However, one of stack registers is used respectively when using an interrupt service routine and when executing a table reference instruction. Accordingly, be careful not to over the stack when performing these operations together. The contents of registers SKs are destroyed when 8 levels are exceeded.

The register SK nesting level is pointed automatically by 3-bit stack pointer (SP). The contents of the stack pointer (SP) can be transferred to register A with the TASP instruction.

Figure 16 shows the stack registers (SKs) structure.

Figure 17 shows the example of operation at subroutine call.

#### (6) Interrupt stack register (SDP)

Interrupt stack register (SDP) is a 1-stage register. When an interrupt occurs, this register (SDP) is used to temporarily store the contents of data pointer, carry flag, skip flag, register A, and register B just before an interrupt until returning to the original routine.

Unlike the stack registers (SKs), this register (SDP) is not used when executing the subroutine call instruction and the table reference instruction.

#### (7) Skip flag

Skip flag controls skip decision for the conditional skip instructions and continuous described skip instructions. When an interrupt occurs, the contents of skip flag is stored automatically in the interrupt stack register (SDP) and the skip condition is retained.

Fig 16. Stack registers (SKs) structure

Fig 17. Example of operation at subroutine call

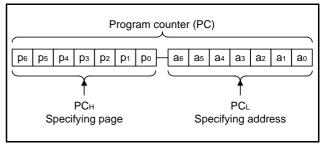

## (8) Program counter (PC)

Program counter (PC) is used to specify a ROM address (page and address). It determines a sequence in which instructions stored in ROM are read. It is a binary counter that increments the number of instruction bytes each time an instruction is executed. However, the value changes to a specified address when branch instructions, subroutine call instructions, return instructions, or the table reference instruction (TABP p) is executed.

Program counter consists of PCH (most significant bit to bit 7) which specifies to a ROM page and PCL (bits 6 to 0) which specifies an address within a page. After it reaches the last address (address 127) of a page, it specifies address 0 of the next page (Figure 18).

Make sure that the PCH does not specify after the last page of the built-in ROM.

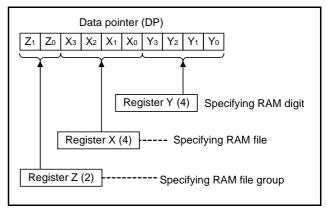

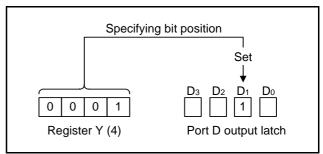

## (9) Data pointer (DP)

Data pointer (DP) is used to specify a RAM address and consists of registers Z, X, and Y. Register Z specifies a RAM file group, register X specifies a file, and register Y specifies a RAM digit (Figure 19).

Register Y is also used to specify the port D bit position.

When using port D, set the port D bit position to register Y certainly and execute the SD, RD, or SZD instruction (Figure 20).

#### Note

Register Z of data pointer is undefined after system is released from reset.

Also, registers Z, X and Y are undefined in the power down mode. After system is returned from the power down mode, set these registers.

Fig 18. Program counter (PC) structure

Fig 19. Data pointer (DP) structure

Fig 20. SD instruction execution example

## **PROGRAM MEMORY (ROM)**

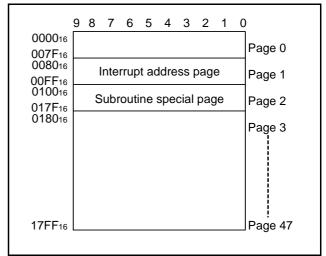

The program memory is a mask ROM. 1 word of ROM is composed of 10 bits. ROM is separated every 128 words by the unit of page (addresses 0 to 127). Table 1 shows the ROM size and pages. Figure 21 shows the ROM map of M34559G6.

Table 8 ROM size and pages

| Part number | ROM (PROM) size<br>(× 10 bits) | Pages        |

|-------------|--------------------------------|--------------|

| M34559G6    | 6144 words                     | 48 (0 to 47) |

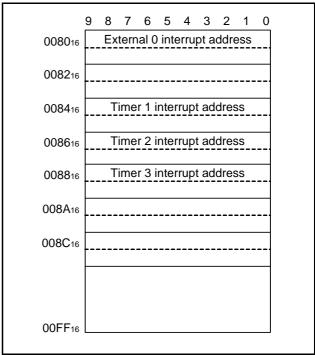

A part of page 1 (addresses 008016 to 00FF16) is reserved for interrupt addresses (Figure 22). When an interrupt occurs, the address (interrupt address) corresponding to each interrupt is set in the program counter, and the instruction at the interrupt address is executed. When using an interrupt service routine, write the instruction generating the branch to that routine at an interrupt address.

Page 2 (addresses 010016 to 017F16) is the special page for subroutine calls. Subroutines written in this page can be called from any page with the 1-word instruction  $(\widetilde{BM})$ . Subroutines extending from page 2 to another page can also be called with the BM instruction when it starts on page 2.

ROM pattern (bits 9 to 0) of all addresses can be used as data areas with the TABP p instruction.

#### **ROM Code Protect Address**

When selecting the protect bit write by using a serial programmer or selecting protect enabled for writing shipment by Renesas Technology corp., reading or writing from/to QzROM is disabled by a serial programmer.

As for the QzROM product in blank, the ROM code is protected by selecting the protect bit write at ROM writing with a serial programmer.

As for the QzROM product shipped after writing, whether the ROM code protect is used or not can be selected as ROM option setup ("MASK option" written in the mask file converter) when ordering.

Fig 21. ROM map of M34559G6

Fig 22. Page 1 (addresses 008016 to 00FF16) structure

## **DATA MEMORY (RAM)**

1 word of RAM is composed of 4 bits, but 1-bit manipulation (with the SB j, RB j, and SZB j instructions) is enabled for the entire memory area. A RAM address is specified by a data pointer. The data pointer consists of registers Z, X, and Y. Set a value to the data pointer certainly when executing an instruction to access RAM (also, set a value after system returns from power down mode).

RAM includes the area for LCD.

When writing "1" to a bit corresponding to displayed segment, the segment is turned on.

Table 9 shows the RAM size. Figure 23 shows the RAM map.

#### Note

Register Z of data pointer is undefined after system is released from reset.

Also, registers Z, X and Y are undefined in power down mode. After system is returned from the power down mode, set these registers.

Table 9 **RAM** size and pages

| Part number | RAM size                       |

|-------------|--------------------------------|

| M34559G6    | 288 words × 4 bits (1152 bits) |

|            | Register Z | Register Z 0 |   |   |   |  |    |    | 1  |    |   |    |    |   |

|------------|------------|--------------|---|---|---|--|----|----|----|----|---|----|----|---|

|            | Register X | 0            | 1 | 2 | 3 |  | 12 | 13 | 14 | 15 | 0 | 1  | 2  |   |

|            | 0          |              |   |   |   |  |    |    |    |    |   |    |    |   |

|            | 1          |              |   |   |   |  |    |    |    |    |   |    |    |   |

|            | 2          |              |   |   |   |  |    |    |    |    |   |    |    |   |

|            | 3          |              |   |   |   |  |    |    |    |    |   |    |    |   |

|            | 4          |              |   |   |   |  |    |    |    |    |   |    |    |   |

|            | 5          |              |   |   |   |  |    |    |    |    |   |    |    |   |

| >          | 6          |              |   |   |   |  |    |    |    |    |   |    |    |   |

| ster       | 7          |              |   |   |   |  |    |    |    |    |   | _  |    |   |

| Register Y | 8          |              |   |   |   |  |    |    |    |    | 0 | 8  | 16 | 2 |

| œ          | 9          |              |   |   |   |  |    |    |    |    | 1 | 9  | 17 | 2 |

|            | 10         |              |   |   |   |  |    |    |    |    | 2 | 10 | 18 | 2 |

|            | 11         |              |   |   |   |  |    |    |    |    | 3 | 11 | 19 | 2 |

|            | 12         |              |   |   |   |  |    |    |    |    | 4 | 12 | 20 | 2 |

|            | 13         |              |   |   |   |  |    |    |    |    | 5 | 13 | 21 | 2 |

|            | 14         |              |   |   |   |  |    |    |    |    | 6 | 14 | 22 | 3 |

|            | 15         |              |   |   |   |  |    |    |    |    | 7 | 15 | 23 | 3 |

Note: The numbers in the shaded area indicate the corresponding segment output pin numbers.

Fig 23. RAM map

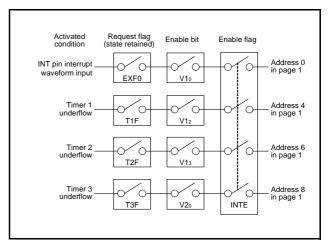

#### INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual address (interrupt address) according to each interrupt source. An interrupt occurs when the following 3 conditions are

- An interrupt activated condition is satisfied (request flag = "1")

- Interrupt enable bit is enabled ("1")

- Interrupt enable flag is enabled (INTE = "1")

Table 10 shows interrupt sources. (Refer to each interrupt request flag for details of activated conditions.)

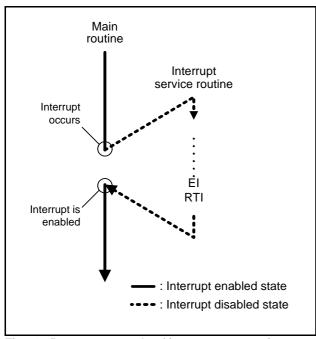

## (1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every interrupt enable/disable. Interrupts are enabled when INTE flag is set to "1" with the EI instruction and disabled when INTE flag is cleared to "0" with the DI instruction. When any interrupt occurs, the INTE flag is automatically cleared to "0," so that other interrupts are disabled until the EI instruction is executed.

## (2) Interrupt enable bit

Use an interrupt enable bit of interrupt control registers V1 and V2 to select the corresponding interrupt or skip instruction.

Table 11 shows the interrupt request flag, interrupt enable bit and skip instruction.

Table 12 shows the interrupt enable bit function.

## (3) Interrupt request flag

When the activated condition for each interrupt is satisfied, the corresponding interrupt request flag is set to "1." Each interrupt request flag except the voltage drop detection circuit interrupt request flag is cleared to "0" when either;

- · an interrupt occurs, or

- · a skip instruction is executed.

The voltage drop detection circuit interrupt request flag cannot be cleared to "0" at the state that the activated condition is satisfied.

Each interrupt request flag is set when the activated condition is satisfied even if the interrupt is disabled by the INTE flag or its interrupt enable bit. Once set, the interrupt request flag retains set until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable state is released while the interrupt request flag is set.

If more than one interrupt request flag is set when the interrupt disable state is released, the interrupt priority level is as follows shown in Table 10.

Table 10 Interrupt sources

| Priority | Interrup          | t source            | Interrupt |  |

|----------|-------------------|---------------------|-----------|--|

| level    | Interrupt name    | Activated condition | address   |  |

| 1        | External 0        | Level change of     | Address 0 |  |

|          | interrupt         | INT0 pin            | in page 1 |  |

| 2        | Timer 1 interrupt | Timer 1             | Address 4 |  |

|          |                   | underflow           | in page 1 |  |

| 3        | Timer 2 interrupt | Timer 2             | Address 6 |  |

|          |                   | underflow           | in page 1 |  |

| 4        | Timer 3 interrupt | Timer 3             | Address 8 |  |

|          |                   | underflow           | in page 1 |  |

Table 11 Interrupt request flag, interrupt enable bit and skip instruction

| Interrupt name       | Interrupt<br>request<br>flag | Skip<br>instruction | Interrupt<br>enable bit |

|----------------------|------------------------------|---------------------|-------------------------|

| External 0 interrupt | EXF0                         | SNZ0                | V10                     |

| Timer 1 interrupt    | T1F                          | SNZT1               | V12                     |

| Timer 2 interrupt    | T2F                          | SNZT2               | V13                     |

| Timer 3 interrupt    | T3F                          | SNZT3               | V20                     |

Table 12 Interrupt enable bit function

| Interrupt enable | Occurrence of | Skip instruction |  |

|------------------|---------------|------------------|--|

| bit              | interrupt     | Skip instruction |  |

| 1                | Enabled       | Invalid          |  |

| 0                | Disabled      | Valid            |  |

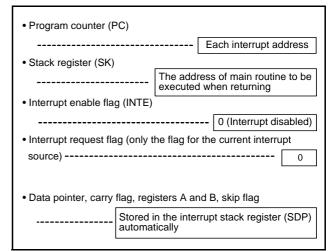

## (4) Internal state during an interrupt

The internal state of the microcomputer during an interrupt is as follows (Figure 25).

- Program counter (PC)

- An interrupt address is set in program counter. The address to be executed when returning to the main routine is automatically stored in the stack register (SK).

- Interrupt enable flag (INTE) INTE flag is cleared to "0" so that interrupts are disabled.

- · Interrupt request flag Only the request flag for the current interrupt source is cleared to "0".

- Data pointer, carry flag, skip flag, registers A and B The contents of these registers and flags are stored automatically in the interrupt stack register (SDP).

# (5) Interrupt processing

When an interrupt occurs, a program at an interrupt address is executed after branching a data store sequence to stack register. Write the branch instruction to an interrupt service routine at an interrupt address. Use the RTI instruction to return from an interrupt service routine.

Interrupt enabled by executing the EI instruction is performed after executing 1 instruction (just after the next instruction is executed). Accordingly, when the EI instruction is executed just before the RTI instruction, interrupts are enabled after returning the main routine. (Refer to Figure 24)

Fig 24. Program example of interrupt processing

Fig 25. Internal state when interrupt occurs

Fig 26. Interrupt system diagram

## (6) Interrupt control registers

• Interrupt control register V1

Interrupt enable bits of external 0, timer 1 and timer 2 are assigned to register V1. Set the contents of this register through register A with the TV1A instruction. The TAV1 instruction can be used to transfer the contents of register V1 to register A.

## • Interrupt control register V2

The timer 3 interrupt enable bit are assigned to register V2. Set the contents of this register through register A with the TV2A instruction. The TAV2 instruction can be used to transfer the contents of register V2 to register A.

Table 13 Interrupt control registers

| Interrupt control register V1 |                                      |   | at reset : 00002                                     | at power down : 00002                            | R/W<br>TAV1/TV1A |  |  |

|-------------------------------|--------------------------------------|---|------------------------------------------------------|--------------------------------------------------|------------------|--|--|

| V13                           | V/A Time and C interment and blockit |   | Interrupt disabled (\$                               | SNZT2 instruction is valid)                      |                  |  |  |

| V 13                          | Timer 2 interrupt enable bit         | 1 | Interrupt enabled (S                                 | Interrupt enabled (SNZT2 instruction is invalid) |                  |  |  |

| V12                           | Timer 1 interrupt enable bit         | 0 | Interrupt disabled (SNZT1 instruction is valid)      |                                                  |                  |  |  |

| V 12                          |                                      | 1 | Interrupt enabled (SNZT1 instruction is invalid)     |                                                  |                  |  |  |

| V11                           | Not used                             | 0 | This bit has no function, but read/write is enabled. |                                                  |                  |  |  |

| V 11                          | Not used                             | 1 |                                                      |                                                  |                  |  |  |

| V10                           | External 0 interrupt enable bit      | 0 | Interrupt disabled (                                 | nterrupt disabled (SNZ0 instruction is valid)    |                  |  |  |

| V 10                          |                                      | 1 | Interrupt enabled (S                                 | SNZ0 instruction is invalid)                     |                  |  |  |

| Interrupt control register V2 |                              |   | at reset : 00002                                     | at power down : 00002                         | R/W<br>TAV2/TV2A |  |  |  |

|-------------------------------|------------------------------|---|------------------------------------------------------|-----------------------------------------------|------------------|--|--|--|

| V23                           | Not used                     | 0 | This bit has no function, but read/write is enabled. |                                               |                  |  |  |  |

|                               |                              | 1 |                                                      |                                               |                  |  |  |  |

| V22                           | Not used                     | 0 | This bit has no function, but read/write is enabled. |                                               |                  |  |  |  |

| V ZZ                          | VZZ Not used                 |   | This bit has no function, but read/white is enabled. |                                               |                  |  |  |  |

| V21                           | Not used                     | 0 | This bit has no function, but read/write is enabled. |                                               |                  |  |  |  |

| V Z1                          | Not used                     | 1 |                                                      |                                               |                  |  |  |  |

| 1/20                          | Timer 3 interrupt enable bit | 0 | Interrupt disabled (S                                | terrupt disabled (SNZT3 instruction is valid) |                  |  |  |  |

| V20                           | Timer 3 interrupt enable bit | 1 | Interrupt enabled (S                                 | SNZT3 instruction is invalid)                 |                  |  |  |  |

Note 1. "R" represents read enabled, and "W" represents write enabled.

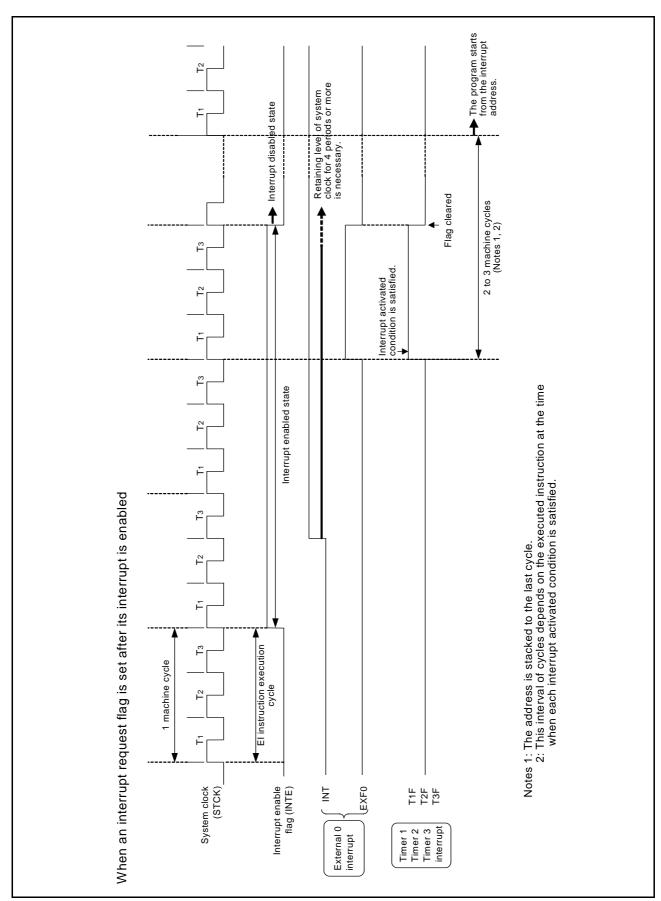

## (7) Interrupt sequence

Interrupts occur only when the respective INTE flag, interrupt enable bits (V10, V12, V13, V30), and interrupt request flag are set to "1." The interrupt occurs two or three cycles after the cycle where all the above three conditions are satisfied.

The interrupt occurs after three machine cycles if instructions other than one-cycle instruction are executed when the conditions are satisfied (Refer to Figure 27).

Fig 27. Interrupt sequence

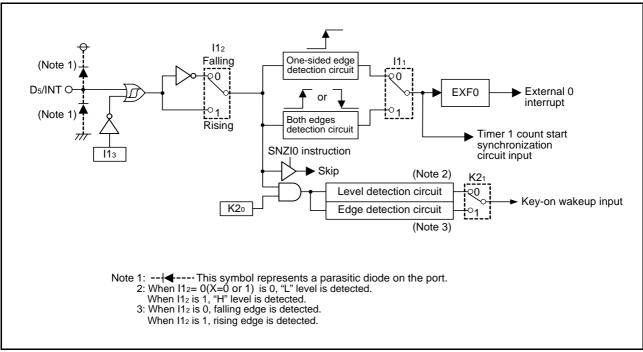

## **EXTERNAL INTERRUPTS**

The 4559 Group has the external 0 interrupt. An external interrupt request occurs when a valid waveform is input to an interrupt input pin (edge detection).

The external interrupt can be controlled with the interrupt control register I1.

Table 14 External interrupt activated conditions

| Name                 | Input pin | Activated condition                                                                                                                               | Valid waveform selection bit |

|----------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| External 0 interrupt | D5/INT    | When the next waveform is input to D₅/INT pin  • Falling waveform ("H" → "L")  • Rising waveform ("L" → "H")  • Both rising and falling waveforms | I11<br>I12                   |

Fig 28. External interrupt circuit structure

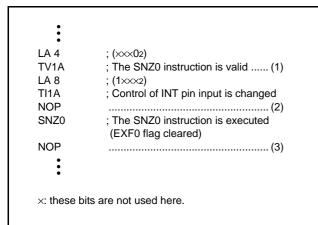

## (1) External 0 interrupt request flag (EXF0)

External 0 interrupt request flag (EXF0) is set to "1" when a valid waveform is input to D5/INT pin.

The valid waveforms causing the interrupt must be retained at their level for 4 clock cycles or more of the system clock (Refer to Figure 27).

The state of EXF0 flag can be examined with the skip instruction (SNZ0). Use the interrupt control register V1 to select the interrupt or the skip instruction. The EXF0 flag is cleared to "0" when an interrupt occurs or when the next instruction is skipped with the skip instruction.

#### • External 0 interrupt activated condition

External 0 interrupt activated condition is satisfied when a valid waveform is input to D5/INT pin.

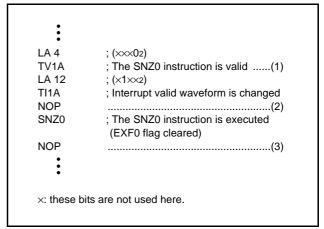

The valid waveform can be selected from rising waveform, falling waveform or both rising and falling waveforms. An example of how to use the external 0 interrupt is as follows.

- (1) Set the bit 3 of register I1 to "1" for the INT pin to be in the input enabled state.

- (2) Select the valid waveform with the bits 1 and 2 of register I1.

- (3) Clear the EXF0 flag to "0" with the SNZ0 instruction.

- (4) Set the NOP instruction for the case when a skip is performed with the SNZ0 instruction.

- (5) Set both the external 0 interrupt enable bit (V10) and the INTE flag to "1."

The external 0 interrupt is now enabled. Now when a valid waveform is input to the D5/INT pin, the EXF0 flag is set to "1" and the external 0 interrupt occurs.

## (2) External interrupt control registers

(1) Interrupt control register I1

Register I1 controls the valid waveform for the external 0 interrupt. Set the contents of this register through register A with the TI1A instruction. The TAI1 instruction can be used to transfer the contents of register I1 to register A.

## Table 15 External interrupt control register

|             | Interrupt control register I1              |   | at reset : 00002                                     | at power down : state retained                   | R/W<br>TAI1/TI1A |  |  |  |

|-------------|--------------------------------------------|---|------------------------------------------------------|--------------------------------------------------|------------------|--|--|--|

| l13         | INT pin input control bit (Note 2)         | 0 | INT pin input disabled                               |                                                  |                  |  |  |  |

| 113         | IN F piri input control bit (Note 2)       | 1 | INT pin input enable                                 | INT pin input enabled                            |                  |  |  |  |

| 112         | Interrupt valid waveform for INT pin/      | 0 | Falling waveform instruction)/"L" level              | ("L" level of INT pin is recognized              | d with the SNZIO |  |  |  |

| 112         | return level selection bit (Note 2)        | 1 | Rising waveform instruction)/"H" leve                | ("H" level of INT pin is recognized              | d with the SNZIO |  |  |  |

| <b>I1</b> 1 | INT pip adge detection airquit control bit | 0 | One-sided edge detected                              |                                                  |                  |  |  |  |

| 1111        | INT pin edge detection circuit control bit | 1 | Both edges detected                                  |                                                  |                  |  |  |  |

| 110         | INT pin timer 1 count start synchronous    | 0 | Timer 1 count start synchronous circuit not selected |                                                  |                  |  |  |  |

| 110         | circuit selection bit                      | 1 | Timer 1 count start                                  | Timer 1 count start synchronous circuit selected |                  |  |  |  |

Note 1."R" represents read enabled, and "W" represents write enabled.

Note 2. When the contents of I12 and I13 are changed, the external interrupt request flag EXF0 may be set.

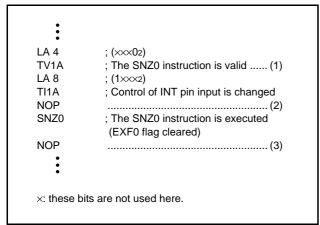

#### (3) Notes on interrupts

- (1) Bit 3 of register I1

- When the input of the INT pin is controlled with the bit 3 of register I1 in software, be careful about the following notes.

- Depending on the input state of the D5/INT pin, the external 0 interrupt request flag (EXF0) may be set when the bit 3 of register I1 is changed. In order to avoid the occurrence of an unexpected interrupt, clear the bit 0 of register V1 to "0" (refer to (1) in Figure 29.) and then, change the bit 3 of register I1. In addition, execute the SNZ0 instruction to clear the EXF0 flag to "0" after executing at least one instruction (refer to (2)

Also, set the NOP instruction for the case when a skip is performed with the SNZ0 instruction (refer to (3) in Figure 29.).

Fig 29. External 0 interrupt program example-1

- (2) Bit 3 of register I1

- When the bit 3 of register I1 is cleared to "0", the power down mode is selected and the input of INT pin is disabled, be careful about the following notes.

- When the INT pin input is disabled (register I13 = "0"), set the key-on wakeup of INT pin to be invalid (register K20 = "0") before system enters to power down mode. (refer to (1) in Figure 30.).

```

LA 0

: (×××02)

TK2A

; INT0 key-on wakeup disabled .....(1)

DI

EPOF

POF2

; RAM back-up

x: these bits are not used here.

```

Fig 30. External 0 interrupt program example-2

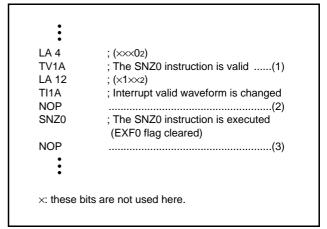

- (3) Bit 2 of register I1

- When the interrupt valid waveform of the INT pin is changed with the bit 2 of register I1 in software, be careful about the following notes.

- Depending on the input state of the D5/INT pin, the external 0 interrupt request flag (EXF0) may be set when the bit 2 of register I1 is changed. In order to avoid the occurrence of an unexpected interrupt, clear the bit 0 of register V1 to "0" (refer to (1) in Figure 31.) and then, change the bit 2 of register I1 is changed.

In addition, execute the SNZ0 instruction to clear the EXF0 flag to "0" after executing at least one instruction (refer to (2) in Figure 31.).

Also, set the NOP instruction for the case when a skip is performed with the SNZ0 instruction (refer to (3) in Figure

Fig 31. External 0 interrupt program example-3

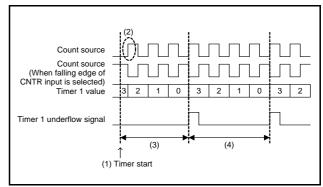

#### **TIMERS**

The 4559 Group has the following timers.

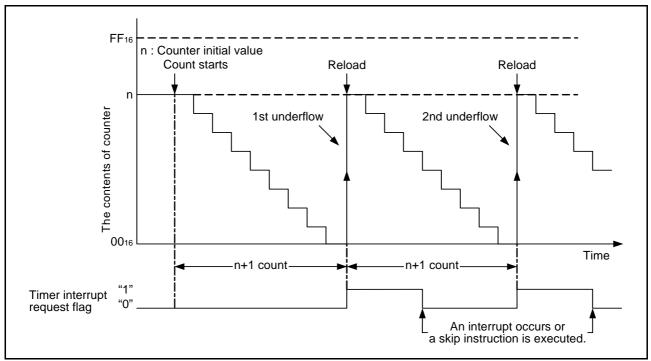

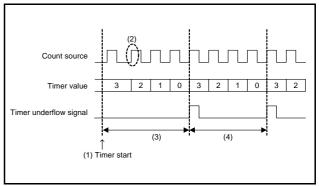

- · Programmable timer

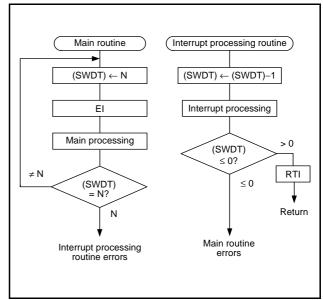

- The programmable timer has a reload register and enables the frequency dividing ratio to be set. It is decremented from a setting value n. When it underflows (count to n + 1), a timer interrupt request flag is set to "1," new data is loaded from the reload register, and count continues (auto-reload function).

- Fixed dividing frequency timer The fixed dividing frequency timer has the fixed frequency dividing ratio (n). An interrupt request flag is set to "1" after every n count of a count pulse.

Fig 32. Auto-reload function

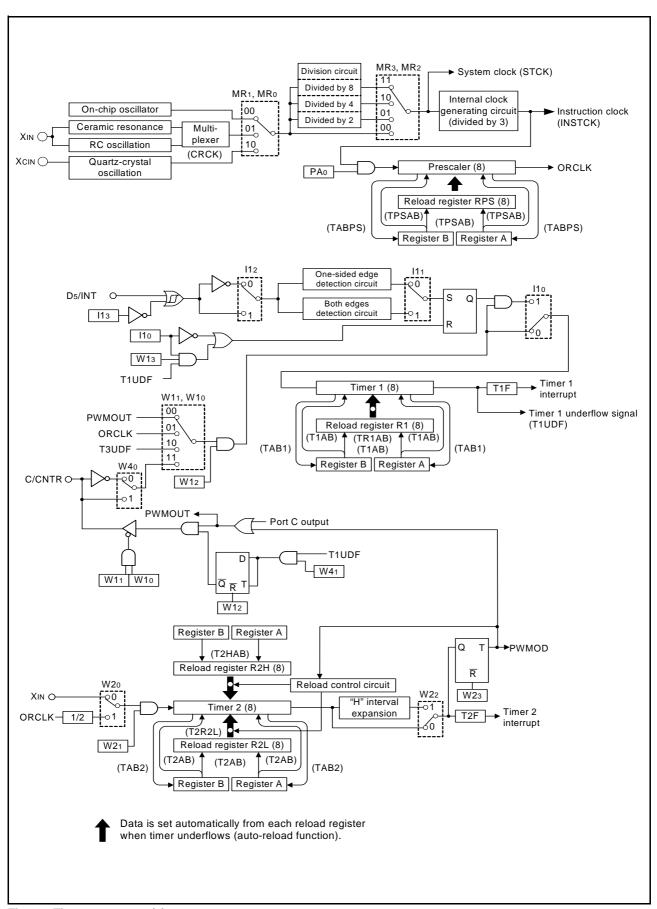

The 4559 Group timer consists of the following circuits.

- Prescaler : 8-bit programmable timer

- Timer 1 : 8-bit programmable timer

- Timer 2 : 8-bit programmable timer

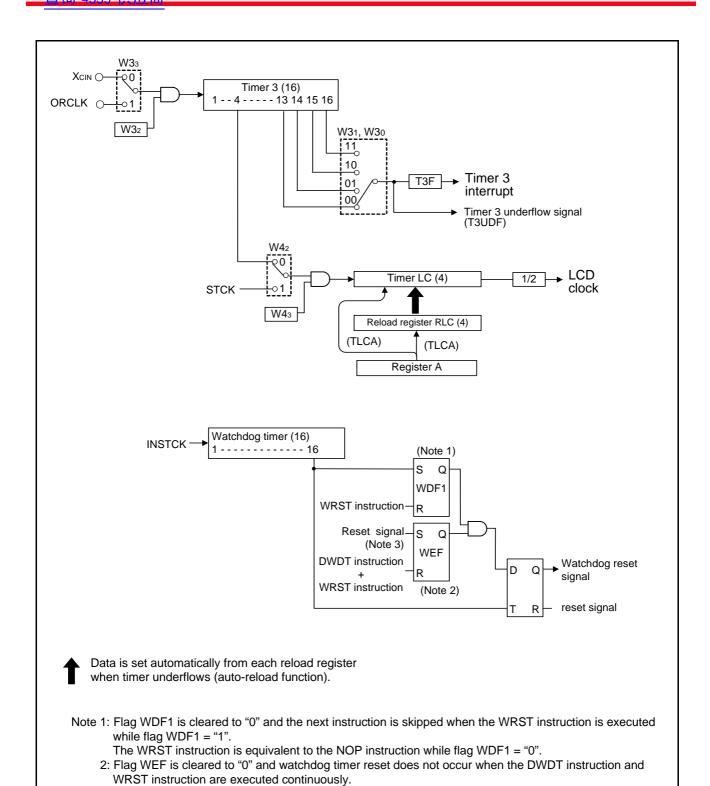

- Timer 3: 16-bit fixed frequency timer

- Timer LC: 4-bit programmable timer

- Watchdog timer: 16-bit fixed frequency timer

(Timers 1, 2 and 3 have the interrupt function, respectively)

Prescaler, timer 1, timer 2, timer 3 and timer LC can be controlled with the timer control registers PA and W1 to W4. The watchdog timer is a free counter which is not controlled with the control register.

Each function is described below.

Table 16 Function related timers

| Circuit        | Structure                                                                                                           | Count source                                                                      | Frequency dividing ratio        | Use of output signal                                                                 | Control register |

|----------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------|------------------|

| Prescaler      | 8-bit programmable binary down counter                                                                              | Instruction clock (INSTCK)                                                        | 1 to 256                        | Timer 1 count source  Timer 2 count source  Timer 3 count source                     | PA               |

| Timer 1        | 8-bit programmable<br>binary down counter<br>(link to INT input)<br>(carrier wave output auto-<br>control function) | PWM signal (PWMOUT) Prescaler output (ORCLK) Timer 3 underflow (T3UDF) CNTR input | 1 to 256                        | CNTR output control     Timer 1 interrupt                                            | W1<br>W4         |

| Timer 2        | 8-bit programmable<br>binary down counter<br>(with carrier wave<br>generation function)                             | XIN input     Prescaler output divided by 2     (ORCLK/2)                         | 1 to 256                        | <ul><li>Timer 1 count source</li><li>CNTR output</li><li>Timer 2 interrupt</li></ul> | W2<br>W4         |

| Timer 3        | 16-bit fixed dividing frequency                                                                                     | XIN input     Prescaler output (ORCLK)                                            | 8192<br>16384<br>32768<br>65536 | Timer 1 count source Timer LC count source Timer 3 interrupt                         | W3               |

| Timer LC       | 4-bit programmable binary down counter                                                                              | Bit 4 of timer 3 (T34)     System clock (STCK)                                    | 1 to 16                         | LCD clock                                                                            | W4               |

| Watchdog timer | 16-bit fixed dividing frequency                                                                                     | Instruction clock (INSTCK)                                                        | 65536                           | <ul><li>System reset (counting twice)</li><li>Decision of flag WDF1</li></ul>        | -                |

Fig 33. Timers structure (1)

Fig 34. Timers structure (2)

3: The WEF flag is set to "1" at system reset or RAM back-up mode.

# Table 17 Timer control registers

|                 | Timer control register PA  |   | at reset : 02        | at power down : 02 | W<br>TPAA |

|-----------------|----------------------------|---|----------------------|--------------------|-----------|

| PA <sub>0</sub> | DA a Draggeler control bit |   | Stop (state retained | )                  |           |

| FAU             | Prescaler control bit      | 1 | Operating            |                    |           |

| Timer control register W1 |                                               |     | at re | set: 00002                 | at power down : state retained | R/W<br>TAW1/TW1A |

|---------------------------|-----------------------------------------------|-----|-------|----------------------------|--------------------------------|------------------|

| W13                       | Timer 1 count auto-stop circuit selection bit |     | Time  | r 1 count auto-stop        | circuit not selected           |                  |

| VV 13                     | (Note 2)                                      | 1   | Time  | r 1 count auto-stop        | circuit selected               |                  |

| W12                       | /12 Timer 1 control bit                       |     | Stop  | (state retained)           |                                |                  |

| VV 12                     | Timer i control bit                           | 1   | Oper  | Operating                  |                                |                  |

|                           |                                               | W11 | W10   |                            | Count source                   |                  |

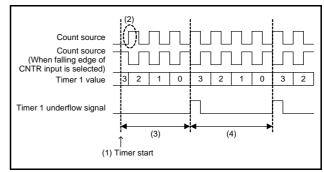

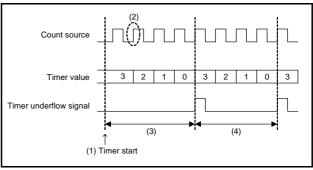

| W11                       |                                               | 0   | 0     | 0 PWM signal (PWMOUT)      |                                |                  |

|                           | Timer 1 count source selection bits (Note 3)  | 0   | 1     | 1 Prescaler output (ORCLK) |                                |                  |

| W10                       |                                               | 1   | 0     | Timer 3 underflow          | signal (T3UDF)                 |                  |

| **10                      |                                               | 1   | 1     | CNTR input                 |                                |                  |

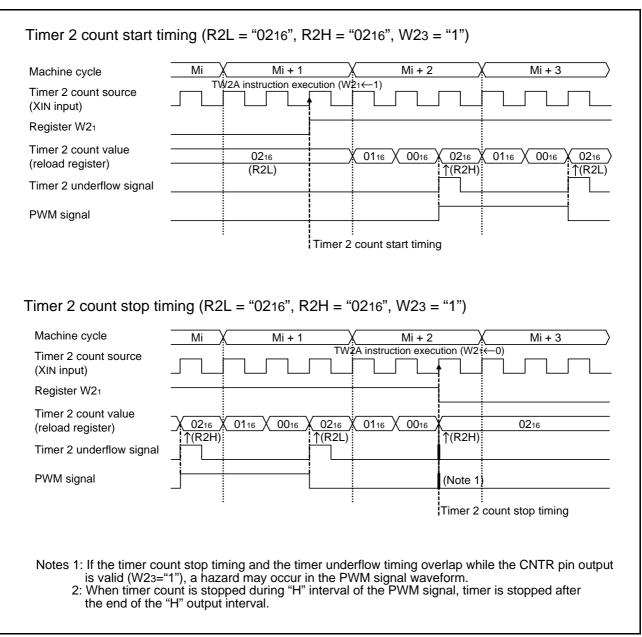

| Timer control register W2           |                                                        | at reset : 00002 |                                                    | at power down : 00002   | R/W<br>TAW2/TW2A |  |  |  |

|-------------------------------------|--------------------------------------------------------|------------------|----------------------------------------------------|-------------------------|------------------|--|--|--|

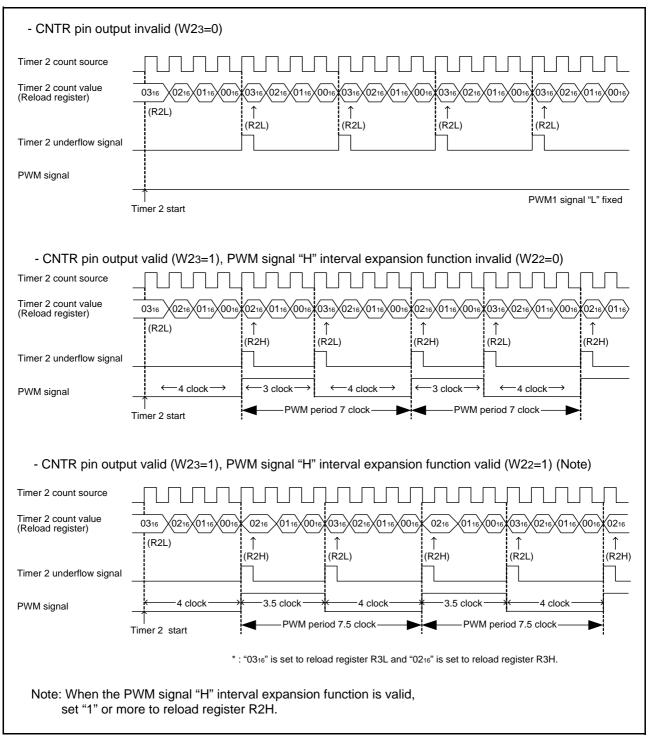

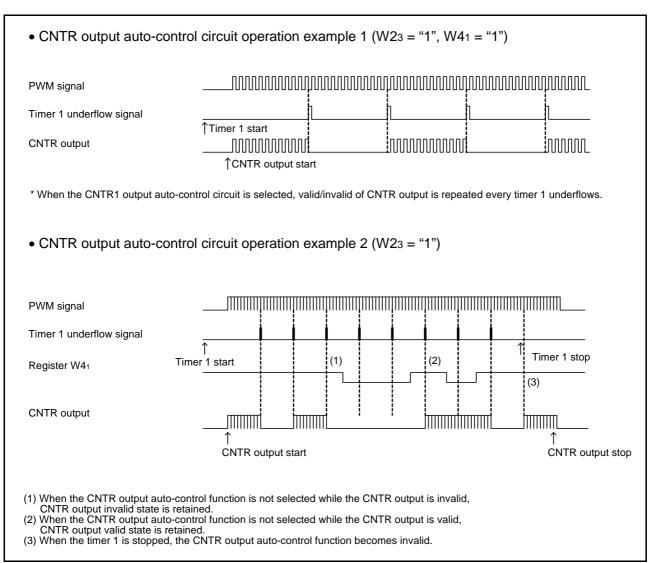

| MO. CNITE air franction control bit |                                                        | 0                | CNTR pin output invalid                            | CNTR pin output invalid |                  |  |  |  |

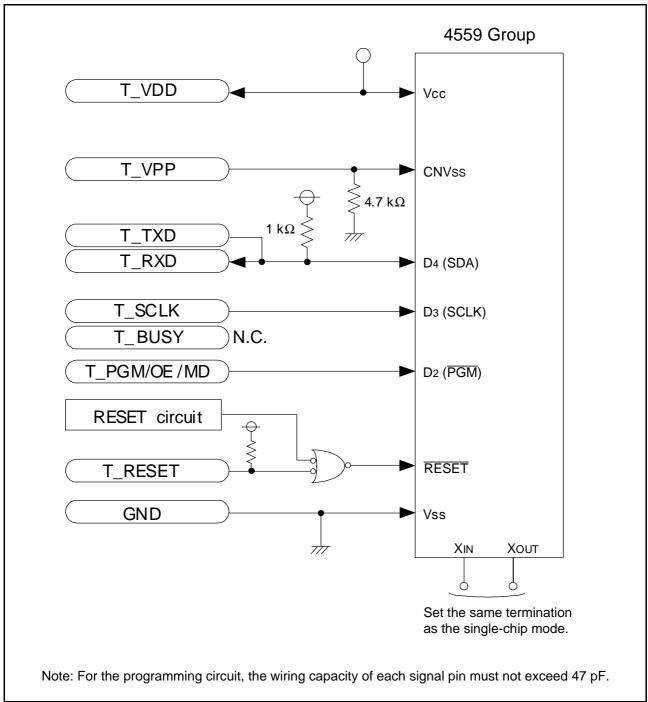

| VVZ3                                | CNTR pin function control bit                          | 1                | CNTR pin output valid                              | CNTR pin output valid   |                  |  |  |  |