# LM49370 Boomer® Audio Power Amplifier Series

# Audio Sub-System with an Ultra Low EMI, Spread Spectrum, Class D Loudspeaker Amplifier, a Dual-Mode Stereo Headphone Amplifier, and a Dedicated PCM Interface for Bluetooth Transceivers

# 1.0 General Description

The LM49370 is an integrated audio subsystem that supports both analog and digital audio functions. The LM49370 includes a high quality stereo DAC, a mono ADC, a stereo headphone amplifier, which supports output cap-less (OCL) or AC-coupled (SE) modes of operation, a mono earpiece amplifier, and an ultra-low EMI spread spectrum Class D loudspeaker amplifier. It is designed for demanding applications in mobile phones and other portable devices.

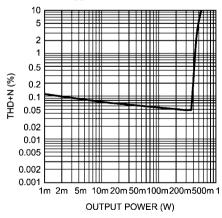

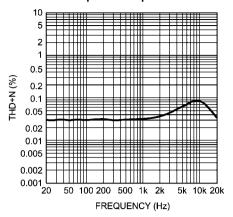

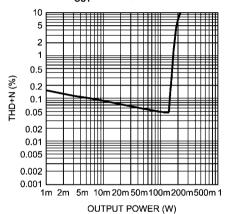

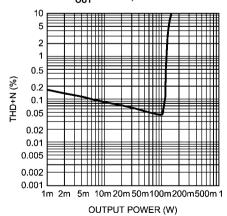

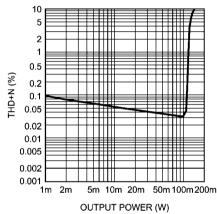

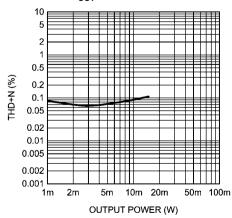

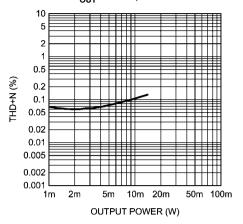

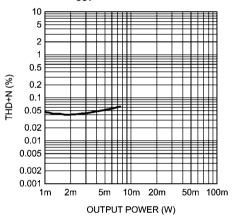

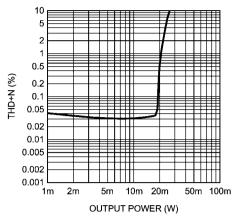

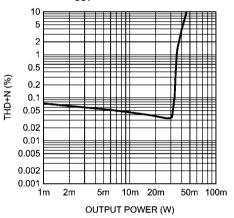

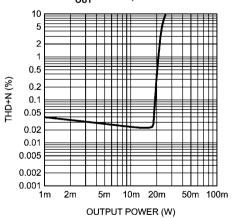

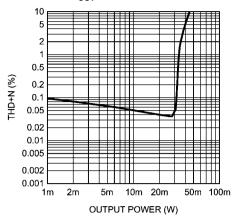

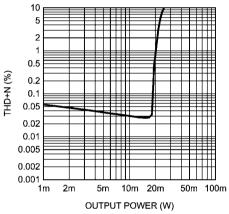

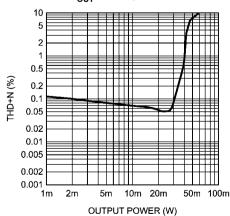

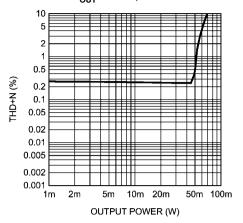

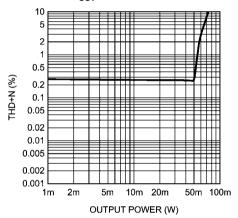

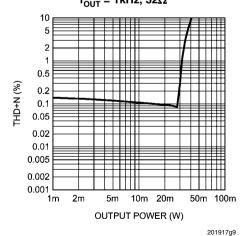

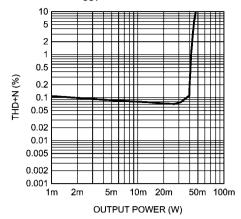

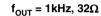

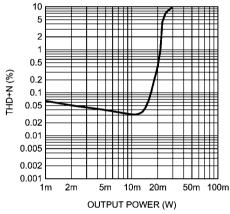

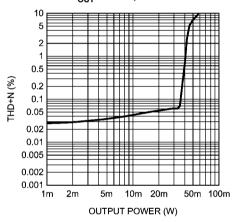

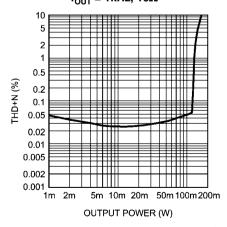

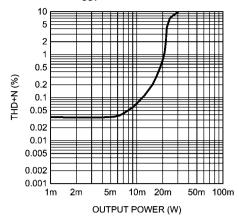

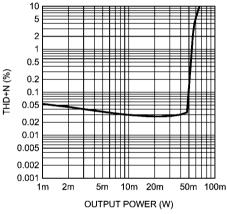

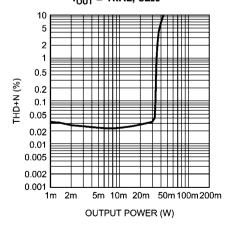

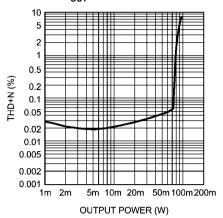

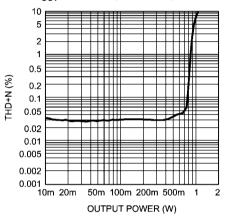

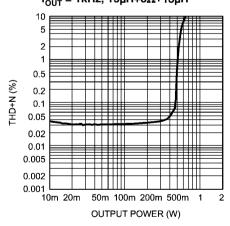

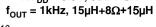

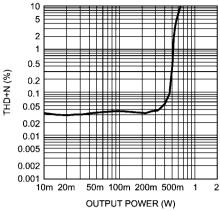

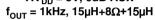

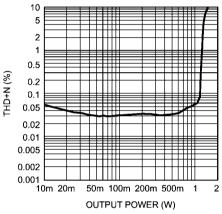

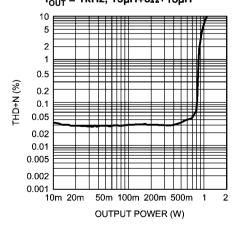

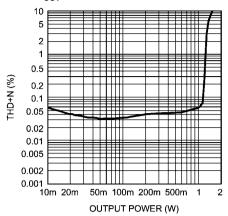

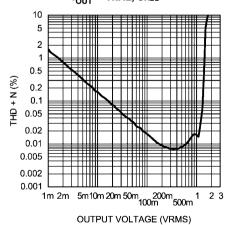

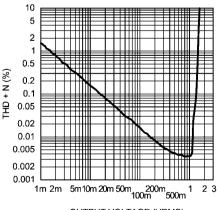

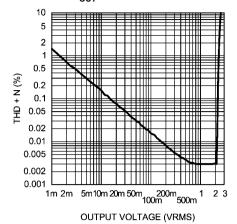

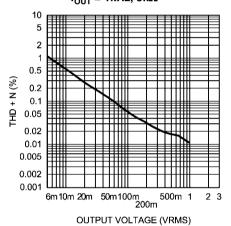

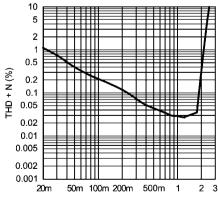

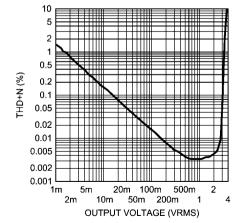

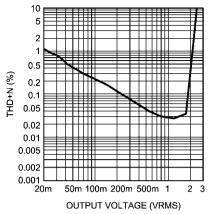

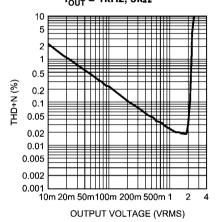

The LM49370 features a bi-directional I²S interface and a bi-directional PCM interface for full range audio on either interface. The LM49370 utilizes an I²C or SPI compatible interface for control. The stereo DAC path features an SNR of 85 dB with an 18-bit 48 kHz input. In SE mode the headphone amplifier delivers at least 33 mW $_{RMS}$  to a 32 $\Omega$  single-ended stereo load with less than 1% distortion (THD+N) when  $A\_V_{DD}=3.3V$ . The mono earpiece amplifier delivers at least 115mW $_{RMS}$  to a 32 $\Omega$  bridged-tied load with less than 1% distortion (THD+N) when  $A\_V_{DD}=3.3V$ . The mono speaker amplifier delivers up to 490mW into an 8 $\Omega$  load with less than 1% distortion when LS $\_V_{DD}=3.3V$  and up to 1.2W when LS $\_V_{DD}=5.0V$ .

The LM49370 employs advanced techniques to reduce power consumption, to reduce controller overhead, to speed development time, and to eliminate click and pop. Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. It is therefore ideally suited for mobile phone and other low voltage applications where minimal power consumption, PCB area and cost are primary requirements.

# 2.0 Applications

- Smart phones

- Mobile Phones and Multimedia Terminals

- PDAs, Internet Appliances and Portable Gaming

- Portable DVD/CD/AAC/MP3 Players

- Digital Cameras/Camcorders

# 3.0 Key Specifications

| $\blacksquare$ P <sub>HP (AC-COUP)</sub> (A_V <sub>DD</sub> = 3.3V, 32Ω, 1% THD) | 33 mW  |

|----------------------------------------------------------------------------------|--------|

| ■ $P_{HP (OCL)} (A_V_{DD} = 3.3V, 32\Omega, 1\% THD)$                            | 31 mW  |

| ■ $P_{LS}$ ( $LS_{DD} = 5V, 8Ω, 1% THD)$                                         | 1.2 W  |

| ■ $P_{LS}$ (LS_ $V_{DD}$ = 4.2V, 8Ω, 1% THD)                                     | 900 mW |

| ■ $P_{LS}$ (LS_ $V_{DD}$ = 3.3V, 8Ω, 1% THD)                                     | 490 mW |

| ■ Shutdown Current                                                               | 0.8 uA |

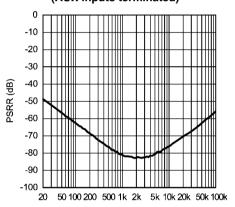

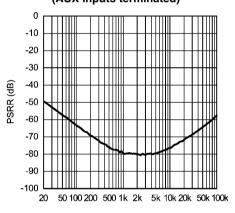

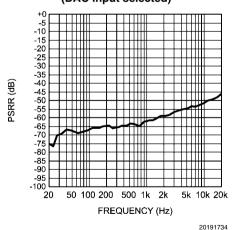

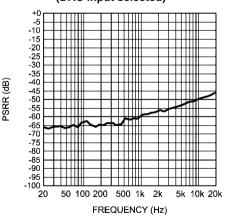

$PSRR_{LS}$  (217 Hz,  $LS_{DD} = 3.3V$ ) 70 dB

| <ul> <li>SNR<sub>LS</sub> (AUX IN to Loudspeaker)</li> </ul>        | 90 dB (typ) |

|---------------------------------------------------------------------|-------------|

| ■ SNR <sub>DAC</sub> (Stereo DAC to AUXOUT)                         | 85 dB (typ) |

| <ul> <li>SNR<sub>ADC</sub> (Mono ADC from Cell Phone In)</li> </ul> | 90 dB (typ) |

| ■ SNR <sub>HP</sub> (Aux In to Headphones)                          | 98 dB (typ) |

## 4.0 Features

- Spread Spectrum Class D architecture reduces EMI

- Mono Class D 8Ω amplifier, 490 mW at 3.3V

- OCL or AC-coupled headphone operation

- 33mW stereo headphone amplifier at 3.3V

- 115 mW earpiece amplifier at 3.3V

- 18-bit stereo DAC

- 16-bit mono ADC

- 8 kHz to 192 kHz stereo audio playback

- 8 kHz to 48 kHz mono recording

- Bidirectional I<sup>2</sup>S compatible audio interface

- Bidirectional PCM compatible audio interface for Bluetooth transceivers

- I<sup>2</sup>S-PCM Bridge with sample rate conversion

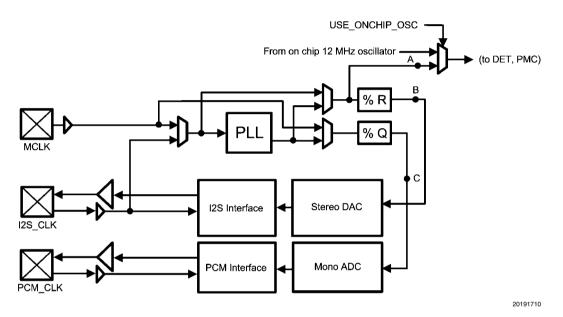

- Sigma-Delta PLL for operation from any clock at any sample rate

- Digital 3D Stereo Enhancement

- FIR filter programmability for simple tone control

- Low power clock network operation if a 12 MHz or 13 MHz system clock is available

- Read/write I<sup>2</sup>C or SPI compatible control interface

- Automatic headphone & microphone detection

- Support for internal and external microphones

- Automatic gain control for microphone input

- Differential audio I/O for external cellphone module

- Mono differential auxiliary output

- Stereo auxiliary inputs

- Differential microphone input for internal microphone

- Flexible audio routing from input to output

- 32 Step volume control for mixers in 1.5 dB steps

- 16 Step volume control for microphone in 2 dB steps

- Programmable sidetone attenuation in 3 dB steps

- Two configurable GPIO ports

- Multi-function IRQ output

- Micro-power shutdown mode

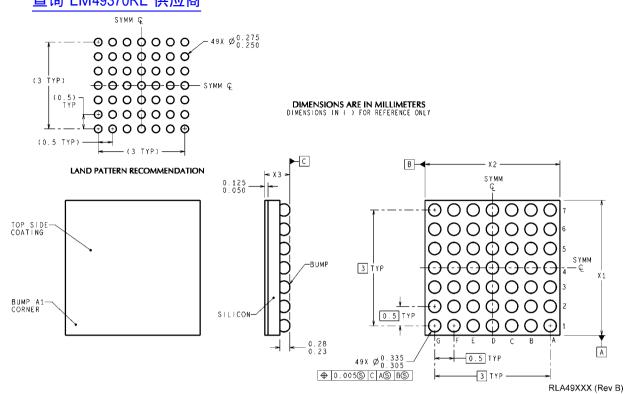

- Available in the 4 x 4 mm 49 bump micro SMDxt package

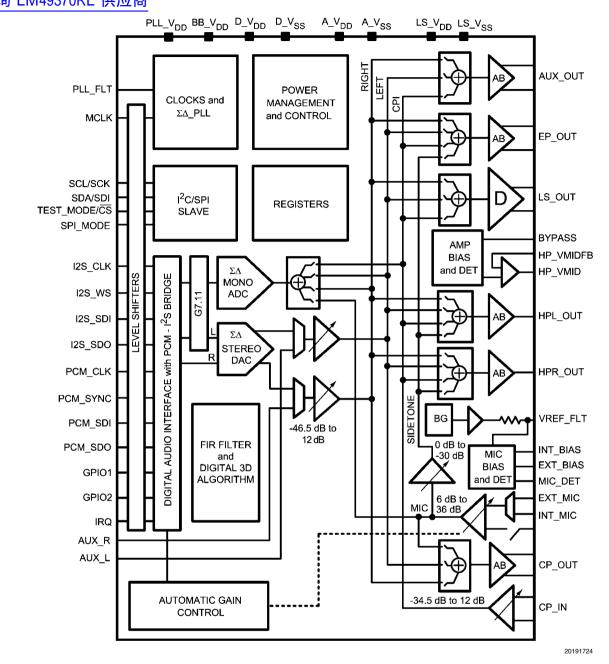

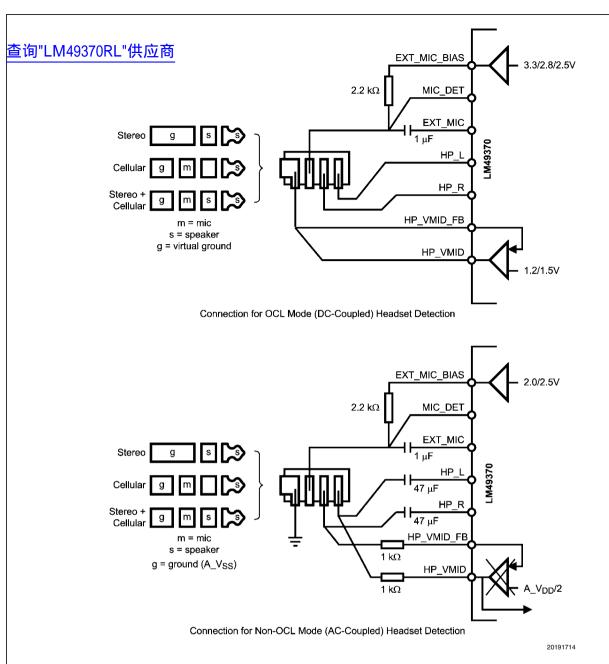

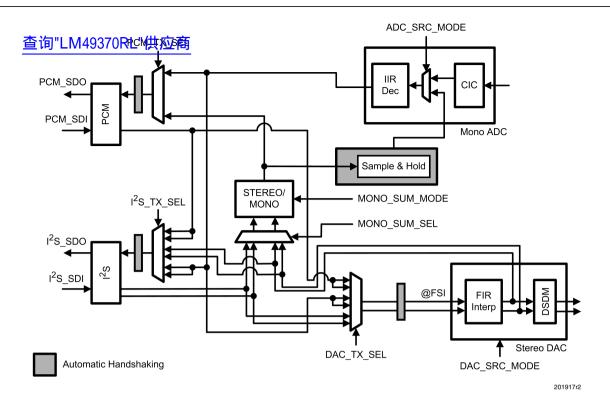

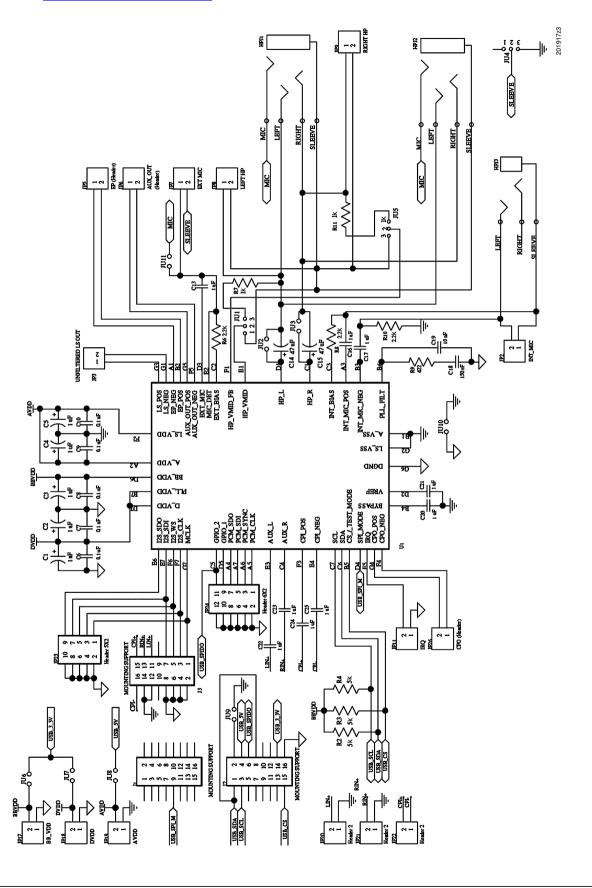

# **5.0 LM49370 Overview** §询"LM49370RL"供应商

FIGURE 1. Conceptual Schematic

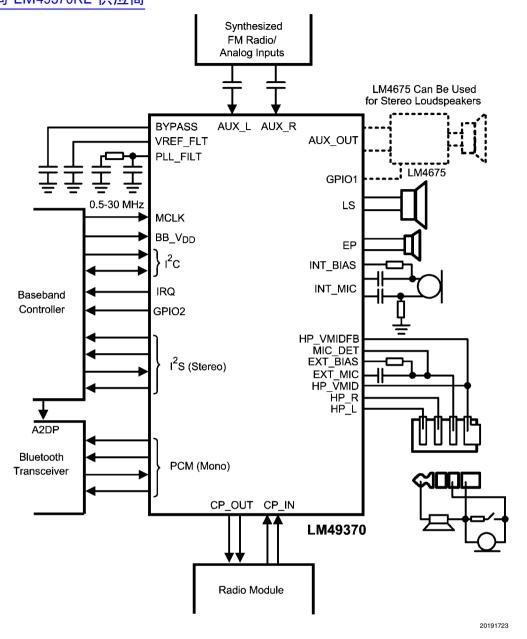

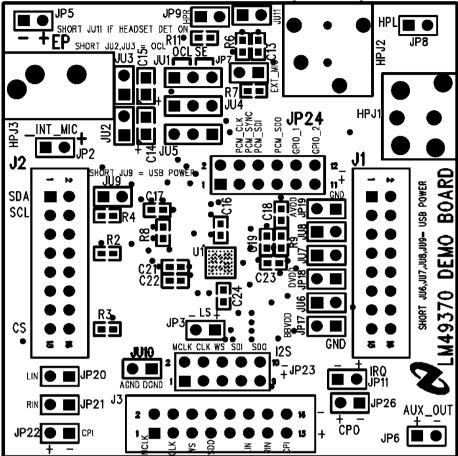

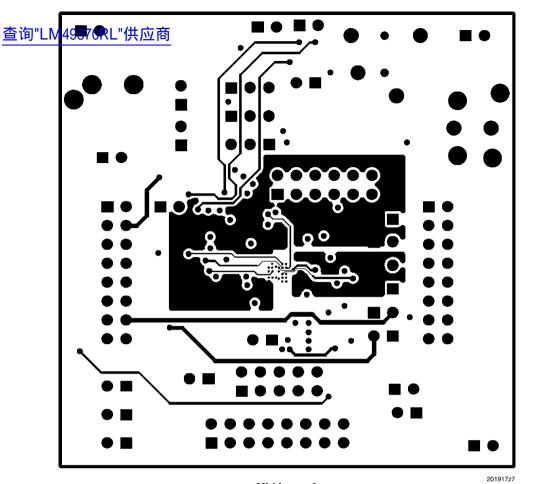

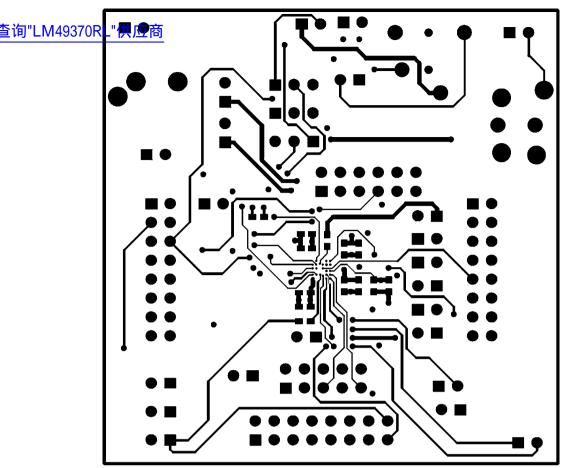

# **6.0 Typical Application** 查询"LM49370RL"供应商

FIGURE 2. Example Application in Multimedia Mobile Phone

# **Table of Contents**

| 10 General Description  2.0 Applications                                                                                                                 | 1    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.0 Applications                                                                                                                                         | 1    |

| 3.0 Key Specifications                                                                                                                                   |      |

| 4.0 Features                                                                                                                                             |      |

| 5.0 LM49370 Overview                                                                                                                                     | 2    |

| 6.0 Typical Application                                                                                                                                  | 3    |

| 7.0 Connection Diagrams                                                                                                                                  |      |

| 7.1 PIN TYPE DEFINITIONS                                                                                                                                 |      |

| 8.0 Absolute Maximum Ratings                                                                                                                             | 8    |

| 9.0 Operating Ratings                                                                                                                                    | 8    |

| 10.0 Electrical Characteristics (Notes 1, 2) Unless otherwise stated PLL_V <sub>DD</sub> = 3.3V, D_V <sub>DD</sub> = 3.3V, BB_V <sub>DD</sub> = 1.8V     | J    |

| A_V <sub>DD</sub> = 3.3V, LS_V <sub>DD</sub> = 3.3V. The following specifications apply for the circuit shown in <i>Figure 2</i> unless otherwise stated |      |

| Limits apply for 25°C.                                                                                                                                   | 8    |

| 11.0 System Control                                                                                                                                      |      |

| 11.1 PC SIGNALS                                                                                                                                          |      |

| 11.2 I <sup>2</sup> C DATA VALIDITY                                                                                                                      |      |

| 11.3 I <sup>2</sup> C START AND STOP CONDITIONS                                                                                                          | . 14 |

| 11.4 TRANSFERRING DATA                                                                                                                                   | . 14 |

| 11.5 I <sup>2</sup> C TIMING PARAMETERS                                                                                                                  | . 16 |

| 12.0 Status & Control Registers                                                                                                                          | . 18 |

| 12.1 BASIC CONFIGURATION REGISTER                                                                                                                        | . 19 |

| 12.2 CLOCKS CONFIGURATION REGISTER                                                                                                                       | . 20 |

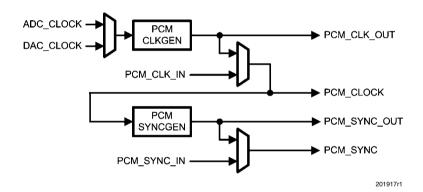

| 12.3 LM49370 CLOCK NETWORK                                                                                                                               | . 21 |

| 12.4 COMMON CLOCK SETTINGS FOR THE DAC & ADC                                                                                                             | . 22 |

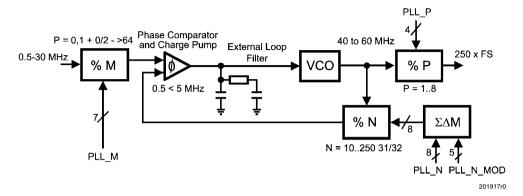

| 12.5 PLL M DIVIDER CONFIGURATION REGISTER                                                                                                                | . 23 |

| 12.6 PLL N DIVIDER CONFIGURATION REGISTER                                                                                                                | . 24 |

| 12.7 PLL P DIVIDER CONFIGURATION REGISTER                                                                                                                |      |

| 12.8 PLL N MODULUS CONFIGURATION REGISTER                                                                                                                |      |

| 12.9 FURTHER NOTES ON PLL PROGRAMMING                                                                                                                    | . 27 |

| 12.10 ADC_1 CONFIGURATION REGISTER                                                                                                                       |      |

| 12.11 ADC_2 CONFIGURATION REGISTER                                                                                                                       | . 31 |

| 12.12 AGC_1 CONFIGURATION REGISTER                                                                                                                       |      |

| 12.13 AGC_2 CONFIGURATION REGISTER                                                                                                                       | . 33 |

| 12.14 AGC_3 CONFIGURATION REGISTER                                                                                                                       |      |

| 12.15 AGC OVERVIEW                                                                                                                                       |      |

| 12.16 MIC_1 CONFIGURATION REGISTER                                                                                                                       |      |

| 12.17 MIC_2 CONFIGURATION REGISTER                                                                                                                       |      |

| 12.18 SIDETONE ATTENUATION REGISTER                                                                                                                      |      |

| 12.19 CP_INPUT CONFIGURATION REGISTER                                                                                                                    | . 38 |

| 12.20 AUX_LEFT CONFIGURATION REGISTER                                                                                                                    | . 39 |

| 12.21 AUX_RIGHT CONFIGURATION REGISTER                                                                                                                   |      |

| 12.22 DAC CONFIGURATION REGISTER                                                                                                                         |      |

| 12.23 CP_OUTPUT CONFIGURATION REGISTER                                                                                                                   | . 41 |

| 12.24 AUX_OUTPUT CONFIGURATION REGISTER                                                                                                                  |      |

| 12.25 LS_OUTPUT CONFIGURATION REGISTER                                                                                                                   |      |

| 12.26 HP_OUTPUT CONFIGURATION REGISTER                                                                                                                   | . 42 |

| 12.27 EP_OUTPUT CONFIGURATION REGISTER                                                                                                                   |      |

| 12.28 DETECT CONFIGURATION REGISTER                                                                                                                      |      |

| 12.29 HEADSET DETECT OVERVIEW                                                                                                                            |      |

| 12.31 3D CONFIGURATION REGISTER                                                                                                                          |      |

| 12.31 3D CONFIGURATION REGISTER                                                                                                                          |      |

| 12.33 I2S PORT CLOCK CONFIGURATION REGISTER                                                                                                              | . 49 |

| 12.33 DIGITAL AUDIO DATA FORMATS                                                                                                                         |      |

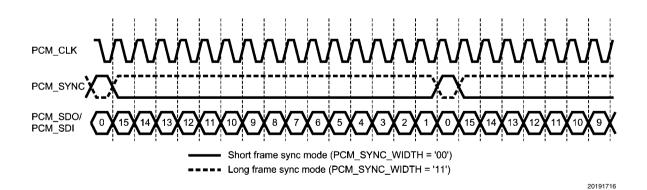

| 12.35 PCM PORT MODE CONFIGURATION REGISTER                                                                                                               | . 51 |

| 12.35 PCM PORT MODE CONFIGURATION REGISTER                                                                                                               |      |

| 12.37 SRC CONFIGURATION REGISTER                                                                                                                         |      |

| 12.37 SAC CONFIGURATION REGISTER                                                                                                                         |      |

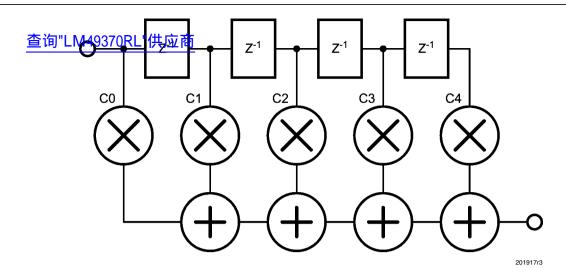

| 12.39 DAC PATH COMPENSATION FIR CONFIGURATION REGISTERS                                                                                                  | . 56 |

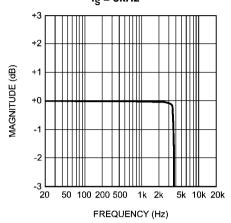

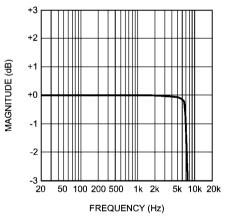

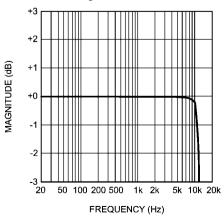

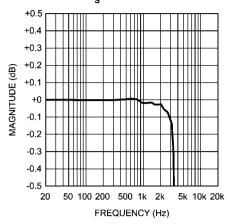

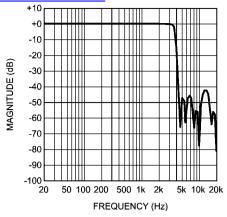

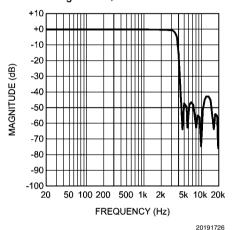

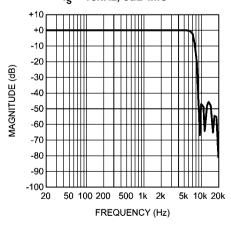

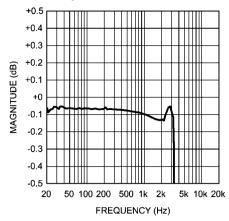

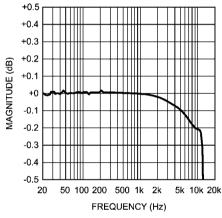

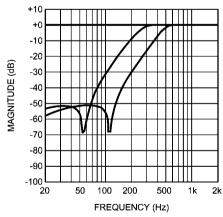

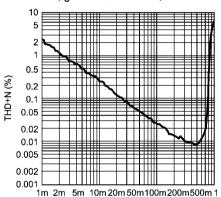

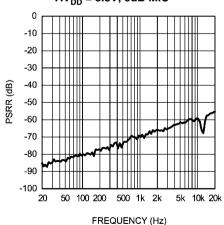

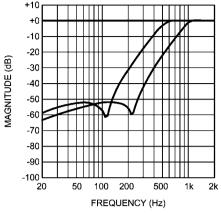

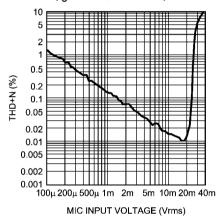

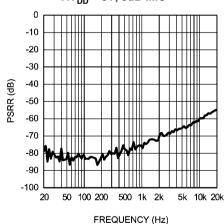

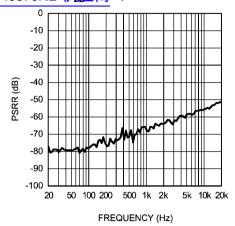

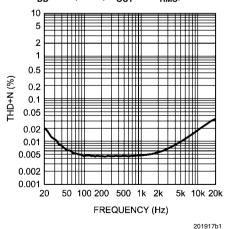

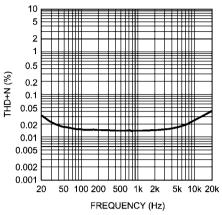

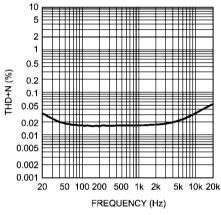

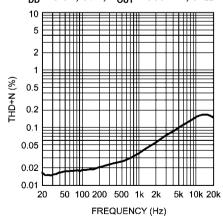

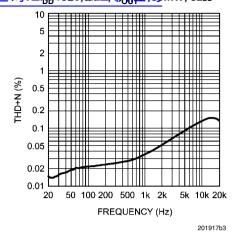

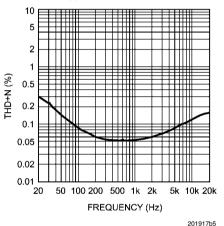

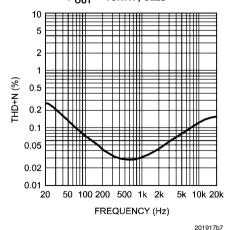

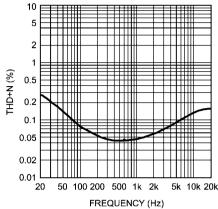

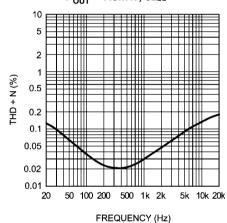

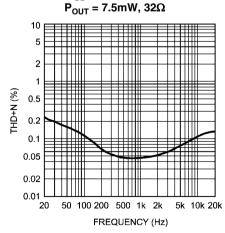

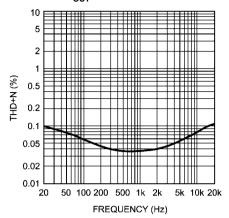

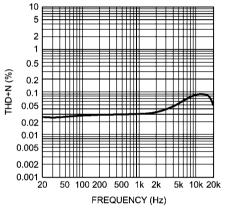

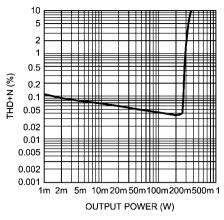

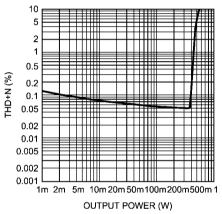

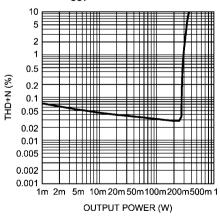

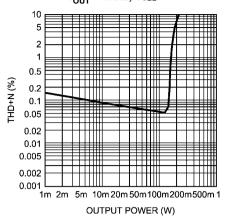

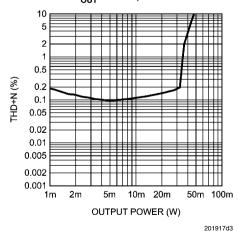

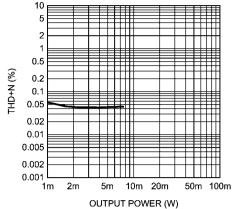

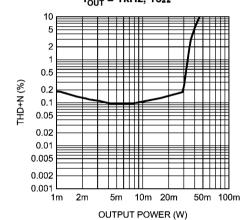

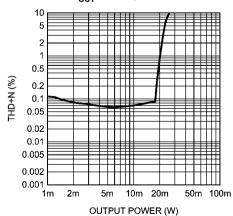

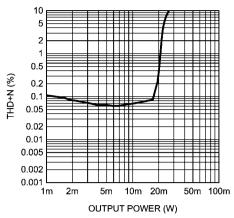

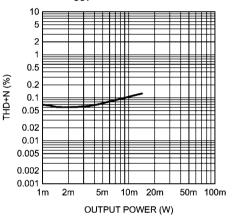

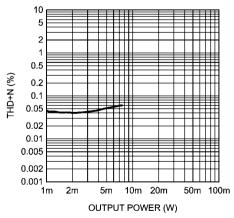

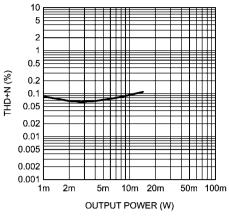

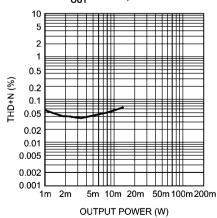

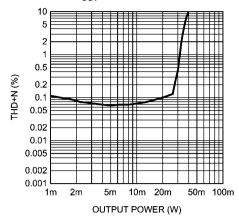

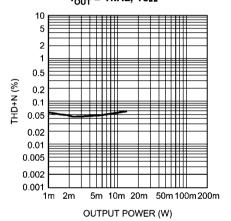

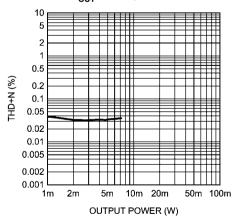

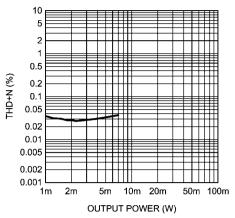

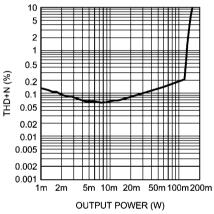

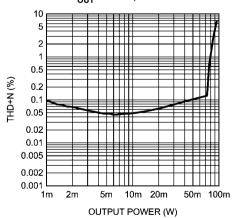

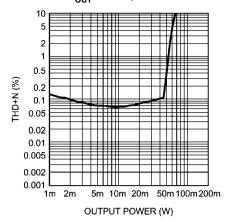

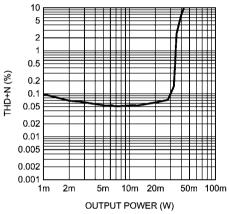

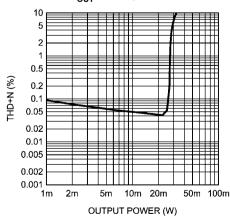

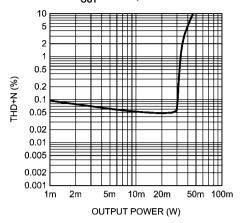

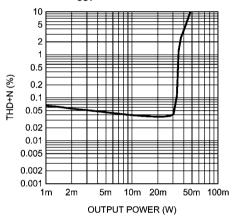

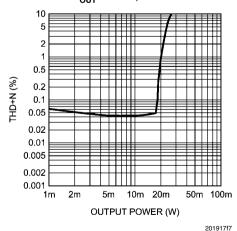

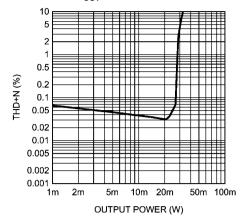

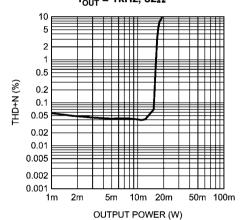

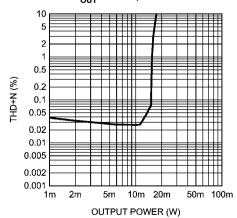

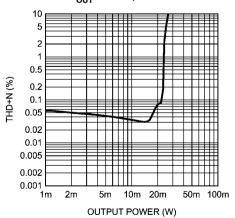

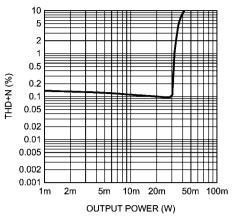

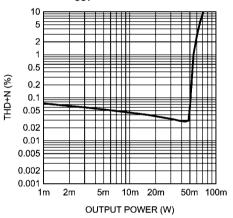

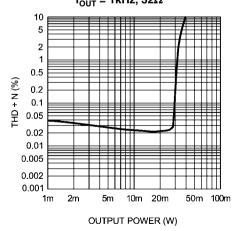

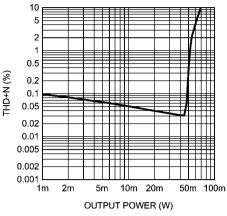

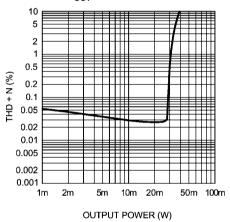

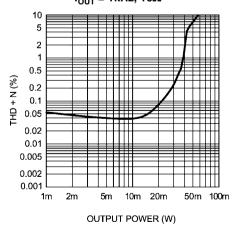

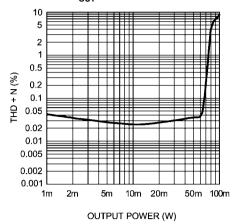

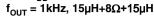

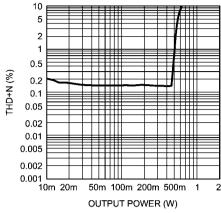

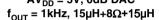

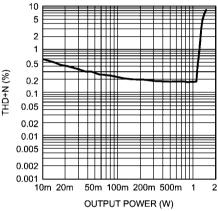

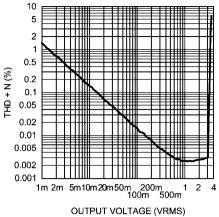

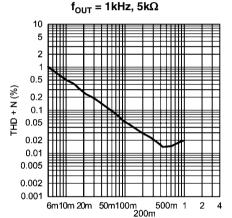

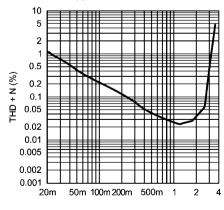

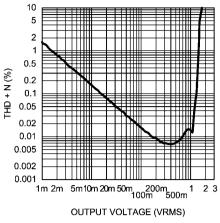

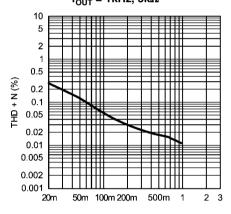

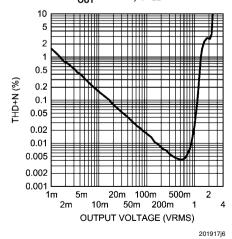

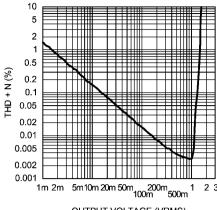

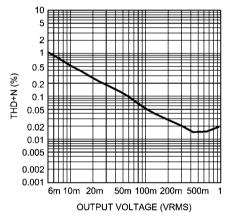

| 13.0 Typical Performance Characteristics                                                                                                                 |      |

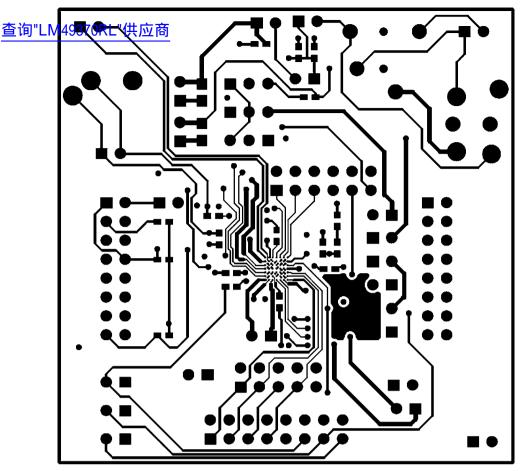

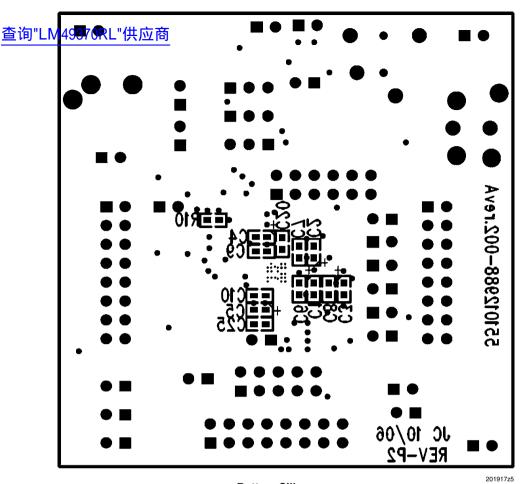

| 14.0 LM49370 Demonstration Board Schematic Diagram                                                                                                       | 91   |

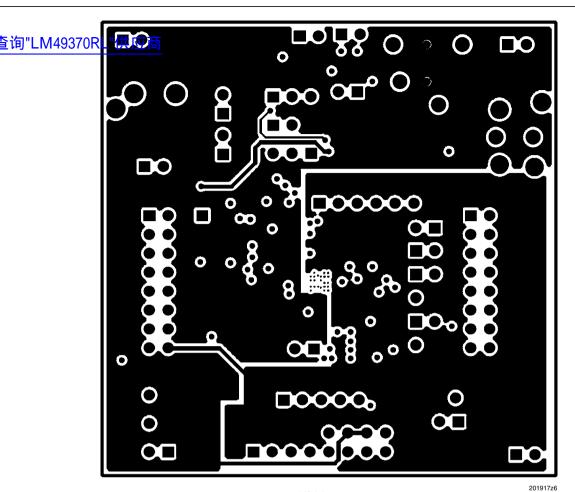

| 15.0 Demoboard PCB Layout                                                                                                                                |      |

| 16.0 Revision History                                                                                                                                    |      |

| 17.0 Physical Dimensions                                                                                                                                 |      |

|                                                                                                                                                          | . 55 |

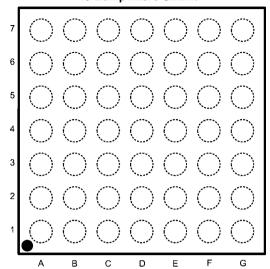

# 7.0 Connection Diagrams 查询"LM49370RL"供应商

49 Bump micro SMDxt

Top View (Bump Side Down) Order Number LM49370RL See NS Package Number RLA49UUA

# 49 Bump micro SMDxt Marking

Top View

XY — Date Code

TT — Die Traceability

G — Boomer

I3 — LM49370RL

# 查**局in/Apscriptipns**商

|     | J LIVI455701VL [六沙古] |         |           |                                                                                  |  |

|-----|----------------------|---------|-----------|----------------------------------------------------------------------------------|--|

| Pin | Pin Name             | Туре    | Direction | Description                                                                      |  |

| A1  | EP_NEG               | Analog  | Output    | Earpiece negative output                                                         |  |

| A2  | $A_V_{DD}$           | Supply  | Input     | Headphone and mixer V <sub>DD</sub>                                              |  |

| A3  | INT_MIC_POS          | Analog  | Input     | Internal microphone positive input                                               |  |

| _A4 | PCM_SDO              | Digital | Output    | PCM Serial Data Output                                                           |  |

| _A5 | PCM_CLK              | Digital | Inout     | PCM clock signal                                                                 |  |

| _A6 | PCM_SYNC             | Digital | Inout     | PCM sync signal                                                                  |  |

| _A7 | PCM_SDI              | Digital | Input     | PCM Serial Data Input                                                            |  |

| B1  | A_V <sub>SS</sub>    | Supply  | Input     | Headphone and mixer ground                                                       |  |

| B2  | EP_POS               | Analog  | Output    | Earpiece positive output                                                         |  |

| B3  | INT_MIC_NEG          | Analog  | Input     | Internal microphone negative input                                               |  |

| B4  | BYPASS               | Analog  | Input     | A_V <sub>DD</sub> /2 filter point                                                |  |

| B5  | TEST_MODE/CS         | Digital | Input     | If $SPI\_MODE = 1$ , then this pin becomes $\overline{CS}$ .                     |  |

| B6  | PLL_FILT             | Analog  | Input     | Filter point for PLL VCO input                                                   |  |

| B7  | PLL_V <sub>DD</sub>  | Supply  | Input     | PLL V <sub>DD</sub>                                                              |  |

| C1  | HP_R                 | Analog  | Output    | Headphone Right Output                                                           |  |

| C2  | EXT_BIAS             | Analog  | Output    | External microphone supply (2.0/2.5/2.8/3.3V)                                    |  |

| C3  | INT_BIAS             | Analog  | Output    | Internal microphone supply (2.0/2.5/2.8/3.3V)                                    |  |

| C4  | AUX_R                | Analog  | Input     | Right Analog Input                                                               |  |

| C5  | GPIO_2               | Digital | Inout     | General Purpose I/O 2                                                            |  |

| C6  | SDA                  | Digital | Inout     | Control Data, I2C_SDA or SPI_SDA                                                 |  |

| C7  | SCL                  | Digital | Input     | Control Clock, I2C_SCL or SPI_SCL                                                |  |

| D1  | HP_L                 | Analog  | Output    | Headphone Left Output                                                            |  |

| D2  | VREF_FLT             | Analog  | Inout     | Filter point for the microphone power supply                                     |  |

| D3  | EXT_MIC              | Analog  | Input     |                                                                                  |  |

| D4  | SPI_MODE             | Digital | Input     | Control mode select 1 = SPI, 0 = I2C                                             |  |

| D5  | GPIO_1               | Digital | Inout     | General Purpose I/O 1                                                            |  |

| D6  | BB_V <sub>DD</sub>   | Supply  | Input     | Baseband V <sub>DD</sub> for the digital I/Os                                    |  |

| D7  |                      | Supply  |           | Digital V <sub>DD</sub>                                                          |  |

|     | D_V <sub>DD</sub>    |         | Input     |                                                                                  |  |

| E1  | HP_VMID              | Analog  | Inout     | Virtual Ground for Headphones in OCL mode, otherwise 1st headset detection input |  |

| E2  | MIC_DET              | Analog  | Input     | Headset insertion/removal and microphone presence detection input.               |  |

| E3  | AUX_L                | Analog  | Input     | Left Analog Input                                                                |  |

| E4  | CPI_NEG              | Analog  | Input     | Cell Phone analog input negative                                                 |  |

| E5  | IRQ                  | Digital | Output    | Interrupt request signal (NOT open drain)                                        |  |

| E6  | I2S_SDO              | Digital | Output    | I2S Serial Data Out                                                              |  |

| E7  | I2S_SDI              | Digital | Input     | I2S Serial Data Input                                                            |  |

| _F1 | HP_VMID_FB           | Analog  | Input     | VMID Feedback in OCL mode, otherwise a 2nd headset detection input               |  |

| F2  | LS_V <sub>DD</sub>   | Supply  | Input     | Loudspeaker V <sub>DD</sub>                                                      |  |

| _F3 | CPI_POS              | Analog  | Input     | Cell Phone analog input positive                                                 |  |

| F4  | CPO_NEG              | Analog  | Output    | Cell Phone analog output negative                                                |  |

| F5  | AUX_OUT_NEG          | Analog  | Output    | Auxiliary analog output negative                                                 |  |

| F6  | I2S_WS               | Digital | Inout     | I2S Word Select Signal (can be master or slave)                                  |  |

| F7  | I2S_CLK              | Digital | Inout     | I2S Clock Signal (can be master or slave)                                        |  |

| G1  | LS_NEG               | Analog  | Output    | Loudspeaker negative output                                                      |  |

| G2  | $LS_V_{SS}$          | Supply  | Input     | Loudspeaker ground                                                               |  |

| G3  | LS_POS               | Analog  | Output    | Loudspeaker positive output                                                      |  |

| G4  | CPO_POS              | Analog  | Output    | Cell Phone analog output positive                                                |  |

| G5  | AUX_OUT_POS          | Analog  | Output    | Auxiliary analog output positive                                                 |  |

|     |                      |         |           |                                                                                  |  |

| Pin | Pin Name | Туре    | Direction | Description                        |

|-----|----------|---------|-----------|------------------------------------|

| G6  | 查询"LM49  | 33/MBIA | 供麻商       | Digital ground                     |

| G7  | MCLK     | Digital | Input     | Input clock from 0.5 MHz to 30 MHz |

#### 7.1 PIN TYPE DEFINITIONS

Analog Inout—

Analog Input— A pin that is used by the analog and is never driven by the device. Supplies are

part of this classification.

Analog Output— A pin that is driven by the device and

should not be driven by external sources.

A pin that is typically used for filtering a DC signal within the device, Passive components can be connected to these pins.

Digital Input— A pin that is used by the digital but is nev-

er driven.

Digital Output— A pin that is driven by the device and should not be driven by another device to

avoid contention.

Digital Inout— A pin that is either open drain (I2C\_SDA)

or a bidirectional CMOS in/out. In the later case the direction is selected by a control

register within the LM49370.

# 8.0 Absolute Maximum Ratings (Notes ၍"LM49370RL"供应商

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Analog Supply Voltage  $(A_V_{DD} \& LS_V_{DD})$

Digital Supply Voltage

$(BB_V_{DD} \& D_V_{DD} \& PLL_V_{DD})$

Storage Temperature -65°C to +150°C Power Dissipation (Note 3) Internally Limited

**ESD Susceptibility**

Human Body Model (Note 4) 2500V Machine Model (Note 5) 200V Junction Temperature 150°C

Thermal Resistance

$\theta_{JA}$  - RLA49 (soldered down to PCB with 2in<sup>2</sup> 1oz. copper plane)

60°C/W Soldering Information

9.0 Operating Ratings

Temperature Range -40°C to +85°C

Supply Voltage

$\mathsf{D}_{-}\mathsf{V}_{\mathsf{DD}}\!/\mathsf{PLL}_{-}\mathsf{V}_{\mathsf{DD}}$ 2.5V to 4.5V BB\_V<sub>DD</sub> 1.8V to 4.5V  $\mathsf{LS}\_\mathsf{V}_\mathsf{DD}/\mathsf{A}\_\mathsf{V}_\mathsf{DD}$ 2.5V to 5.5V

10.0 Electrical Characteristics (Notes 1, 2) Unless otherwise stated PLL\_ $V_{DD}$  = 3.3V,  $D_{L}V_{DD}$  = 3.3V,  $BB_V_{DD} = 1.8V$ ,  $A_V_{DD} = 3.3V$ ,  $LS_V_{DD} = 3.3V$ . The following specifications apply for the circuit shown in *Figure 2* unless otherwise stated. Limits apply for 25°C.

6.0V

6.0V

|                  |                                                |                                                                                            | LM49370             |                           |          |

|------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------|---------------------------|----------|

| Symbol           | Parameter                                      | Conditions                                                                                 | Typical<br>(Note 6) | Limit<br>(Notes 7,<br>11) | Units    |

| POWER            |                                                |                                                                                            |                     |                           |          |

| DI <sub>SD</sub> | Digital Shutdown Current                       | Chip Mode '00', f <sub>MCLK</sub> = 13MHz                                                  | 0.7                 | 2.2                       | μA (max) |

| DI <sub>ST</sub> | Digital Standby Current                        | Chip Mode '01', f <sub>MCLK</sub> = 13MHz                                                  | 0.9                 | 1.8                       | mA(max)  |

| Al <sub>SD</sub> | Analog Shutdown Current                        | Chip Mode '00'                                                                             | 0.1                 | 1.2                       | μA(max)  |

| Al <sub>ST</sub> | Analog Standby Current                         | Chip Mode '01'                                                                             | 0.1                 | 1.2                       | μA (max) |

|                  | Digital Playback Mode Digital                  | Chip Mode '10', $f_{MCLK} = 12MHz$ , $f_S = 48kHz$ , DAC on; PLL off                       | 7.9                 |                           | mA       |

|                  | Active Current                                 | Chip Mode '10', $f_{MCLK} = 13MHz$ , $f_{PLLOUT} = 12MHz$ , $f_{S} = 48kHz$ ; DAC + PLL on | 12.5                | 14.5                      | mA(max)  |

|                  |                                                | Chip Mode '10', HP On, SE mode, DAC inputs selected                                        | 9.0                 | 13.5                      | mA(max)  |

|                  | Digital Playback Mode Analog Active Current    | Chip Mode '10', HP On, OCL mode, DAC inputs selected                                       | 9.4                 | 13.5                      | mA(max)  |

|                  |                                                | Chip Mode '10', LS On,<br>DAC inputs selected                                              | 11.5                | 15.5                      | mA(max)  |

|                  | Analog Playback Mode Digital Active<br>Current | Chip Mode '10', f <sub>MCLK</sub> = 13MHz,<br>DAC +ADC + PLL off                           | 0.9                 | 1.8                       | mA(max)  |

|                  |                                                | Chip Mode '10', HP On, SE mode,<br>AUX inputs selected                                     | 5.9                 | 9.5                       | mA(max)  |

|                  | Analog Playback Mode Analog Active Current     | Chip Mode '10', HP On, OCL mode,<br>AUX inputs selected                                    | 6.3                 | 9.7                       | mA(max)  |

|                  |                                                | Chip Mode '10', LS On,<br>AUX inputs selected                                              | 8.4                 | 12                        | mA(max)  |

|                  | CODEC Mode Digital Active Current              | Chip Mode '10', f <sub>MCLK</sub> = 13MHz, f <sub>S</sub> = 8kHz,<br>DAC +ADC on; PLL Off  | 2.7                 | 3.5                       | mA(max)  |

|                  | CODEC Mode Analog Active Current               | Chip Mode '10', EP On,<br>DAC inputs selected                                              | 11.2                | 15.5                      | mA(max)  |

|                  | Voice Module Mode Digital Active<br>Current    | Chip Mode '10', f <sub>MCLK</sub> = 13MHz,<br>DAC +ADC + PLL off                           | 0.9                 | 1.8                       | mA(max)  |

|                  | Voice Module Mode Analog Active<br>Current     | Chip Mode '10', EP + CPOUT on,<br>CPIN input selected                                      | 7.4                 | 11                        | mA(max)  |

| 木と                    | <br>                                        |                                                                                                                  | LM49                | 9370                      |                              |

|-----------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|------------------------------|

| Symb <del>ol [P</del> | "LM49370RL"供应商<br>Parameter                 | Conditions                                                                                                       | Typical<br>(Note 6) | Limit<br>(Notes 7,<br>11) | Units                        |

| LOUDSPEAK             | ER AMPLIFIER                                |                                                                                                                  |                     |                           |                              |

|                       |                                             | 8Ω load, LS_ $V_{DD} = 5V$                                                                                       | 1.2                 |                           | W                            |

| LS                    | Max Loudspeaker Power                       | $8\Omega$ load, LS_V <sub>DD</sub> = 4.2V                                                                        | 0.9                 |                           | W                            |

|                       |                                             | $8\Omega$ load, LS_V <sub>DD</sub> = 3.3V                                                                        | 0.5                 | 0.43                      | W (min                       |

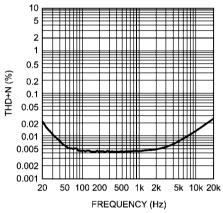

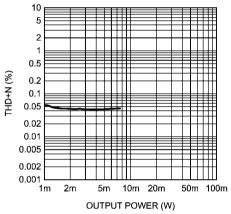

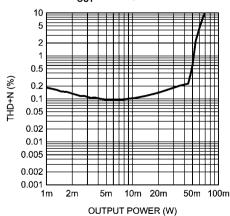

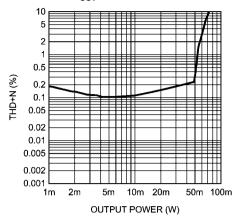

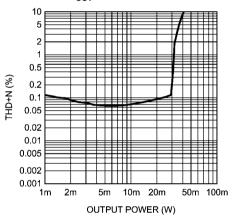

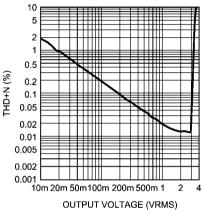

| LS <sub>THD+N</sub>   | Loudspeaker Harmonic Distortion             | $8\Omega$ load, LS_V <sub>DD</sub> = 3.3V,<br>P <sub>O</sub> = 400mW                                             | 0.04                |                           | %                            |

| _S <sub>EFF</sub>     | Efficiency                                  | 0 dB Input<br>MCLK = 12.000 MHz                                                                                  | 84                  |                           | %                            |

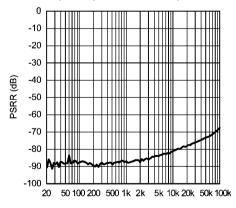

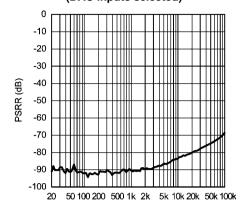

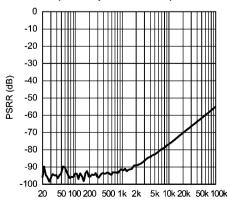

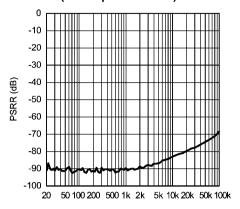

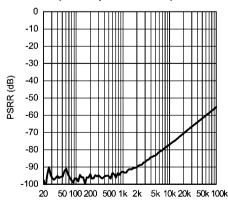

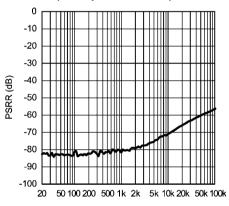

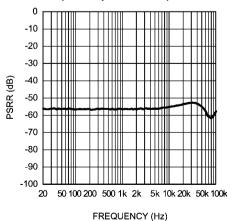

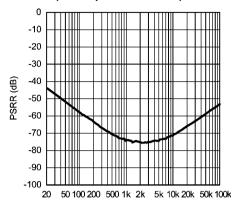

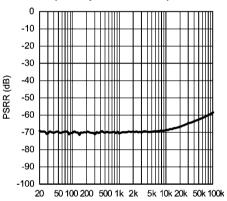

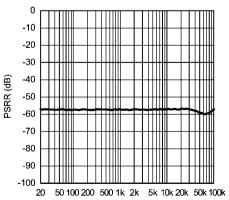

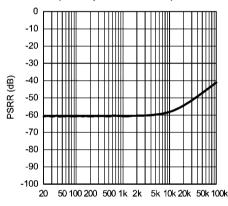

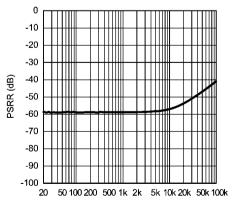

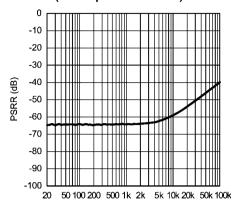

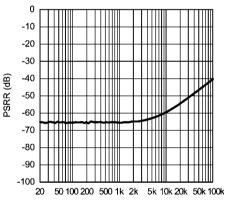

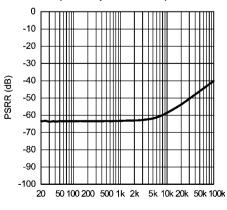

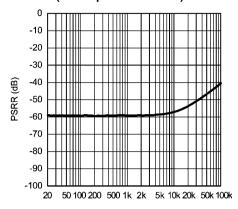

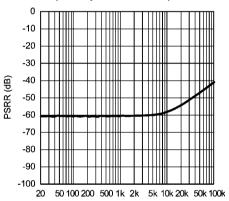

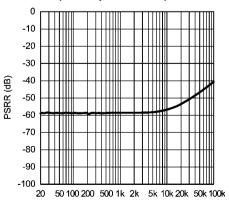

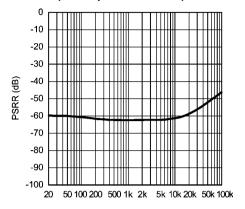

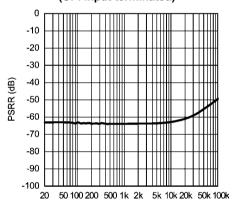

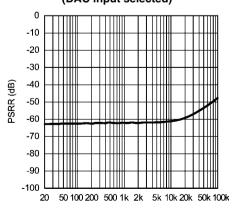

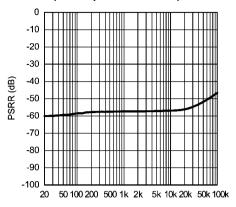

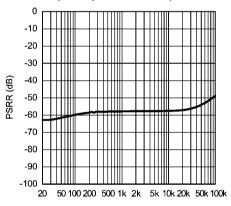

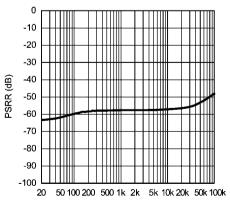

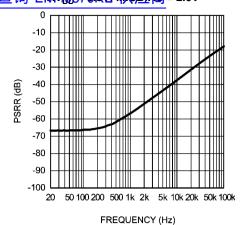

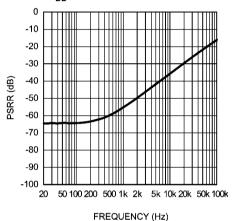

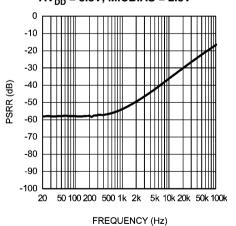

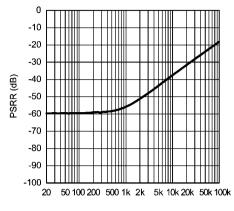

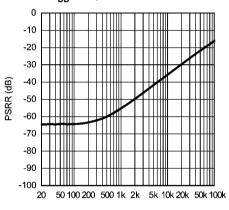

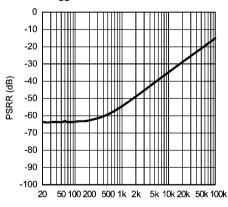

| PSRR <sub>LS</sub>    | Power Supply Rejection Ration (Loudspeaker) | AUX inputs terminated $C_{BYPASS} = 1.0 \ \mu F$ $V_{RIPPLE} = 200 \ mV_{P-P}$ $f_{RIPPLE} = 217 \ Hz$           | 70                  |                           | dB                           |

| SNR <sub>LS</sub>     | Signal to Noise Ratio                       | From 0 dB Analog AUX input, A-weighted                                                                           | 90                  | 80                        | dB(min                       |

| e <sub>N</sub>        | Output Noise                                | A-weighted                                                                                                       | 62                  |                           | μV                           |

| V <sub>os</sub>       | Loudspeaker Offset Voltage                  |                                                                                                                  | 12                  |                           | mV                           |

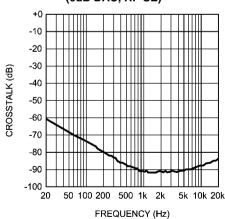

| HEADPHONE             | AMPLIFIER                                   |                                                                                                                  |                     | _!                        |                              |

|                       |                                             | 32Ω load, 3.3V, SE                                                                                               | 33                  | 25                        | mW<br>(min)                  |

|                       |                                             | 16Ω load, 3.3V, SE                                                                                               | 52                  |                           | W W W W (min) mW mW mW mW dB |

| O<br>HP               | Headphone Power                             | 32Ω load, 3.3V, OCL, VCM = 1.5V                                                                                  | 31                  |                           | mW                           |

| 111                   | ·                                           | 32Ω load, 3.3V, OCL, VCM = 1.2V                                                                                  | 20                  |                           | mW                           |

|                       |                                             | 16Ω load, 3.3V, OCL, VCM = 1.5V                                                                                  | 50                  |                           | mW                           |

|                       |                                             | 16Ω load, 3.3V, OCL, VCM = 1.2V                                                                                  | 32                  |                           | mW                           |

|                       |                                             | AUX inputs terminated $C_{BYPASS} = 1.0 \mu F$ $V_{RIPPLE} = 200 \text{ mV}_{P-P}$ $f_{RIPPLE} = 217 \text{ Hz}$ |                     |                           |                              |

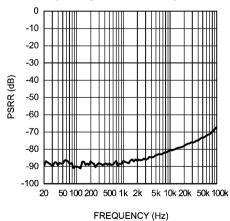

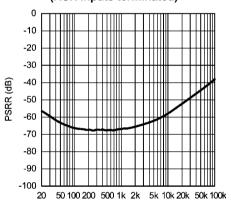

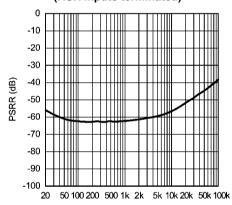

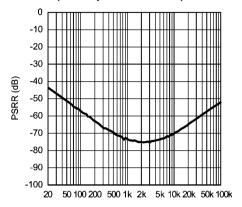

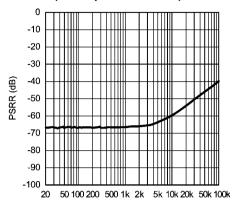

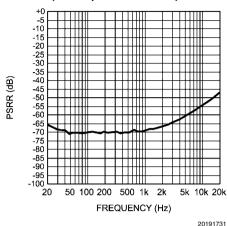

| PSRR <sub>HP</sub>    | Power Supply Rejection Ratio (Headphones)   | SE Mode                                                                                                          | 60                  |                           | dB                           |

|                       | (пеационея)                                 | OCL Mode<br>VCM = 1.2V                                                                                           | 68                  | 55                        | dB(min                       |

|                       |                                             | OCL Mode<br>VCM = 1.5V                                                                                           | 65                  |                           | dB                           |

|                       |                                             | From 0dB Analog AUX input A-weighted                                                                             |                     |                           |                              |

| CNID                  | Circulate Nation D. 15                      | SE Mode                                                                                                          | 98                  | 1                         | dB                           |

| SNR <sub>HP</sub>     | Signal to Noise Ratio                       | OCL Mode<br>VCM = 1.2V                                                                                           | 97                  | <u> </u>                  | dB                           |

|                       |                                             | OCL Mode<br>VCM = 1.5V                                                                                           | 96                  |                           |                              |

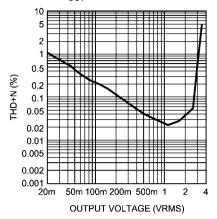

| HP <sub>THD+N</sub>   | Headphone Harmonic Distortion               | $32\Omega$ load, 3.3V, P <sub>O</sub> = 7.5mW                                                                    | 0.05                |                           |                              |

| P <sub>N</sub>        | Output Noise                                | A-weighted                                                                                                       | 12                  |                           | μV                           |

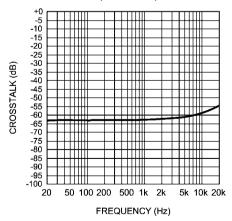

| ∆A <sub>CH-CH</sub>   | Stereo Channel-to-Channel Gain<br>Mismatch  |                                                                                                                  | 0.3                 |                           | dB                           |

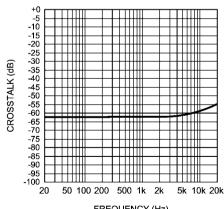

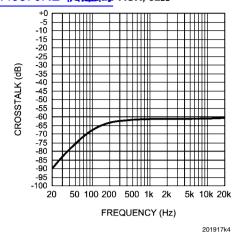

| <b>K</b> TALK         | Stereo Crosstalk                            | SE Mode                                                                                                          | 61                  |                           | dB                           |

|                       |                                             | OCL Mode                                                                                                         | 71                  |                           | dB                           |

| V <sub>os</sub>       | Offset Voltage                              |                                                                                                                  | 8                   |                           | mV                           |

9

|                      |                                         |                                                                                                                         | LM49                    | 370                       |                  |

|----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|------------------|

| ≦询"LM4<br>Symbol     | 9370RL"供应商<br>arameter                  | Conditions                                                                                                              | <b>Typical</b> (Note 6) | Limit<br>(Notes 7,<br>11) | Units            |

| P <sub>EP</sub>      | Earpiece Power                          | 32Ω load, 3.3V                                                                                                          | 115                     | 100                       | mW<br>(min)      |

|                      |                                         | 16Ω load, 3.3V                                                                                                          | 150                     |                           | mW               |

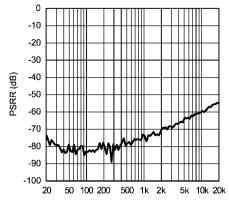

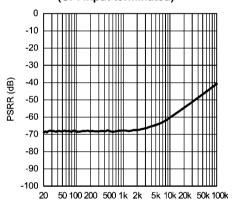

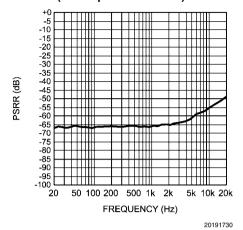

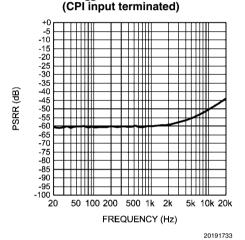

| PSRR <sub>EP</sub>   | Power Supply Rejection Ratio (Earpiece) | CP_IN terminated $C_{BYPASS} = 1.0 \mu F$ $V_{RIPPLE} = 200 \text{ mV}_{P-P}$ $F_{RIPPLE} = 217 \text{ Hz}$             | 76                      |                           | dB               |

| SNR <sub>EP</sub>    | Signal to Noise Ratio                   | From 0dB Analog AUX input, A-weighted                                                                                   | 93                      |                           | dB               |

| EP <sub>THD+N</sub>  | Earpiece Harmonic Distortion            | $32\Omega$ load, 3.3V, $P_O = 50$ mW                                                                                    | 0.04                    |                           | %                |

| e <sub>N</sub>       | Output Noise                            | A-weighted                                                                                                              | 41                      |                           | μV               |

| V <sub>OS</sub>      | Offset Voltage                          |                                                                                                                         | 8                       |                           | mV               |

| AUXOUT AI            |                                         |                                                                                                                         |                         |                           |                  |

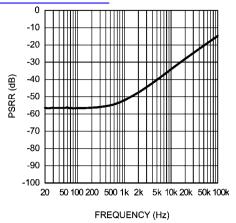

| THD+N                | Total Harmonic Distortion + Noise       | $V_O = 1V_{RMS}$ , $5k\Omega$ load                                                                                      | 0.02                    |                           | %                |

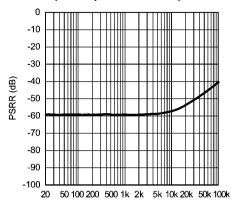

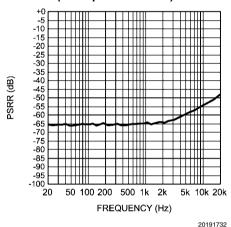

| PSRR                 | Power Supply Rejection Ratio            | $V_0 = V_{RMS}$ , $SISE 1000$ $CP_IN terminated$ $C_{BYPASS} = 1.0 \mu F$ $V_{RIPPLE} = 200 mVPP$ $f_{RIPPLE} = 217 Hz$ | 86                      |                           | dB               |

| CP_OUT AN            | MPLIFIER                                | ,                                                                                                                       |                         |                           |                  |

| THD+N                | Total Harmonic Distortion + Noise       | $V_O = 1V_{RMS}$ , $5k\Omega$ load                                                                                      | 0.02                    |                           | %                |

| PSRR                 | Power Supply Rejection Ratio            | $C_{BYPASS} = 1.0 \mu F$ $V_{RIPPLE} = 200 m V P P$ $f_{RIPPLE} = 217 H z$                                              | 86                      |                           | dB               |

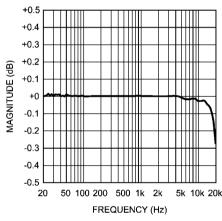

| MONO ADC             | ;                                       |                                                                                                                         |                         |                           |                  |

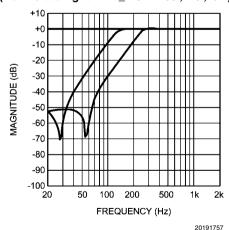

| R <sub>ADC</sub>     | ADC Ripple                              |                                                                                                                         | ±0.25                   |                           | dB               |

| PB <sub>ADC</sub>    | ADC Passband                            | Lower (HPF Mode 1), f <sub>S</sub> = 8 kHz                                                                              | 300                     |                           | Hz               |

| · PADC               |                                         | Upper                                                                                                                   | 3470                    |                           | Hz               |

| SBA <sub>ADC</sub>   | ADC Stopband Attenuation                | Above Passband HPF Notch, 50 Hz/60 Hz (worst case)                                                                      | 60<br>58                |                           | dB<br>dB         |

| SNR <sub>ADC</sub>   | ADC Signal to Noise Ratio               | From CPI, A-weighted                                                                                                    | 90                      |                           | dB               |

| ADC <sub>LEVEL</sub> | ADC Full Scale Input Level              |                                                                                                                         | 1                       |                           | V <sub>RMS</sub> |

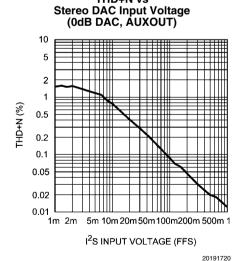

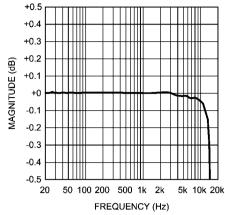

| STEREO DA            |                                         | -                                                                                                                       |                         | ļ                         | i avio           |

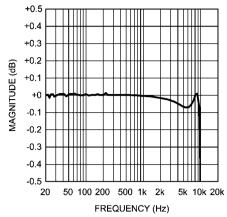

| R <sub>DAC</sub>     | DAC Ripple                              |                                                                                                                         | 0.1                     |                           | dB               |

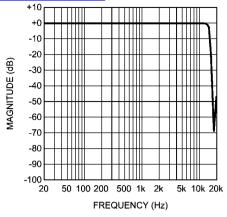

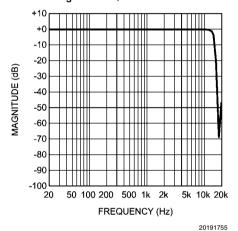

| PB <sub>DAC</sub>    | DAC Passband                            |                                                                                                                         | 20                      |                           | kHz              |

| SBA <sub>DAC</sub>   | DAC Stopband Attenuation                |                                                                                                                         | 70                      |                           | dB               |

| SNR <sub>DAC</sub>   | DAC Signal to Noise Ratio               | A-weighted, AUXOUT                                                                                                      | 85                      |                           | dB               |

| DR <sub>DAC</sub>    | DAC Dynamic Range                       |                                                                                                                         | 96                      |                           | dB               |

| DAC                  | DAC Full Scale Output Level             |                                                                                                                         | 1                       |                           | V <sub>RMS</sub> |

| PLL                  | 1                                       |                                                                                                                         | •                       |                           | - HMS            |

| F <sub>IN</sub>      | Input Frequency Range                   | Min                                                                                                                     |                         | 0.5                       | MHz              |

|                      | ,                                       | Max                                                                                                                     |                         | 30                        | MHz              |

| I2S/PCM              |                                         |                                                                                                                         |                         | 1                         |                  |

|                      |                                         | f <sub>S</sub> = 48kHz; 16 bit mode                                                                                     | 1.536                   |                           | MHz              |

| f <sub>ree</sub>     | I2S CLK Frequency                       | f <sub>S</sub> = 48kHz; 25 bit mode                                                                                     | 2.4                     |                           | MHz              |

| f <sub>I2SCLK</sub>  | 120 OLIVI Tequency                      | f <sub>S</sub> = 8kHz; 16 bit mode                                                                                      | 0.256                   |                           | MHz              |

|                      |                                         | f <sub>S</sub> = 8kHz; 25 bit mode                                                                                      | 0.4                     |                           | MHz              |

| 木丛                       | <br>                          |                                           | LM49                | LM49370                   | <u> </u> |

|--------------------------|-------------------------------|-------------------------------------------|---------------------|---------------------------|----------|

| Symb <del>ol II</del>    | D"LM49370RL"供应商<br>Parameter  | Conditions                                | Typical<br>(Note 6) | Limit<br>(Notes 7,<br>11) | Units    |

|                          |                               | f <sub>S</sub> = 48kHz; 16 bit mode       | 0.768               |                           | MHz      |

|                          |                               | f <sub>S</sub> = 48kHz; 25 bit mode       | 1.2                 |                           | MHz      |

| f <sub>PCMCLK</sub>      | PCM CLK Frequency             | f <sub>S</sub> = 8kHz; 16 bit mode        | 0.128               |                           | MHz      |

|                          |                               | f <sub>S</sub> = 8kHz; 25 bit mode        | 0.2                 |                           | MHz      |

|                          |                               | Min                                       |                     | 40                        | % (min)  |

| DC <sub>I2S_CLK</sub>    | I2S_CLK Duty Cycle            | Max                                       |                     | 60                        | % (max)  |

| DC <sub>I2S_WS</sub>     | I2S_WS Duty Cycle             |                                           | 50                  |                           | %        |

| I2C                      |                               |                                           |                     | -\                        |          |

| T <sub>I2CSET</sub>      | I2C Data Setup Time           | Refer to Pg. 16 for more details          |                     | 100                       | ns (min  |

| T <sub>I2CHOLD</sub>     | I2C Data Hold Time            | Refer to Pg. 16 for more details          |                     | 300                       | ns (min  |

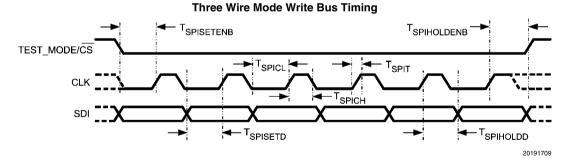

| SPI                      |                               | 1                                         |                     |                           |          |

| T <sub>SPISETENB</sub>   | Enable Setup Time             |                                           |                     | 100                       | ns (min  |

| T <sub>SPIHOLD-ENB</sub> | Enable Hold Time              |                                           |                     | 100                       | ns (min  |

| T <sub>SPISETD</sub>     | Data Setup Time               |                                           |                     | 100                       | ns (min  |

| T <sub>SPIHOLDD</sub>    | Data Hold Time                |                                           |                     | 100                       | ns (min  |

| T <sub>SPICL</sub>       | Clock Low Time                |                                           |                     | 500                       | ns (min  |

| T <sub>SPICH</sub>       | Clock High Time               |                                           |                     | 500                       | ns (min  |

| VOLUME COI               | -                             |                                           |                     | 1 000                     | 1 (      |

|                          |                               | Minimum Gain w/ AUX_BOOST OFF             | -46.5               |                           | dB       |

|                          |                               | Maximum Gain w/ AUX_BOOST OFF             | 0                   |                           | dB       |

| VCR <sub>AUX</sub>       | AUX Volume Control Range      | Minimum Gain w/ AUX_BOOST ON              | -34.5               |                           | dB       |

|                          |                               | Maximum Gain w/ AUX_BOOST ON              | 12                  |                           | dB       |

|                          |                               | Minimum Gain w/ DAC_BOOST OFF             | -46.5               |                           | dB       |

|                          |                               | Maximum Gain w/ DAC_BOOST OFF             | 0                   |                           | dB       |

| VCR <sub>DAC</sub>       | DAC Volume Control Range      | Minimum Gain w/ DAC_BOOST ON              | -34.5               |                           | dB       |

|                          |                               | Maximum Gain w/ DAC_BOOST ON              | 12                  |                           | dB       |

|                          |                               | Minimum Gain                              | -34.5               |                           | dB       |

| VCR <sub>CPIN</sub>      | CPIN Volume Control Range     | Maximum Gain                              | 12                  |                           | dB       |

| VOD                      | 14101/1                       | Minimum Gain                              | 6                   |                           | dB       |

| VCR <sub>MIC</sub>       | MIC Volume Control Range      | Maximum Gain                              | 36                  |                           | dB       |

| VOD                      | OIDETONE VIL. O. I. I.B.      | Minimum Gain                              | -30                 |                           | dB       |

| VCR <sub>SIDE</sub>      | SIDETONE Volume Control Range | Maximum Gain                              | 0                   |                           | dB       |

| SS <sub>AUX</sub>        | AUX VCR Stepsize              |                                           | 1.5                 |                           | dB       |

| SS <sub>DAC</sub>        | DAC VCR Stepsize              |                                           | 1.5                 |                           | dB       |

| SS <sub>CPIN</sub>       | CPIN VCR Stepsize             |                                           | 1.5                 |                           | dB       |

| SS <sub>MIC</sub>        | MIC VCR Stepsize              |                                           | 2                   |                           | dB       |

| SS <sub>SIDE</sub>       | SIDETONE VCR Stepsize         |                                           | 3                   |                           | dB       |

|                          | <u>'</u>                      | _                                         | al and select       | ed onto mi                | xer)     |

|                          |                               | Minimum Gain from AUX input,<br>BOOST OFF | -34.5               |                           | dB       |

|                          | Loudspeaker Audio Path Gain   | Maximum Gain from AUX input,<br>BOOST OFF | 12                  |                           | dB       |

|                          |                               | Minimum Gain from CPI input               | -22.5               |                           | dB       |

|                          |                               | Maximum Gain from CPI input               | 24                  |                           | dB       |

|                   |                              |                                                                                  | LM49                | 370                       |      |

|-------------------|------------------------------|----------------------------------------------------------------------------------|---------------------|---------------------------|------|

| 间"LM493<br>Symbol | 70RL"供应 <b>商</b><br>arameter | Conditions                                                                       | Typical<br>(Note 6) | Limit<br>(Notes 7,<br>11) | Unit |

|                   |                              | Minimum Gain from AUX input,<br>BOOST OFF                                        | -52.5               |                           | dB   |

|                   |                              | Maximum Gain from AUX input,<br>BOOST OFF                                        | -6                  |                           | dB   |

|                   |                              | Minimum Gain from CPI input                                                      | -40.5               |                           | dB   |

|                   | Headphone Audio Path Gain    | Maximum Gain from CPI input                                                      | 6                   |                           | dB   |

|                   |                              | Minimum Gain from MIC input using SIDETONE path w/ VCR <sub>MIC</sub> gain = 6dB | -30                 |                           | dE   |

|                   |                              | Maximum Gain from MIC input using SIDETONE path w/ VCR <sub>MIC</sub> gain = 6dB | 0                   |                           | dE   |

|                   |                              | Minimum Gain from AUX input,<br>BOOST OFF                                        | -40.5               |                           | dE   |

|                   |                              | Maximum Gain from AUX input, BOOST OFF                                           | 6                   |                           | dE   |

|                   |                              | Minimum Gain from CPI input                                                      | -28.5               |                           | dE   |

|                   | Earpiece Audio Path Gain     | Maximum Gain from CPI input                                                      | 18                  |                           | dE   |

|                   |                              | Minimum Gain from MIC input using SIDETONE path w/ VCR <sub>MIC</sub> gain = 6dB | -18                 |                           | dE   |

|                   |                              | Maximum Gain from MIC input using SIDETONE path w/ VCR <sub>MIC</sub> gain = 6dB | 12                  |                           | dE   |

|                   |                              | Minimum Gain from AUX input,<br>BOOST OFF                                        | -46.5               |                           | dE   |

|                   | AUXOUT Audio Path Gain       | Maximum Gain from AUX input, BOOST OFF                                           | 0                   |                           | dE   |

|                   |                              | Minimum Gain from CPI input                                                      | -34.5               |                           | dE   |

|                   |                              | Maximum Gain from CPI input                                                      | 12                  |                           | dE   |

|                   |                              | Minimum Gain from AUX input,<br>BOOST OFF                                        | -46.5               |                           | dE   |

|                   | CPOUT Audio Path Gain        | Maximum Gain from AUX input, BOOST OFF                                           | 0                   |                           | dE   |

|                   |                              | Minimum Gain from MIC input                                                      | 6                   |                           | dE   |

|                   |                              | Maximum Gain from MIC input                                                      | 36                  |                           | dE   |

|                    |                                     |                                                              | LM49                | 370                       |       |

|--------------------|-------------------------------------|--------------------------------------------------------------|---------------------|---------------------------|-------|

| Symb <del>ol</del> | "LM49370RL"供应商<br>Parameter         | Conditions                                                   | Typical<br>(Note 6) | Limit<br>(Notes 7,<br>11) | Units |

| Total DC Powe      | er Dissipation                      |                                                              |                     | -                         |       |

|                    |                                     | DAC (f <sub>S</sub> = 48kHz) and HP ON                       |                     |                           |       |

|                    | Digital Playback Mode Power         | f <sub>MCLK</sub> = 12MHz, PLL OFF                           | 56                  |                           | mW    |

|                    | Dissipation                         | $f_{MCLK} = 13MHz$ , PLL ON $f_{PLLOUT} = 12MHz$             | 71                  |                           | mW    |

|                    | Analog Playback Mode Power          | AUX Inputs selected and HP ON                                |                     |                           |       |

|                    | Dissipation                         | f <sub>MCLK</sub> = 13MHz, PLL OFF                           | 22                  |                           | mW    |

|                    | VOICE CODEC Mode Power              | PCM DAC ( $f_S = 8kHz$ ) + ADC ( $f_S = 8kHz$ )<br>and EP ON |                     |                           |       |

|                    | Dissipation                         | f <sub>MCLK</sub> = 13MHz, PLL OFF                           | 46                  |                           | mW    |

|                    | VOIDEM LL M L B B' : i'             | CP IN selected. EP and CPOUT ON                              |                     |                           |       |

|                    | VOICE Module Mode Power Dissipation | f <sub>MCLK</sub> = 13MHz, PLL OFF                           | 27                  |                           | mW    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits.

Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 2: All voltages are measured with respect to the relevant V<sub>SS</sub> pin unless otherwise specified. All grounds should be coupled as close as possible to the device

Note 3: The maximum power dissipation must be de-rated at elevated temperatures and is dictated by  $TJ_{MAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower.

Note 4: Human body model: 100pF discharged through a  $1.5k\Omega$  resistor.

Note 5: Machine model: 220pF - 240pF discharged through all pins.

Note 6: Typical values are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to Nationals AOQL (Average Outgoing Quality Level).

Note 8: Best operation is achieved by maintaining  $3.0V < A_V_{DD} < 5.0$  and  $3.0V < D_V_{DD} < 3.6V$  and  $A_V_{DD} > D_V_{DD} < 0.00$

Note 9: Digital shutdown current is measured with system clock set for PLL output while the PLL is disabled.

Note 10: Disabling or bypassing the PLL will usually result in an improvement in noise measurements.

Note 11: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

# 11.0 System Control

Method 1. I2C Compatible Interface

#### 11.1 I2C SIGNALS

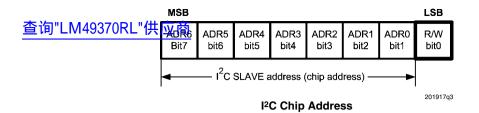

In I<sup>2</sup>C mode the LM49370 pin SCL is used for the I<sup>2</sup>C clock SCL and the pin SDA is used for the I<sup>2</sup>C data signal SDA. Both these signals need a pull-up resistor according to I<sup>2</sup>C specification. The I<sup>2</sup>C slave address for LM49370 is  $0011010_2$ .

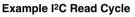

#### 11.2 I2C DATA VALIDITY

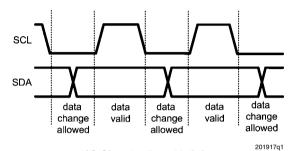

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

I2C Signals: Data Validity

#### 11.3 I2C START AND STOP CONDITIONS

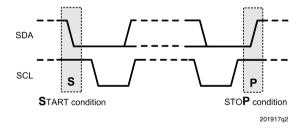

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

### 11.4 TRANSFERRING DATA

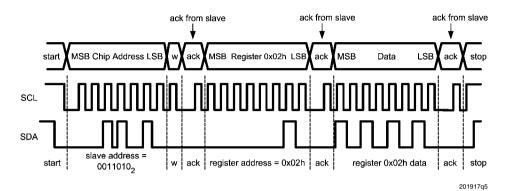

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eight bit which is a data direction bit (R/W). The LM49370 address is **0011010<sub>2</sub>**. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Register changes take an effect at the SCL rising edge during the last ACK from slave.

w = write (SDA = "0") r = read (SDA = "1") ack = acknowledge (SDA pulled down by slave) rs = repeated start

Example I2C Write Cycle

宣训 READ function is to be accomplished, a WRITE function must precede the READ function, as shown in the Read Cycle

I<sup>2</sup>C Timing Diagram

#### 11.5 I2C TIMING PARAMETERS

| Symbol         | Parameter                                                       | Lir                  | nit | Units |

|----------------|-----------------------------------------------------------------|----------------------|-----|-------|

|                |                                                                 | Min                  | Max |       |

| 1              | Hold Time (repeated) START Condition                            | 0.6                  |     | μs    |

| 2              | Clock Low Time                                                  | 1.3                  |     | μs    |

| 3              | Clock High Time                                                 | 600                  |     | ns    |

| 4              | Setup Time for a Repeated START Condition                       | 600                  |     | ns    |

| 5              | Data Hold Time (Output direction, delay generated by LM49370)   | 300                  | 900 | ns    |

| 5              | Data Hold Time (Input direction, delay generated by the Master) | 0                    | 900 | ns    |

| 6              | Data Setup Time                                                 | 100                  |     | ns    |

| 7              | Rise Time of SDA and SCL                                        | 20+0.1C <sub>b</sub> | 300 | ns    |

| 8              | Fall Time of SDA and SCL                                        | 15+0.1C <sub>b</sub> | 300 | ns    |

| 9              | Set-up Time for STOP condition                                  | 600                  |     | ns    |

| 10             | Bus Free Time between a STOP and a START Condition              | 1.3                  |     | μs    |

| C <sub>b</sub> | Capacitive Load for Each Bus Line                               | 10                   | 200 | pF    |

NOTE: Data guaranteed by design

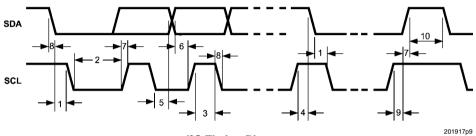

#### Method 2. SPI/Microwire Control/3-wire Control

The LMS 10 LM 4937 MP WITCH The wire interface consisting of a clock, data and an active low chip\_select. To use this control method connect SPI\_MODE to BB\_V\_DD and use TEST\_MODE/CS as the chip\_select as follows:

FIGURE 3. SPI Write Transaction

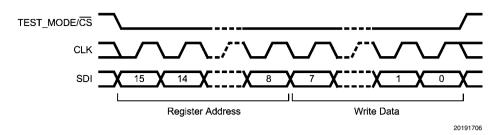

If the application requires read access to the register set; for example to determine the cause of an interrupt request, the GPIO2 pin can be configured as an SPI format serial data output by setting the GPIO\_SEL in the GPIO configuration register (0x1Ah) to SPI\_SDO. To perform a read rather than a write to a particular address the MSB of the register address field is set to a 1, this effectively mirrors the contents of the register field to read-only locations above 0x80h:

FIGURE 4. SPI Read Transaction

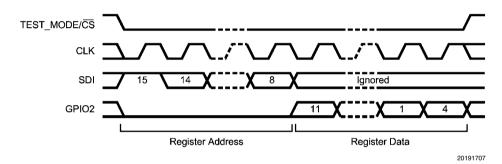

**FIGURE 5. SPI Timing**

# 12.0 Status & Control Registers 查询"LM49370RL"供应商

# TABLE 1. Register Map

(The default value of all I2C registers is 0x00h)

| Addre     | Register  | 7                | 6                    | 5                | 4                | 3                            | 2          | 1         | 0              |

|-----------|-----------|------------------|----------------------|------------------|------------------|------------------------------|------------|-----------|----------------|

| SS        | DACIO     | D.4.0            | MODE                 | 045              | CIZE             | 000 515                      | חון באים   | 0110      | 1000           |

| 0x00h     | BASIC     | DAC_             | MODE                 |                  | _SIZE            | OSC_ENB   PLL_ENB   CHP_MODE |            |           |                |

|           | CLOCKS    |                  | 1                    | R_C              | DIV              |                              |            | DAC_CI    | K_SEL          |

|           | PLL_M     | FORCERQ          |                      |                  |                  | PLL_M                        |            |           |                |

|           | PLL_N     |                  | Г                    |                  | PLL <sub>.</sub> | _N                           |            |           |                |

|           | PLL_P     | VCOFATS          |                      | Q_DIV            |                  |                              | PLI        |           |                |

|           | PLL_MOD   | PLLTEST          | PLL_CL               |                  |                  |                              | PLL_N_MOD  |           |                |

|           | ADC_1     |                  | MODE                 |                  | E_RATE           | RIGHT                        | LEFT       | CPI       | MIC            |

| 0x07h     | ADC_2     | NGZXDD           | ADC_CL               | K_SEL            |                  | PEAKTIME                     |            | ADCMUTE   | ADC_MO<br>E    |

| 0x08h     | AGC_1     | NOISE.           | GATE_THRES           | SHOLD            | NG_ENB           | ,                            | AGC_TARGE  | Т         | AGC_EN         |

| 0x09h     | AGC_2     | AGC_TIGH<br>T    | A                    | AGC_DECAY        |                  |                              | AGC_MA     | AX_GAIN   |                |

| 0x0Ah     | AGC_3     |                  | AGC_ATTACK           |                  |                  | AG                           | C_HOLD_TII | ME        |                |

| 0x0Bh     | MIC_1     |                  | INT_EXT              | SE_DIFF          | MUTE             |                              | PREAM      | P_GAIN    |                |

| 0x0Ch     | MIC_2     |                  |                      | BTN_DEBO         | UNCE_TIME        | BTNTYPE                      | MIC_BIAS   | _VOLTAGE  | VCMVOL         |

| 0x0Dh     | SIDETONE  |                  |                      |                  |                  |                              | SIDETON    | E_ATTEN   |                |

| 0x0Eh     | CP_INPUT  |                  |                      | MUTE             |                  |                              | CPI_LEVEL  |           |                |

|           | AUX_LEFT  |                  |                      |                  |                  | AU                           | X_LEFT_LEV | /EL       |                |

|           | AUX_RIGHT | AUX_DAC          | MUTE                 | BOOST            |                  | AUX_RIGHT_LEVEL              |            |           |                |

|           | DAC       | USAXLVL          | DACMUTE              | BOOST            |                  |                              | DAC_LEVEL  |           |                |

|           | CP_OUTPUT |                  |                      |                  | MICGATE          | MUTE                         | LEFT       | RIGHT     | МІС            |

| 0x13h     |           |                  |                      |                  |                  | MUTE                         | LEFT       | RIGHT     | CPI            |

| 0,7,10,11 | OUTPUT    |                  |                      |                  |                  |                              |            | 1         | 0              |

| 0x14h     | LS_OUTPUT |                  |                      |                  |                  | MUTE                         | LEFT       | RIGHT     | CPI            |

|           | HP_OUTPUT |                  | OCL                  | STEREO           | MUTE             | LEFT                         | RIGHT      | CPI       | SIDE           |

|           | EP_OUTPUT |                  |                      | 0121120          | MUTE             | LEFT                         | RIGHT      | CPI       | SIDE           |

|           | DETECT    |                  |                      | L<br>HS_DBN      | L                |                              | TEMP_INT   | BTN_INT   | DET_INT        |

|           | STATUS    |                  | GPIN1                | GPIN2            | TEMP             | BTN                          | MIC        | STEREO    | HEADSE         |

| 0x19h     | +         | CUST_COM<br>P    | ATTENUATE            |                  | EQ               | LE\                          |            | MODE      | 3DENB          |

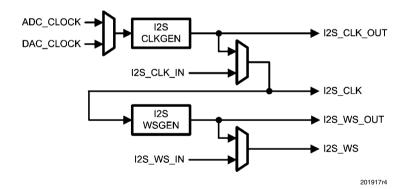

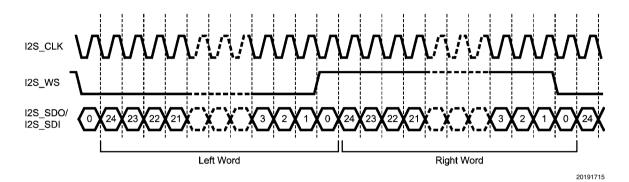

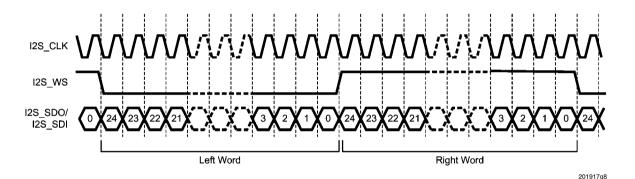

| 0x1Ah     | I2SMODE   | WORD_<br>ORDER   | I2S_WS_GE            | EN_MODE          | WS_MS            | STEREO<br>REVERSE            | I2S_MODE   | INENB     | OUTENB         |

| 0x1Bh     | I2SCLOCK  |                  | ICWIDTH              |                  | I2S_CLOCK        | GEN_MODE                     |            | CLKSCE    | CLK_MS         |

|           | PCMMODE   | ALAW/<br>μLAW    | COMPAND              | SDO_<br>LSB_HZ   | SYNC_MS          | CLKSRCE                      | CLK_MS     | INENB     | OUTENE         |

| 0x1Dh     | PCMCLOCK  | '                | PCM S                | SYNC_GEN_N       | MODE             |                              | PCM CLOCK  | KGEN MODE | !              |

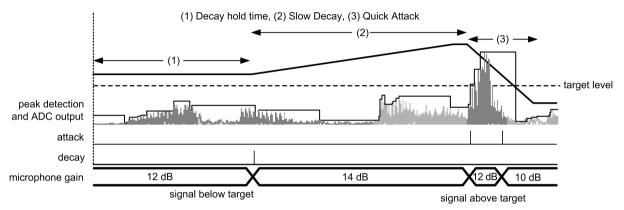

|           | BRIDGE    | MONO_S           | UM_MODE              | MONO_<br>SUM_SEL |                  | X_SEL                        |            | X_SEL     | PCM_<br>TX_SEL |