## **DM115B**

Version : A.001

Issue Date : 2007/02/07

File Name : SP-DM115B-A.001

**Total Pages**

## 8-Bit CONSTANT CURRENT LED DRIVERS with

3.3v ~ 5v supply voltage

新竹市科學園區展業一路9號7樓之1 SILICON TOUCH TECHNOLOGY INC.

9-7F-1, Prosperity Road I, Science Based Industrial Park, Hsin-Chu, Taiwan 300, R.O.C.

Tel: 886-3-5645656 Fax: 886-3-5645626

## **DM115B**

# 8-Bit CONSTANT CURRENT LED DRIVERS with 3.3v ~ 5v Supply Voltage

#### **General Description**

The DM115B is the constant current driver specifically designed for LED display applications. The value of constant current can be varied using an external resistor. The devices include an 8-bit shift register, latches, and constant current drivers on a single Silicon CMOS chip.

#### **Features**

Maximum Output Voltage: 17V

Maximum Clock Frequency: 25MHz (Cascade Operation)

• Power Supply Voltage: 3.3V to 5.0V

CMOS Compatible Input

• Package: PDIP16, SOP16, SSOP16

• Package and Pin Layout: Pin layout and functionality are similar to those of the ST2221A.

(Each characteristic value is different.)

• Constant Current Matching:  $(Ta = 25^{\circ}C \cdot VDD = 5.0V)$

Chip-to-Chip: ± 10.0%

Bit-to-Bit:  $\pm 4.0\%$  @ IouT =  $20 \sim 60$ mA  $\pm 6.0\%$  @ IouT =  $5 \sim 20$ mA

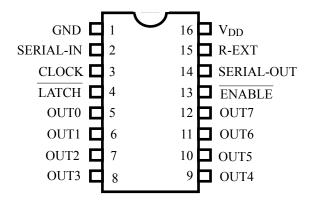

#### Pin Connection (Top view)

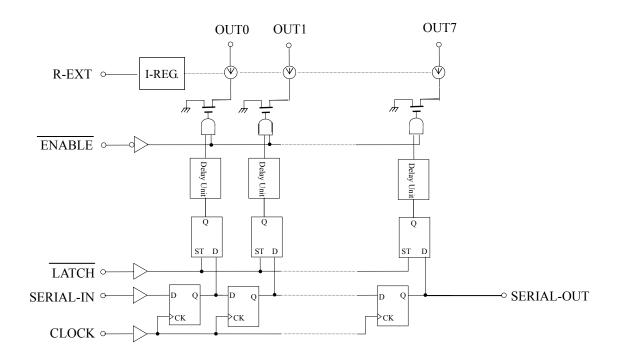

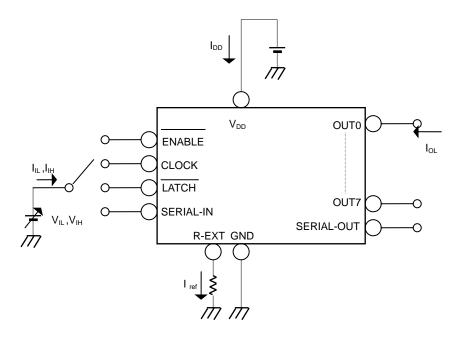

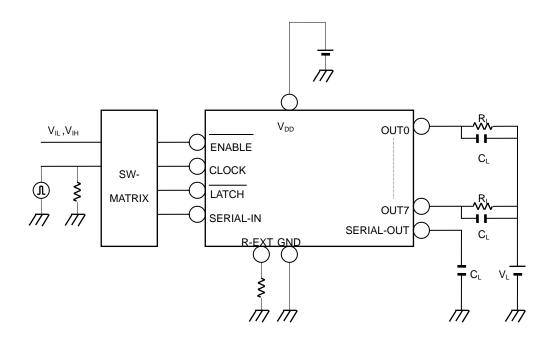

## **Block Diagram**

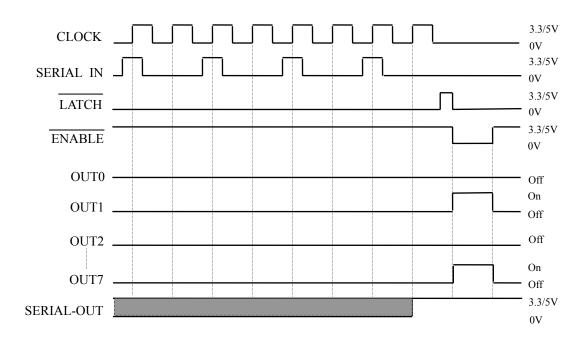

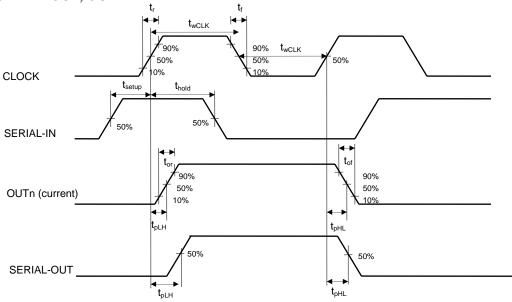

#### **Timing Diagram**

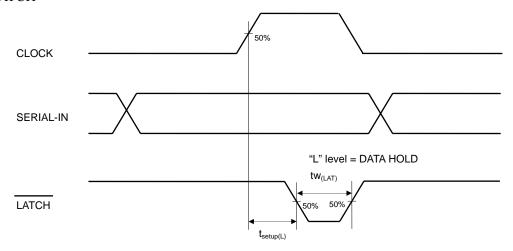

(Note) Latches are level sensitive (not edge triggered).

$\overline{\text{LATCH}}$ -terminal = H level, latches become transparent;  $\overline{\text{LATCH}}$ -terminal = L level, latches hold data.

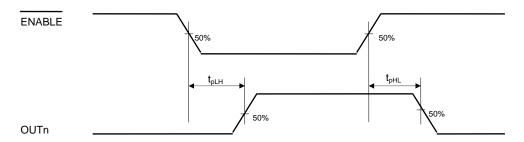

$\overline{\text{ENABLE}}$ -terminal = H level, all outputs (OUT0 $\sim$ 7) are off.

An external resistor is connected between R-EXT and GND for setting up the value of constant current.

SERIAL-OUT changes state on the rising edges of clock.

## **Pin Description**

| PIN No. | PIN NAME   | FUNCTION                                      |

|---------|------------|-----------------------------------------------|

| 1       | GND        | GND terminal                                  |

| 2       | SERIAL-IN  | Input terminal of a data shift register       |

| 3       | CLOCK      | Input terminal of a clock for shift register  |

| 4       | LATCH      | Input terminal for data strobe                |

| 5~12    | OUT0~7     | Output terminals                              |

| 13      | ENABLE     | Input terminal for output enable (active low) |

| 14      | SERIAL-OUT | Output terminal of a data shift register      |

| 15      | R-EXT      | Input terminal of an external resistor        |

| 16      | $V_{DD}$   | 3.3/5V Supply voltage terminal                |

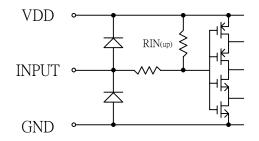

## **Equivalent Circuit of Inputs and Outputs**

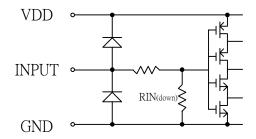

#### 1. ENABLE terminal

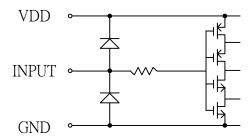

#### 2. LATCH terminal

#### 3. CLOCK, SERIAL-IN terminal

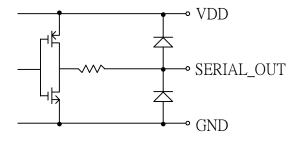

#### 4. SERIAL-OUT terminal

## $\label{eq:maximum Ratings (Ta = 25°C, Tj_{(max)} = 150°C)} \textbf{Maximum Ratings (Ta = 25°C, Tj_{(max)} = 150°C)}$

| CHARACTERISTIC       | SYMBOL   | RATING                                | UNIT        |

|----------------------|----------|---------------------------------------|-------------|

| Supply Voltage       | Vdd      | 0 ~ 7.0                               | V           |

| Input Voltage        | Vin      | $-0.4 \sim VDD + 0.4$                 | V           |

| Output Current       | Iout     | 60                                    | mA          |

| Output Voltage       | Vout     | <b>-</b> 0.3 ∼ 17                     | V           |

| Clock Frequency      | fclk     | 25                                    | MHz         |

| GND Terminal Current | IGND     | 500                                   | mA          |

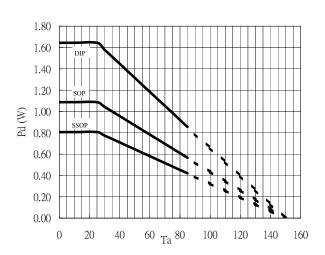

| Power Dissipation    | PD       | 1.64 ( PDIP-16 : Ta=25°C)             |             |

|                      |          | 1.08 ( SOP-16 : Ta=25°C)              | $\exists$ w |

|                      |          | 0.8 ( SSOP-16 : Ta=25°C) single-layer | W           |

|                      |          | 1.47 ( SSOP-16 : Ta=25°C) 4-layer     |             |

| Thermal Resistance   | Rth(j-a) | 76 ( PDIP-16 )                        | °C/W        |

|                      |          | 115 ( SOP-16 )                        |             |

|                      |          | 155 ( SSOP-16 ) single-layer          |             |

|                      |          | 85 (SSOP-16) 4-layer                  |             |

| Storage Temperature  | Tstg     | -55 ∼ 150                             | °C          |

## **Recommended Operating Condition**

| CHARACTERISTIC        | SYMBOL    | CONDITION                         | MIN.   | TYP. | MAX.    | UNIT                   |  |

|-----------------------|-----------|-----------------------------------|--------|------|---------|------------------------|--|

| Supply Voltage        | Vdd       |                                   | 3.0    |      | 5.5     | V                      |  |

| Output Voltage        | Vout      |                                   |        |      | 17      | V                      |  |

| Operating temperature | $T_{OPR}$ |                                   | -40    |      | 85      | $^{\circ}\!\mathbb{C}$ |  |

|                       | Io        | OUTn                              |        |      | 60      |                        |  |

| Output Current        | Іон       | SERIAL-OUT                        |        |      | 1.0     | mA                     |  |

|                       | IOL       | SERIAL-OUT                        |        |      | -1.0    |                        |  |

| Innut Voltago         | Vih       | _                                 | 0.7VDD | _    | VDD+0.3 | - V                    |  |

| Input Voltage         | VIL       | _                                 | -0.3 — |      | 0.3VDD  | V                      |  |

| LATCH Pulse Width     | tw LAT    |                                   | 15     |      |         | ns                     |  |

| CLOCK Pulse Width     | tw CLK    |                                   | 15     |      |         | ns                     |  |

| Set-up Time for DATA  | tsetup(D) | $V_{DD} = 3.0 \sim 5.5 \text{ V}$ | 10     |      |         | ns                     |  |

| Hold Time for DATA    | thold(D)  |                                   | 5      |      |         | ns                     |  |

| Set-up Time for LATCH | tsetup(L) |                                   | 15     |      |         | ns                     |  |

| Clock Frequency       | fCLK      | 2 chips cascade operation         |        |      | 25      | MHz                    |  |

|                       | PD        | $Ta = 85^{\circ}C(PDIP-16)$       |        |      | 0.85    |                        |  |

| Power Dissipation     |           | $Ta = 85^{\circ}C(SOP-16)$        |        |      | 0.56    | W                      |  |

|                       |           | $Ta = 85^{\circ}C(SSOP-16)$       |        |      | 0.41    |                        |  |

## **Electrical Characteristics** (VDD = 5.0 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC                | SYMBOL               | CONDITION                                |                    | MIN.   | TYP. | MAX.       | UNIT  |

|-------------------------------|----------------------|------------------------------------------|--------------------|--------|------|------------|-------|

| Input Voltage "H" Level       | Vih                  | _                                        |                    | 0.7VDD |      | VDD        | V     |

| Input Voltage "L" Level       | VIL                  | _                                        |                    | GND    |      | 0.3VDD     | v     |

| Output Leakage Current        | Іон                  | VOH = 17 V                               | VOH = 17 V         |        |      | 1.0        | uA    |

|                               | Vol                  | IOL = 1.0 mA, VDD=5V                     |                    |        | _    | 0.4        |       |

| Output Voltage (S - OUT)      | Voh                  | IOH = -1.0 mA, VDD=5V                    |                    | 4.6    |      | _          | V     |

|                               | Vol                  | IOL = 1.0 mA, VDD=3.3V                   |                    |        |      | 0.4        |       |

|                               | Voh                  | IOH = -1.0 mA, VDD=3.3V                  |                    | 2.7    |      |            |       |

| Output Current (Bit-Bit)      | $\Delta$ Iout        | VOUT = 1.2V<br>(1 channel on)            | REXT = $780\Omega$ |        | ±1.5 | <u>±</u> 4 | %     |

| Output Current<br>(Chip-Chip) | Iout                 | VOUT = 1.2V<br>(1 channel on)            | REXT = $780\Omega$ | 18.0   | 20.0 | 22.0       | mA    |

| Output Voltage Regulation     | % / Vout             | $Vdd = 3.3V \sim 5.0V$                   |                    |        | 0.1  | 0.5        | % / V |

| Pull-Up Resistor              | RIN(up)              |                                          |                    | 200    | 400  | 600        | ΚΩ    |

| Pull-Down Resistor            | RIN(down)            | _                                        |                    | 100    | 200  | 300        | ΚΩ    |

| Supply Current "OFF"          | Idd (off)            | REXT = OPEN, all outputs off             |                    |        | 5.0  | _          |       |

| Supply Current Off            | VDD=5V               | REXT = $300\Omega$ , OUT0 $\sim$ 7 = off |                    |        | 11.0 | _          | mA    |

| Supply Current "ON"           | Idd (on)<br>VDD=5V   | REXT = $300\Omega$ , OUT0~7 = on         |                    |        | 11.0 |            | IIIA  |

| Complet Compant "OFF"         | Idd (off)            | REXT = OPEN, all outputs off             |                    |        | 1.1  |            |       |

| Supply Current "OFF"          | VDD=3.3V             | REXT = $300\Omega$ , OUT0~7 = off        |                    |        | 7.2  |            | 1 .   |

| Supply Current "ON"           | Idd (on)<br>VDD=3.3V | REXT = $300\Omega$ , OUT0~7 = on         |                    |        | 7.2  |            | mA    |

## Switching Characteristics (Ta = 25 °C unless otherwise noted)

| CHARACTERISTIC           | SYMBOL            | CONDITION                     | MIN. | TYP. | MAX. | UNIT |

|--------------------------|-------------------|-------------------------------|------|------|------|------|

| Propagation ENABLE-OUT0  | 4                 | VDD=5.0V                      |      | 66   | 132  |      |

| Delay Time ("L" to "H")  | tр <sub>L</sub> H | VIH=VDD<br>VIL=GND            |      | 16   | 20   | ns   |

| Propagation ENABLE-OUT0  | 4                 | REXT=630Ω                     | _    | 81   | 162  |      |

| Delay Time ("H" to "L")  | tрнL              | VL=5.0V<br>RL=150Ω<br>CL=15pF |      | 16   | 20   | ns   |

| Output Current Rise Time | tor               |                               |      | 30   | 60   | ns   |

| Output Current Fall Time | tof               |                               | _    | 32   | 50   | ns   |

#### Note: (Delay between outputs)

The DM115B also incorporated the delay unit between outputs. The delay time is 4 ns(typ.), out7 has no delay, out5 has 4 ns delay, out 3 has 8 ns delay, and then out 1, out 0, out 2, out 4, out6. The delay is to prevent large current impulse.

## **Test Circuit**

#### DC characteristic

#### AC characteristic

## **Timing Diagram**

#### 1. CLOCK-SERIAL OUT, OUTn

#### 2. CLOCK-LATCH

#### 3. ENABLE-OUTn (Current)

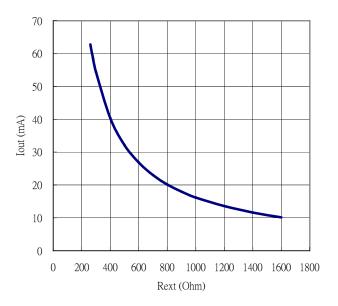

## **Output Current vs. External Resistor**

Iout  $\approx 1.3 \text{V} / \text{Rext} * 12.5$

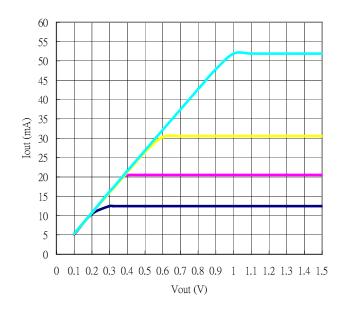

## **Output Current Performance vs. Output Voltage**

Note: In order to obtain a good constant current output, a suitable output voltage is necessary. Users can get related information about the minimum output voltage from the above graph.

#### Note

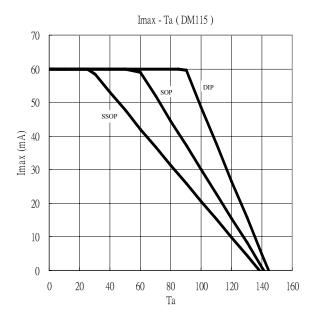

As the power dissipation of a semiconductor chip is limited its package and ambient temperature, this device requires a maximum output current be calculated for a given operating condition. The maximum allowable power consumption (Pd (max)) of this device is calculated as follows:

$$Pd(\max)(Watt) = \frac{(\text{Tj (junction temperature) (max) - Ta (ambient temperature) )(^{\circ}C)}{\text{Rth (}^{\circ}C/Watt)}$$

Based on the Pd (max), the maximum allowable current can be calculated as follows:

$$Iout = (Pd - V_{DD} \cdot I_{DD}) / (\# outputs \cdot Vo \cdot Duty)$$

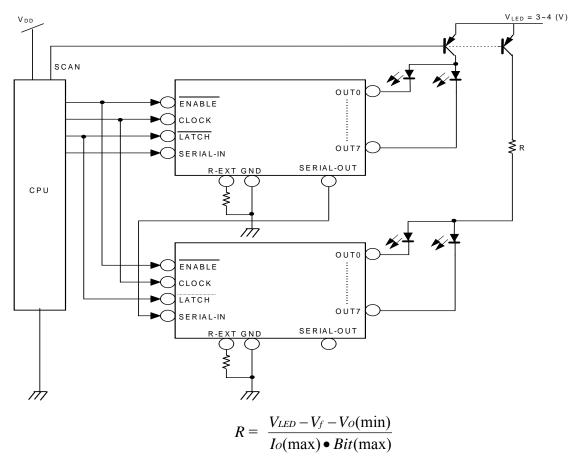

#### **System Configuration Example**

#### [1] Output current (I<sub>OUT</sub>)

Sink current is set by the external resistor as shown in figure (Iout vs. Rext).

[2] LED supply voltage (V<sub>LED</sub>) setup

$$V_{LED} = V_{CE} (T_r V_{sat}) + V_f (LED \text{ forward voltage}) + V_O (IC \text{ supply voltage})$$

To prevent too much power dissipated by the device due to higher  $V_{LED}$ , an additional R can be used to reduce the Vout when the outputs consume current:

Note

This device has only one ground pin shared by signal, output sink current, and power ground. It is advisable to pattern the ground layout with minimized inductance such that the switching noise induced by the input signals and the output sink current would not cause chip malfunction. To prevent the drivers' outputs from damage by overshoot stress, it is also advisable not to turn off the drivers and scan transistors simultaneously.

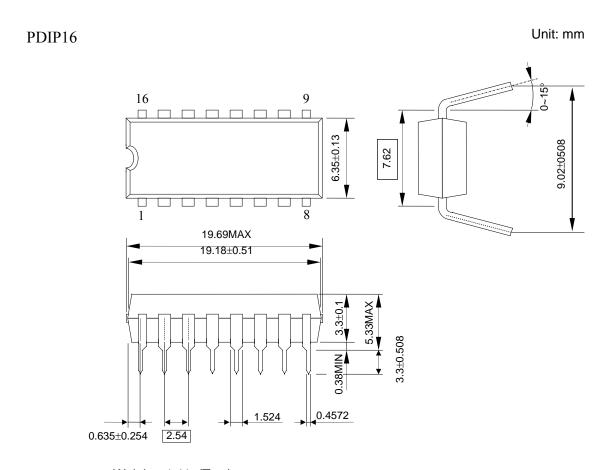

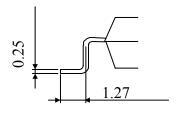

## **Package Outline**

Weight: 1.11g(Typ.)

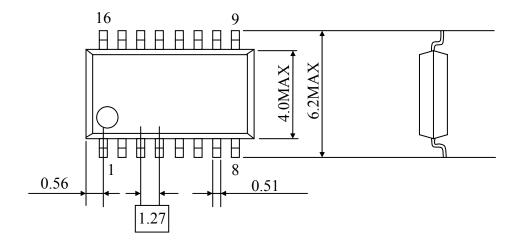

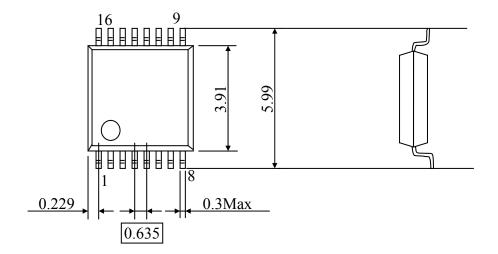

## **Package Outline**

SOP16 Unit: mm

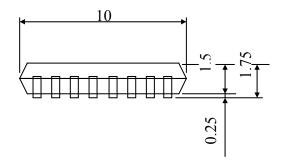

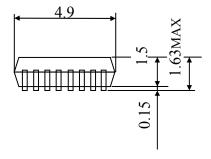

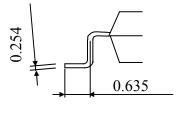

## **Package Outline**

SSOP16 Unit: mm

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.