### SM5168 series

# PLL Synthesizer IC

### **OVERVIEW**

The SM5168 series are PLL synthesizer ICs fabricated using NPC's Molybdenum-gate CMOS process. They provide several combinations of reference and comparator frequency divider ratios, set in master-slice, making them ideal for frequency synthesizers in IF stages of mobile communications devices. They also feature a lock detect signal output (LD).

### **FEATURES**

- 2.7 to 3.6V operating supply voltage range

- Maximum operating frequency

- SM5168A× series: 200MHz,  $V_{DD} = 2.7V$

- SM5168C× series: 340MHz,  $V_{DD} = 2.7V$

- Operating current consumption

- SM5168A× series: 3.3mA (typ, 200MHz at 0.3Vp-p, V<sub>DD</sub> = 3.0 V)

- SM5168C× series: 4mA (typ, 340MHz at 0.3Vp-p, V<sub>DD</sub> = 3.0 V)

- SM5168A× (built-in standby function) and SM168C× (dual frequency divider ratios) series available, as set by master-slice

- Charge pump output with output polarity for connection to passive filter

- Lock detect function output

- -30 to 85°C operating temperature range

- 8-pin plastic VSOP

### **APPLICATIONS**

- Mobile communications

- Portable telephones

- Related applications

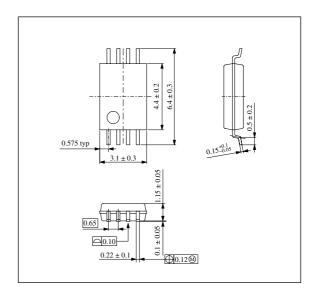

### **PACKAGE DIMENSIONS**

(Unit: mm)

### **SERIES CONFIGURATION**

| Version         | Maximum operating | Reference/comparator | Frequency divid | Standby function |     |

|-----------------|-------------------|----------------------|-----------------|------------------|-----|

| frequency       |                   | frequency dividers   | N counter       | Standby function |     |

| SM5168A× series | 200MHz            | 1                    | 272 to 65535    | 5 to 65535       | Yes |

| SM5168C× series | 340MHz            | 2                    | 272 to 65535    | 5 to 65535       | No  |

<sup>1.</sup> SM5168C $\times$  series: Dual frequency divider ratios are set within the ratio ranges.

### ORDERING INFORMATION

| Device    | Package    |  |  |

|-----------|------------|--|--|

| SM5168××V | 8-pin VSOP |  |  |

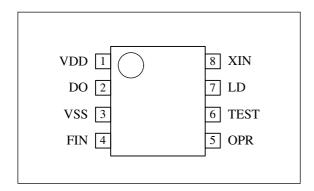

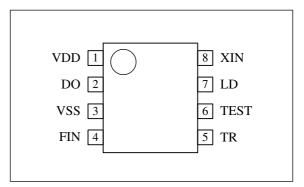

# **PINOUT**

(Top view)

### SM5168A× series

### SM5168C× series

# **PIN DESCRIPTION**

| Number | Name                     | I/O | Description                                                                                                                                                                                                 |  |

|--------|--------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | VDD                      | -   | 2.7 to 3.6V supply                                                                                                                                                                                          |  |

| 2      | DO                       | 0   | Phase comparator error signal three-state output pin.  Built-in charge pump means that this output can be connected to a low-pass filter. The output polarity is preset for connection to a passive filter. |  |

| 3      | VSS                      | -   | Ground pin                                                                                                                                                                                                  |  |

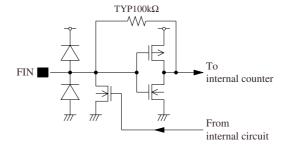

| 4      | FIN                      | ı   | Phase comparator frequency divider (N-counter) signal input pin. Feedback resistor built-in, so input can be AC-coupled.                                                                                    |  |

| 5      | OPR<br>(SM5168A× series) |     | Power-save control pin.<br>Start when HIGH, standby mode when LOW.                                                                                                                                          |  |

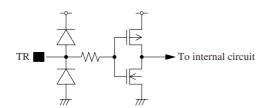

| 3      | TR<br>(SM5168C× series)  | 1   | Frequency divider switching control. Switches between 2 sets of reference and comparator frequency dividers.                                                                                                |  |

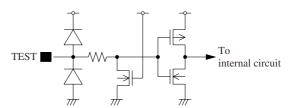

| 6      | TEST                     | I   | Test pin. Leave open or connect to VSS for normal operation.                                                                                                                                                |  |

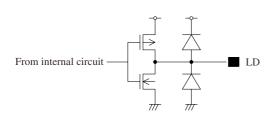

| 7      | LD                       | 0   | Unlock signal output pin. (Unlocked when LOW)                                                                                                                                                               |  |

| 8      | XIN                      | I   | Reference frequency divider (R-counter) external clock input pin. Feedback resistor built-in, so input can be AC-coupled.                                                                                   |  |

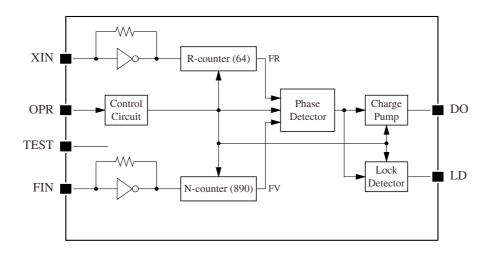

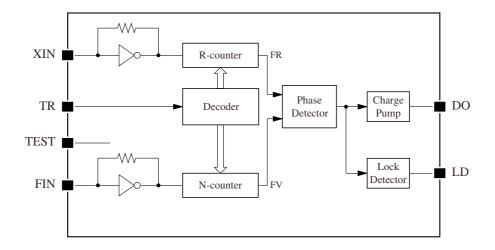

# **BLOCK DIAGRAMS**

### SM5168A× series

### SM5168C× series

# **SPECIFICATIONS**

# **Absolute Maximum Ratings**

$$V_{SS} = 0V$$

| Parameter                 | Symbol           | Rating                                  | Unit |

|---------------------------|------------------|-----------------------------------------|------|

| Supply voltage            | V <sub>DD</sub>  | -0.3 to 6.0                             | V    |

| Input voltage range       | V <sub>IN</sub>  | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

| Storage temperature range | T <sub>STG</sub> | -55 to 125                              | °C   |

| Power dissipation         | P <sub>D</sub>   | 100                                     | mW   |

# **Recommended Operating Conditions**

$$V_{SS} = 0V$$

| Parameter                   | Symbol           | Rating     | Unit |

|-----------------------------|------------------|------------|------|

| Supply voltage              | V <sub>DD</sub>  | 2.7 to 3.6 | V    |

| Operating temperature range | T <sub>OPR</sub> | -30 to 85  | °C   |

### **Electrical Characteristics**

$V_{SS} = 0V$ ,  $V_{DD} = 2.7$  to 3.6V, Ta = -30 to  $85^{\circ}C$  unless otherwise noted.

| D                                                     | 0                 | 0 1111 -                       | Condition              |                       | Rating |     |      |

|-------------------------------------------------------|-------------------|--------------------------------|------------------------|-----------------------|--------|-----|------|

| Parameter                                             | Symbol            | ol Condition                   |                        | min                   | typ    | max | Unit |

| Supply voltage                                        | V <sub>DD</sub>   |                                |                        | 2.7                   | -      | 3.6 | V    |

| VDD operating current consumption 1 (SM5168A× series) |                   | Note 4                         | V <sub>DD</sub> = 3.0V | -                     | 3.3    | -   | 4    |

|                                                       | l <sub>DD1</sub>  | Note 1.                        | V <sub>DD</sub> = 3.3V | -                     | -      | 5.2 | - mA |

| VDD operating current consumption 2                   |                   | Note 0                         | V <sub>DD</sub> = 3.0V | -                     | 4      | _   | - mA |

| (SM5168C× series)                                     | I <sub>DD2</sub>  | Note 2.                        | V <sub>DD</sub> = 3.6V | -                     | -      | 8   |      |

| FIN maximum operating frequency 1 (SM5168A× series)   | f <sub>max1</sub> | 300mVp-p sine wave.<br>Note 3. | V <sub>DD</sub> = 2.7V | 200                   | -      | _   | MHz  |

| XIN maximum operating frequency 1 (SM5168A× series)   | f <sub>max2</sub> | 300mVp-p sine wave<br>Note 3.  | V <sub>DD</sub> = 2.7V | 20                    | -      | -   | MHz  |

| FIN maximum operating frequency 2 (SM5168C× series)   | f <sub>max1</sub> | 300mVp-p sine wave<br>Note 3.  | V <sub>DD</sub> = 2.7V | 340                   | -      | _   | MHz  |

| XIN maximum operating frequency 2 (SM5168C× series)   | f <sub>max2</sub> | 300mVp-p sine wave<br>Note 3.  | V <sub>DD</sub> = 2.7V | 20                    | -      | _   | MHz  |

| FIN minimum operating input frequency                 | f <sub>min</sub>  | 300mVp-p sine wave<br>Note 3.  | V <sub>DD</sub> = 3.6V | -                     | -      | 10  | MHz  |

| FIN AC-coupled input voltage range                    | V <sub>AC1</sub>  | 340MHz                         | V <sub>DD</sub> = 2.7V | 0.3                   | -      | _   | Vp-p |

| XIN AC-coupled input voltage range                    | V <sub>AC2</sub>  | 20MHz                          | V <sub>DD</sub> = 2.7V | 0.3                   | -      | _   | Vp-p |

| OPR, TR LOW-level input voltage                       | V <sub>IL</sub>   |                                | V <sub>DD</sub> = 2.7V | -                     | -      | 0.3 | V    |

| OPR, TR HIGH-level input voltage                      | V <sub>IH</sub>   |                                | V <sub>DD</sub> = 2.7V | V <sub>DD</sub> - 0.3 | -      | _   | V    |

| XIN LOW-level input current                           | I <sub>IL1</sub>  | V <sub>IN</sub> = 0V           | V <sub>DD</sub> = 3.6V | -                     | -      | 50  | μΑ   |

| FIN LOW-level input current                           | I <sub>IL2</sub>  | V <sub>IN</sub> = 0V           | V <sub>DD</sub> = 3.6V | -                     | -      | 50  | μΑ   |

| XIN HIGH-level input current                          | I <sub>IH1</sub>  | $V_{IN} = V_{DD}$              | V <sub>DD</sub> = 3.6V | -                     | -      | 50  | μΑ   |

| FIN HIGH-level input current                          | I <sub>IH2</sub>  | $V_{IN} = V_{DD}$              | V <sub>DD</sub> = 3.6V | -                     | -      | 50  | μΑ   |

| OPR, TR LOW-level input leakage current               | I <sub>LL</sub>   | V <sub>IN</sub> = 0V           | V <sub>DD</sub> = 3.6V | -                     | -      | 100 | nA   |

| OPR, TR HIGH-level input leakage current              | I <sub>LH</sub>   | $V_{IN} = V_{DD}$              | V <sub>DD</sub> = 3.6V | -                     | -      | 100 | nA   |

| DO, LD LOW-level output voltage                       | V <sub>OL</sub>   | I <sub>OL</sub> = 0.25mA       | V <sub>DD</sub> = 2.7V | -                     | -      | 0.4 | V    |

| DO, LD HIGH-level output voltage                      | V <sub>OH</sub>   | I <sub>OH</sub> = 0.25mA       | V <sub>DD</sub> = 2.7V | V <sub>DD</sub> - 0.4 | -      | _   | V    |

| DO, LD LOW-level output current                       | l <sub>OL</sub>   | V <sub>OL</sub> = 0.4V         | V <sub>DD</sub> = 2.7V | 0.25                  | -      | -   | mA   |

| DO, LD HIGH-level output current                      | I <sub>OH</sub>   | $V_{OH} = V_{DD} - 0.4V$       | V <sub>DD</sub> = 2.7V | 0.25                  | -      | -   | mA   |

| DO three-state output high-impedance                  | l <sub>OZL</sub>  | V <sub>OL</sub> = 0V           | V <sub>DD</sub> = 3.6V | -                     | -      | 100 | nA   |

| leakage current                                       | I <sub>OZH</sub>  | $V_{OH} = V_{DD}$              | V <sub>DD</sub> = 3.6V | -                     | -      | 100 | nA   |

Note 1.  $f_{FIN}$  = 200MHz (300mVp-p sine wave),  $f_{XIN}$  = 20MHz (300mVp-p sine wave), TR = HIGH Note 2.  $f_{FIN}$  = 340MHz (300mVp-p sine wave),  $f_{XIN}$  = 20MHz (300mVp-p sine wave), TR = HIGH Note 3. Signal generator AC-coupled input with  $50\Omega$  termination.

### **FUNCTIONAL DESCRIPTION**

### SM5168A× series

### Frequency dividers

The comparator frequency divider (N-counter) and reference frequency divider (R-counter), one of each, are set in master-slice to the following values.

- Comparator frequency divider (N-counter) = 272 to 65535

- Reference frequency divider (R-counter) = 5 to 65535

### Standby mode

When OPR goes from HIGH to LOW, the PLL is in standby mode with the following input/output conditions.

| Block                                    | State     |

|------------------------------------------|-----------|

| Input FIN                                | LOW level |

| Comparator frequency divider (N-counter) | Stopped   |

| Input XIN                                | LOW level |

| Reference frequency divider (R-counter)  | Stopped   |

| Phase comparator                         | Reset     |

| Output DO                                | Floating  |

| Output LD                                | LOW-level |

When OPR goes from LOW to HIGH, standby mode is released and the PLL is in operating mode, and the following start-up sequence is executed.

Internal feedback resistance is connected to XIN to activate the reference frequency divider (R-counter). Internal feedback resistance is connected to FIN.

The comparator frequency divider (N-counter) and the phase comparator are reset.

DO is floating and LD is LOW.

$\downarrow$

Reference frequency divider (R-counter) starts to perform frequency division. An internal signal (FR signal) is output on the 2nd clock cycle.

1

Phase comparator starts and comparator frequency divider (N-counter) starts to perform frequency division. DO floating condition is released and LD goes HIGH.

#### SM5168C× series

### **Frequency Dividers**

The comparator frequency divider (N-counter) and reference frequency divider (R-counter), with 2 sets of comparator frequency divider and reference frequency divider ratios, are set in master-slice. The frequency divider set selected is determined by the state of TR (pin 5). The ratio ranges are the same when TR is HIGH or LOW, and are:

- Comparator frequency divider (N-counter) = 272 to 65535

- Reference frequency divider (R-counter) = 5 to 65535

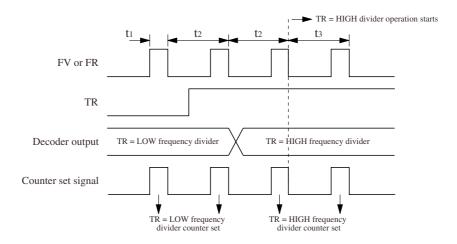

## Frequency Divider Switching

When switching the frequency dividers using TR, the dividers switch in sync with the R-counter divider signal (FR) and the N-counter divider signal (FV) to minimize any disturbance in the PLL loop.

If t<sub>F</sub> represents the FIN cycle time:

$t_1 = 48t_F$

$t_2 = (divider ratio when TR = LOW) \times t_F$

$t_3 = (divider ratio when TR = HIGH) \times t_F$

If t<sub>X</sub> represents the XIN cycle time:

$t_1 = 3t_X$

$t_2 = (divider ratio when TR = LOW) \times t_X$

$t_3$  = (divider ratio when TR = HIGH)  $\times$   $t_X$

Both the R-counter and N-counter are configured with presettable counters. The divider outputs (FR and FV) are then input to the phase comparator which performs phase comparison on the falling edge of each signal. The FR/FV signals also function as the R/N-counter preset strobe signals, respectively. Consequently, when the TR signal level switches, the decoder output changes on the first FR/FV (R/N-counter preset strobe) signal and the counters are set in the new frequency dividers on the second FR/FV (R/N-counter preset strobe) signal. Frequency division with the new frequency dividers starts on the falling edge of the second FR/FV (R/N-counter preset strobe) signal.

The timing in the diagram shows an example when TR goes from LOW to HIGH only, but the timing operation is identical under the reverse transition. The R/N-counters operate with the same timing, although the N-counter has a dual modulus prescaler in the initial-stage which means the HIGH-level pulsewidth of the FV and FR signals is different.

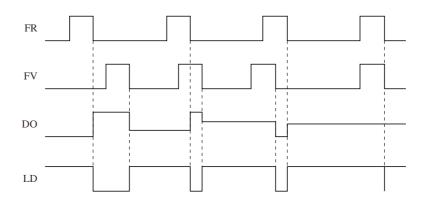

# **DO Output Timing**

The phase comparator error signal charge pump signal is output on DO with polarity for connection to an external passive filter. The signals compared are FV and FR, which are the internal comparator frequency divider output signal and reference frequency divider output signal, respectively. The timing is shown in the following figure.

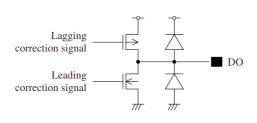

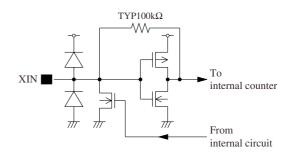

## INPUT/OUTPUT EQUIVALENT CIRCUITS

DO FIN

TR TEST

LD XIN

Please pay your attention to the following points at time of using the products shown in this document.

The products shown in this document (hereinafter "Products") are not intended to be used for the apparatus that exerts harmful influence on human lives due to the defects, failure or malfunction of the Products. Customers are requested to obtain prior written agreement for such use from SEIKO NPC CORPORATION (hereinafter "NPC"). Customers shall be solely responsible for, and indemnify and hold NPC free and harmless from, any and all claims, damages, losses, expenses or lawsuits, due to such use without such agreement. NPC reserves the right to change the specifications of the Products in order to improve the characteristic or reliability thereof. NPC makes no claim or warranty that the contents described in this document dose not infringe any intellectual property right or other similar right owned by third parties. Therefore, NPC shall not be responsible for such problems, even if the use is in accordance with the descriptions provided in this document. Any descriptions including applications, circuits, and the parameters of the Products in this document are for reference to use the Products, and shall not be guaranteed free from defect, inapplicability to the design for the mass-production products without further testing or modification. Customers are requested not to export or re-export, directly or indirectly, the Products to any country or any entity not in compliance with or in violation of the national export administration laws, treaties, orders and regulations. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

#### SEIKO NPC CORPORATION

15-6, Nihombashi-kabutocho, Chuo-ku, Tokyo 103-0026, Japan Telephone: +81-3-6667-6601 Facsimile: +81-3-6667-6611 http://www.npc.co.jp/ Email: sales@npc.co.jp

NC0008BE 2006.04