EVALUATION KIT

## **General Description**

The MAX9730 features a mono Class G power amplifier with an integrated inverting charge-pump power supply. The charge pump can supply up to 500mA of peak output current over a 2.7VDC to 5.5VDC supply voltage range, guaranteeing up to 2.4W output power into an  $8\Omega$  load. The 2.4W output power allows for transient audio content to remain unclipped as the battery rail collapses over time.

The MAX9730 maximizes battery life by offering highperformance efficiency. Maxim's proprietary output stage provides efficiency levels greater than Class AB devices without the EMI penalties commonly associated with Class D amplifiers. High efficiency allows the MAX9730 to be packaged in a WLP package without derating the output power handling capability.

The device utilizes fully differential inputs and outputs, comprehensive click-and-pop suppression, shutdown control, and soft-start circuitry. The MAX9730 is fully specified over the -40°C to +85°C extended temperature range and is available in ultra-small, lead-free, 20-bump WLP (2mm x 2.5mm) and 28-pin TQFN (4mm x 4mm) packages.

### **Applications**

MP3 Players Personal Media Players Handheld Gaming Consoles Cell Phones Smartphones Notebook Computers

|   | F | e | at | U | re | S |

|---|---|---|----|---|----|---|

| _ |   |   |    |   |    |   |

- ♦ 2.7V to 5.5V Operation

- Integrated Charge-Pump Power Supply

- 63% Efficiency (Vcc = 5V, Pout = 1W)

- 2.4W Output Power into 8Ω at Vcc = 5V

- Clickless/Popless Operation

- Small Thermally Efficient Packages 2mm x 2.5mm 20-Bump WLP 4mm x 4mm 28-Pin TQFN

## **Ordering Information**

| PART            | PIN-PACKAGE | TEMP RANGE     |  |

|-----------------|-------------|----------------|--|

| MAX9730EWP+TG45 | 20 WLP      | -40°C to +85°C |  |

| MAX9730ETI+     | 28 TQFN-EP* | -40°C to +85°C |  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

G45 indicates protective die coating.

\*EP = Exposed pad.

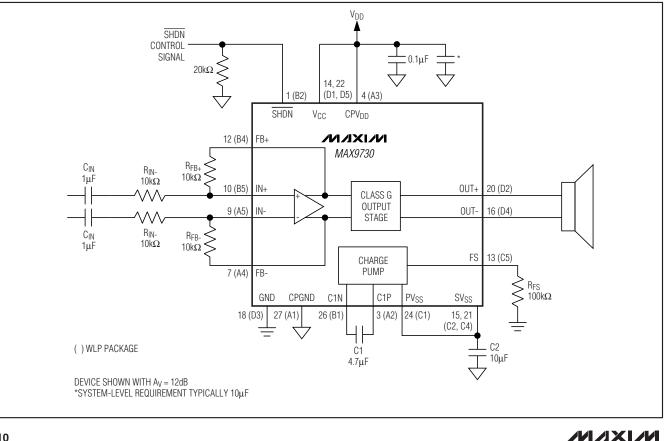

Typical Application Circuit/Functional Diagram and Pin Configurations appear at end of data sheet.

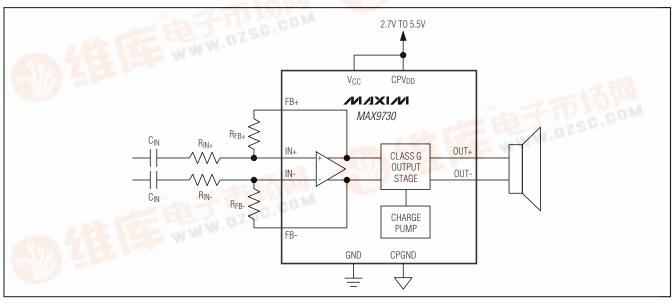

## Simplified Block Diagram

MIXI/N

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

(Voltages with respect to GND.)

| V <sub>CC</sub> , CPV <sub>DD</sub> 0.3V to +6V                |  |

|----------------------------------------------------------------|--|

| PV <sub>SS</sub> , SV <sub>SS</sub> 6V to +0.3V                |  |

| CPGND0.3V to +0.3V                                             |  |

| OUT+, OUT(SV <sub>SS</sub> - 0.3V) to (V <sub>CC</sub> + 0.3V) |  |

| IN+, IN-, FB+, FB0.3V to (V <sub>CC</sub> + 0.3V)              |  |

| C1N( $PV_{SS} - 0.3V$ ) to (CPGND + 0.3V)                      |  |

| C1P(CPGND - 0.3V) to (CPV <sub>DD</sub> + 0.3V)                |  |

| FS, <u>SHDN</u> 0.3V to (V <sub>CC</sub> + 0.3V)               |  |

| Continuous Current Into/Out of                                 |  |

| OUT+, OUT-, V <sub>CC</sub> , GND, SV <sub>SS</sub> 800mA      |  |

| CPV <sub>DD</sub> , CPGND, C1P, C1N, PV <sub>SS</sub> 800mA    |  |

| Any Other Pin20mA                                              |  |

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| 20-Bump WLP (derate 10.3mW/°C above +70°C)827n  | nW  |

|-------------------------------------------------|-----|

| 28-Pin TQFN (derate 20.8mW/°C above +70°C)1667n | nW  |

| Operating Temperature Range40°C to +85          | ŏ°С |

| Storage Temperature Range65°C to +150           |     |

| Lead Temperature (soldering, 10s)+300           | )°C |

| Bump Temperature (soldering) Reflow+260         | )°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{CPVDD} = V_{SHDN} = 3.6V, V_{GND} = V_{CPGND} = 0V, R_{IN+} = R_{IN-} = 10k\Omega, R_{FB+} = R_{FB-} = 10k\Omega, R_{FS} = 100k\Omega, C1 = 4.7\mu$ F, C2 = 10µF; speaker load resistors (R<sub>L</sub>) are terminated between OUT+ and OUT-, unless otherwise stated; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                     | SYMBOL          | CONDITIONS                                                                             | MIN | ТҮР  | MAX | UNITS |  |

|-------------------------------|-----------------|----------------------------------------------------------------------------------------|-----|------|-----|-------|--|

| GENERAL                       |                 | ·                                                                                      |     |      |     |       |  |

| Supply Voltage Range          | Vcc             | Inferred from PSRR test                                                                | 2.7 |      | 5.5 | V     |  |

| Quiescent Current             | Icc             |                                                                                        |     | 8    | 12  | mA    |  |

| Chip Power Dissipation        | PDISS           | $V_{OUT} = 2.8 V_{RMS}$ , f = 1kHz, R <sub>L</sub> = 8 $\Omega$                        |     | 0.9  |     | W     |  |

| Shutdown Current              | ISHDN           | SHDN = GND                                                                             |     | 0.3  | 5   | μΑ    |  |

| Turn-On Time                  | ton             | Time from shutdown or power-on to full operation                                       |     | 50   |     | ms    |  |

| Input DC Bias Voltage         | VBIAS           | IN_ inputs                                                                             | 1.1 | 1.24 | 1.4 | V     |  |

| Charge-Pump Oscillator        | 6               | I <sub>LOAD</sub> = 0mA (slow mode)                                                    | 55  | 83   | 110 | kHz   |  |

| Frequency (Slow Mode)         | fosc            | I <sub>LOAD</sub> > 100mA (normal mode)                                                | 230 | 330  | 430 |       |  |

| Maximum Capacitive Load       | CL              |                                                                                        |     | 200  |     | рF    |  |

|                               |                 | VIH                                                                                    | 1.4 |      |     | V     |  |

| SHDN Input Threshold (Note 3) |                 | VIL                                                                                    |     |      | 0.4 | v     |  |

| SHDN Input Leakage Current    |                 |                                                                                        |     |      | ±1  | μA    |  |

| SPEAKER AMPLIFIER             |                 |                                                                                        |     |      |     |       |  |

| Output Offset Voltage         | V <sub>OS</sub> | $T_A = +25^{\circ}C$                                                                   |     | ±3   | ±15 | mV    |  |

|                               |                 | $T_{MIN} \le T_A \le T_{MAX}$                                                          |     |      | ±20 |       |  |

| Common-Mode Rejection Ratio   | CMRR            | $f_{IN} = 1 \text{kHz} \text{ (Note 4)}$                                               |     | 68   |     | dB    |  |

| Click-and-Pop Level           | V <sub>CP</sub> | Peak voltage into/out of shutdown<br>A-weighted, 32 samples per second<br>(Notes 5, 6) |     | -52  |     | dBV   |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{CPVDD} = V_{SHDN} = 3.6V, V_{GND} = V_{CPGND} = 0V, R_{IN+} = R_{IN-} = 10k\Omega, R_{FB+} = R_{FB-} = 10k\Omega, R_{FS} = 100k\Omega, C1 = 4.7\mu$ F, C2 = 10µF; speaker load resistors (R<sub>L</sub>) are terminated between OUT+ and OUT-, unless otherwise stated; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                      | SYMBOL | CONDITI                                                          | ONS                                                  | MIN  | ТҮР   | MAX  | UNITS |  |

|--------------------------------|--------|------------------------------------------------------------------|------------------------------------------------------|------|-------|------|-------|--|

| Voltage Gain                   | Av     | (Notes 4, 7)                                                     |                                                      | 11.5 | 12    | 12.5 | dB    |  |

|                                |        |                                                                  | $V_{CC} = 5V$                                        |      | 2.4   |      | w     |  |

| Captionaus Output Power        | Davia  | THD+N = 1%, f = 1kHz,                                            | $V_{CC} = 4.2V$                                      |      | 1.67  |      |       |  |

| Continuous Output Power        | POUT   | $R_L = 8\Omega$                                                  | $V_{CC} = 3.6V$                                      |      | 1.25  |      |       |  |

|                                |        |                                                                  | $V_{CC} = 3.0V$                                      |      | 0.8   |      |       |  |

|                                |        |                                                                  | $V_{CC} = 5V$                                        |      | 7.1   |      |       |  |

|                                |        | f = 1kHz, 1% THD+N,                                              | $V_{CC} = 4.2V$                                      |      | 5.9   |      | VRMS  |  |

|                                |        | $Z_L = 1\mu F + 10\Omega$                                        | $V_{CC} = 3.6V$                                      |      | 5.1   |      |       |  |

|                                |        |                                                                  | $V_{CC} = 3.0V$                                      |      | 4.2   |      |       |  |

| Output Voltage                 | Vout   | f = 10kHz, 1% THD+N,<br>Z <sub>L</sub> = 1 $\mu$ F + 10 $\Omega$ | $V_{CC} = 5V$                                        |      | 6.5   |      |       |  |

|                                |        |                                                                  | $V_{CC} = 4.2V$                                      |      | 5.4   |      |       |  |

|                                |        |                                                                  | $V_{CC} = 3.6V$                                      |      | 4.7   |      |       |  |

|                                |        |                                                                  | V <sub>CC</sub> = 3.0V                               |      | 3.8   |      |       |  |

|                                | PSRR   | V <sub>CC</sub> = 2.7V to 5.5V                                   |                                                      | 63   | 77    |      |       |  |

| Power-Supply Rejection Ratio   |        | f = 217Hz, 200mV <sub>P-P</sub> ripple                           |                                                      |      | 77    |      | dB    |  |

| (Note 4)                       |        | f = 1kHz, 200mV <sub>P-P</sub> ripple                            |                                                      |      | 77    |      |       |  |

|                                |        | f = 20kHz, 200mV <sub>P-P</sub> ripple                           |                                                      |      | 58    |      |       |  |

| Total Harmonic Distortion Plus |        | $R_L = 8\Omega$ , $V_{OUT} = 1$ kHz / 4                          | $R_L = 8\Omega$ , $V_{OUT} = 1$ kHz / 400m $V_{RMS}$ |      | 0.007 |      | 0/    |  |

| Noise                          | THD+N  | $R_L = 8\Omega$ , $V_{OUT} = 1kHz / 1V_{RMS}$                    |                                                      |      | 0.12  |      | %     |  |

| Signal-to-Noise Ratio          | SNR    | $V_{OUT} = 0.5V_{RMS}$ , inputs to GND by C1N, A-weighted        |                                                      |      | 95    |      | dB    |  |

| Dunamia Danga                  |        | (Note 0)                                                         | 22Hz to 22kHz                                        |      | 96    |      | dB    |  |

| Dynamic Range                  | DR     | (Note 9)                                                         | A-weighted                                           |      | 99    |      |       |  |

**Note 1:** All devices are 100% production tested at room temperature. All temperature limits are guaranteed by design.

**Note 2:** Testing performed with resistive and inductive loads to simulate an actual speaker load. For dynamic speakers,  $R_L = 8\Omega$ ,  $68\mu$ H.

**Note 3:** Designed for 1.8V logic.

Note 4: RIN and RFB have 0.5% tolerance.

**Note 5:** Amplifier inputs AC-coupled to GND.

**Note 6:** Testing performed at room temperature with  $8\Omega$  resistive load in series with  $68\mu$ H inductive load connected across BTL output for speaker amplifier. Mode transitions are controlled by SHDN. Vcp is the peak output transient expressed in dBV.

**Note 7:** Voltage gain is defined as:  $[V_{OUT+} - V_{OUT-}] / [V_{IN+} - V_{IN-}]$ .

**Note 8:** Mode A tone burst tested at full amplitude for one cycle and half amplitude for nine cycles. Mode B tone burst tested at full amplitude for three cycles and half amplitude for seven cycles. Full amplitude is defined as 1% THD+N at full battery (V<sub>CC</sub> = 4.2V). *Electrical Characteristics* table targets must be met at THD+N = 1% for one cycle (Mode A) and THD+N < 5% for three cycles (Mode B).

**Note 9:** Dynamic range is calculated by measuring the RMS voltage difference between a -60dBFS output signal and the noise floor, then adding 60dB. Full scale is defined as the output signal needed to achieve 1% THD+N.

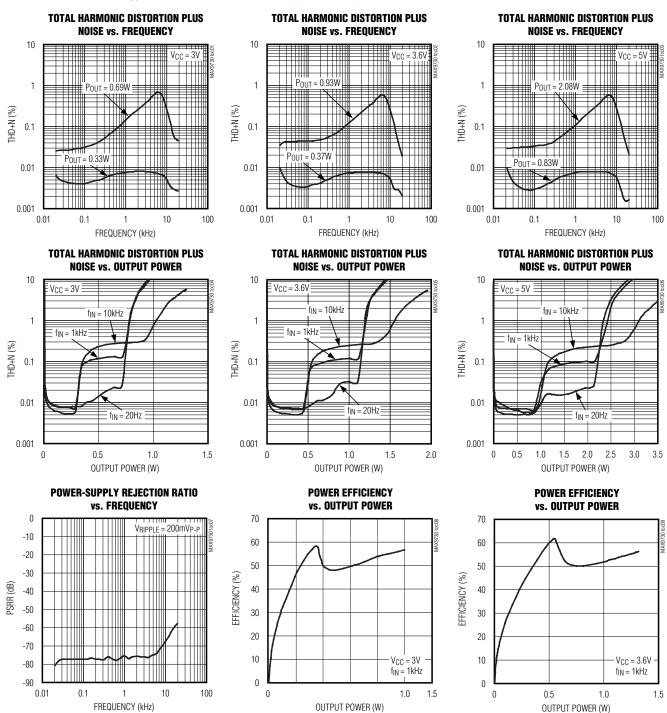

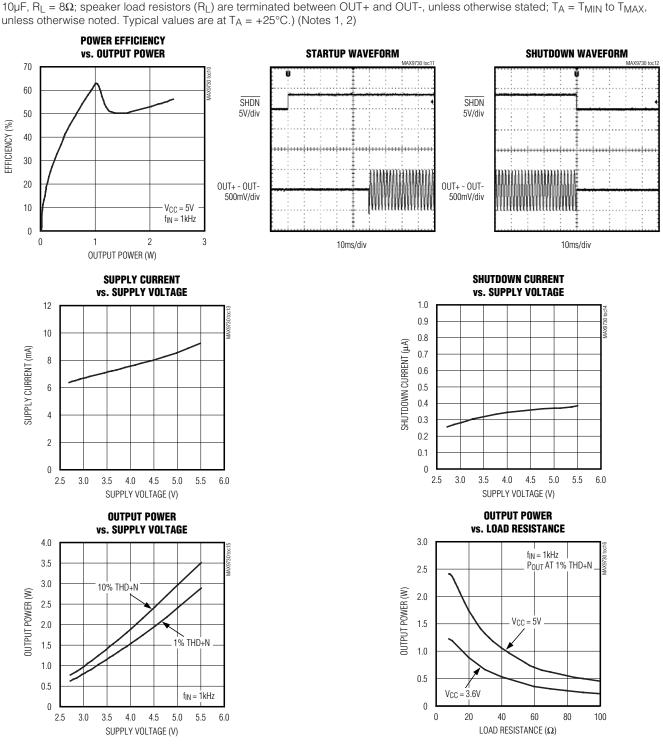

unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 1, 2)

# 2.4W, Single-Supply, Class G Power Amplifier

$10\mu$ F, R<sub>L</sub> = 8 $\Omega$ ; speaker load resistors (R<sub>L</sub>) are terminated between OUT+ and OUT-, unless otherwise stated; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>,

**MAX9730**

## **Typical Operating Characteristics** $(V_{CC} = V_{CPVDD} = V_{\overline{SHDN}} = 3.6V, V_{GND} = V_{CPGND} = 0V, R_{IN+} = R_{IN-} = 10k\Omega, R_{FB+} = R_{FB-} = 10k\Omega, R_{FS} = 100k\Omega, C1 = 4.7\mu\text{F}, C2 = 10k\Omega$

M /X / M

Δ

Typical Operating Characteristics (continued)

$(V_{CC} = V_{CPVDD} = V_{\overline{SHDN}} = 3.6V, V_{GND} = V_{CPGND} = 0V, R_{IN+} = R_{IN-} = 10k\Omega, R_{FB+} = R_{FB-} = 10k\Omega, R_{FS} = 100k\Omega, C1 = 4.7\mu F, C2 = 10k\Omega$  $10\mu$ F, R<sub>L</sub> = 8 $\Omega$ ; speaker load resistors (R<sub>L</sub>) are terminated between OUT+ and OUT-, unless otherwise stated; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 1, 2)

MXXIM

5

# **MAX9730**

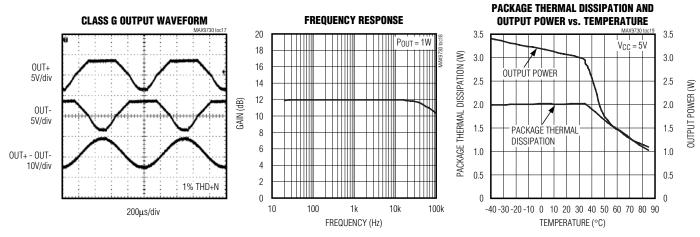

# \_Typical Operating Characteristics (continued)

$(V_{CC} = V_{CPVDD} = V_{SHDN} = 3.6V, V_{GND} = V_{CPGND} = 0V, R_{IN+} = R_{IN-} = 10k\Omega, R_{FB+} = R_{FB-} = 10k\Omega, R_{FS} = 100k\Omega, C1 = 4.7\mu$ F, C2 = 10 $\mu$ F, R<sub>L</sub> = 8 $\Omega$ ; speaker load resistors (R<sub>L</sub>) are terminated between OUT+ and OUT-, unless otherwise stated; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Notes 1, 2)

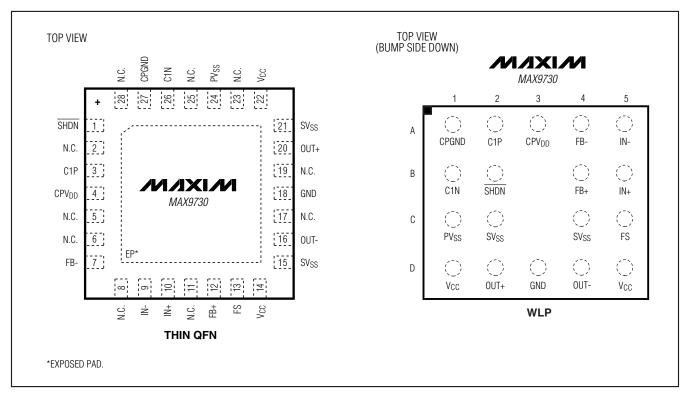

# **Pin Description**

| PIN<br>TQFN WLP                       |        |                  | FUNCTION                                                                                                              |  |  |

|---------------------------------------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

|                                       |        | NAME             |                                                                                                                       |  |  |

| 1                                     | B2     | SHDN             | Shutdown                                                                                                              |  |  |

| 2, 5, 6, 8, 11, 17,<br>19, 23, 25, 28 | _      | N.C.             | No Connection. No internal connection.                                                                                |  |  |

| 3                                     | A2     | C1P              | Charge-Pump Flying Capacitor, Positive Terminal. Connect a $4.7\mu$ F capacitor between C1P and C1N.                  |  |  |

| 4                                     | A3     | CPVDD            | Charge-Pump Positive Supply                                                                                           |  |  |

| 7                                     | A4     | FB-              | Negative Amplifier Feedback                                                                                           |  |  |

| 9                                     | A5     | IN-              | Negative Amplifier Input                                                                                              |  |  |

| 10                                    | B5     | IN+              | Positive Amplifier Input                                                                                              |  |  |

| 12                                    | B4     | FB+              | Positive Amplifier Feedback                                                                                           |  |  |

| 13                                    | C5     | FS               | Charge-Pump Frequency Set. Connect a $100k\Omega$ resistor from FS to GND to set the charge-pump switching frequency. |  |  |

| 14, 22                                | D1, D5 | Vcc              | Supply Voltage. Bypass with a 10µF capacitor to GND.                                                                  |  |  |

| 15, 21                                | C2, C4 | SV <sub>SS</sub> | Amplifier Negative Power Supply. Connect to PVSS.                                                                     |  |  |

| 16                                    | D4     | OUT-             | Negative Amplifier Output                                                                                             |  |  |

| 18                                    | D3     | GND              | Ground                                                                                                                |  |  |

| 20                                    | D2     | OUT+             | Positive Amplifier Output                                                                                             |  |  |

| 24                                    | C1     | PV <sub>SS</sub> | Charge-Pump Output. Connect a $10\mu\text{F}$ capacitor between $\text{PV}_{\text{SS}}$ and CPGND.                    |  |  |

| 26                                    | B1     | C1N              | Charge-Pump Flying Capacitor, Negative Terminal. Connect a 4.7µF capacitor between C1N and C1P.                       |  |  |

| 27                                    | A1     | CPGND            | Charge-Pump Ground. Connect to GND.                                                                                   |  |  |

| EP                                    | _      | EP               | Exposed Pad. Connect the TQFN EP to GND.                                                                              |  |  |

## **Detailed Description**

The MAX9730 Class G power amplifier with inverting charge pump is the latest in linear amplifier technology. The Class G output stage offers the performance of a Class AB amplifier while increasing efficiency to extend battery life. The integrated inverting charge pump generates a negative supply capable of delivering up to 500mA.

The Class G output stage and the inverting charge pump allow the MAX9730 to deliver an output power that is up to four times greater than a traditional single-supply linear amplifier. This allows the MAX9730 to maintain 0.8W into an  $8\Omega$  load as the battery rail collapses.

#### **Class G Operation and Efficiency**

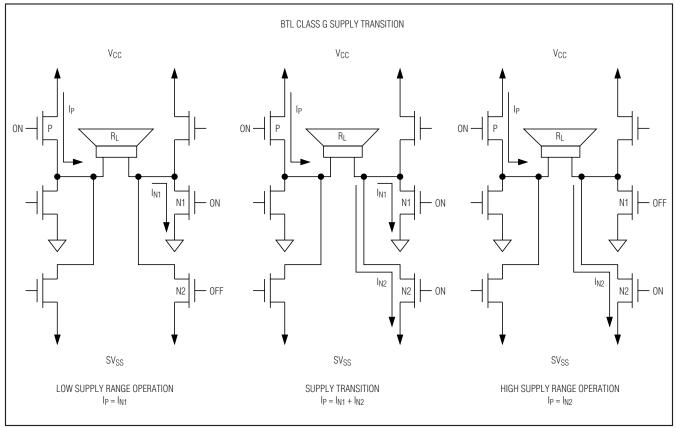

The MAX9730 Class G amplifier is a linear amplifier that operates within a low (V<sub>CC</sub> to GND) and high (V<sub>CC</sub> to SV<sub>SS</sub>) supply range. Figure 1 illustrates the transition from the low to high supply range. For small signals, the device operates within the lower (V<sub>CC</sub> to GND) sup-

ply range. In this range, the operation of the device is identical to a traditional single-supply Class AB amplifier where:

#### $I_{LOAD} = I_{N1}$

As the output signal increases, so a wider supply is needed, the device begins its transition to the higher supply range ( $V_{CC}$  to  $SV_{SS}$ ) for the large signals. To ensure a seamless transition between the low and high supply ranges, both of the lower transistors are on so that:

#### $I_{LOAD} = I_{N1} + I_{N2}$

As the output signal continues to increase, the transition to the high supply is complete. The device then operates in the higher supply range, where the operation of the device is identical to a traditional dual-supply Class AB amplifier where:

#### $I_{LOAD} = I_{N2}$

During operation, the output common-mode voltage of the MAX9730 adjusts dynamically as the device transitions between supply ranges.

Figure 1. Class G Supply Transition

Utilizing a Class G output stage with an inverting charge pump allows the MAX9730 to realize a 2.4W output power with a 5V supply.

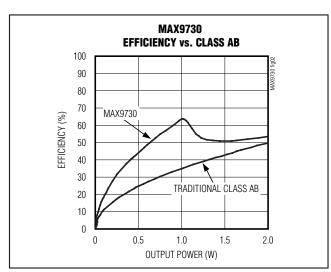

The theoretical best efficiency of a linear amplifier is 78%; however, that efficiency is only exhibited at peak output powers. Under normal operating levels (typical music reproduction levels), efficiency falls below 30%, whereas the MAX9730 still exhibits 50% efficiency under the same conditions.

#### **Inverting Charge Pump**

The MAX9730 features an integrated charge pump with an inverted supply rail that can supply greater than 700mA over the positive 2.7V to 5.5V supply range. In the case of the MAX9730, the charge pump generates the negative supply rail ( $PV_{SS}$ ) needed to create the higher supply range, which allows the output of the device to operate over a greater dynamic range as the battery supply collapses over time.

#### Shutdown Mode

The MAX9730 has a shutdown mode that reduces power consumption and extends battery life. Driving SHDN low places the MAX9730 in a low-power ( $0.3\mu A$ ) shutdown mode. Connect SHDN to V<sub>CC</sub> for normal operation.

#### **Click-and-Pop Suppression**

The MAX9730 Class G amplifier features Maxim's comprehensive, industry-leading click-and-pop suppression. During startup, the click-and-pop suppression circuitry eliminates any audible transient sources internal to the device.

## **Applications Information**

#### **Differential Input Amplifier**

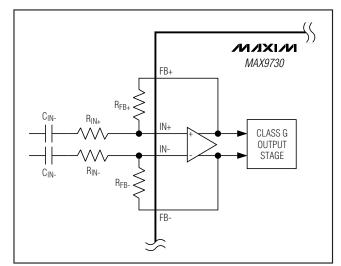

The MAX9730 features a differential input configuration, making the device compatible with many CODECs, and offering improved noise immunity over a single-ended input amplifier. In devices such as PCs, noisy digital signals can be picked up by the amplifier's input traces. The signals appear at the amplifiers' inputs as common-mode noise. A differential input amplifier amplifies the difference of the two inputs, and signals common to both inputs are canceled out. When configured for differential inputs, the voltage gain of the MAX9730 is set by:

$$A_V = 20 \log \left[ 4 \times \left( \frac{R_{FB_-}}{R_{IN_-}} \right) \right] (dB)$$

where A<sub>V</sub> is the desired voltage gain in dB. R<sub>IN+</sub> should be equal to R<sub>IN-</sub> and R<sub>FB+</sub> should be equal to R<sub>FB-</sub>. The Class G output stage has a fixed gain of 4V/V (12dB). Any gain or attenuation set by the external input stage resistors will add to or subtract from this fixed gain. See Figure 3.

Figure 2. MAX9730 Efficiency vs. Class AB Efficiency vs. Class D Efficiency

Figure 3. Gain Setting

In differential input configurations, the common-mode rejection ratio (CMRR) is primarily limited by the external resistor and capacitor matching. Ideally, to achieve the highest possible CMRR, the following external components should be selected where:

$$\frac{R_{FB+}}{R_{IN+}} = \frac{R_{FB-}}{R_{IN-}}$$

and

$$C_{IN+} = C_{IN-}$$

#### **Component Selection**

#### Input-Coupling Capacitor

The AC-coupling capacitors  $(C_{IN})$  and input resistors  $(R_{IN})$  form highpass filters that remove any DC bias from an input signal (see the *Typical Application Circuit/Functional Diagram*). C<sub>IN</sub> blocks DC voltages from the amplifier. The -3dB point of the highpass filter, assuming zero source impedance due to the input signal source, is given by:

$$f_{-3dB} = \frac{1}{2\pi \times R_{IN} \times C_{IN}} (Hz)$$

Choose  $C_{IN}$  so that  $f_{-3dB}$  is well below the lowest frequency of interest. Setting  $f_{-3dB}$  too high affects the amplifier's low frequency response. Use capacitors with low-voltage coefficient dielectrics. Aluminum electrolytic, tantalum, or film dielectric capacitors are good choices for AC-coupling capacitors. Capacitors with high-voltage coefficients, such as ceramics (non-COG dielectrics), can result in increased distortion at low frequencies.

#### **Charge-Pump Capacitor Selection**

Use capacitors with an ESR less than  $50m\Omega$  for optimum performance. Low-ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric.

#### Flying Capacitor (C1)

The value of the flying capacitor (C1) affects the load regulation and output resistance of the charge pump. A C1 value that is too small degrades the device's ability

to provide sufficient current drive. Increasing the value of C1 improves load regulation and reduces the chargepump output resistance to an extent. Above  $1\mu$ F, the onresistance of the switches and the ESR of C1 and C2 dominate. A 4.7 $\mu$ F capacitor is recommended.

#### Hold Capacitor (C2)

The output capacitor value and ESR directly affect the ripple at PVss. Increasing C2 reduces output ripple. Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. A  $10\mu$ F capacitor is recommended.

#### Charge-Pump Frequency Set Resistor (RFS)

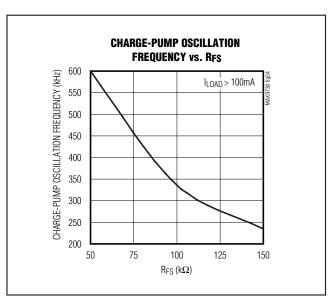

The charge pump operates in two modes. When the charge pump is loaded below 100mA, it operates in a slow mode where the oscillation frequency is reduced to 1/4 of its normal operating frequency. Once loaded, the charge-pump oscillation frequency returns to normal operation. In applications where the design may be sensitive to the operating charge-pump oscillation frequency, the value of the external resistor RFS can be changed to adjust the charge-pump oscillation frequency (see Figure 4).

Figure 4. Charge-Pump Oscillation Frequency vs. RFS

#### **Thermal Considerations**

Class G amplifiers provide much better efficiency and thermal performance than a comparable Class AB amplifier. However, the system's thermal performance must be considered with realistic expectations and include consideration of many parameters. This section examines Class G amplifiers using general examples to illustrate good design practices.

#### **TQFN** Considerations

The exposed pad is the primary route of keeping heat away from the IC. With a bottom-side exposed pad, the PCB and its copper become the primary heatsink for the Class G amplifier. Solder the exposed pad to a large copper polygon that is connected to the ground plane. The copper polygon to which the exposed pad is attached should have multiple vias to the opposite side of the PCB, where they connect to GND. Make this polygon as large as possible within the system's constraints.

## \_WLP Applications Information

For the latest application details on WLP construction, dimensions, tape carrier information, PCB techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, go to the Maxim website at www.maximic.com/ucsp for the application note, UCSP—A Wafer-Level Chip-Scale Package.

# **Typical Application Circuit/Functional Diagram**

# \_Pin Configurations

# **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 20 WLP       | W202A2+1     | <u>21-0059</u> |

| 28 TQFN      | T2844-1      | <u>21-0139</u> |

**MAX9730**

# \_\_\_Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                          | PAGES<br>CHANGED       |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 0                  | 1/07             | Initial release                                                                                                                                                      | —                      |

| 1                  | 11/07            | Include tape and reel note, edit <i>Absolute Maximum Ratings</i> , update TQFN package outline                                                                       | 1, 2,12, 13            |

| 2                  | 12/07            | Update Electrical Characteristics table                                                                                                                              | 3                      |

| 3                  | 2/08             | Changed UCSP to WLP throughout data sheet including new WLP package outline, added new TOCs 8 and 19                                                                 | 1, 2, 4, 6, 10, 11, 14 |

| 4                  | 5/08             | Updated Typcial Application Circuit and fixed various errors                                                                                                         | 1–6, 10                |

| 5                  | 3/10             | Removed erroneous bullet in the <i>Features</i> section and corrected errors in the <i>Absolute Maximum Ratings</i> section and the Electrical Characteristics table | 1, 2, 3                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600