Advance Information

Tri-Band GSM GPRS 3.5 V Power Amplifier

MMM5063/D Rev. 0.2, 09/2003

## Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

## MMM5063

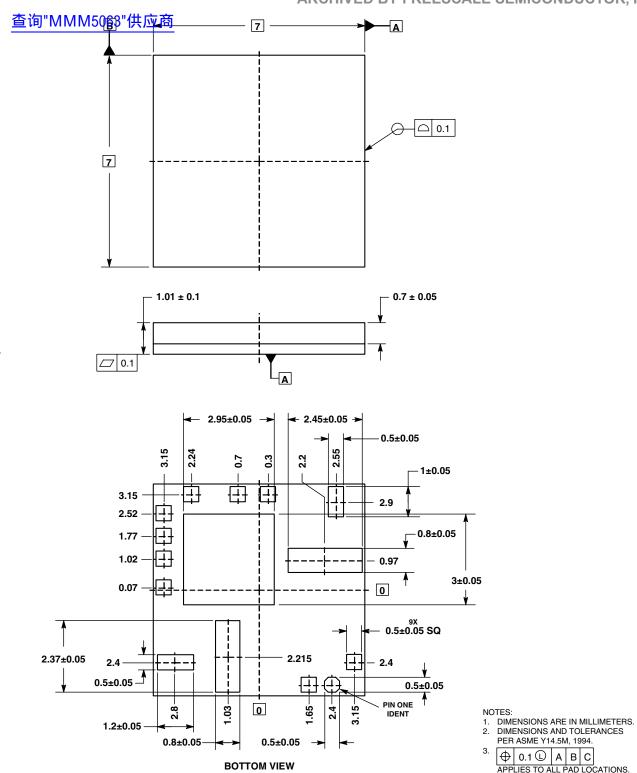

Package Information Plastic Package Case 1383 (Module, 7x7 mm)

#### **Ordering Information**

| Device  | Device Marking | Package |  |

|---------|----------------|---------|--|

| MMM5063 | See Figure 25  | Module  |  |

The MMM5063 is a tri-band single supply RF Power Amplifier for GSM900/DCS1800/ PCS1900 GPRS handheld radios. This fully integrated Power Amplifier uses a patented concept to realize the 50  $\Omega$  matching on-chip through integration of passives on the GaAs die. This allows module functionality in a very small 7 x 7 mm package and achieves best-inclass Power Amplifier performance and multi-band capability.

#### **Applications:**

- Tri-Band GSM900 DCS1800 and PCS1900

- Guaranteed for 25% Duty Cycle

#### Features:

- Single Supply Enhancement Mode GaAs MESFET Technology

- Internal 50  $\Omega$  Input/Output Matching

- High Gain Three Stage Amplifier Design

- Typical 3.5 V Characteristics:

$P_{out} = 35.2 \text{ dBm}, PAE = 53\% \text{ for GSM}$

$P_{out} = 33.8 \text{ dBm}, PAE = 44\% \text{ for DCS}$

$P_{out} = 34 \text{ dBm}, PAE = 43\% \text{ for PCS}$

- Optimized and Guaranteed for Open-Loop Power Control Applications

- Small 7 x 7 mm Package

This document contains information on a pre-production product. Specifications and Pre-production information herein are subject to change without notice. © Motorola, Inc., 2003. All rights reserved.

This device contains 26 active transistors.

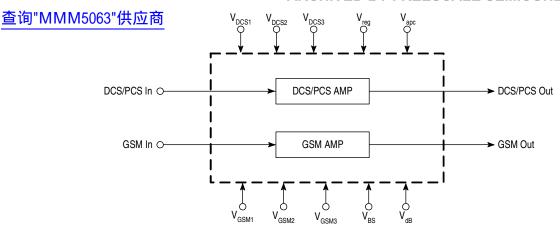

Figure 1. Simplified Block Diagram

## 1 Electrical Specifications

**Table 1. Maximum Ratings**

| Rating                                      | Symbol                                                             | Value      | Unit |

|---------------------------------------------|--------------------------------------------------------------------|------------|------|

| Supply Voltage                              | V <sub>GSM1,2,3</sub> ,<br>V <sub>DCS1,2,3</sub> , V <sub>dB</sub> | 6.0        | V    |

| RF Input Power                              | GSM IN,<br>DCS/PCS IN                                              | 11         | dBm  |

| RF Output Power GSM Section DCS/PCS Section | GSM OUT<br>DCS/PCS OUT                                             | 38<br>36   | dBm  |

| Operating Case Temperature Range            | T <sub>C</sub>                                                     | -35 to 100 | °C   |

| Storage Temperature Range                   | T <sub>stg</sub>                                                   | -55 to 150 | °C   |

| Die Temperature                             | TJ                                                                 | 150        | °C   |

NOTES: 1. Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics or Recommended Operating Conditions tables.

ESD (electrostatic discharge) immunity meets Human Body Model (HBM) ≤150 V and Machine Model (MM) ≤50 V. Additional ESD data available upon request.

<sup>3.</sup> Meets Moisture Sensitivity Level (MSL) 3. See Figure 25 on page 17 for additional details.

# Freescale Semiconductor, Inc Electrical Specifications

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005**

## 查询"MMM5063"供应商

## **Table 2. Recommended Operating Conditions**

| Characteristic        | Symbol                                           | Min  | Тур | Max | Unit |

|-----------------------|--------------------------------------------------|------|-----|-----|------|

| Drain Supply Voltage  | V <sub>GSM1,2,3</sub> ,<br>V <sub>DCS1,2,3</sub> | 2.7  | -   | 5.5 | V    |

| Bias Supply Voltage   | $V_{dB}$                                         | 2.7  | -   | 5.5 | V    |

| Regulated Voltage     | V <sub>REG</sub>                                 | 2.5  | 2.8 | 3.0 | V    |

| Power Control Voltage | V <sub>apc</sub>                                 | 0    | 1.8 | 2.8 | V    |

| Band Select           | V <sub>BS</sub>                                  | 0    | 2.8 | 3.0 | V    |

| Input Power GSM       | GSM IN                                           | -1.0 | -   | 8.0 | dBm  |

| Input Power DCS/PCS   | DCS/PCS<br>IN                                    | 2.0  | -   | 10  | dBm  |

#### **Table 3. Control Requirements**

| Characteristic                                               | Symbol           | Min      | Тур  | Max | Unit |

|--------------------------------------------------------------|------------------|----------|------|-----|------|

| Current for V <sub>reg</sub> @ 2.8 V                         | I <sub>reg</sub> | -        | 7.7  | 10  | mA   |

| Band Select Low Band Enable Voltage High Band Enable Voltage | $V_{BS}$         | 2.2<br>0 | 2.8  | 0.3 | ٧    |

| Current for V <sub>BS</sub> = 2.8 V                          | I <sub>BS</sub>  | -        | 0.76 | 1.0 | mA   |

**Table 4. Electrical Characteristics**

(Peak measurement at 25% duty cycle, 4.6 ms period,  $T_A = 25^{\circ}C$ , unless otherwise noted.)

| Characteristic                                                                                            | Symbol                                                                                                                                                                                           | Min  | Тур        | Max        | Unit |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------------|------|--|--|--|

| <b>GSM 900 Section</b> (P <sub>in</sub> = -1.0 dBm, V <sub>GSM1,2,3</sub> = 3.5 V pulse                   | <b>GSM 900 Section</b> (P <sub>in</sub> = -1.0 dBm, V <sub>GSM1,2,3</sub> = 3.5 V pulsed, V <sub>dB</sub> = 3.5 V, V <sub>REG</sub> = V <sub>BS</sub> = 2.8 V, V <sub>ramp</sub> = 1.8 V pulsed) |      |            |            |      |  |  |  |

| Frequency Range                                                                                           | BW                                                                                                                                                                                               | 880  | -          | 915        | MHz  |  |  |  |

| Output Power                                                                                              | P <sub>out</sub>                                                                                                                                                                                 | 34.2 | 35.2       | -          | dBm  |  |  |  |

| Power Added Efficiency                                                                                    | PAE                                                                                                                                                                                              | 48   | 53         | -          | %    |  |  |  |

| Output Power @ Low Voltage (V <sub>GSM1,2,3</sub> = 2.8 V pulsed, V <sub>dB</sub> = 2.8 V)                | P <sub>out</sub>                                                                                                                                                                                 | 32.5 | 33.4       | -          | dBm  |  |  |  |

| Power Added Efficiency @ Low Voltage ( $V_{GSM1,2,3} = 2.8 \text{ V pulsed}$ , $V_{dB} = 2.8 \text{ V}$ ) | PAE                                                                                                                                                                                              | 48   | 54         | -          | %    |  |  |  |

| Harmonic Output 2f <sub>o</sub> ≥3f <sub>o</sub>                                                          |                                                                                                                                                                                                  | -    | -37<br>-60 | -33<br>-45 | dBc  |  |  |  |

#### Freescale Semiconductor, Inc. **Electrical Specifications**

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

**Table 4. Electrical Characteristics (Continued)**

查询"MMM5063"供应商 (Peak measurement at 25% duty cycle, 4.6 ms period, T<sub>A</sub> = 25°C, unless otherwise noted.)

| Characteristic                                                                                                                                               | Symbol            | Min                                                     | Тур        | Max        | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------|------------|------------|------|

| Second Harmonic Leakage at DCS Output (Crosstalk isolation)                                                                                                  |                   | -                                                       | -28        | -15        | dBm  |

| Input Return Loss                                                                                                                                            | S <sub>11</sub>   | -                                                       | 10         | -          | dB   |

| Output Power Isolation (V <sub>ramp</sub> = 0 V, V <sub>GSM1,2,3</sub> = 0 V)                                                                                | P <sub>off</sub>  | -                                                       | -45        | -40        | dBm  |

| Noise Power in Rx Band @ $P_{in}$ = -1.0 dBm (100 kHz measurement bandwidth) @ $f_{o}$ + 10 MHz ( $f_{o}$ = 915 MHz) @ $f_{o}$ + 20 MHz ( $f_{o}$ = 915 MHz) | NP                | -                                                       | -80<br>-81 |            | dBm  |

| Noise Power in Rx Band @ $P_{in}$ = 6.0 dBm (100 kHz measurement bandwidth) @ $f_o$ + 10 MHz ( $f_o$ = 915 MHz) @ $f_o$ + 20 MHz ( $f_o$ = 915 MHz)          | NP                | -                                                       | -84<br>-86 | -77<br>-81 | dBm  |

| Stability-Spurious Output (P <sub>out</sub> = 5.0 to 35 dBm, Load VSWR = 6:1 all Phase Angles, Adjust V <sub>ramp</sub> for specified power)                 | P <sub>spur</sub> | -                                                       | -          | -60        | dBc  |

| Load Mismatch Stress (P <sub>out</sub> = 5.0 to 35 dBm, Load VSWR = 10:1 all phase angles, 5 seconds, Adjust V <sub>ramp</sub> for specified power)          |                   | No Degradation in Output Power<br>Before and After Test |            |            | ower |

**DCS Section**( $P_{in} = 2.0 \text{ dBm}, V_{DCS1,2,3} = 3.5 \text{ V} \text{ pulsed}, V_{dB} = 3.5 \text{ V}, V_{REG} = 2.8 \text{ V}, V_{ramp} = 1.8 \text{ V} \text{ pulsed}, V_{BS} = 0 \text{ V})$

| Frequency Range                                                                                                                            | BW                | 1710 | -          | 1785       | MHz |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------------|------------|-----|

| Output Power                                                                                                                               | P <sub>out</sub>  | 32.5 | 33.8       | -          | dBm |

| Power Added Efficiency                                                                                                                     | PAE               | 38   | 44         | -          | %   |

| Output Power @ Low Voltage (V <sub>DCS1,2,3</sub> = 2.8 V pulsed, V <sub>dB</sub> = 2.8 V)                                                 | P <sub>out</sub>  | 31   | 32         | -          | dBm |

| Power Added Efficiency @ Low Voltage (V <sub>DCS1,2,3</sub> = 2.8 V pulsed, V <sub>dB</sub> = 2.8 V)                                       | PAE               | 38   | 45         | -          | %   |

| Harmonic Output 2f <sub>o</sub> ≥3f <sub>o</sub>                                                                                           |                   | -    | -65<br>-50 | -45<br>-45 | dBc |

| Input Return Loss                                                                                                                          | S <sub>11</sub>   | -    | 9.0        | -          | dB  |

| Output Power Isolation (V <sub>ramp</sub> = 0 V, V <sub>DCS1,2,3</sub> = 0 V)                                                              | P <sub>off</sub>  | -    | -40        | -35        | dBm |

| Noise Power in Rx Band @ $P_{in}$ = 2.0 dBm @ $f_{o}$ + 20 MHz ( $f_{o}$ = 1785 MHz) (100 kHz measurement bandwidth)                       | NP                | -    | -78        | -75        | dBm |

| Stability-Spurious Output (P <sub>out</sub> = 0 to 33 dBm, Load VSWR = 6:1 all Phase Angles, Adjust V <sub>ramp</sub> for specified power) | P <sub>spur</sub> | -    | -          | -60        | dBc |

# Freescale Semiconductor, Inc Electrical Specifications

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

#### **Table 4. Electrical Characteristics (Continued)**

查询"MMM5063"供应商 (Peak measurement at 25% duty cycle, 4.6 ms period, T<sub>A</sub> = 25°C, unless otherwise noted.)

| Characteristic                                                                                                                                    | Symbol | Min                                                     | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------|-----|------|------|

| Load Mismatch Stress (P <sub>out</sub> = 0 to 33 dBm, Load VSWR = 10:1 all phase angles, 5 seconds, Adjust V <sub>ramp</sub> for specified power) |        | No Degradation in Output Power<br>Before and After Test |     | ower |      |

**PCS Section**( $P_{in} = 3.0 \text{ dBm}$ ,  $V_{DCS1,2,3} = 3.5 \text{ V}$  pulsed,  $V_{dB} = 3.5 \text{ V}$ ,  $V_{REG} = 2.8 \text{ V}$ ,  $V_{ramp} = 1.8 \text{ V}$  pulsed,  $V_{BS} = 0 \text{ V}$ )

| 1 00 000 1011(1    1 010 02111, 1 DCS1,2,3 010 1 Paisou, 1 (                                                                         | ID OIG 1, THE     | g =.0 ., .                                              | ramp       | , pa.ooa, ., | 55 0 1/ |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------|------------|--------------|---------|

| Frequency Range                                                                                                                      | BW                | 1850                                                    | -          | 1910         | MHz     |

| Output Power                                                                                                                         | P <sub>out</sub>  | 32.5                                                    | 34         | -            | dBm     |

| Power Added Efficiency                                                                                                               | PAE               | 37                                                      | 43         | -            | %       |

| Output Power @ Low Voltage ( $V_{DCS1,2,3} = 2.8 \text{ V}$ pulsed, $V_{dB} = 2.8 \text{ V}$ )                                       | P <sub>out</sub>  | 31                                                      | 32         | -            | dBm     |

| Power Added Efficiency @ Low Voltage (V <sub>DCS1,2,3</sub> = 2.8 V pulsed, V <sub>dB</sub> = 2.8 V)                                 | PAE               | 37                                                      | 43         | -            | %       |

| Harmonic Output 2f <sub>o</sub> ≥3f <sub>o</sub>                                                                                     |                   | -                                                       | -65<br>-50 | -45<br>-45   | dBc     |

| Input Return Loss                                                                                                                    | S <sub>11</sub>   | -                                                       | 5.0        | -            | dB      |

| Output Power Isolation (V <sub>ramp</sub> = 0 V, V <sub>DCS1,2,3</sub> = 0 V)                                                        | P <sub>off</sub>  | -                                                       | -35        | -32          | dBm     |

| Noise Power in Rx Band @ $P_{in}$ = 3.0 dBm @ $f_{o}$ + 20 MHz ( $f_{o}$ = 1910 MHz) (100 kHz measurement bandwidth)                 | NP                | -                                                       | -78        | -75          | dBm     |

| Stability-Spurious Output ( $P_{out}$ = 0 to 33 dBm, Load VSWR = 6:1 all Phase Angles, Adjust $V_{ramp}$ for specified power)        | P <sub>spur</sub> | -                                                       | -          | -60          | dBc     |

| Load Mismatch Stress ( $P_{out}$ = 0 to 33 dBm, Load VSWR = 10:1 all phase angles, 5 seconds, Adjust $V_{ramp}$ for specified power) |                   | No Degradation in Output Power<br>Before and After Test |            |              |         |

|                                                                                                                                      |                   |                                                         |            |              |         |

ARCHIVED BY

Freescale Semiconductor, Inc.

# Typical Performance Characteristics Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

# 查名"Mypical Performance Characteristics

## 2.1 **GSM**

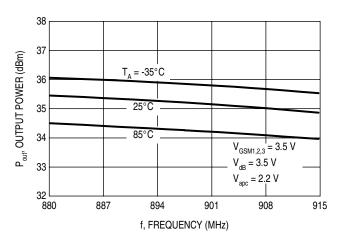

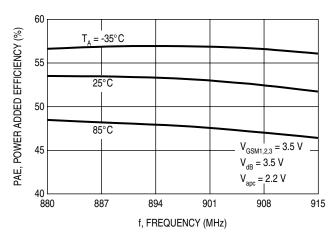

Figure 2. Output Power versus Frequency

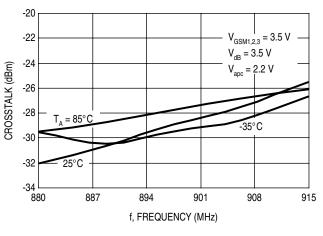

Figure 4. Crosstalk versus Frequency

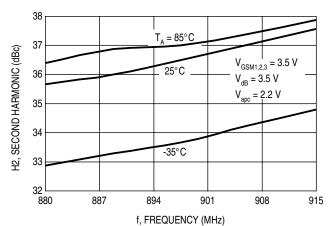

Figure 5. Second Harmonic Output versus Frequency

# Freescale Semiconductor, Inc. Typical Performance Characteristics

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

## 查询"MMM5063"供应商

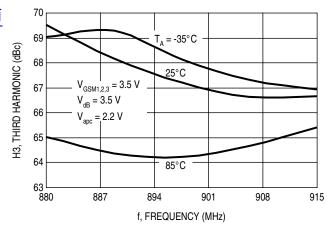

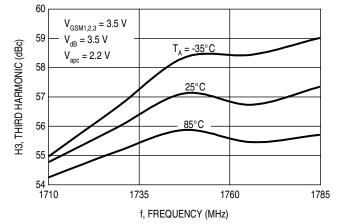

Figure 6. Third Harmonic Output versus Frequency

## 2.2 DCS

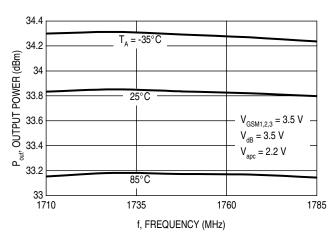

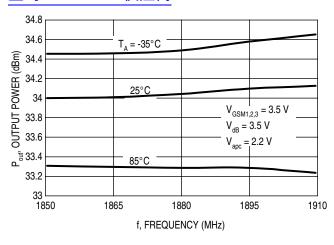

Figure 7. Output Power versus Frequency

7<sub>A</sub> = 85°C V<sub>GSM1,2,3</sub> = 3.5 V V<sub>dB</sub> = 3.5 V V<sub>apc</sub> = 2.2 V

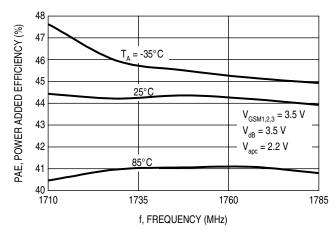

Figure 8. Power Added Efficiency versus Frequency

Figure 9. Second Harmonic Output versus Frequency

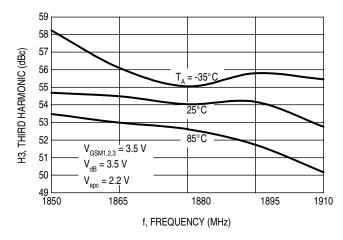

Figure 10. Third Harmonic Output versus Frequency

## 查**看**3MMM5863"供应商

46 PAE, POWER ADDED EFFICIENCY (%)  $T_{\Lambda} = -35^{\circ}C$ 25°C 42 40 85°C  $V_{GSM1,2,3} = 3.5 \text{ V}$ 38  $V_{dB} = 3.5 \text{ V}$  $V_{apc} = 2.2 V_{apc}$ 36 1850 1865 1880 1895 1910 f, FREQUENCY (MHz)

Figure 11. Output Power versus Frequency

70  $T_{\Lambda} = 85^{\circ}C$ 69 H2, SECOND HARMONIC (dBc) 25°C -35°C 67  $V_{GSM1,2,3} = 3.5 \text{ V}$ 66  $V_{dB} = 3.5 \text{ V}$ 65 = 2.2 V64 L 1850 1865 1880 1895 1910 f, FREQUENCY (MHz)

Figure 13. Second Harmonic Output versus Frequency

Figure 12. Power Added Efficiency versus Frequency

Figure 14. Third Harmonic Output versus Frequency

# Freescale Semiconductor, Inc. Contact Descriptions and Connections

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

## 查备" Contact Descriptions and Connections

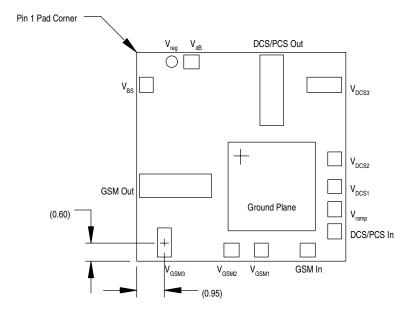

**Table 5. Contact Function Description**

| Pin | Symbol            | Description                                                                                                                                                    |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>reg</sub>  | Regulated dc voltage for bias circuit                                                                                                                          |

| 2   | V <sub>dB</sub>   | DC supply voltage for active bias circuits connected to the battery                                                                                            |

| 3   | DCS/PCS Out       | DCS/PCS RF output                                                                                                                                              |

| 4   | V <sub>DCS3</sub> | DCS/PCS DC supply voltage for 3rd stage                                                                                                                        |

| 5   | V <sub>DCS2</sub> | DCS/PCS DC supply voltage for 2nd stage                                                                                                                        |

| 6   | V <sub>DCS1</sub> | DCS/PCS DC supply voltage for 1st stage                                                                                                                        |

| 7   | V <sub>apc</sub>  | Power control for both line-ups (V <sub>apc</sub> = 0 V, P <sub>out</sub> = P <sub>off</sub> , V <sub>apc</sub> = 1.8 V, P <sub>out</sub> = P <sub>max</sub> ) |

| 8   | DCS/PCS In        | DCS/PCS RF input                                                                                                                                               |

| 9   | GSM In            | GSM RF input                                                                                                                                                   |

| 10  | V <sub>GSM1</sub> | GSM DC supply voltage for 1st stage                                                                                                                            |

| 11  | V <sub>GSM2</sub> | GSM DC supply voltage for 2nd stage                                                                                                                            |

| 12  | V <sub>GSM3</sub> | GSM DC supply voltage for 3rd stage                                                                                                                            |

| 13  | GSM Out           | GSM RF output                                                                                                                                                  |

| 14  | V <sub>BS</sub>   | Band selection between GSM and DCS/PCS                                                                                                                         |

**NOTE:** For optimum performance  $V_{GSM1}$  and  $V_{GSM2}$ , as well as  $V_{DCS1}$  and  $V_{DCS2}$ , must be strapped together on the application demobard.

Figure 15. Contact Connections

(Bottom View)

## 查例"Mpplication Information

#### 4.1 Power Control Considerations

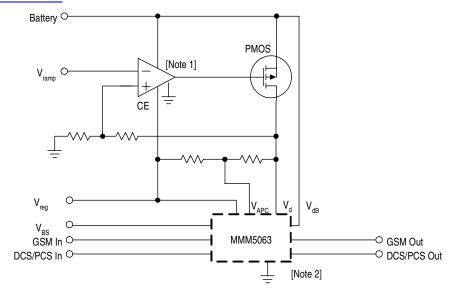

The MMM5063 is designed for open loop (drain control) applications. A PMOS FET is used to switch the MMM5063 drain and vary the supply voltage from 0 to the battery voltage setting ( $V_{bat}$ ). The simplified concept schematic (see Figure 22) describes the application circuit used to control the device through the drain voltage.

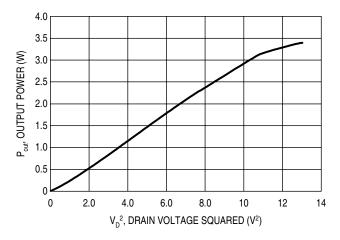

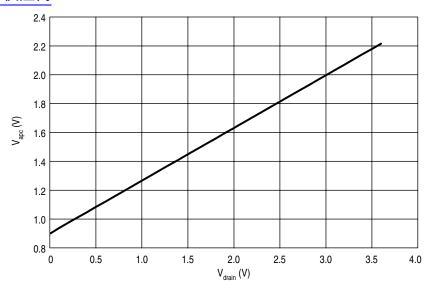

A drain control provides a linear transfer function which is repeatable versus control voltage (see Figure 16).

Figure 16. Output Power versus Drain Voltage

## 4.2 GSM Second Harmonic (H2) Trap Circuitry

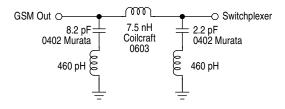

When transmitting in GSM saturated mode, the second harmonic is naturally present at the RF output of the PA and reaches the antenna after additional filtering in the front-end. ETSI specifies that harmonic level cannot exceed -36 dBm. In order to improve H2 rejection in low Band (GSM), an H2 trap has been developed. The topology is based on a Low Pass  $\pi$  Cell Filter (see Figure 17) where the first shunt capacitor is actually part of the PA output match.

Figure 17. Low Pass Filter

This circuit reduces H2 level by 7 to 8 dB with low in-band insertion losses (mainly due to the series inductor). Moreover, this structure can be used to match Power amplifier module output to the switchplexer.

# Freescale Semiconductor, Inc. Application Information

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

## 查得3MApplication Schematics and Printed Circuit Boards

NOTES: 1. Op/Amp is either external (with an enable pin CE) or in an ASIC.

2. The MMM5063 requires 4 to 6 RF/LF decoupling capacitors (not shown).

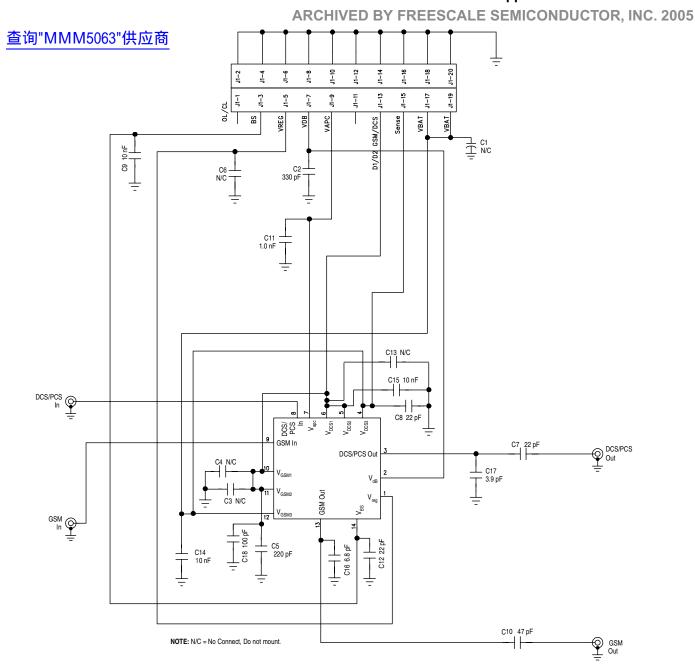

Figure 18. Open Loop Control Application Schematic

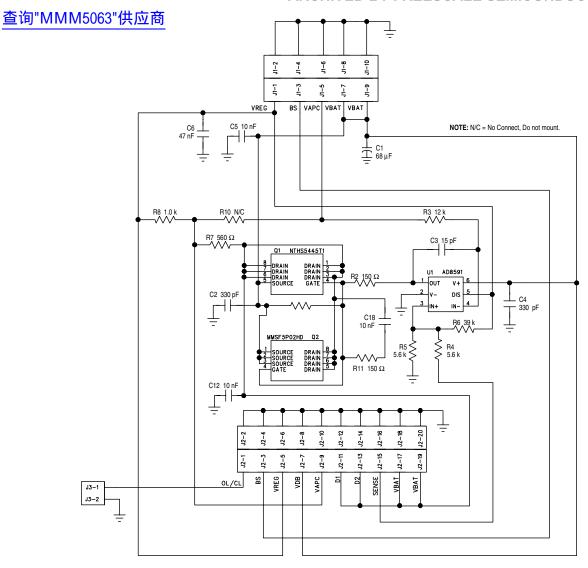

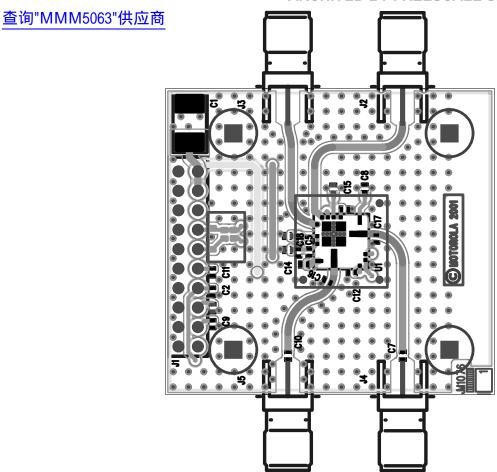

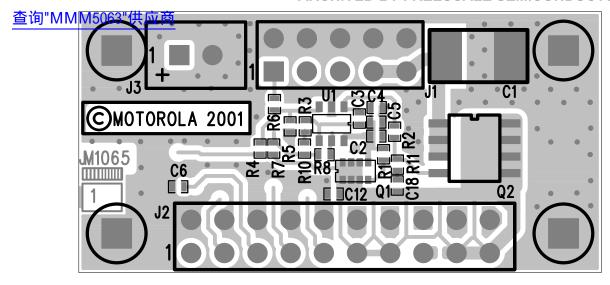

Figure 18 represents the complete Power Amplifier implementation including the MMM5063 Amplifier Module and the Control Circuitry. This functionality is realized with two separate printed circuit boards; the PA Evaluation Circuit with schematic shown in Figure 21 and PCB Layout shown in Figure 23, and the Power Amplifier Control Loop with schematic shown in Figure 22 and PCB Layout shown in Figure 24.

The PA Evaluation Circuit is straightfoward and, due to the MMM5063's high level of integration, requires only a few passive components around the package. These components are mainly de-coupling capacitors.

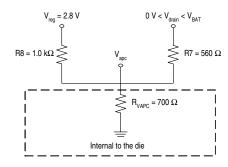

The Power Amplifier Control Loop is based on an operational amplifier driving a PMOS transistor. The PMOS device functions as a linear drain voltage regulator controlled by  $V_{ramp}$  with a typical gain of 2 which is set through the resistive divider R4 and R5 as shown in Figure 22. To control output power through the drain,  $V_{apc}$  must be indexed to the drain voltage to prevent the PA Section from drawing excessive current especially at low output power. Nevertheless,  $V_{apc}$  should stay above 0.8 V to provide sufficient gain for the line-up. Figure 19 describes the application circuit used to control  $V_{apc}$  through the drain voltage. It uses  $V_{reg}$  to pre-position  $V_{apc}$  at 0.9 V and add a voltage which is dependent on the drain Voltage.

Figure 19.

## **Application Information**

## Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

查询"MM9063"供应费 0.9 V while R7 sets the V<sub>apc</sub> slope. V<sub>apc</sub> versus V<sub>drain</sub> is shown in the Figure 20.

Figure 20. V<sub>apc</sub> versus V<sub>drain</sub>

It is possible that the Power Control DAC output voltage can be in the 200 mV to 2.0 V range. This raises a concern for the MMM5063 ramp control voltage ( $V_{ramp}$ ) which must start at 0 V to get enough output power dynamic range. To overcome this limitation, a resistor (R6 in Figure 22) is used to set an additional offset (200 mV with R6 = 39 k $\Omega$ ). This residual voltage is then subtracted the DAC output voltage through the differential Operational Amplifier.

# Freescale Semiconductor, Inc. Application Information

Figure 21. PA Evaluation Circuit

Figure 22. Power Amplifier Control Loop

# Freescale Semiconductor, Inc. Application Information

Figure 23. PA Evaluation Circuit PCB

Table 6. PA Evaluation Circuit PCB Bill of Materials

| Reference           | Value              | Part Number    | Manufacturer |

|---------------------|--------------------|----------------|--------------|

| C1, C3, C4, C6, C13 | N/C - Do not mount |                |              |

| C2                  | 330 pF             | GRM36COG330J50 | Murata       |

| C5                  | 220 pF             | GRM36X7R221K50 | Murata       |

| C7, C8, C12         | 22 pF              | GRM36COG220J50 | Murata       |

| C9, C14, C15        | 10 nF              | GRM36X7R103K25 | Murata       |

| C10                 | 47 pF              | GRM36COG470J50 | Murata       |

| C11                 | 1.0 nF             | GRM36X7R102K25 | Murata       |

| C16                 | 6.8 pF             | GRM36COG6R8J50 | Murata       |

| C17                 | 3.9 pF             | GRM36COG3R9J50 | Murata       |

| C18                 | 100 nF             | GRM36X7R104K25 | Murata       |

| J2, J3, J4, J5      | 50 Ω               | 142-0711-821   | Johnson      |

Figure 24. Power Amplifier Control Loop PCB

Table 7. Power Amplifier Control Loop PCB Bill of Materials

| Reference    | Value              | Part Number       | Manufacturer     |

|--------------|--------------------|-------------------|------------------|

| C1           | 68 μF              | 293D685X9020C     | Sprague          |

| C2           | 330 pF             | GRM36COG330J50    | Murata           |

| C3           | 15 pF              | GRM36COG150J50    | Murata           |

| C4           | 330 pF             | GRM36x7R331K50    | Murata           |

| C5, C12, C18 | 10 nF              | GRM36X7R103K25    | Murata           |

| C6           | 47 nF              | GRM36X7R473K10    | Murata           |

| J1, J2, J3   | DC connector       |                   |                  |

| Q1           | Power MOSFET       | NTHS5445T         | ON Semiconductor |

| Q2           | N/C - Do not mount |                   |                  |

| R1, R8       | 1.0 k              | CRG0402 5% 1 kO   | NEOHM            |

| R2           | 150 Ω              | CRG0402 5% 150 O  | NEOHM            |

| R3           | 12 k               | CRG0402 5% 12 kO  | NEOHM            |

| R4, R5       | 5.6 k              | CRG0402 5% 5.6 kO | NEOHM            |

| R6, R10      | N/C - Do not mount |                   |                  |

| R7           | 560 Ω              | CRG0402 5% 560 O  | NEOHM            |

| R11          | 100 Ω              | CRG0402 5% 100 O  | NEOHM            |

| U1           | CMOS Op Amp        | AD8591            | Analog Devices   |

# Freescale Semiconductor, Inc. Packaging Information

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

## 查看"Mackaging Information

#### Shipping, Packaging and Marking Information

Tape Width: 16.0 mm

Tape Pitch 12 mm (part to part) Reel Diameter: 330 mm (13 in)

Component Orientation: Parts are to be orientated with pin 1 side closest to the tape's round sprocket holes on the tape's trailing edge.

**Dry Pack:** This device meets Moisture Sensitiviy Level (MSL) 3. Parts will be shipped in Dry Pack. Parts must be stored at 30°C and 60% relative humidity with time out of dry pack not to exceed 168 hours.

In the event that parts are not handled or stored within these limits, one of the following dry out procedures must be completed prior to reflow:

1) 40°C Dry Out: Bake devices at 40°C  $\leq$   $T_A$   $\leq$  45°C, 5% Relative Humidity for at least 192 hours.

2) Room Temperature Dry Out: Store devices at less than 20% Relative Humidity for at least 500 hours.

#### Marking:

1st line: Motorola Logo

2nd Line: Partnumber coded on 7 characters

3rd Line: Wafer lot number (coded on 6 characters) followed by wafer num-

ber (coded on 3 digits)

4th Line: Assy site code (on 1 or 2 characters), followed by Wafer Lot Num-

ber (coded on 1 or 2 characters), followed by Year

(on 2 digits) and Workweek (on 2 digits).

Tape & Reel Orientation (Top View)

Figure 25. Packaging Information

Figure 26. Outline Dimensions for 7x7 mm Module (Case 1383-02, Issue A)

## Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

查询"MMM5063"供应商

**NOTES**

HOME PAGE:

## Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

查询"MMM5063"供应商

# HOW TO REACH US: "USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217 1-303-675-2140 or 1-800-441-2447 JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu Minato-ku, Tokyo 106-8573 Japan 81-3-3440-3569 ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334 TECHNICAL INFORMATION CENTER:

√http://www.motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2003

MMM5063/D