# 2.5 $\Omega$ Quad SPST Switches in Chip Scale Package

# ADG781/ADG782/ADG783

#### **FEATURES**

1.8 V to 5.5 V Single Supply Low On Resistance (2.5  $\Omega$  Typ) Low On-Resistance Flatness (0.5  $\Omega$ ) -3 dB Bandwidth > 200 MHz Rail-to-Rail Operation 20-Lead 4 mm × 4 mm Chip Scale Package **Fast Switching Times**  $t_{ON} = 16 \text{ ns}$

$t_{OFF} = 10 \text{ ns}$

Typical Power Consumption (< 0.01 μW)

**TTL/CMOS Compatible**

For Functionally Equivalent Devices in 16-Lead TSSOP and SOIC Packages, See ADG711/ADG712/ADG713

#### **APPLICATIONS**

**Battery Powered Systems Communication Systems** Sample Hold Systems **Audio Signal Routing** Video Switching Mechanical Reed Relay Replacement

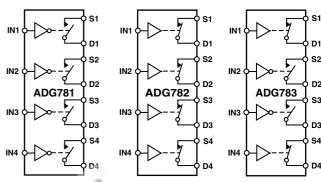

### **FUNCTIONAL BLOCK DIAGRAMS**

SWITCHES SHOWN FOR A LOGIC "1" INPUT

#### **GENERAL DESCRIPTION**

The ADG781, ADG782, and ADG783 are monolithic CMOS devices containing four independently selectable switches. These switches are designed on an advanced submicron process that provides low power dissipation and high switching speed, low on resistance, low leakage currents and high bandwidth.

They are designed to operate from a single 1.8 V to 5.5 V supply, making them ideal for use in battery powered instruments and with the new generation of DACs and ADCs from Analog Devices. Fast switching times and high bandwidth make the part suitable for video signal switching.

The ADG781, ADG782, and ADG783 contain four independent single-pole/single throw (SPST) switches. The ADG781 and ADG782 differ only in that the digital control logic is inverted. The ADG781 switches are turned on with a logic low on the appropriate control input, while a logic high is required to turn on the switches of the ADG782. The ADG783 contains two switches whose digital control logic is similar to the ADG781, while the logic is inverted on the other two switches.

Each switch conducts equally well in both directions when ON. The ADG783 exhibits break-before-make switching action.

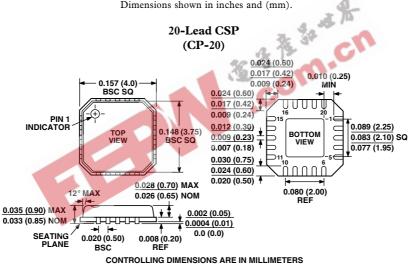

The ADG781/ADG782/ADG783 are available in 20-lead chip scale packages.

### PRODUCT HIGHLIGHTS

- 1. 20-Lead 4 mm × 4 mm Chip Scale Package (CSP).

- 2. 1.8 V to 5.5 V Single Supply Operation. The ADG781, ADG782, and ADG783 offer high performance and are fully specified and guaranteed with 3 V and 5 V supply

- 3. Very Low  $R_{ON}$  (4.5  $\Omega$  max at 5 V, 8  $\Omega$  max at 3 V). At supply voltage of 1.8 V,  $R_{ON}$  is typically 35  $\Omega$  over the temperature

- 4. Low On-Resistance Flatness.

- 5. -3 dB Bandwidth >200 MHz.

- 6. Low Power Dissipation. CMOS construction ensures low power dissipation.

- 7. Fast t<sub>ON</sub>/t<sub>OFF</sub>.

- 8. Break-Before-Make Switching. This prevents channel shorting when the switches are configured as a multiplexer (ADG783

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703

© Analog Devices, Inc., 2002

# ADG781/ADG782/ADG783—SPECIFICATIONS $(V_{DD} = 5 \text{ V} \pm 10\%, \text{ GND} = 0 \text{ V}. \text{ All specifications } -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.})$

|                                                 | B Ve  |                                              |              |                                                                                     |

|-------------------------------------------------|-------|----------------------------------------------|--------------|-------------------------------------------------------------------------------------|

| Parameter                                       | +25°C | -40°C to<br>+85°C                            | Unit         | Test Conditions/Comments                                                            |

| ANALOG SWITCH                                   |       |                                              |              |                                                                                     |

| Analog Signal Range                             |       | $0~\mathrm{V}$ to $\mathrm{V}_{\mathrm{DD}}$ | V            |                                                                                     |

| On Resistance (R <sub>ON</sub> )                | 2.5   |                                              | Ω typ        | $V_{S} = 0 \text{ V to } V_{DD}, I_{S} = -10 \text{ mA};$                           |

|                                                 | 4     | 4.5                                          | $\Omega$ max | Test Circuit 1                                                                      |

| On-Resistance Match Between                     |       | 0.05                                         | Ω typ        | $V_S = 0 \text{ V to } V_{DD}, I_S = -10 \text{ mA}$                                |

| Channels ( $\Delta R_{ON}$ )                    |       | 0.4                                          | $\Omega$ max |                                                                                     |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> ) | 0.5   |                                              | Ω typ        | $V_S = 0 \text{ V to } V_{DD}, I_S = -10 \text{ mA}$                                |

|                                                 |       | 1.0                                          | Ω max        |                                                                                     |

| LEAKAGE CURRENTS                                |       |                                              |              | $V_{\rm DD} = 5.5 \text{ V};$                                                       |

| Source OFF Leakage I <sub>S</sub> (OFF)         | ±0.01 |                                              | nA typ       | $V_S = 4.5 \text{ V/1 V}, V_D = 1 \text{ V/4.5 V};$                                 |

|                                                 | ±0.1  | $\pm 0.2$                                    | nA max       | Test Circuit 2                                                                      |

| Drain OFF Leakage I <sub>D</sub> (OFF)          | ±0.01 |                                              | nA typ       | $V_S = 4.5 \text{ V/1 V}, V_D = 1 \text{ V/4.5 V};$                                 |

|                                                 | ±0.1  | $\pm 0.2$                                    | nA max       | Test Circuit 2                                                                      |

| Channel ON Leakage ID, IS (ON)                  | ±0.01 |                                              | nA typ       | $V_S = V_D = 1 \text{ V, or } 4.5 \text{ V;}$                                       |

|                                                 | ±0.1  | $\pm 0.2$                                    | nA max       | Test Circuit 3                                                                      |

| DIGITAL INPUTS                                  |       |                                              |              |                                                                                     |

| Input High Voltage, V <sub>INH</sub>            |       | 2.4                                          | V min        | 4                                                                                   |

| Input Low Voltage, V <sub>INL</sub>             |       | 0.8                                          | V max 🊜 🏓    | B 700                                                                               |

| Input Current                                   |       |                                              | 36 34        | -10                                                                                 |

| I <sub>INL</sub> or I <sub>INH</sub>            | 0.005 |                                              | μA typ       | $V_{\rm IN} = V_{\rm INL}$ or $V_{\rm INH}$                                         |

|                                                 |       | ±0.1                                         | μA max       |                                                                                     |

| DYNAMIC CHARACTERISTICS <sup>2</sup>            |       |                                              | ~0"          |                                                                                     |

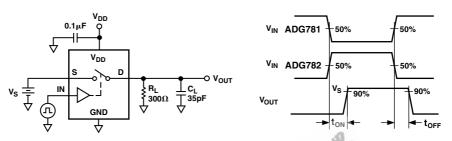

| $t_{ON}$                                        | 11    |                                              | ns typ       | $R_L = 300 \Omega, C_L = 35 pF,$                                                    |

|                                                 |       | 16                                           | ns max       | $V_S = 3 V$ ; Test Circuit 4                                                        |

| $t_{\mathrm{OFF}}$                              | 6     |                                              | ns typ       | $R_{L} = 300 \Omega, C_{L} = 35 pF,$                                                |

| 011                                             |       | 10                                           | ns max       | V <sub>S</sub> = 3 V; Test Circuit 4                                                |

| Break-Before-Make Time Delay, tD                | 6     |                                              | ns typ       | $R_L = 300 \Omega, C_L = 35 pF,$                                                    |

| (ADG783 Only)                                   |       | 1                                            | ns min       | $V_{S1} = V_{S2} = 3 \text{ V}$ ; Test Circuit 5                                    |

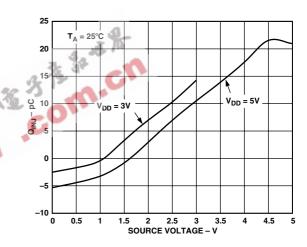

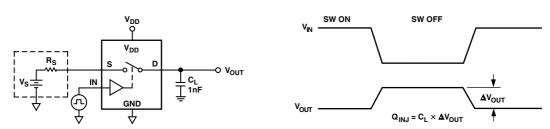

| Charge Injection                                | 3     |                                              | pC typ       | $V_S = 2 V; R_S = 0 \Omega, C_L = 1 nF;$                                            |

|                                                 |       |                                              |              | Test Circuit 6                                                                      |

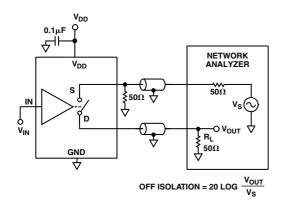

| Off Isolation                                   | -58   |                                              | dB typ       | $R_L = 50 \Omega, C_L = 5 pF, f = 10 MHz$                                           |

|                                                 | -78   |                                              | dB typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>Test Circuit 7                  |

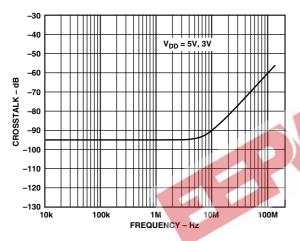

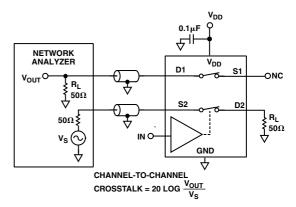

| Channel-to-Channel Crosstalk                    | -90   |                                              | dB typ       | R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = 5 pF, f = 10 MHz;<br>Test Circuit 8 |

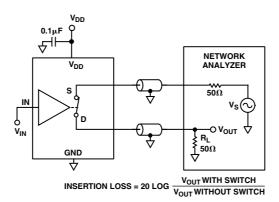

| Bandwidth –3 dB                                 | 200   |                                              | MHz typ      | R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = 5 pF; Test Circuit 9                |

| C <sub>S</sub> (OFF)                            | 10    |                                              | pF typ       | f = 1 MHz                                                                           |

| C <sub>D</sub> (OFF)                            | 10    |                                              | pF typ       | f = 1  MHz                                                                          |

| $C_D$ , $C_S$ (ON)                              | 22    |                                              | pF typ       | f = 1 MHz                                                                           |

| POWER REQUIREMENTS                              |       |                                              |              | V <sub>DD</sub> = 5.5 V                                                             |

| I <sub>DD</sub>                                 | 0.001 |                                              | μA typ       | Digital Inputs = 0 V or 5.5 V                                                       |

| -עע                                             | ""    | 1.0                                          | μA max       |                                                                                     |

Specifications subject to change without notice.

REV. A

<sup>&</sup>lt;sup>1</sup>Temperature ranges are as follows: B Version: –40°C to +85°C. <sup>2</sup>Guaranteed by design, not subject to production test.

$\label{eq:continuous} \textbf{SPECIFICATIONS}^{1} \quad \text{(V}_{DD} = 3 \text{ V} \pm 10\%, \text{ GND} = 0 \text{ V}. \text{ All specifications} -40^{\circ}\text{C to} +85^{\circ}\text{C unless otherwise noted.)}$

|                                                 | B Version |                                              |                  |                                                                              |  |

|-------------------------------------------------|-----------|----------------------------------------------|------------------|------------------------------------------------------------------------------|--|

|                                                 |           | <b>-40°C</b> to                              |                  |                                                                              |  |

| Parameter                                       | +25°C     | +85°C                                        | Unit             | Test Conditions/Comments                                                     |  |

| ANALOG SWITCH                                   |           |                                              |                  |                                                                              |  |

| Analog Signal Range                             |           | $0~\mathrm{V}$ to $\mathrm{V}_{\mathrm{DD}}$ | V                |                                                                              |  |

| On Resistance (R <sub>ON</sub> )                | 5         | 5.5                                          | Ω typ            | $V_S = 0 \text{ V to } V_{DD}, I_S = -10 \text{ mA};$                        |  |

| ( 010                                           |           | 10                                           | Ω max            | Test Circuit 1                                                               |  |

| On-Resistance Match Between                     | 0.1       |                                              | Ω typ            | $V_S = 0 \text{ V to } V_{DD}, I_S = -10 \text{ mA}$                         |  |

| Channels ( $\Delta R_{ON}$ )                    |           | 0.5                                          | Ω max            | 5 227 5                                                                      |  |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> ) |           | 2.5                                          | Ω typ            | $V_S = 0 \text{ V to } V_{DD}, I_S = -10 \text{ mA}$                         |  |

| LEAKAGE CURRENTS                                |           |                                              |                  | $V_{\rm DD} = 3.3 \text{ V};$                                                |  |

| Source OFF Leakage I <sub>S</sub> (OFF)         | ±0.01     |                                              | nA typ           | $V_S = 3 \text{ V/1 V}, V_D = 1 \text{ V/3 V};$                              |  |

| Source off Bearings is (Off)                    | ±0.1      | ±0.2                                         | nA max           | Test Circuit 2                                                               |  |

| Drain OFF Leakage I <sub>D</sub> (OFF)          | ±0.01     | ±0.2                                         | nA typ           | $V_S = 3 \text{ V/1 V}, V_D = 1 \text{ V/3 V};$                              |  |

| Zimi Oli Zemmge ip (Oli)                        | ±0.01     | ±0.2                                         | nA max           | Test Circuit 2                                                               |  |

| Channel ON Leakage ID, IS (ON)                  | ±0.01     | _0.2                                         | nA typ           | $V_S = V_D = 1 \text{ V, or } 3 \text{ V;}$                                  |  |

| Chaimer of v Dearage 15, 15 (OTV)               | ±0.1      | ±0.2                                         | nA max           | Test Circuit 3                                                               |  |

| DICUTAL INDUCE                                  |           |                                              | 4                | position .                                                                   |  |

| DIGITAL INPUTS                                  |           | 2.0                                          | 77 mate 18 /     |                                                                              |  |

| Input High Voltage, V <sub>INH</sub>            |           | 2.0<br>0.8                                   | V min<br>V max   |                                                                              |  |

| Input Low Voltage, V <sub>INL</sub>             |           | 0.8                                          | V IIIax          |                                                                              |  |

| Input Current                                   | 0.005     | 26.                                          |                  | $V_{IN} = V_{INI}$ or $V_{INH}$                                              |  |

| $I_{INL}$ or $I_{INH}$                          | 0.005     | ±0.1                                         | μΑ typ<br>μΑ max | VIN - VINL OF VINH                                                           |  |

| DYNAMIC CHARACTERISTICS <sup>2</sup>            |           | 1                                            |                  |                                                                              |  |

| $t_{ON}$                                        | 13        |                                              | ns typ           | $R_L = 300 \Omega, C_L = 35 pF,$                                             |  |

|                                                 |           | 20                                           | ns max           | $V_S = 2 V$ ; Test Circuit 4                                                 |  |

| t <sub>OFF</sub>                                | 7         |                                              | ns typ           | $R_L = 300 \Omega, C_L = 35 pF,$                                             |  |

|                                                 |           | 12                                           | ns max           | $V_S = 2 V$ ; Test Circuit 4                                                 |  |

| Break-Before-Make Time Delay, t <sub>D</sub>    | 7         |                                              | ns typ           | $R_L = 300 \Omega, C_L = 35 pF,$                                             |  |

| (ADG783 Only)                                   |           | 1                                            | ns min           | $V_{S1} = V_{S2} = 2 \text{ V}$ ; Test Circuit 5                             |  |

| Charge Injection                                | 3         |                                              | pC typ           | $V_S = 1.5 \text{ V}; R_S = 0 \Omega, C_L = 1 \text{ nF};$<br>Test Circuit 6 |  |

| Off Isolation                                   | -58       |                                              | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$                              |  |

|                                                 | -78       |                                              | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 10 \text{ MHz}$ ;            |  |

|                                                 | -70       |                                              | dB typ           | Test Circuit 7                                                               |  |

| Channel-to-Channel Crosstalk                    | -90       |                                              | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ;<br>Test Circuit 8          |  |

| Bandwidth –3 dB                                 | 200       |                                              | MHz typ          | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; Test Circuit 9                            |  |

| $C_{S}$ (OFF)                                   | 10        |                                              | pF typ           | f = 1 MHz                                                                    |  |

| $C_{\rm D}$ (OFF)                               | 10        |                                              | pF typ           | f = 1 MHz                                                                    |  |

| $C_D, C_S (ON)$                                 | 22        |                                              | pF typ           | f = 1 MHz                                                                    |  |

| POWER REQUIREMENTS                              |           |                                              |                  | $V_{\rm DD} = 3.3 \text{ V}$                                                 |  |

| I <sub>DD</sub>                                 | 0.001     |                                              | μA typ           | Digital Inputs = 0 V or 3.3 V                                                |  |

| <i>DD</i>                                       |           | 1.0                                          | μA max           |                                                                              |  |

REV. A -3-

$<sup>^{1}</sup>Temperature$  ranges are as follows: B Version:  $-40\,^{\circ}C$  to +85 $^{\circ}C.$

<sup>&</sup>lt;sup>2</sup>Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

| Lead Temperature, Soldering (10 sec) | 300°C |

|--------------------------------------|-------|

| IR Reflow (<20 sec)                  | 235°C |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

#### **ORDERING GUIDE**

| Model                  | Temperature Range                | Package Description                                  | Package Option |

|------------------------|----------------------------------|------------------------------------------------------|----------------|

| ADG781BCP<br>ADG782BCP | -40°C to +85°C<br>-40°C to +85°C | 20-Lead Chip Scale (CSP)<br>20-Lead Chip Scale (CSP) | CP-20<br>CP-20 |

| ADG783BCP              | −40°C to +85°C                   | 20-Lead Chip Scale (CSP)                             | CP-20          |

#### Table I. Truth Table (ADG781/ADG782)

| ADG781 In | ADG782 In | Switch Condition |

|-----------|-----------|------------------|

| 0         | 1         | ON               |

| 1         | 0         | OFF              |

Table II. Truth Table (ADG783)

| 0 OFF 01 | V  |

|----------|----|

| 1 ON 01  | FF |

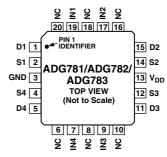

# PIN CONFIGURATION (CSP)

NC = NO CONNECT EXPOSED PAD TIED TO SUBSTRATE, GND

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADG781/ADG782/ADG783 feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

1– REV. A

<sup>&</sup>lt;sup>2</sup>Overvoltages at IN, S, or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.

#### **TERMINOLOGY**

| $V_{DD}$             | Most positive power supply potential.                                                                                       | $C_D, C_S (ON)$ | "ON" switch capacitance.                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|

| GND                  | Ground (0 V) reference.                                                                                                     | $t_{ON}$        | Delay between applying the digital control                                                                             |

| S                    | Source terminal. May be an input or output.                                                                                 |                 | input and the output switching on.                                                                                     |

| D                    | Drain terminal. May be an input or output.                                                                                  | $t_{ m OFF}$    | Delay between applying the digital control input and the output switching off.                                         |

| IN                   | Logic control input.                                                                                                        | t <sub>D</sub>  | "OFF" time or "ON" time measured                                                                                       |

| $R_{ON}$             | Ohmic resistance between D and S.                                                                                           | чD              | between the 90% points of both switches,                                                                               |

| $\Delta R_{ m ON}$   | On-resistance match between any two channels (i.e., $R_{ON}$ max and $R_{ON}$ min).                                         |                 | when switching from one address state to another (ADG783 only).                                                        |

| $R_{FLAT(ON)} \\$    | Flatness is defined as the difference between the maximum and minimum value of on resistance as measured over the specified | Crosstalk       | A measure of unwanted signal that is coupled through from one channel to another as a result of parasitic capacitance. |

|                      | analog signal range.                                                                                                        | Off Isolation   | A measure of unwanted signal coupling                                                                                  |

| I <sub>S</sub> (OFF) | Source leakage current with the switch "OFF."                                                                               |                 | through an "OFF" switch.                                                                                               |

| $I_D$ (OFF)          | Drain leakage current with the switch "OFF."                                                                                | Charge          | A measure of the glitch impulse transferred                                                                            |

| $I_D$ , $I_S$ (ON)   | Channel leakage current with the switch "ON."                                                                               | Injection       | from the digital input to the analog output                                                                            |

| $V_{D}(V_{S})$       | Analog voltage on terminals D, S.                                                                                           |                 | during switching.                                                                                                      |

| $C_{S}$ (OFF)        | "OFF" switch source capacitance.                                                                                            | On Response     | The frequency response of the "ON" switch.                                                                             |

| $C_D$ (OFF)          | "OFF" switch drain capacitance.                                                                                             | On Loss         | The loss due to the on resistance of the switch.                                                                       |

| Typical Po           | erformance Characteristics                                                                                                  | 7 7 6<br>5.5    | V <sub>DD</sub> = 5V                                                                                                   |

| 5 ——                 | V <sub>DD</sub> = 2.7V                                                                                                      | 5 ⊢             | <del></del>                                                                                                            |

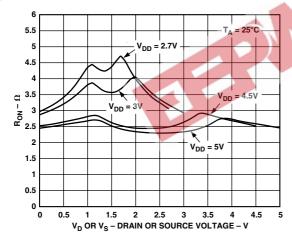

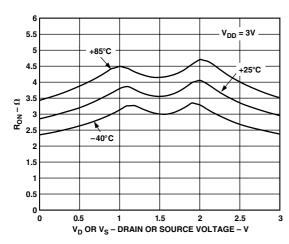

# **Typical Performance Characteristics**

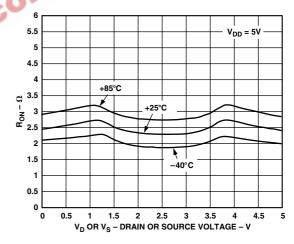

TPC 1. On Resistance as a Function of  $V_D$  ( $V_S$ )

TPC 2. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures  $V_{DD} = 3 V$

TPC 3. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures  $V_{DD} = 5 V$

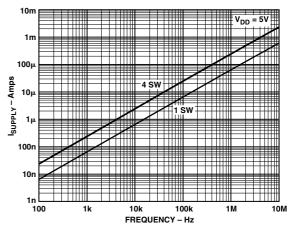

TPC 4. Supply Current vs. Input Switching Frequency

REV. A -5-

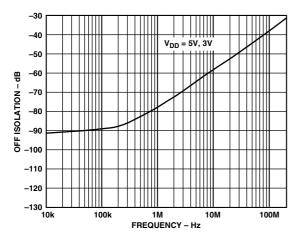

TPC 5. Off Isolation vs. Frequency

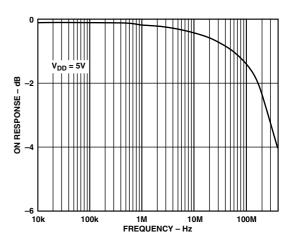

TPC 7. On Response vs. Frequency

TPC 6. Crosstalk vs. Frequency

TPC 8. Charge Injection vs. Source Voltage

#### APPLICATIONS

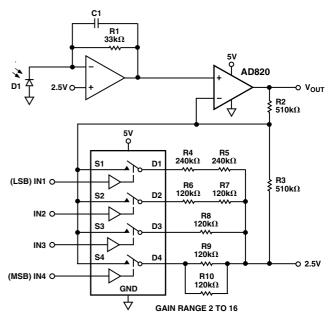

Figure 1 illustrates a photodetector circuit with programmable gain. An AD820 is used as the output operational amplifier. With the resistor values shown in the circuit, and using different combinations of the switches, gain in the range of 2 to 16 can be achieved.

Figure 1. Photodetector Circuit with Programmable Gain

-6- REV. A

## **Test Circuits**

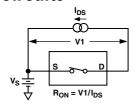

Test Circuit 1. On Resistance

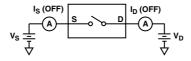

Test Circuit 2. Off Leakage

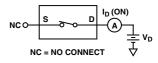

Test Circuit 3. On Leakage

Test Circuit 4. Switching Times

Test Circuit 5. Break-Before-Make Time Delay, t<sub>D</sub>

Test Circuit 6. Charge Injection

Test Circuit 7. Off Isolation

Test Circuit 8. Channel-to-Channel Crosstalk

Test Circuit 9. Bandwidth

# **OUTLINE DIMENSIONS**Dimensions shown in inches and (mm).

# **Revision History**

| Location                                     | Page  |

|----------------------------------------------|-------|

| Data Sheet changed from REV. 0 to REV. A.    |       |

| Edits to Typical Performance Characteristics | . 5–6 |

| Changes to OUTLINE DIMENSIONS drawing        | 8     |