CS1232

T-65-13

## **Micromonitor**

#### **Features**

- Halts and restarts an out-of-control microprocessor

- Holds microprocessor in check during power transients

- Automatic restart after power failure

- Monitors pushbutton for external reset

- Monitors microprocessor power supply to be within 5% or 10% of 5 V

- No discrete components needed

- 8-pin Mini-DIP or 16-pin SOIC

- Pin compatible with DS1232

## **General Description**

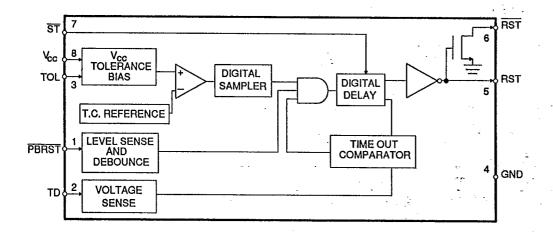

The CS1232 is a monitor for microprocessors which checks program execution, power source quality, and external reset status.

The power status (Vcc) is monitored by a comparator and a precision temperature-compensated reference. Reset is forced active by an internal signal when Vcc goes out-of-tolerance. Reset signals stay active for a minimum for 250 ms after Vcc returns to an in-tolerance condition. This allows both power supply and processor to stabilize.

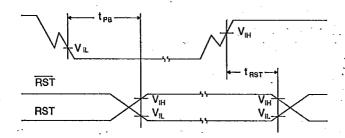

The pushbutton reset control input is debounced and the active reset minimum pulse width of 250 ms is guaranteed.

The internal watchdog timer forces the reset signals active if the strobe input is not driven low prior to time out. The CS1232 timer can be set to operate at time out settings of approximately 150ms, 600ms, and 1.2 seconds.

A surface mount 16-pin SOIC is available, as well as an 8-pin Plastic DIP.

#### **ORDERING INFORMATION:**

| Wodel     | iemp. Hange      | Package           |

|-----------|------------------|-------------------|

| CS1232- P | 0 °C to 70 °C    | 8-pin Plastic DIP |

| CS1232-IP | -40 °C to +85 °C | 8-pin Plastic DIP |

| CS1232- S | 0 °C to 70 °C    | 16-pin SOIC       |

| CS1232-IS | -40 °C to +85 °C | 16-pin SOIC       |

|           |                  |                   |

Preliminary Product Information

This document contains information for a new product. Crystal Semiconductor reserves the right to modify this product without notice.

Crystal Semiconductor Corporation P.O. Box 17847, Austin, TX 78760 (512) 445 7222 FAX: (512) 445 7581 JUN '89 DS18PP1 8-3

T-65-13 CS1232

## ANALOG CHARACTERISTICS (TMIN to TMAX, VCC = 4.5 to 5.5V)

| Parameter                  | . 1          | 2:       | Symbol            | min  | typ  | max  | Units |

|----------------------------|--------------|----------|-------------------|------|------|------|-------|

| V <sub>CC</sub> Trip Point | (TOL = GND)  | (Note 1) | V <sub>CCTP</sub> | 4.50 | 4.62 | 4.74 | V     |

| V <sub>CC</sub> Trip Point | (TOL = V cc) | (Note 1) | V <sub>CCTP</sub> | 4.25 | 4.37 | 4.49 | ٧     |

| Operating Curren           | t .          | (Note 2) | I cc ·            |      | 0.4  | 2.0  | mA    |

Notes: 1. All Voltages Referenced To Ground

2. Measured with outputs open

### RECOMMENDED OPERATING CONDITIONS

| Parameter             |                     | Symbol          | min       | typ | max          | Units    |

|-----------------------|---------------------|-----------------|-----------|-----|--------------|----------|

| Operating Temperature | CS1232<br>CS1232- I |                 | 0<br>- 40 | -   | + 70<br>+ 85 | °C<br>°C |

| Supply Voltage (Note  | 1)                  | V <sub>cc</sub> | 4.5       | 5.0 | 5.5          | V        |

## DIGITAL CHARACTERISTICS (TMIN to TMAX, VCC = 4.5V to 5.5V)

| Parameter                                 | Symbol          | min   | typ  | max                  | Units |

|-------------------------------------------|-----------------|-------|------|----------------------|-------|

| ST and PBRST Input High Level (Note 1)    | V <sub>IH</sub> | 2.0   | _    | V <sub>cc</sub> +0.3 | ٧     |

| ST and PBRST Input Low Level (Note 1)     | V <sub>IL</sub> | -0.3  | -    | + 0.8                | ٧     |

| Output High Current @2.4 V RST only       | Іон             | - 1.0 | -2.0 | _                    | mA    |

| Output Low Current @0.4 V RST, RST        | loL             | 2.0   | 3.0  |                      | mA    |

| Input Leakage (Note 3)                    | I <sub>IL</sub> | -1.0  | _    | + 1.0                | uA    |

| Input Capacitance T <sub>A</sub> = 25 °C  | C <sub>IN</sub> |       |      | 5                    | pF    |

| Output Capacitance T <sub>A</sub> = 25 °C | Соит            | -     | -    | 7                    | pF    |

Note: 3. PBRST is internally pulled up to Vcc with an internal impedance of 100 k $\Omega$  typical.

Specifications are subject to change without notice.

T-65-13 CS1232

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                | min               | typ | max  | Units |  |

|------------------------------------------|-------------------|-----|------|-------|--|

| Voltage on any Pin<br>Relative to Ground | - 1.0             |     | +7.0 | · V   |  |

| Input Current                            | -                 |     | ±10  | mA    |  |

| Storage Temperature                      | - 55              |     | +125 | °င    |  |

| Soldering Temperature                    | 260 °C for 10 Sec |     |      |       |  |

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes

## SWITCHING CHARACTERISTICS (TMIN to TMAX, VCC = 5V ± 10%)

| Parameter                                                                                     | Symbol           | min                | typ          | max                 | Units          |

|-----------------------------------------------------------------------------------------------|------------------|--------------------|--------------|---------------------|----------------|

| PBRST = V <sub>IL</sub>                                                                       | t <sub>PB</sub>  | 20                 | <del>-</del> | <b>-</b> .          | ms             |

| RESET Active Time                                                                             | t <sub>RST</sub> | 250                | 610          | 1000                | ms             |

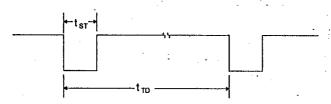

| ST Pulse Width                                                                                | t sr             | 20                 | <u> </u>     | -                   | ns             |

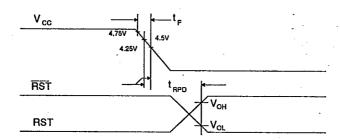

| V <sub>CC</sub> Detect to RST and RST                                                         | t RPD            | -                  |              | 100                 | ns             |

| V <sub>CC</sub> Slew Rate from 4.75V - 4.25V                                                  | t <sub>F</sub>   | 300                |              | _                   | us             |

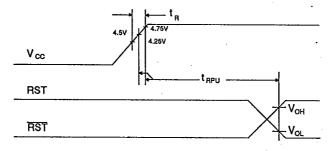

| V <sub>CC</sub> Detect to RST and RST (Note 4)                                                | t <sub>RPU</sub> | 250                | 610          | 1000                | ms             |

| V <sub>CC</sub> Slew Rate from 4.25V - 4.75V                                                  | t <sub>R</sub>   | 0                  | _            | _                   | ns             |

| ST Pulse Period TD pin at Ground TD pin floating TD pin connected to V <sub>CC</sub> (Note 5) | t <sub>TD</sub>  | 62.5<br>250<br>500 | . –          | 250<br>1000<br>2000 | ms<br>ms<br>ms |

Note:

4.  $t_R = 5 \mu s$

5. ttp is the maximum elapsed time between ST pulses which will keep the watchdog timer from forcing RST and RST to the active state for a time of trast.

6. RST is an N-channel open drain output.

CS1232

Timing Diagram—Pushbutton Reset

Timing Diagram—Strobe Input

Timing Diagram—Power Down

Timing Diagram-Power Up

T-65-13 CS1232

# 一些海色3/252中供应商

#### POWER SUPPLY MONITOR

The CS1232 will detect out-of-tolerance power supplies for processor-based systems as well as warn of an impending power failure. The TOL digital input pin defines the threshold level for VCC; when the VCC level drops below the TOL defined level, the comparator outputs the signals RST and RST. The threshold level is set to typically 4.37 V if TOL is connected to VCC, and is set to typically 4.62 V if TOL is connected to GND. The processor is allowed to continue until the last possible moment that VCC is valid. Upon return of power, RST and RST are active for 250 ms (minimum) to allow stabilization.

#### **PUSHBUTTON RESET CONTROL**

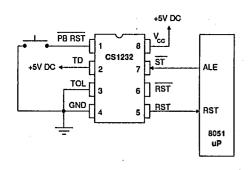

$\overline{PBRST}$  is normally connected to a reset pushbutton (see Figure 1). This active low signal is debounced and timed to generate signals of 250 ms (minimum) for RST and  $\overline{RST}$ . The delay begins when  $\overline{PBRST}$  is released from from the low state.  $\overline{PBRST}$  has an internal 100 kΩ pull-up resistor.

#### WATCHDOG TIMER

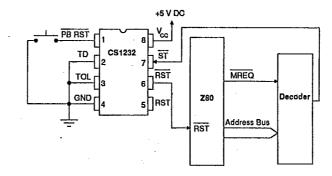

When RST and RST become inactive (normal CPU operation), the watchdog timer starts timing out, using the time set by TD. RST and RST are forced active when ST is not stimulated for this predetermined time. TD sets the time to be: 150 ms if TD is connected to ground, 600 ms is TD is not connected, or 1.2 seconds with TD connected to VCC. RST and RST are driven active for 250 ms (minimum) if no high-to-low transition occurs on the ST input pin before time out. Microprocessor address signals, data signals, control signals, and output port bits can be used for the ST input pin. These signals cause the watchdog timer to be reset prior to time out indicating normal function of the microprocessor (see Figure 2).

Figure 1. Pushbutton Reset

Figure 2. Watchdog Timer

38E D ≥ 2546324 0003312 6 ≥ CYS

T-65-13 CS1232

| PUSH BUTTON RESET INPUT  | PBRST | [1 8] Vcc                   | +5 VOLT POWER                        |

|--------------------------|-------|-----------------------------|--------------------------------------|

| TIME DELAY SET           | TD    | [27] ST                     | STROBE INPUT                         |

| SELECTS VCC DETECT LEVEL | TOL   | [3 <sup>CS1232</sup> 6] RST | RESET OUTPUT (Active Low, Open Drain |

| GROUND                   | GND   | [4 5] RST                   | RESET OUTPUT (Active High)           |

| rain |

|------|

|      |

|      |

|      |