|                       |         |          |      |      |              |                 |        | F   | REVISION | ONS |         |      |                       |             |          |             |                |             |      |    |

|-----------------------|---------|----------|------|------|--------------|-----------------|--------|-----|----------|-----|---------|------|-----------------------|-------------|----------|-------------|----------------|-------------|------|----|

| <sup>L</sup> 暨询"5     | 962-9   | 8538     | 0102 | 'Δ"Щ | 应商           | DESCR           | IPTION | ١   |          |     |         |      | DA                    | TE (Y       | R-MO-    | DA)         |                | APPR        | OVED |    |

|                       |         |          |      |      | <del>/</del> | _               |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| '                     |         |          |      |      |              |                 |        |     |          |     |         | 1    |                       |             |          |             | 1              |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| REV                   |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| SHEET                 |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| REV                   |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| SHEET                 | 15      | 16       | 17   | 18   | 19           | 20              | 21     | 22  | 23       |     |         |      |                       |             |          |             |                |             |      |    |

| REV STATUS            |         |          |      | REV  |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| OF SHEETS             |         |          |      | SHE  | ET           |                 | 1      | 2   | 3        | 4   | 5       | 6    | 7                     | 8           | 9        | 10          | 11             | 12          | 13   | 14 |

| PMIC N/A              |         |          |      |      | PARED        | ) BY<br>ithadia |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      | 1 10 | ajesii i     | madia           |        |     |          |     | ы       | EEEN | ee ei                 | IDDI        | V CE     | NTED        | COL            | UMBI        | ıe   |    |

| STAN                  | IDAR    | <u> </u> |      | CHE  | CKED         | RV              |        |     |          |     | וט      | EFEN |                       |             |          |             | 43216          |             | Jo   |    |

| MICRO                 |         |          |      | Ra   | ajesh P      | ithadia         |        |     |          |     |         |      | -                     | •           | , ·      |             |                |             |      |    |

| DRA                   | WING    | 3        |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

|                       |         |          |      |      | ROVE         |                 |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| THIS DRAWIN<br>FOR US |         |          | 3LE  | Ra   | aymono       | d Monni         | n      |     |          | MIC | ROC     | IRCL | ЛІ, L                 | OIGI I      | AL-LI    | NEA<br>TO F | R, CN<br>DIGIT | MOS,        | LOW  | -  |

| DEPAR                 |         |          |      |      |              |                 |        |     |          | COL | UVFF    | RTER | -BII<br>WIT           | ANA<br>H.SE | RIAL     | CON         | JTRO           | AL<br>IL AN | D 8  |    |

|                       |         |          |      |      |              |                 |        |     |          |     |         |      |                       |             |          |             | SILIC          |             |      |    |

| AND AGEN              |         |          |      | DRA' | WING.        | APPRO           | OVAL D | ATE |          |     |         |      |                       |             |          |             |                |             |      |    |

| DEPARTMEN             | I OF D  | 'CLEN    | SE   | '    | 98-06-2      | 24              |        |     |          |     |         |      |                       |             |          |             |                |             |      |    |

| A N A C               | SC N/A  |          |      |      |              |                 |        |     |          | _   |         | _    |                       |             | Π        |             |                |             |      |    |

| Alvic                 | JO IN/A |          |      | REVI | SION I       | _EVEL           |        |     |          | Siz | ZE<br>A |      | GE CC<br><b>67268</b> |             |          |             | 5962-          | 9853        | 8    |    |

|                       |         |          |      |      |              |                 |        |     |          | SHE |         | '    | J. 200                | •           | <u> </u> |             |                |             |      |    |

|                       |         |          |      |      |              |                 |        |     |          | SHE | = 1     |      | 1                     | OF          | 23       |             |                |             |      |    |

DSCC FORM 2233 APR 97

APR 97

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

5962-E430-98

### 1. SCOPE

查览5962 798538011 Q 20公司 供加速的 product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

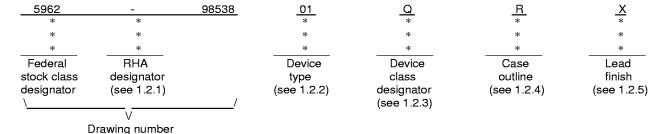

1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | <u>Generic number</u> | <u>Circuit function</u>                                                                         |

|-------------|-----------------------|-------------------------------------------------------------------------------------------------|

| 01          | TLV1548               | Low -Voltage 10-Bit Analog to Digital<br>Converters with Serial control and 8<br>Analog Inputs. |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

M Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A

Q or V Certification and qualification to MIL-PRF-38535

1.2.4 Case outline(s). The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style         |

|----------------|------------------------|------------------|-----------------------|

| R              | GDIP1-T20 or CDIP2-T20 | 20               | Dual-in-line          |

| 2              | CQCC1-N20              | 20               | Leadless chip carrier |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 2    |

### 1.3 Absolute maximum ratings. 1/2/

| 查询"55%208866386402%"供应商                                       | -0.5 V dc to +6.5 V dc <u>2</u> / |

|---------------------------------------------------------------|-----------------------------------|

| Input voltage range (V <sub>I</sub> ) (any input)             | -0.3 V to V <sub>CC</sub> +0.3 V  |

| Output voltage (V <sub>O</sub> )                              |                                   |

| Positive reference voltage, V <sub>REF+</sub>                 | V <sub>CC</sub> + 0.1 V           |

| Negative reference voltage, V <sub>REF</sub>                  |                                   |

| Peak input current I <sub>I</sub> (any input)                 | ± 20 mA                           |

| Peak total input current (all inputs)                         | -30 mA                            |

| Storage temperature range (T <sub>STG</sub> )                 | -65°C to +150°C                   |

| Lead temperature 1, 6 mm (1/16 inch) from case for 10 seconds | +260°C                            |

| Maximum power dissipation, T <sub>A</sub> ≤25°C: 3/           |                                   |

| Case R                                                        | 1894 m <b>W</b>                   |

| Case 2                                                        |                                   |

| Thermal resistance, junction-to-case ( $\theta_{JC}$ ):       |                                   |

| Case R                                                        | 28°C/W                            |

| Case 2                                                        | 20°C/W                            |

| Thermal resistance, junction-to-ambient $(\theta_{JA})$ :     |                                   |

| Case R                                                        | 66°C/W                            |

| Case 2                                                        | 65°C/W                            |

| Junction temperature (T <sub>J</sub> )                        |                                   |

|                                                               |                                   |

| 1.4 Recommended operating conditions.                         |                                   |

| Supply voltage range (V <sub>CC</sub> )                       | +2.7 V dc to +5.5 V dc            |

| Positive reference Voltage, (V <sub>REF+)</sub>               |                                   |

| Negative reference Voltage, (V <sub>REF-1</sub> )             |                                   |

| Differential reference Voltage, VREF+ - VREF                  |                                   |

| Analog input voltage range (V <sub>I</sub> )                  |                                   |

|                                                               | _                                 |

| High level input voltage, (V <sub>H</sub> )                   |                                   |

| Low level input voltage, (V <sub>IL</sub> )                   | 0.6 7 00                          |

- Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- 2/ All voltage values are with respect to GND with REF- and GND wired together. (unless otherwise noted).

- 3/ Derate factor at  $T_A > 25$ °C for case R is 15.1 mW/°C, and for case 2 is 11.0 mW/°C.

4/ Analog input voltages greater than that applied to REF+ convert as all ones (1111111111), while input voltage less than that applied to REF- convert as all zeros (000000000). The device is functional with reference voltages down to 1 V (V<sub>ref+</sub> - V<sub>ref-</sub>); however, the electrical specifications are no longer applicable.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 3    |

1.4 Recommended operating conditions - Continued.

| ·询"振96&ra863,8 <del>01年4件</del> ",供应商 <sub>RT)</sub>                   | 0.84 μs         |

|------------------------------------------------------------------------|-----------------|

| Setup time, CS ↑ to CSTART ↓, t <sub>su</sub> (CSTART)                 | 10 ns           |

| Clock frequency at I/O CLK, fcLK; Vcc = 5.5 V                          |                 |

| $V_{CC} = 2.7 \text{ V}$                                               |                 |

| Pulse duration, I/O CLK high, $t_{wH}(I/O)$ ; $V_{CC} = 5.5 \text{ V}$ | 50 ns           |

| $V_{CC} = 2.7 \text{ V}$                                               | 100 ns          |

| Pulse duration, I/O CLK low, $t_{wL}(I/O)$ ; $V_{CC} = 5.5 \text{ V}$  | 50 ns           |

| $V_{CC} = 2.7 \text{ V}$                                               | 100 ns          |

| Transition time, I/O CLK t <sub>t</sub> (I/O)                          | 1 μs <u>5</u> / |

| Transition time, DATA IN, t <sub>t</sub> (DATA IN)                     | 10 μs           |

| Transition time, $\overline{\text{CS}}$ , $t_t(\text{CS})$             | 10 μs           |

| Transition time, FS, t <sub>t</sub> (FS)                               |                 |

| Transition time, CSTART, tt(CSTART)                                    | 10 μs           |

| Operating free-air temperature range (T <sub>A</sub> )                 | -55°C to +125°C |

### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation.

#### **SPECIFICATION**

### DEPARTMENT OF DEFENSE

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### **STANDARDS**

### DEPARTMENT OF DEFENSE

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-973 - Configuration Management.

MIL-STD-1835 - Interface Standard For Microcircuit Case Outlines.

#### **HANDBOOKS**

### DEPARTMENT OF DEFENSE

MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's).

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

<sup>5/</sup> This is the time required for the I/O CLK signal to fall from V<sub>IH</sub> max to V<sub>IL</sub> min or to rise from V<sub>IL</sub> max to V<sub>IH</sub> min. In the vicinity of normal room temperature, the devices function with an input clock transition time as slow as 1µs for remote data acquisition applications where the sensor and the A/D converter are placed several feet away from the controlling microprocessor.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>4 |

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.3 Truth table. The truth table shall be as specified on figure 2.

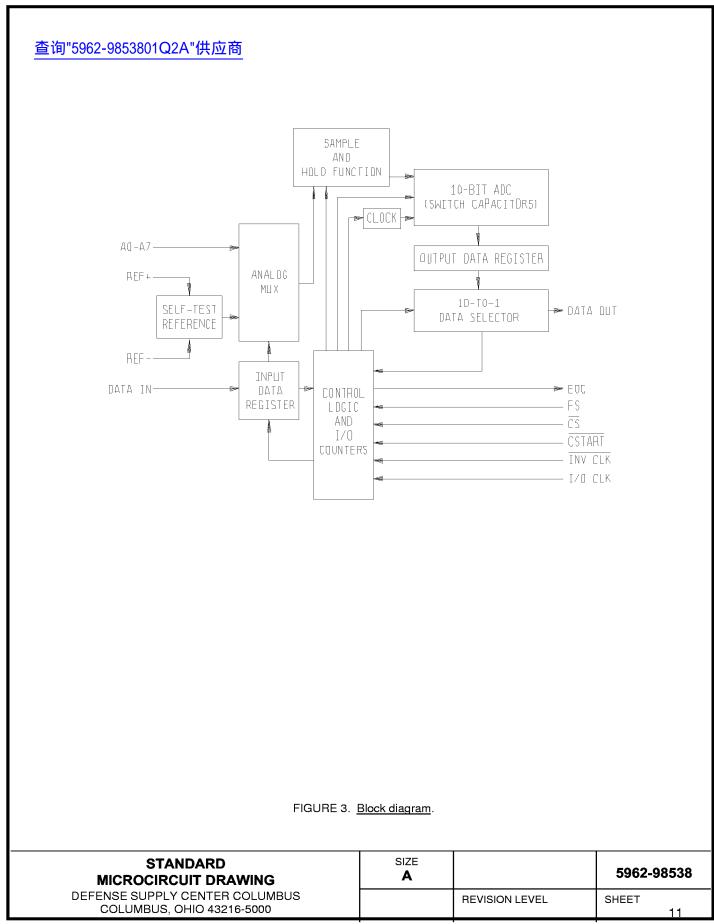

- 3.2.4 Block diagram. The block or logic diagram shall be as specified on figure 3.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M.</u> For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 81 (see MIL-PRF-38535, appendix A).

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 5    |

TABLE I. <u>Electrical performance characteristics</u>. 查询"5962-9853801O2A"供应商

| Test                                | Symbol              | Test conditions $\underline{1}$ / -55°C $\leq$ T <sub>A</sub> $\leq$ +125°C                                                                                 | Device<br>type | Group A<br>subgroups | Lin                   | Limits |    |

|-------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|-----------------------|--------|----|

|                                     |                     | unless otherwise specified                                                                                                                                  |                |                      | Min                   | Мах    |    |

| High level output<br>voltage        | V <sub>OH</sub>     | $I_{OH} = -0.2 \text{ mA}$<br>$V_{CC} = 5.5 \text{ V}$                                                                                                      | 01             | 1, 2, 3              | 2.4                   |        | V  |

|                                     |                     | $I_{OH} = -20 \mu A$ $V_{CC} = 2.7 V$                                                                                                                       |                |                      | V <sub>CC</sub> - 0.1 |        |    |

| Low level output<br>voltage         | V <sub>OL</sub>     | l <sub>OL</sub> = 0.8 mA<br>V <sub>CC</sub> = 5.5 V                                                                                                         | 01             | 1, 2, 3              |                       | 0.4    | V  |

|                                     |                     | $I_{OL} = 20 \mu A$ $V_{CC} = 2.7 V$                                                                                                                        |                |                      |                       | 0.1    |    |

| High impedance<br>output current    | loz                 | $V_{OUT} = V_{CC}, \overline{CS} = V_{CC}$                                                                                                                  | 01             | 1, 2, 3              |                       | 2.5    | μА |

|                                     |                     | V <sub>OUT</sub> = 0 V, $\overline{\text{CS}}$ = V <sub>CC</sub>                                                                                            |                |                      |                       | -2.5   |    |

| High level input<br>current         | I <sub>IH</sub>     | V <sub>IN</sub> = V <sub>CC</sub>                                                                                                                           | 01             | 1, 2, 3              |                       | 2.5    | μА |

| Low level input<br>current          | I <sub>IL</sub>     | V <sub>IN</sub> = 0 V                                                                                                                                       | 01             | 1, 2, 3              |                       | 2.5    |    |

| Operating supply current            | lcc                 | I/O CLK = GND, $V_{CC}$ = 3.3 V to 5.5 V,<br>Conversion speed = fast,<br>For all digital inputs,<br>$0 \le V_{IN} \le 0.3$ V or $V_{IN} \ge V_{CC}$ - 0.3 V | 01             | 1,2,3                |                       | 1.5    | mA |

|                                     |                     | I/O CLK = GND, $V_{CC}$ = 3.3 V to 5.5 V, Conversion speed=slow, For all digital inputs, $0 \le V_{IN} \le 0.3$ V or $V_{IN} \ge V_{CC}$ - 0.3 V            |                |                      |                       | 1.0    |    |

|                                     |                     | I/O CLK = GND, $V_{CC}$ = 2.7 V to 3.3 V, Conversion speed = slow For all digital inputs, $0 \le V_{IN} \le 0.3$ V or $V_{IN} \ge V_{CC}$ - 0.3 V           |                |                      |                       | 0.75   |    |

| Power down supply<br>current        | I <sub>CC(PD)</sub> | For all digital inputs, $0 \le V_{\text{IN}} \le 0.3 \text{ V}$ or $V_{\text{IN}} \ge V_{\text{CC}}$ - 0.3 V                                                | 01             | 1,2,3                |                       | 25     | μА |

| Selected channel<br>leakage current | $I_{lkg}$           | Selected channel at V <sub>CC</sub><br>Unselected channel at 0 V                                                                                            | 01             | 1,2,3                |                       | 1.0    | μΑ |

|                                     |                     | Selected channel at 0 V<br>Unselected channel at V <sub>CC</sub>                                                                                            |                |                      |                       | -1.0   |    |

See footnotes at end of table

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 6    |

TABLE I. <u>Electrical performance characteristics</u> - Continued. 查询"5962-9853801Q2A"供应商

| Test                                                                                                        | Symbol              | Test conditions <u>1</u> /<br>-55°C ≤ T <sub>A</sub> ≤+125°C | Device<br>type | Group A<br>subgroups | Lir | nits                      | Unit               |

|-------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------|----------------|----------------------|-----|---------------------------|--------------------|

|                                                                                                             |                     | unless otherwise specified                                   |                |                      | Min | Max                       |                    |

| Maximum static analog reference current into REF+                                                           |                     | $V_{ref+} = V_{CC} = 5.5V$<br>$V_{ref-} = GND$               | 01             | 1,2,3                |     | 1                         | μА                 |

| Input capacitance, analog inputs                                                                            | C <sub>IN</sub>     | 2/                                                           | 01             | 1,2,3                |     | 55                        | pF                 |

| Input capacitance, control inputs                                                                           | C <sub>IN</sub>     | <u>2</u> /                                                   | 01             | 1,2,3                |     | 15                        | pF                 |

| Input multiplexer                                                                                           | Z <sub>IN</sub>     | V <sub>CC</sub> = 4.5 V <u>2</u> /                           | 01             | 1,2,3                |     | 1                         | kΩ                 |

| resistance                                                                                                  |                     | V <sub>CC</sub> = 2.7 V <u>2</u> /                           |                |                      |     | 5                         |                    |

| Linearity Error                                                                                             | EL                  | <u>3</u> /                                                   | 01             | 1,2,3                |     | ±1                        | LSB                |

| Differential linearity error                                                                                | E <sub>D</sub>      | <u>4</u> /                                                   | 01             | 1,2,3                |     | ±1                        | LSB                |

| Offset error                                                                                                | Eo                  | <u>4</u> / <u>5</u> /                                        | 01             | 1,2,3                |     | ±1.5                      | LSB                |

| Gain error                                                                                                  | E <sub>G</sub>      | <u>4</u> / <u>5</u> /                                        | 01             | 1,2,3                |     | ±1                        | LSB                |

| Total unadjusted error                                                                                      | E <sub>T</sub>      | <u>6</u> /                                                   | 01             | 1,2,3                |     | ±1.75                     | LSB                |

| Functional tests                                                                                            |                     | See 4.4.1C                                                   | 01             | 7,8 <b>A</b> ,8B     | L   | Н                         |                    |

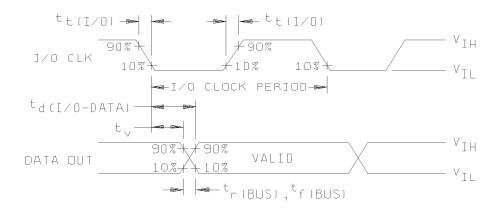

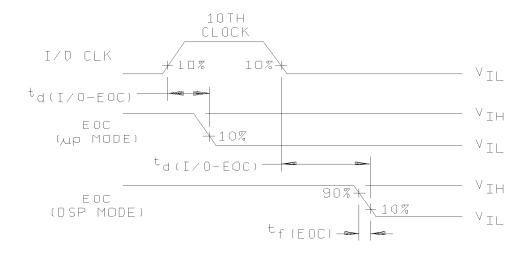

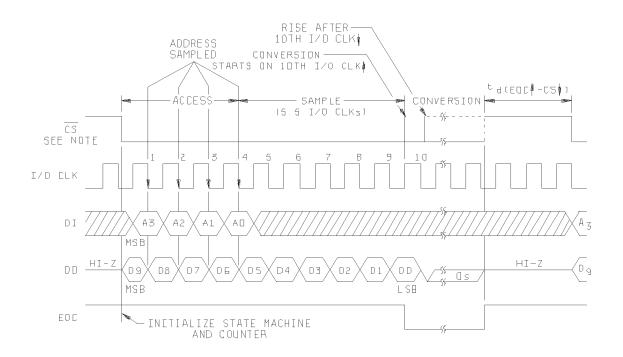

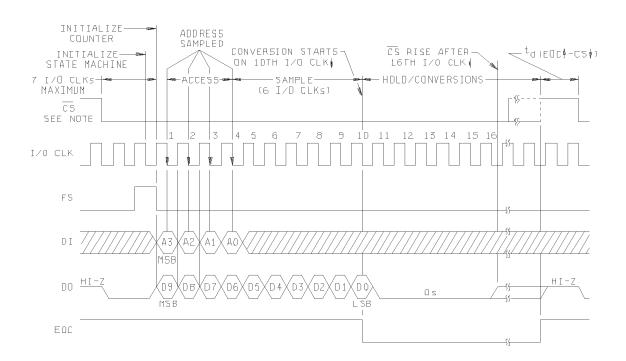

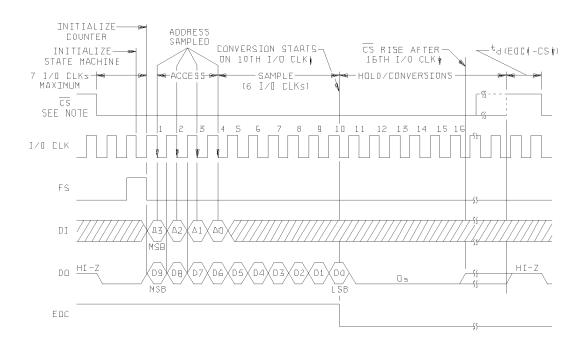

| Conversion time                                                                                             | t <sub>CONV</sub>   | Fast conversion speed See figure 4                           | 01             | 9,10,11              |     | 10                        | μs                 |

|                                                                                                             |                     | Slow conversion speed<br>See figure 4                        |                |                      |     | 25                        |                    |

| Total cycle time (access, sample, conversion and EOC $\uparrow$ to $\overline{\text{CS}} \downarrow$ delay) | tc                  | Fast conversion speed See figure 4 7/8/9/                    | 01             | 9,10,11              |     | 10.1 +<br>10 I/O<br>CLK   | μs                 |

|                                                                                                             |                     | Slow conversion speed See figure 4 7/ 9/                     |                |                      |     | 40.1<br>+10<br>I/O<br>CLK |                    |

| Channel acquisition time (sample)                                                                           | t <sub>acq</sub>    | See figure 4 7/                                              | 01             | 9,10,11              |     | 6                         | I/O CLK<br>periods |

| Valid time, DATA OUT<br>remains valid after I/O<br>CLK↓                                                     | t <sub>V</sub>      | See figure 4                                                 | 01             | 9,10,11              | 50  |                           | ns                 |

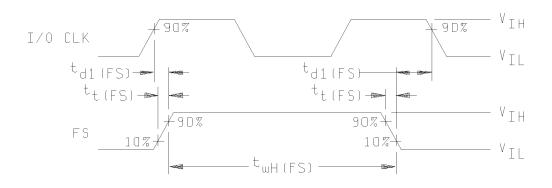

| Delay time, I/O CLK high to FS high                                                                         | t <sub>d1(FS)</sub> | See figure 4                                                 | 01             | 9,10,11              | 5   | 50                        | ns                 |

| Delay time, I/O CLK high to FS low                                                                          | t <sub>d2(FS)</sub> | See figure 4                                                 | 01             | 9,10,11              | 10  | 60                        | ns                 |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>7 |

### TABLE I. Electrical performance characteristics - Continued.

| 查询"5962-985380                                                      | 1Q2A"供应商                            | Test conditions $\underline{1}/$ -55°C $\leq$ T <sub>A</sub> $\leq$ +125°C | Device<br>type | Group A subgroups | Li  | mits | Unit                  |

|---------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------|----------------|-------------------|-----|------|-----------------------|

|                                                                     |                                     | unless otherwise specified                                                 |                |                   | Min | Max  |                       |

| Delay time, EOC↑ to CS low                                          | t <sub>d(EOC</sub> ↑ - CS↓)         | See figure 4 10/                                                           | 01             | 9,10,11           | 100 |      | ns                    |

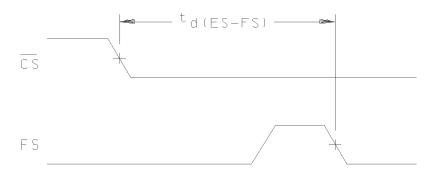

| Delay time $\overline{CS}\downarrow$ to $FS\uparrow$                | t <sub>d(CS</sub> ↓ - FS↑)          | See figure 4                                                               | 01             | 9,10,11           | 1   | 7    | I/O<br>CLK<br>periods |

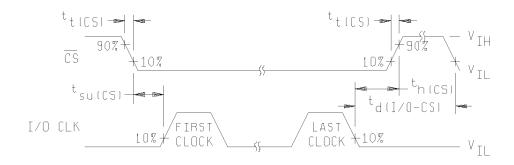

| Delay time, 10th I/O CLK low to CS low to abort conversion.         | t <sub>d (I/O-CS)</sub>             | See figure 4 11/                                                           | 01             | 9,10,11           |     | 1.1  | μs                    |

| Delay time, I/O CLK<br>low to DATA OUT<br>valid                     | t <sub>d (I</sub> /O - DATA)        | See figure 4                                                               | 01             | 9,10,11           |     | 50   | ns                    |

| Delay time, 10th I/O<br>CLK ↓ to EOC low                            | t <sub>d (1</sub> / 0 - EOC)        | See figure 4                                                               | 01             | 9,10,11           |     | 240  | ns                    |

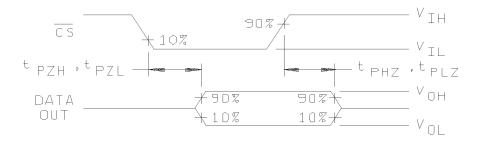

| Enable time, CS<br>low to DATA OUT<br>valid (MSB driven)            | t <sub>PZH</sub> , t <sub>PZL</sub> | See figure 4                                                               | 01             | 9,10,11           |     | 1.3  | μs                    |

| Disable time, CS<br>high to DATA OUT<br>invalid (high<br>impedance) | t <sub>PHZ</sub> , t <sub>PLZ</sub> | See figure 4                                                               | 01             | 9,10,11           |     | 150  | ns                    |

| Fall time, EOC                                                      | t <sub>f (EOC)</sub>                | See figure 4                                                               | 01             | 9,10,11           |     | 50   | ns                    |

| Rise time, output<br>data bus at 2.2 MHz<br>I/O CLK                 | t <sub>r (bus)</sub>                | See figure 4                                                               | 01             | 9,10,11           |     | 250  | ns                    |

| Fall time, output<br>data bus at 2.2 MHz<br>I/O CLK                 | t <sub>f (bus)</sub>                | See figure 4                                                               | 01             | 9,10,11           |     | 250  | ns                    |

- $1/VCC = V_{ref+} = 2.7 V \text{ to } 5.5 V, I/O \text{ frequency} = 2.2 MHz.$

- 2/ Tested initially and after any design or process changes which affect this parameter.

- Linearity error is the maximum deviation from the best straight line through the A/D transfer characteristics.

- 4/ Analog input voltages greater than that applied to REF+ convert as all ones (11111111111), while input voltage less than that applied to REF- convert as all zeros (0000000000). The device is functional with reference voltages down to 1 V (V<sub>ref+</sub> - V<sub>ref-</sub>); however, the electrical specifications are no longer applicable.

- 5/ Zero error is the difference between 0000000000 and the converted output for zero input voltage. Full-scale error is the difference between 1111111111 and the converted output for full-scale input voltage.

- 6/ Total unadjusted error comprises linearity, zero-scale and full-scale errors.

- 7/ I/O CLK period = 1/ (I/O CLK frequency).

- 8/ For 3.3 V to 5.5 V only.

- 9/ For microprocessor mode.

- 10/ For all operating modes.

- 11/ Any transactions of  $\overline{CS}$  are recognized as valid only when the level is maintained for a setup time after the transition.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>8 |

### 查询"5962-9853801Q2A<u>"供应商</u>

| 1/1/12/19       |                 |

|-----------------|-----------------|

| Device type     | 01              |

| Case outlines   | R and 2         |

| Terminal number | Terminal symbol |

| 1               | A0              |

| 2               | A1              |

| 3               | A2              |

| 4               | <b>A</b> 3      |

| 5               | A4              |

| 6               | <b>A</b> 5      |

| 7               | <b>A</b> 6      |

| 8               | A7              |

| 9               | CSTART          |

| 10              | <u>GND</u>      |

| 11              | INV CLK         |

| 12              | FS              |

| 13              | REF-            |

| 14              | R <u>EF</u> +   |

| 15              | cs              |

| 16              | DATA OUT        |

| 17              | DATA IN         |

| 18              | I/O CLK         |

| 19              | EOC             |

| 20              | V <sub>CC</sub> |

|                | Pin description                   |

|----------------|-----------------------------------|

| Terminal       | Description                       |

| An (n =0 to 7) | Analog signal inputs              |

| CSTART         | Sampling/conversion start control |

| INV CLK        | Inverted clock input              |

| FS             | DSP frame synchronization input   |

| REF-           | Lower reference voltage           |

| REF+           | Upper reference voltage           |

| CS             | Chip select                       |

| DATA OUT       | Serial data output                |

| DATA IN        | Serial data input                 |

| I/O CLK        | Input-output clock                |

| EOC            | End of conversion                 |

FIGURE 1. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 9    |

### 查询"5962-9853801Q2A"供应商

| Cor     | ndition Clock  | I/O CLK A              | ctive Edge            |

|---------|----------------|------------------------|-----------------------|

| INV CLK | FS at CS↓      | Output data changes on | Input data sampled on |

| High    | High (MP mode) | $\downarrow$           | <b>↑</b>              |

| High    | Low (DSP mode) | <b>↑</b>               | $\downarrow$          |

| Low     | High (MP mode) | $\downarrow$           | $\downarrow$          |

| Low     | Low (DSP mode) | <u></u>                | <u></u>               |

### FIGURE 2. Truth table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 10   |

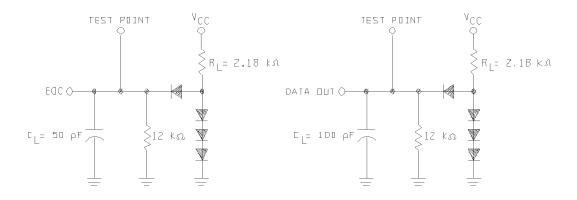

### DATA OUT to HI-Z voltage

### 查询"5962-9853801Q2A"供应商

### CS and I/O CLK voltage

FIGURE 4. Switching waveforms and test circuit.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 12   |

## 查询"5962-9853801Q2A"供应商 DATA OUT and I/O CLK voltage

### CS low to FS low

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>13 |

### \_\_\_\_I/O CLK and EOC voltage

### 查询"5962-9853801Q2A"供应商

### FS and I/O CLK voltage

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>14 |

### 查询"5962-9853801Q2A"供应商

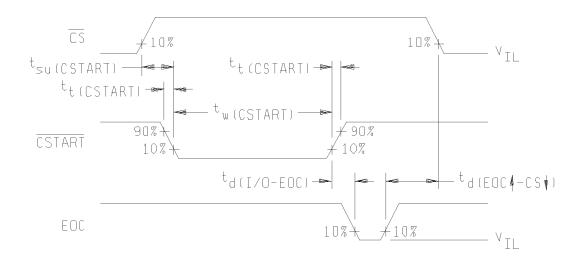

CSTART and CS

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD MICROCIRCUIT DRAWING                               | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 15   |

NOTE: To minimize errors caused by noise at  $\overline{\text{CS}}$ , the internal circuitry waits for a setup time after  $\overline{\text{CS}}$  ↓ before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{\text{CS}}$  setup time elapses.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>16 |

NOTE: To minimize errors caused by noise at  $\overline{\text{CS}}$ , the internal circuitry waits for a setup time after  $\overline{\text{CS}} \downarrow$  before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{\text{CS}}$  setup time elapses.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>17 |

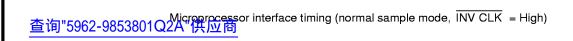

查询"5962-9853801Q2A"供应商 (16-clock transfer, normal sample mode, INV CLK = High)

NOTE: To minimize errors caused by noise at  $\overline{\text{CS}}$ , the internal circuitry waits for a setup time after  $\overline{\text{CS}} \downarrow$  before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{\text{CS}}$  setup time elapses.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>18 |

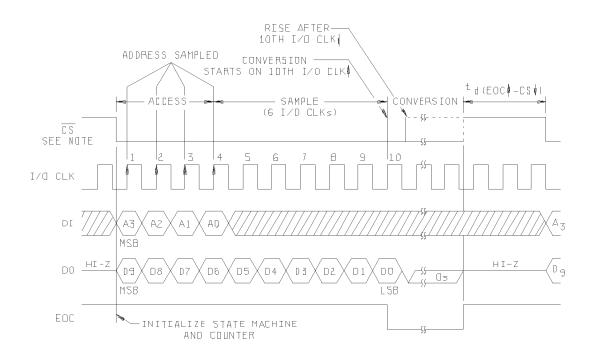

查询"5962-9853801Q2A"供应商 (16-clock transfer, normal sample mode, INV CLK = Low)

NOTE: To minimize errors caused by noise at  $\overline{\text{CS}}$ , the internal circuitry waits for a setup time after  $\overline{\text{CS}}$  ↓ before responding to control input signals. No attempt should be made to clock in input data until the minimum  $\overline{\text{CS}}$  setup time elapses.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>19 |

### 查询"5962-9853801Q2A"供应商

NOTE:  $C_L$  includes probe and jig capacitance.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 20   |

### 4. QUALITY ASSURANCE PROVISIONS

- 4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A = +125EC$ , minimum.

- Interim and final electrical test parameters shall be as specified in table II herein.

- 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

- 4.3 Qualification inspection for device classes Q and V. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections and as specified herein except where option 2 of MIL-PRF-38535 permits alternate in-line control testing. Quality conformance inspection for device class M shall be in accordance with MIL-PRF-38535, appendix A and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 21   |

### TABLE II. Electrical test requirements

查询"5962-9853801Q2A"供应商

| 2 300000                                          |                                                                  |                                      |                                      |

|---------------------------------------------------|------------------------------------------------------------------|--------------------------------------|--------------------------------------|

| Test requirements                                 | Subgroups (in accordance with MIL-STD-883, method 5005, table I) | Subgr<br>(in accord<br>MIL-PRF-385   | ance with                            |

|                                                   | Device<br>class M                                                | Device<br>class Q                    | Device<br>class V                    |

| Interim electrical parameters (see 4.2)           |                                                                  |                                      | 1                                    |

| Final electrical parameters (see 4.2)             | 1,2,3,7,8A,8B,9,<br>10,11 <u>1</u> /                             | 1,2,3,7,8A,8B,<br>9,10,11 <u>1</u> / | 1,2,3,7,8A,<br>8B,9,10,11 <u>2</u> / |

| Group A test requirements (see 4.4)               | 1,2,3,7,8A,8B,9,<br>10,11                                        | 1,2,3,7,8 <b>A</b> ,8B,<br>9,10,11   | 1,2,3,7,8A,<br>8B,9,10,11            |

| Group C end-point electrical parameters (see 4.4) | 1                                                                | 1                                    | 1                                    |

| Group D end-point electrical parameters (see 4.4) | 1                                                                | 1                                    | 1                                    |

| Group E end-point electrical parameters (see 4.4) |                                                                  |                                      |                                      |

<sup>1/</sup> PDA applies to subgroup 1.

### 4.4.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the truth table. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device.

- 4.4.2 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.2.1 Additional criteria for device class M. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition A, B, C or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- b.  $T_A = +125EC$ , minimum.

- Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- 4.4.2.2 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>22 |

<sup>2/</sup> PDA applies to subgroups 1 and 7.

4.4.3 Group D inspection. The group D inspection end-point electrical parameters shall be as specified in table II herein.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535 for the RHA level being tested. For device class M, the devices shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535, appendix A for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table I at T<sub>A</sub> = +25EC " 5EC, after exposure, to the subgroups specified in table II herein.

- c. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

- 5. PACKAGING

- 5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor prepared specification or drawing.

- 6.1.2 Substitutability. Device class Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.3 <u>Record of users</u>. Military and industrial users should inform Defense Supply Center Columbus when a system application requires configuration control and which SMD's are applicable to that system. DSCC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DSCC-VA, telephone (614) 692-0525.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DSCC-VA, Columbus, Ohio 43216-5000, or telephone (614) 692-0674.

- 6.5 <u>Abbreviations, symbols, and definitions</u>. The abbreviations, symbols, and definitions used herein are defined in MIL-PRF-38535 and MIL-HDBK-1331.

- 6.6 Sources of supply.

- 6.6.1 Sources of supply for device classes Q and V. Sources of supply for device classes Q and V are listed in QML-38535. The vendors listed in QML-38535 have submitted a certificate of compliance (see 3.6 herein) to DSCC-VA and have agreed to this drawing.

- 6.6.2 Approved sources of supply for device class M. Approved sources of supply for class M are listed in MIL-HDBK-103. The vendors listed in MIL-HDBK-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DSCC-VA.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-98538 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 23   |

# 查询"5962-9853801Q2A"供应商

DATE: 98-06-24

Approved sources of supply for SMD 5962-98538 are listed below for immediate acquisition information only and shall be added to MIL-HDBK-103 and QML-38535 during the next revision. MIL-HDBK-103 and QML-38535 will be revised to include the addition or deletion of sources. The vendors listed below have agreed to this drawing and a certificate of compliance has been submitted to and accepted by DSCC-VA. This bulletin is superseded by the next dated revision of MIL-HDBK-103 and QML-38535.

| Standard<br>microcircuit drawing<br>PIN <u>1</u> / | Vendor<br>CAGE<br>number | Vendor<br>similar<br>PIN <u>2</u> / |

|----------------------------------------------------|--------------------------|-------------------------------------|

| 5962-9853801QRA                                    | 01295                    | TLV1548MJB                          |

| 5962-9853801Q2A                                    | 01295                    | TLV1548MFKB                         |

- 1/ The lead finish shown for each PIN representing a hermetic package is the most readily available from the manufacturer listed for that part. If the desired lead finish is not listed contact the vendor to determine its availability.

- 2/ Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

Vendor CAGE Vendor name and address number

01295 Texas Instruments Incorporated 13500 N. Central Expressway P.O. Box 655303

Dallas, TX 75265 Point of contact:

I-20 at FM 1788 Midland, TX 79711-0448

The information contained herein is disseminated for convenience only and the Government assumes no liability whatsoever for any inaccuracies in the information bulletin.