## LP5521 Programmable Three Channel LED Driver

#### **General Description**

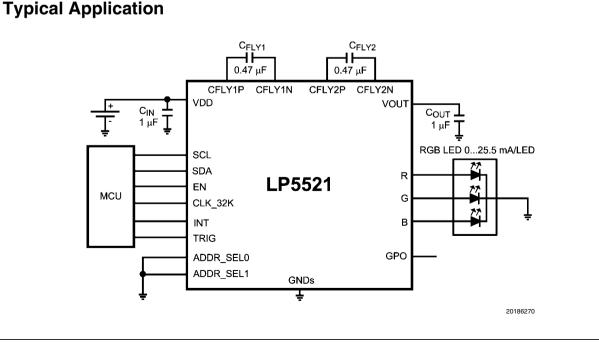

The LP5521 is a three channel LED driver designed to produce variety of lighting effects for mobile devices. High efficiency charge pump enables LED driving over full Li-Ion battery voltage range. The device has a program memory for creating variety of lighting sequences. When program memory has been loaded, LP5521 can operate independently without processor control.

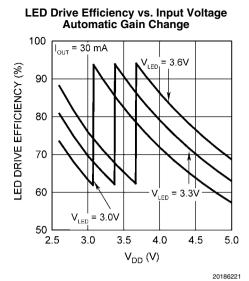

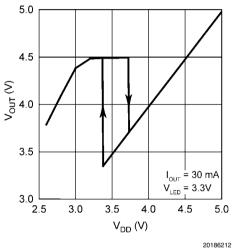

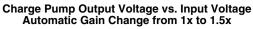

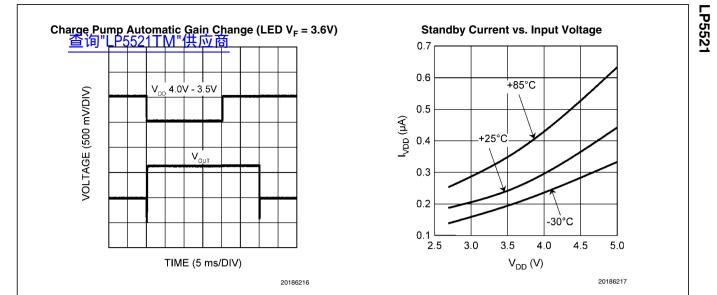

LP5521 maintains excellent efficiency over a wide operating range by automatically selecting proper charge pump gain based on LED forward voltage requirements. LP5521 is able to automatically enter power-save mode, when LED outputs are not active and thus lowering current consumption.

Three independent LED channels have accurate programmable current sources and PWM control. Each channel has program memory for creating desired lighting sequences with PWM control.

LP5521 has a flexible digital interface. Trigger I/O and 32 kHz clock input allow synchronization between multiple devices. Interrupt output can be used to notify processor, when LED sequence has ended. LP5521 has four pin selectable I<sup>2</sup>C addresses. This allows connecting up to four parallel devices in one I<sup>2</sup>C bus. GPO and INT pins can be used as a digital control pin for other devices.

LP5521 requires only four small and low cost ceramic capacitors.

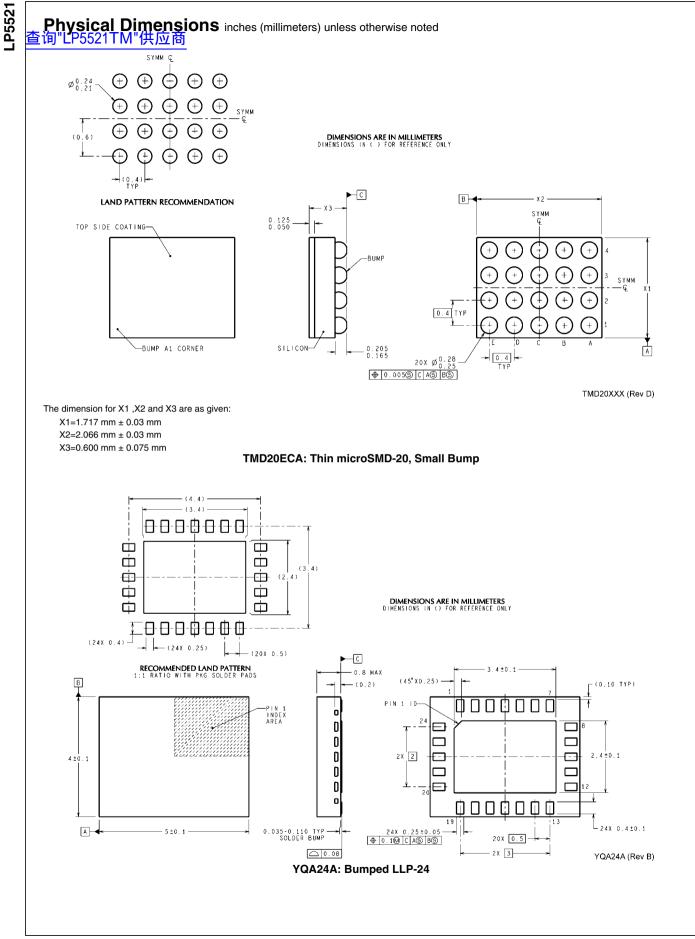

LP5521 is available in tiny 2.1x1.7x0.6 mm microSMD-20 package and in 4.0x5.0x0.8 mm bumped LLP-24 package.

Comprehensive application tools are available, including command compiler for easy LED sequence programming.

#### Features

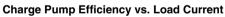

- Adaptive charge pump with 1x and 1.5x gain provides up to 95% LED drive efficiency

- Charge pump with soft start and overcurrent/short circuit protection

- Low input ripple and EMI

- Very small solution size, no inductor or resistors required

- 200 nA typical shutdown current

- Automatic power save mode

- I<sup>2</sup>C compatible interface

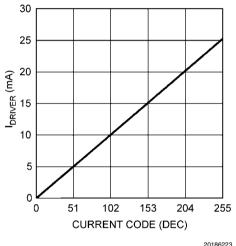

- Independently programmable constant current outputs with 8-bit current setting and 8-bit PWM control

- Typical LED output saturation voltage 50 mV and current matching 1%

- Three program execution engines with flexible instruction set

- Autonomous operation without external control

- Large SRAM program memory

- Two general purpose digital outputs

- microSMD-20 package, 0.4 mm pitch

- Bumped LLP-24 package, 0.5 mm pitch

#### Applications

- Fun / indicator lights

- LCD sub-display backlighting

- Keypad RGB backlighting and phone cosmetics

- Vibra, speakers, waveform generator

LP5521

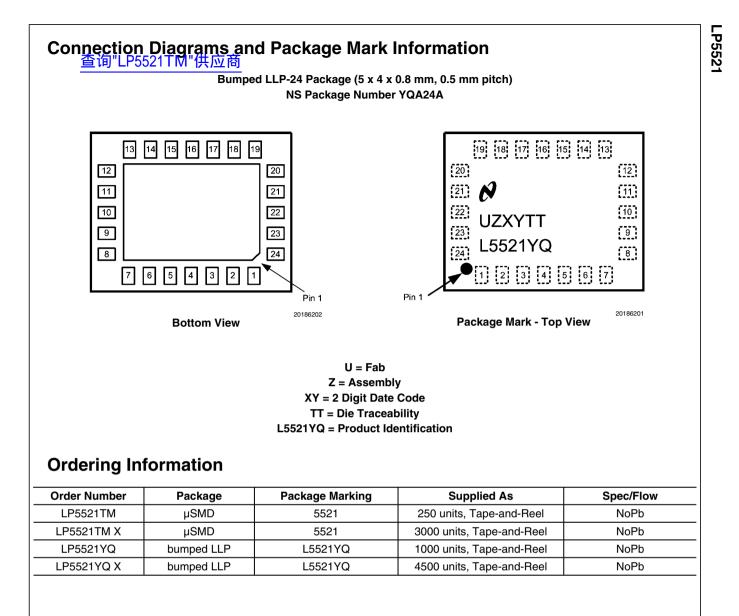

## Connection Diagrams and Package Mark Information 查询"LP5521\_TM"供应商

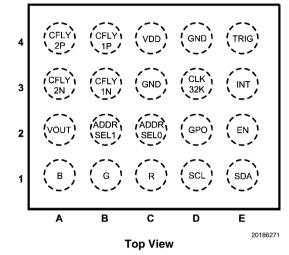

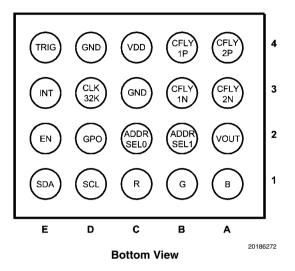

Thin microSMD-20 Package (2.1 x 1.7 x 0.6 mm, 0.4 mm pitch) NS Package Number TMD20ECA

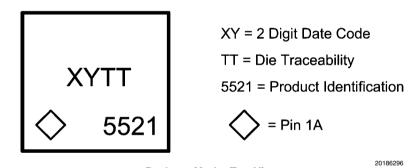

#### **Package Mark**

Package Mark - Top View

#### Pin Descriptions LP5521TM 询"LP5521TM"供应商

| Pin # | Name      | Туре | Description                                         |  |  |  |

|-------|-----------|------|-----------------------------------------------------|--|--|--|

| 1A    | В         | A    | Current source output                               |  |  |  |

| 1B    | G         | А    | Current source output                               |  |  |  |

| 1C    | R         | А    | Current source output                               |  |  |  |

| 1D    | SCL       | Ι    | I <sup>2</sup> C Serial interface clock input       |  |  |  |

| 1E    | SDA       | I/OD | I <sup>2</sup> C Serial interface data input/output |  |  |  |

| 2A    | VOUT      | А    | Charge pump output                                  |  |  |  |

| 2B    | ADDR_SEL1 | Ι    | I <sup>2</sup> C address select input               |  |  |  |

| 2C    | ADDR_SEL0 | Ι    | I <sup>2</sup> C address select input               |  |  |  |

| 2D    | GPO       | 0    | General purpose output                              |  |  |  |

| 2E    | EN        | I    | Chip enable                                         |  |  |  |

| ЗA    | CFLY2N    | А    | Negative terminal of charge pump fly capacitor 2    |  |  |  |

| 3B    | CFLY1N    | А    | Negative terminal of charge pump fly capacitor 1    |  |  |  |

| 3C    | GND       | G    | Ground                                              |  |  |  |

| 3D    | CLK_32K   | Ι    | 32 kHz clock input                                  |  |  |  |

| 3E    | INT       | OD/O | Interrupt output / General Purpose Output           |  |  |  |

| 4A    | CFLY2P    | А    | Positive terminal of charge pump fly capacitor 2    |  |  |  |

| 4B    | CFLY1P    | А    | Positive terminal of charge pump fly capacitor 1    |  |  |  |

| 4C    | VDD       | Р    | Power supply pin                                    |  |  |  |

| 4D    | GND       | G    | Ground                                              |  |  |  |

| 4E    | TRIG      | I/OD | Trigger input/output                                |  |  |  |

A: Analog Pin, G: Ground Pin, P: Power Pin, I: Input Pin, I/O: Input/Output Pin, O: Output Pin, OD: Open Drain Pin

| Pin # | Descriptions<br>查询"LP5521TM<br>Name |           | Description                                         |  |

|-------|-------------------------------------|-----------|-----------------------------------------------------|--|

| 1     | CFLY2P                              | Туре<br>А | Positive terminal of charge pump fly capacitor 2    |  |

| 2     | CFL12F<br>CFLY1P                    | A         | Positive terminal of charge pump fly capacitor 2    |  |

| 3     | VDD                                 | A         | Power supply pin                                    |  |

| 4     | GND                                 | G         | Ground                                              |  |

| 5     | CLK_32K                             | G         | 32 kHz clock input                                  |  |

| 6     | INT                                 | OD/O      | Interrupt output / General purpose output           |  |

| 7     | TRIG                                | I/OD      | Trigger input/output                                |  |

| 8     | Thid                                | N/C       |                                                     |  |

| 9     |                                     | N/C       |                                                     |  |

| 10    |                                     | N/C       |                                                     |  |

| 11    |                                     | N/C       |                                                     |  |

| 12    |                                     | N/C       |                                                     |  |

| 13    | SDA                                 | I/OD      | I <sup>2</sup> C Serial interface data input/output |  |

| 14    | EN                                  | 1/00      | Chip enable                                         |  |

| 14    | SCL                                 | I         | I <sup>2</sup> C Serial interface clock input       |  |

| 15    | GPO                                 | 0         |                                                     |  |

|       |                                     |           | General purpose output                              |  |

| 17    | R<br>G                              | <u>A</u>  | Current source output                               |  |

| 18    |                                     | A         | Current source output                               |  |

| 19    | B                                   | A         | Current source output                               |  |

| 20    | ADDR_SEL0                           | I         | I <sup>2</sup> C address select input               |  |

| 21    | ADDR_SEL1                           |           | I <sup>2</sup> C address select input               |  |

| 22    | VOUT                                | A         | Charge pump output                                  |  |

| 23    | CFLY2N                              | A         | Negative terminal of charge pump fly capacitor 2    |  |

| 24    | CFLY1N                              | A         | Negative terminal of charge pump fly capacitor 1    |  |

A: Analog Pin, G: Ground Pin, P: Power Pin, I: Input Pin, I/O: Input/Output Pin, O: Output Pin, OD: Open Drain Pin, N/C: Not Connected

LP5521

#### Absolute Maximum Ratings (Notes 1, 2)

值 10 5521 TM 14 应 商 If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| V(V <sub>DD</sub> , V <sub>OUT</sub> , R, G, B) | -0.3V to +6.0V                 |

|-------------------------------------------------|--------------------------------|

| Voltage on Logic Pins                           | -0.3V to V <sub>DD</sub> +0.3V |

|                                                 | with 6.0V max                  |

| Continuous Power Dissipation (Note 3)           | Internally Limited             |

| Junction Temperature (T <sub>J-MAX</sub> )      | 125°C                          |

| Storage Temperature Range                       | -65°C to +150°C                |

| Maximum Lead Temperature<br>(Soldering)         | (Note 4)                       |

| ESD Rating (Note 5)                             |                                |

| Human Body Model:                               | 2 kV                           |

| Machine Model:                                  | 200V                           |

|                                                 |                                |

#### **Operating Ratings** (Notes 1, 2)

| V <sub>DD</sub>                             | 2.7 to 5.5V     |

|---------------------------------------------|-----------------|

| Recommended Charge Pump                     |                 |

| Load Current I <sub>OUT</sub>               | 0 to 100 mA     |

| Junction Temperature $(T_J)$ Range          | -30°C to +125°C |

| Ambient Temperature (T <sub>A</sub> ) Range |                 |

| (Note 6)                                    | -30°C to +85°C  |

| <b>Fhermal Properties</b>                   |                 |

| Junction-to-Ambient Thermal                 |                 |

| Resistance ( $\theta_{JA}$ ), TMD20 Package |                 |

(Note 7) 50 - 90°C/W Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), YQA24A Package (Note 7) 37 - 90°C/W

#### Electrical Characteristics (Notes 2, 8)

Limits in standard typeface are for  $T_J = 25^{\circ}$ C. Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A < +85^{\circ}$ C). Unless otherwise noted, specifications apply to the LP5521 Block Diagram with: 2.7V  $\leq V_{DD} \leq 5.5$ V,  $C_{OUT} = C_{IN} = 1 \ \mu$ F,  $C_{FLY1} = C_{FLY2} = 0.47 \ \mu$ F. (Note 9).

| Symbol           | Parameter                                               | Condition                                                                     | Min      | Тур  | Max    | Units |

|------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|----------|------|--------|-------|

| I <sub>VDD</sub> | Standby supply<br>current                               | EN = 0 (pin), CHIP_EN = 0 (bit), external 32 kHz clock running or not running |          | 0.2  | 2      | μA    |

|                  |                                                         | EN = 1 (pin), CHIP_EN = 0 (bit), external 32 kHz clock not running            |          | 1.0  |        | μA    |

|                  |                                                         | EN = 1 (pin), CHIP_EN = 0 (bit), external 32 kHz clock running                |          | 1.4  |        | μA    |

|                  | Normal mode                                             | Charge pump and LED drivers disabled                                          |          | 0.25 |        | mA    |

|                  | supply current                                          | Charge pump in 1x mode, no load, LED drivers disabled                         |          | 0.70 |        | mA    |

|                  | Charge pump in 1.5x mode, no load, LED drivers disabled |                                                                               | 1.5      |      | mA     |       |

|                  | Charge pump in 1x mode, no load, LED drivers enabled    |                                                                               | 1.2      |      | mA     |       |

|                  | Powersave mode                                          | External 32 kHz clock running                                                 |          | 10   |        | μA    |

|                  | supply current                                          | Internal oscillator running                                                   |          | 0.25 |        | mA    |

| f <sub>osc</sub> | Internal oscillator<br>frequency accuracy               |                                                                               | -4<br>-7 |      | 4<br>7 | %     |

#### Charge Pump Electrical Characteristics (Note 10)

| Symbol           | Parameter                                                          | Condition                                                       | Min | Тур  | Max | Units |

|------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|-----|------|-----|-------|

| R <sub>OUT</sub> | Charge pump output resistance                                      | Gain = 1.5x                                                     |     | 3.5  |     | Ω     |

|                  |                                                                    | Gain = 1x                                                       |     | 1    |     | Ω     |

| f <sub>sw</sub>  | Switching frequency                                                |                                                                 |     | 1.25 |     | MHz   |

|                  |                                                                    |                                                                 | -7  |      | 7   | %     |

| I <sub>GND</sub> | Ground current                                                     | Gain = 1.5x                                                     |     | 1.2  |     | mA    |

|                  |                                                                    | Gain = 1x                                                       |     | 0.5  |     | mA    |

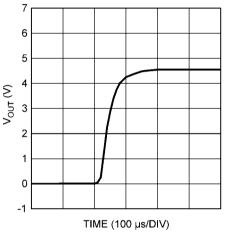

| t <sub>on</sub>  | V <sub>OUT</sub> turn-on time from charge pump<br>off to 1.5x mode | V <sub>DD</sub> = 3.6V, CHIP_EN = H<br>I <sub>OUT</sub> = 60 mA |     | 100  |     | μs    |

| V <sub>OUT</sub> | Charge pump output voltage                                         | $V_{DD} = 3.6V$ , no load, Gain = 1.5x                          |     | 4.55 |     | V     |

| Symbol               | Parameter                     | Condition                                                  |                                                       | Min                   | Гур Мах             | Units |

|----------------------|-------------------------------|------------------------------------------------------------|-------------------------------------------------------|-----------------------|---------------------|-------|

| LEAKAGE              | R, G, B pin leakage current   |                                                            |                                                       |                       | 0.1 <b>1</b>        | μA    |

| MAX                  | Maximum Source Current        | Outputs R, G, B                                            |                                                       | 2                     | 25.5                | mA    |

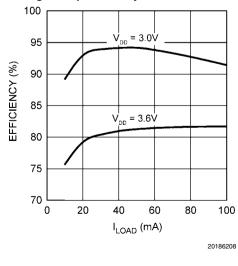

| I <sub>OUT</sub>     | Accuracy of output current    | Output current set to 17.5 mA, V                           | Output current set to 17.5 mA, V <sub>DD</sub> = 3.6V |                       | 4<br>5              | %     |

| I <sub>MATCH</sub>   | Matching (Note 11)            | I <sub>OUT</sub> = 17.5 mA, V <sub>DD</sub> = 3.6V         |                                                       |                       | 1 2                 | %     |

| f <sub>LED</sub>     | LED PWM switching frequency   |                                                            |                                                       |                       | 558                 | Hz    |

|                      |                               | PWM_HF = 0<br>Frequency defined by 32 kHz clo<br>external) | 2                                                     | 256                   | Hz                  |       |

| V <sub>SAT</sub>     | Saturation voltage (Note 12)  | I <sub>OUT</sub> set to 17.5 mA                            |                                                       |                       | 50 100              | mV    |

| Symbol<br>LOGIC IN   | Parameter<br>PUT EN           | Conditions                                                 | Min                                                   | Тур                   | Max                 | Units |

| -                    |                               | Conditions                                                 | IVIIII                                                | тур                   | IVIAX               | Units |

| V <sub>IL</sub>      | Input Low Level               |                                                            |                                                       |                       | 0.5                 | V     |

| V <sub>IH</sub>      | Input High Level              |                                                            | 1.2                                                   |                       |                     | V     |

| I <sub>I</sub>       | Logic Input Current           |                                                            | -1.0                                                  |                       | 1.0                 | μA    |

| t <sub>DELAY</sub>   | Input delay                   |                                                            |                                                       | 2                     |                     | μs    |

| LOGIC IN             | PUT SCL, SDA, TRIG, CLK_32K   |                                                            |                                                       |                       |                     |       |

| V <sub>IL</sub>      | Input Low Level               |                                                            |                                                       |                       | 0.2xV(EN)           | V     |

| V <sub>IH</sub>      | Input High Level              |                                                            | 0.8xV(EN)                                             |                       |                     | V     |

| l <sub>i</sub>       | Input Current                 |                                                            | -1.0                                                  |                       | 1.0                 | μA    |

| f <sub>CLK_32K</sub> | Clock frequency               |                                                            |                                                       | 32                    |                     | kHz   |

| f <sub>SCL</sub>     | Clock frequency               |                                                            |                                                       |                       | 400                 | kHz   |

| LOGIC OL             | JTPUT SDA, TRIG, INT          |                                                            |                                                       |                       |                     |       |

| V <sub>OL</sub>      | Output Low Level              | I <sub>OUT</sub> = 3 mA (pull-up current)                  |                                                       | 0.3                   | 0.5                 | V     |

| I <sub>L</sub>       | Output Leakage Current        |                                                            |                                                       |                       | 1.0                 | μA    |

| LOGIC IN             | PUT ADDR_SEL0, ADDR_SEL1      |                                                            |                                                       |                       |                     |       |

| V <sub>IL</sub>      | Input Low Level               |                                                            |                                                       |                       | 0.2xV <sub>DD</sub> | V     |

| V <sub>IH</sub>      | Input High Level              |                                                            | 0.8xV <sub>DD</sub>                                   |                       |                     | V     |

| I <sub>I</sub>       | Input Current                 |                                                            | -1.0                                                  |                       | 1.0                 | μA    |

| LOGIC OI             | JTPUT GPO, INT (in GPO state) |                                                            |                                                       |                       |                     |       |

| V <sub>OL</sub>      | Output Low Level              | I <sub>OUT</sub> = 3 mA                                    |                                                       | 0.3                   | 0.5                 | V     |

| V <sub>OH</sub>      | Output High Level             | I <sub>OUT</sub> = -2 mA                                   | V <sub>DD</sub> - 0.5                                 | V <sub>DD</sub> - 0.3 |                     | ٧     |

|                      |                               |                                                            |                                                       |                       |                     |       |

## LP5521

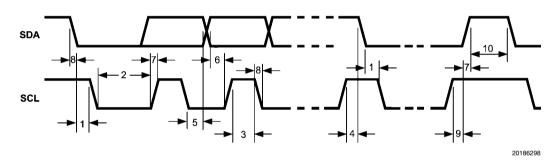

### STAC Timing Parameters (SDA, SCL) (Note 13)

| Cumbal           | Deventer                                           | Lim                  | Limit |       |

|------------------|----------------------------------------------------|----------------------|-------|-------|

| Symbol           | Parameter                                          | Min                  | Max   | Units |

| f <sub>SCL</sub> | Clock Frequency                                    |                      | 400   | kHz   |

| 1                | Hold Time (repeated) START Condition               | 0.6                  |       | μs    |

| 2                | Clock Low Time                                     | 1.3                  |       | μs    |

| 3                | Clock High Time                                    | 600                  |       | ns    |

| 4                | Setup Time for a Repeated START Condition          | 600                  |       | ns    |

| 5                | Data Hold Time                                     | 50                   |       | ns    |

| 6                | Data Setup Time                                    | 100                  |       | ns    |

| 7                | Rise Time of SDA and SCL                           | 20+0.1C <sub>b</sub> | 300   | ns    |

| 8                | Fall Time of SDA and SCL                           | 15+0.1C <sub>b</sub> | 300   | ns    |

| 9                | Set-up Time for STOP condition                     | 600                  |       | ns    |

| 10               | Bus Free Time between a STOP and a START Condition | 1.3                  |       | μs    |

| C <sub>b</sub>   | Capacitive Load for Each Bus Line                  | 10                   | 200   | pF    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pins.

Note 3: Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 150^{\circ}C$  (typ.) and disengages at  $T_J = 130^{\circ}C$  (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note AN1112 : Micro SMD Wafer Level Chip Scale Package or AN1187 : Leadless Leadframe Package (LLP).

Note 5: The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin. MIL-STD-883 3015.7

**Note 6:** In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 7: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

Note 8: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

Note 9: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

Note 10: Input, output, and fly capacitors should be of the type X5R or X7R low ESR ceramic capacitor.

Note 11: Matching is the maximum difference from the average of the three output's currents.

Note 12: Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at  $V_{OUT}$  - 1V. Note 13: Guaranteed by design.

#

LED Current vs. Output Pin Headroom Voltage

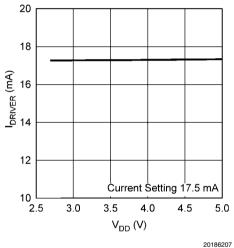

LED Current vs. Supply Voltage

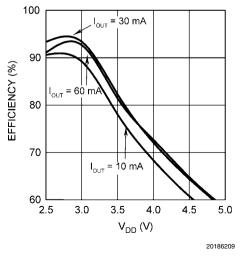

Charge Pump Efficiency vs. Input Voltage 1.5x Mode

LP5521

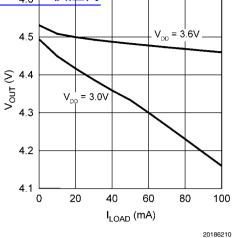

Charge Pump Output Voltage vs. Load Current 查询"LP5524.5M"供应商

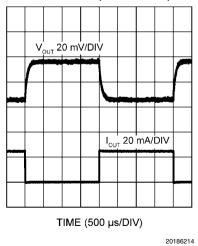

Charge Pump Load Transient Response in 1.5x Mode (0 to 25.5 mA)

20186211

Charge Pump Startup in 1.5x Mode No Load

20186213

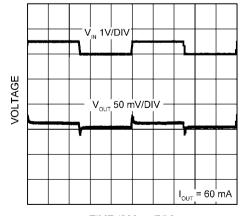

Charge Pump Line Transient Response 1.5x Mode (V\_{IN} 3.5V to 4.0V)

TIME (200 µs/DIV)

20186215

For full LP5521 datasheet please contact nearest National Semiconductor sales office.

查询"LP5521TM"供应商

## Notes

查询"LP5521TM"供应商

### Notes

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560