| <                                       |                     |                  |                |          | =        |                      |      |             |              | -    |       |             |      |          |             |             |      | · Parksahler en |      |    |

|-----------------------------------------|---------------------|------------------|----------------|----------|----------|----------------------|------|-------------|--------------|------|-------|-------------|------|----------|-------------|-------------|------|-----------------|------|----|

|                                         | r                   |                  | ·              |          |          | ···                  |      | R           | EVIS         | IONS |       |             | 1    |          |             |             | Т    |                 |      |    |

| LTR<br>查询                               | 506                 | 0-006.           | <b>7</b> Ω∩1 N | <u> </u> | D<br>'供应 | ESCR                 | IPTI | ON          |              |      |       |             | I    | ATE      | (YR-M       | )-DA)       | ļ    | APPR            | OVED | )  |

| 므                                       | J302                | 2-300            | 70011          | VIV.     | 六四       | . ( <del>***</del> ) |      |             |              |      |       |             |      |          |             |             |      |                 |      |    |

|                                         |                     |                  |                |          |          |                      |      |             |              |      |       |             | •    |          |             |             | •    |                 |      |    |

| REV                                     |                     |                  |                |          |          |                      |      |             |              |      |       |             |      | <u> </u> |             |             |      |                 |      |    |

| SHEET                                   |                     |                  |                |          |          |                      |      |             |              |      |       |             |      |          |             |             |      |                 |      |    |

| REV                                     |                     |                  |                |          |          |                      |      |             |              |      |       |             |      |          |             |             |      |                 |      |    |

| SHEET                                   | 15                  | 16               | 17             | 18       | 19       | 20                   | 21   | 22          | 23           | 24   | 25    | 26          | 27   | 28       |             |             |      |                 |      |    |

| REV STAT                                |                     |                  |                | RE       | V        |                      |      |             |              |      |       |             |      |          |             |             |      |                 |      |    |

| OF SHEET                                | ·<br>               |                  |                | SH       | EET      |                      | 1    | 2           | 3            | 4    | 5     | 6           | 7    | 8        | 9           | 10          | 11   | 12              | 13   | 14 |

| PMIC N/A                                | -                   |                  |                | PREP     | ARED B   |                      | K    | )<br>une l  | 1            | DE   | EFENS |             |      |          | S SU<br>HIO |             | CENT | r <b>e</b> r    |      |    |

|                                         | ARDI<br>ITAF<br>WIN | Υ                |                | - O      |          | na                   | - M  | ./6         |              | MTC  | יפטרי | <del></del> |      | ·        | <u></u>     |             | CMOS | . 1,            | 6 DI | m  |

| THIS DRAWIN<br>FOR USE BY A<br>AND AGEN | LL DEF              | PARTMEI<br>F THE | NTS            | 1/2      | OVED B   | PROVAL               | DATE | 1/2         | <del>J</del> |      |       |             |      |          |             |             | HIC  |                 |      |    |

| DEPARTMEN<br>Amsc n/A                   | T OF D              | EFENSE           |                | •        | 92-0     | 8-05                 |      | <del></del> |              | SIZ  | E     |             | E CO |          |             | 59          | 962- | 9067            | 78   |    |

|                                         |                     |                  |                |          |          |                      |      |             |              | SHE  | ET    | ·           |      |          | <u> </u>    | <del></del> |      |                 |      | ,  |

### SCOPE

- 1.1 Scope. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes B, Q, and M) and space application (device reliables Quand W) Name a thousand lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of radiation hardness assurance (RHA) levels are reflected in the PIN.

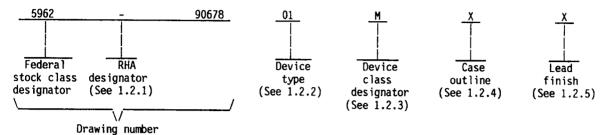

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes M, B, and S RHA marked devices shall meet the MIL-M-38510 specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>    | f <u>clk</u> |

|-------------|----------------|----------------------------|--------------|

| 01          | 80C286-10      | 16-bit CMOS microprocessor | 10 MHz       |

| 02          | 80C286-12      | 16-bit CMOS microprocessor | 12.5 MHz     |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

| <u>Device class</u> | <u>Device requirements documentation</u>                                                                                |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| М                   | Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883 |

| B or S              | Certification and qualification to MIL-M-38510                                                                          |

| Q or V              | Certification and qualification to MIL-I-38535                                                                          |

1.2.4 <u>Case outline(s)</u>. For device classes M, B, and S, case outline(s) shall meet the requirements in appendix C of MIL-M-38510 and as listed below. For device classes Q and V, case outline(s) shall meet the requirements of MIL-I-38535, appendix C of MIL-M-38510, and as listed below.

| Outline letter | <u>Case outline</u>                                                  |

|----------------|----------------------------------------------------------------------|

| X              | P-AC (68-pin 1.180" x 1.180" x .345"), pin grid array package        |

| Υ              | See figure 1 (68-terminal, .970" x .970" x .115"), quad flat package |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-M-38510 for classes M, B, and S or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-90678 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 2    |

1.3 Absolute maximum ratings. 1/ Input, output or I/O voltage applical range - - - - - - - - -1.0 V dc to V<sub>CC</sub> +1.6 V dc Junction temperature (3-) -----+150°C Lead temperature (soldering, 10 seconds) - - - - - 275°C Power dissipation (PD) --------Thermal resistance, junction-to-case (Ojc): See MIL-M-38510, appendix C Case Y - - - - - 9.5°C/W 1.4 Recommended operating conditions. Supply voltage range (V<sub>CC</sub>) - - - - - - - +4.5 V dc to +5.5 V dc Input rise and fall time (from 0.8 V to 2.0 V): Device type 01 ----- 10 ns maximum Device type 02 ---- 8.0 ns maximum 1.5 Digital logic testing for device classes Q and Y. Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012) ---- XX percent 2/ 2. APPLICABLE DOCUMENTS 2.1 Government specifications, standards, bulletin, and handbook. Unless otherwise specified, the following specifications, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein. **SPECIFICATIONS MILITARY** MIL-n-38510 - Microcircuits, General Specialication for. MIL-1-38535 - Integrated Circuits, Monufacturing, General Specification for. **STANDARDS** MILITARY MIL-STD-480 Configuration Control-Engineering Changes, Deviations and Waivers. MIL-STD-883 - Test Methods and Procedures for Microelectronics. BULLETIN **MILITARY** MIL-BUL-103 - List of Standardized Military Drawings (SMD's). HANDBOOK MILITARY MIL-HDBK-780 - Standardized Military Drawings. (Copies of the specifications, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.) Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability. 2/ Values will be added when they become available. STANDARDIZED SIZE 5962-90678 MILITARY DRAWING A DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL

SHEET

3

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

###

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. For device classes B and S, a full electrical characterization table for each device type shall be included in this SMD. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V and herein.

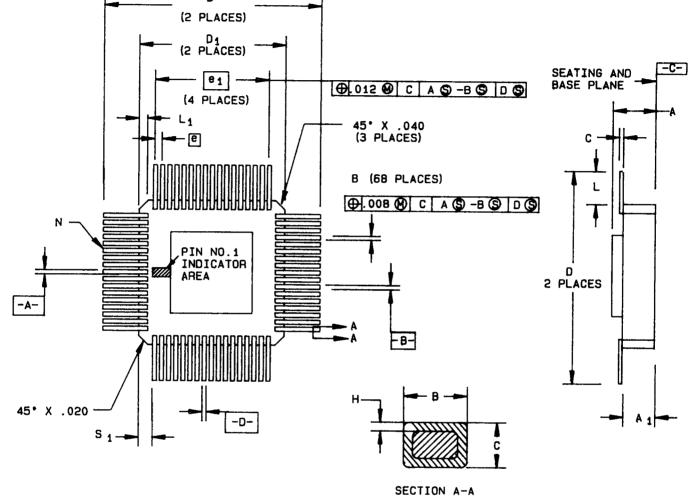

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

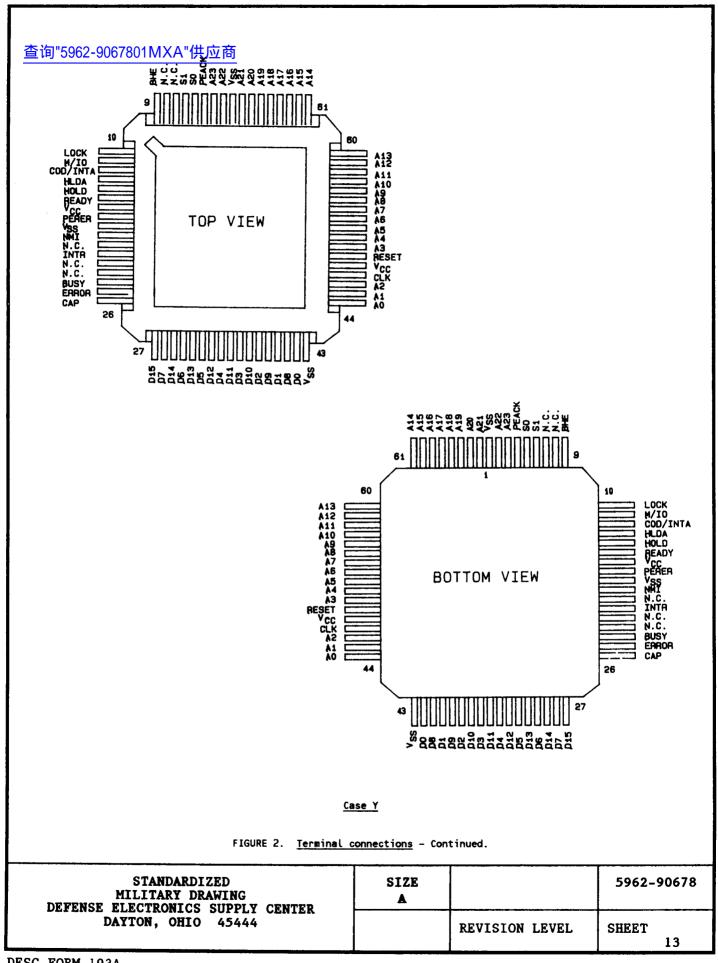

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

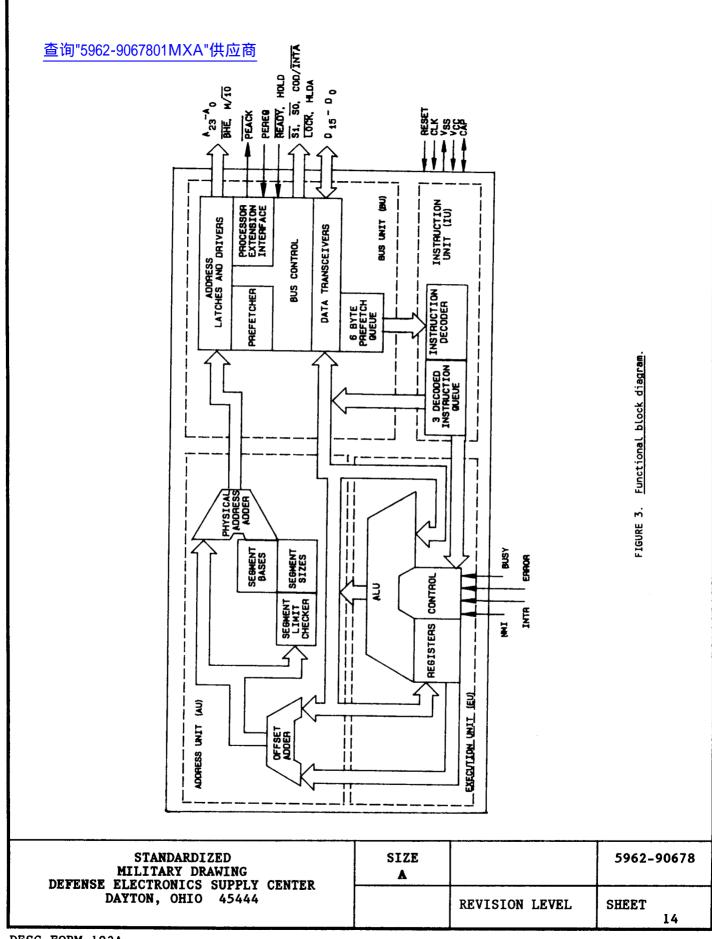

- 3.2.3 Functional block diagram. The functional block diagram shall be as specified on figure 3.

- 3.2.4 Radiation exposure circuit. The radiation exposure circuit shall be specified when available.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes B and S shall be in accordance with MIL-M-38510. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes B and S shall be a "J" or "JAN" as required in MIL-M-38510. The certification mark for device classes Q and V shall be a "QML" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.3 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.2 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or device classes B and S in MIL-M-38510 or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DESC-ECC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-480.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device classes M, B, and S</u>. Device classes M, B, and S devices covered by this drawing shall be in microcircuit group number 105 (see MIL-M-38510, appendix E).

- 3.11 <u>Serialization for device class S</u>. All device class S devices shall be serialized in accordance with MIL-M-38510.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90678 |

|-----------------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL | SHEET<br>4 |

### TABLE I. <u>Electrical performance characteristics</u>.

| Test                                                  | Symbol           | Group A                                                                                          | Device                      | Li_Li                | Unit                       |                                   |                             |

|-------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------------|-----------------------------------|-----------------------------|

| )                                                     |                  | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>unless otherwise specified | subgroups<br> <br>          | type                 | Min                        | Max                               | <br> <br>                   |

| Input low voltage                                     | V <sub>IL</sub>  | V <sub>CC</sub> = 4.5 V<br>f = 2 MHz                                                             | <br>  1,2,3<br>             | <br>  All<br>        | -0.5                       | 0.8                               | <br>  <b>v</b><br>          |

| Input high volt <b>age</b>                            | v <sub>IH</sub>  | V <sub>CC</sub> = 5.5 V<br>f = 2 MHz                                                             | <u> </u><br>                | <br> <br>            | 2.0                        | v <sub>cc</sub> +                 | <br> <br>                   |

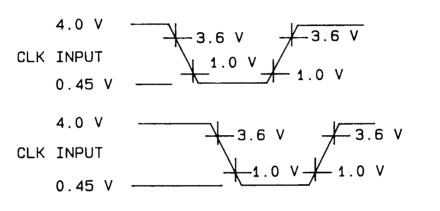

| CLK input low<br>voltage                              | VILC             | V <sub>CC</sub> = 4.5 V<br>f = 2 MHz                                                             | <br> <br>                   | <br> <br> <br>       | -0.5<br>                   | 1.0<br> <br>                      | <br>                        |

| CLK input high<br>voltage                             | v <sub>IHC</sub> | V <sub>CC</sub> = 5.5 V<br>  f = 2 MHz                                                           | †<br> <br> -<br>            | <br> <br> <br>       | 3.6                        | <br> V <sub>CC</sub> +<br>  0.5 v | !<br>!<br>                  |

| Output low voltage                                    | v <sub>oL</sub>  | $ I_{OL} = 2.0 \text{ mA} $ $2/$ $ V_{CC} = 4.5 \text{ V}$                                       | <br> <br> <br> <br>         | ;<br> <br> <br> <br> |                            | 0.45                              | <br> <br> <br> <br>         |

| Output high voltage                                   | V <sub>OH</sub>  | I <sub>OH</sub> = -2.0 mA                                                                        | <u> </u><br> <br> <br> <br> |                      | 3.0                        |                                   | <u> </u><br> <br> <br> <br> |

|                                                       | <br> <br>        | I <sub>OH</sub> = -100 μA <u>2</u> /<br>V <sub>CC</sub> = 4.5 V                                  | <br> <br> <br>              | <br> <br>            | V <sub>CC</sub> -<br>0.5 V |                                   |                             |

| Input leakage<br>current                              | IIL              | V <sub>CC</sub> = 5.5 V, <u>2</u> /<br>  measured on pins:<br>  29, 31, 57, 59, 61, 63, and 64   |                             | <br> <br> <br> <br>  | <br>  -10<br>              | <br>  +10<br>                     | μΑ                          |

| Input sustaining<br>current<br>(bus hold low)         | I IBHL           | v <sub>IN</sub> = 1.0 v <u>3</u> /                                                               |                             | <br> <br> <br>       | 35<br> <br>                | <br>  200<br>                     | <del> </del>                |

| Input sustaining<br>current<br>(bus hold high)        | I <sub>BHH</sub> | V <sub>IN</sub> = 3.0 V <u>4</u> /                                                               | -<br> <br> <br> <br> <br>   |                      | -50                        | <br>  -400<br>                    |                             |

| Input sustaining<br>current on BUSY<br>and ERROR pins | IsL              | v <sub>IN</sub> = 0.0 v <u>5</u> /                                                               | †<br> -<br> -<br> -         | <br> <br> <br>       | <br>  -30<br>              | -500                              | <u> </u><br>                |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-90678 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>5 |

| 查请\$5962-9067                                                         | <br>                        | 供应商。Condit                                                                                               | ions <u>1</u> /                                                                                                | Group A                  | Device | Limits        |                | ⊥ Unit                |  |

|-----------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|--------|---------------|----------------|-----------------------|--|

| 查询 <sup>\$\$</sup> 5962-9067                                          |                             | 4.5 V ≤ V <sub>CC</sub><br>unless otherw                                                                 | ≤ +125°C<br>≤ 5.5 V<br>ise specified                                                                           | subgroups                | type   | <br>  Min<br> | <br>  Max<br>  |                       |  |

| Bus hold low<br>overdrive                                             | I<br>BHLO                   | $\begin{vmatrix} v_{CC} = 5.5 \text{ V} & \underline{6} \\ v_{IN} = 5.5 \text{ V or } 0. \end{vmatrix}$  | /<br>0 <b>v</b>                                                                                                | 1,2,3                    | ALL    | 250<br>       | <br> <br> <br> | μΑ                    |  |

| Bus hold high overdrive                                               | <br>  <sup>I</sup> внно<br> |                                                                                                          |                                                                                                                |                          |        | -420<br>      |                |                       |  |

| Output leakage<br>current                                             | I I <sub>LO</sub>           | V <sub>OUT</sub> = 0.0 V or 5<br>  V <sub>CC</sub> = 5.5 V, meas<br>  pins 1, 7, 8, 1<br>  32, 33 and 34 | .5 V,<br>ured on<br>0 through 28,                                                                              | <br> <br> <br> <br> <br> |        | -10           | +10            |                       |  |

| Active power<br>supply current                                        | Icc                         | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 2.4 V or<br>0.40 V, outputs                                 | <br>  f = 10 MHz                                                                                               |                          | 01     |               | 200            | m.A                   |  |

|                                                                       | <br> <br> <br>              | 0.40 V, outputs<br>  unloaded<br>  C <sub>L</sub> = 100 pF                                               | <br>  f = 12.5 MHz<br>                                                                                         |                          | 02     |               | <br>  220<br>  |                       |  |

| Standby power<br>supply current                                       | l Iccs                      | <br> V <sub>CC</sub> = 5.5 V, V <sub>IN</sub><br> 5.5 V, outputs un                                      | = 0.0 V or<br>loaded <u>7</u> /                                                                                |                          | ALL    |               | <br>  5.0<br>  |                       |  |

| Clk input<br>capacitance                                              | <br>  <sup>C</sup> CLK      | <br> f <sub>CLK</sub> = 1.0 MHz,<br> see 4.4.1c                                                          |                                                                                                                | 4                        |        |               | <br>  20<br>   | pF                    |  |

| Other input<br>capacitance                                            | c <sub>IN</sub>             |                                                                                                          |                                                                                                                |                          |        |               | 10             | - <del></del>         |  |

| Input/output<br>capacitance                                           | c <sub>o</sub>              | <del>-</del><br> <br> <br>                                                                               |                                                                                                                |                          |        |               | 20             |                       |  |

| Functional tests                                                      |                             |                                                                                                          |                                                                                                                | 7, 8                     | 1      | <br>          | <br> <br>      |                       |  |

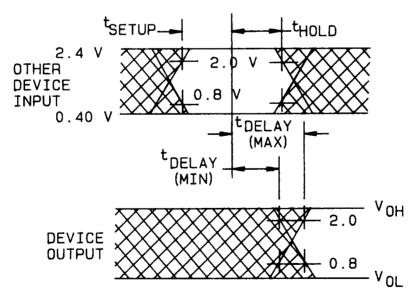

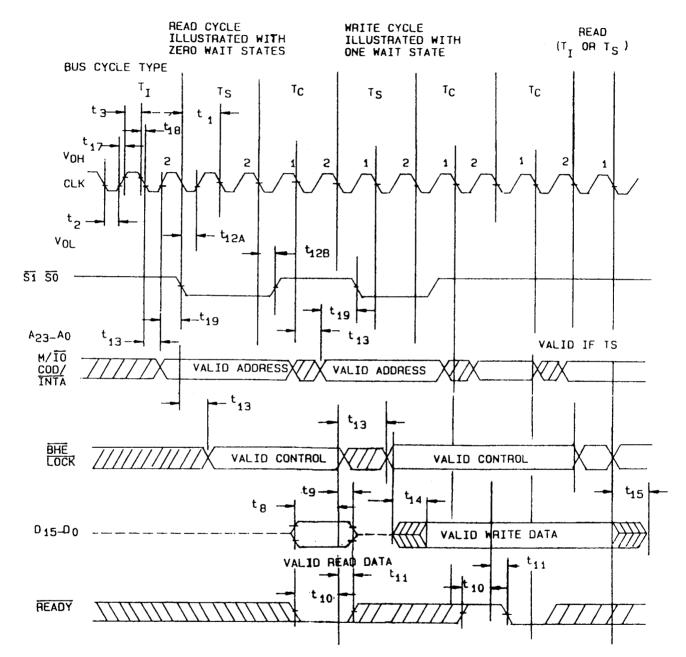

| System clock period                                                   | <br>  t <sub>1</sub>        | <br> See figure 3                                                                                        |                                                                                                                | 9,10,11                  | 01     | 50            |                | ns                    |  |

|                                                                       | <br> <br>                   |                                                                                                          | MAN mile de la companya de la compa |                          | 02     | 40            |                | •                     |  |

| System clock low<br>time                                              | t <sub>2</sub>              | <br> Measured between the 1.0 V<br> reference points on the<br> clock input, see figure 3                |                                                                                                                |                          | 01     | 12            |                | <br> <br><del> </del> |  |

|                                                                       | 1                           | <br>                                                                                                     | gu. c 3                                                                                                        |                          | 02     | 11            | <u> </u><br>   | <u> </u>              |  |

| See footnotes at end o                                                | f table.                    |                                                                                                          |                                                                                                                |                          |        |               |                |                       |  |

| STANDARDIZED<br>MILITARY DRAWING                                      |                             | i                                                                                                        | ZE                                                                                                             |                          |        | 59            | 62-90678       |                       |  |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                             |                                                                                                          | R                                                                                                              |                          |        | ON LEVEL S    |                | HEET                  |  |

| 查询"5962-906780<br>Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 川MXA"1共<br>Symbol | Conditions 1/                                                                                          | Group A                 | <br>  Device        | Limits       |           | <br>  Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|-------------------------|---------------------|--------------|-----------|------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | $-55^{\circ}C \le T_{C} \le +125^{\circ}C^{-}$ $4.5 V \le V_{CC} \le 5.5 V$ unless otherwise specified | subgroups               | type                | Min          | <br>  Max | <u> </u>   |

| System clock high time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>3</sub>    |                                                                                                        | reference points on the |                     | <br>  16<br> | <br>      | ns         |

| PARTITION AND ADDRESS OF THE PARTITION ADDRESS OF THE PARTITION AND ADDRES |                   |                                                                                                        |                         | <br>  02<br>        | 13           | <br> <br> |            |

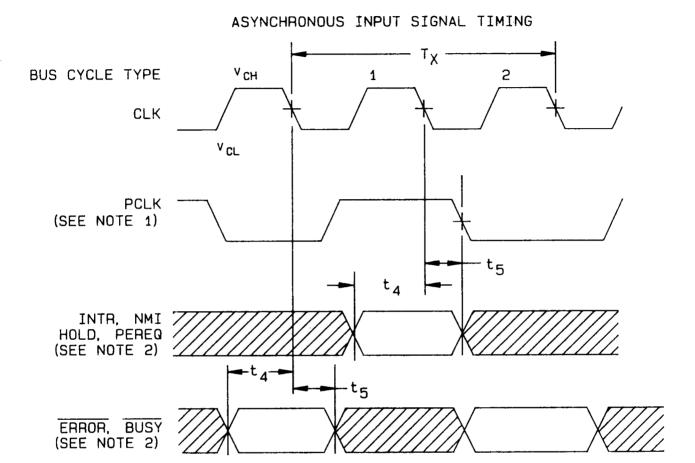

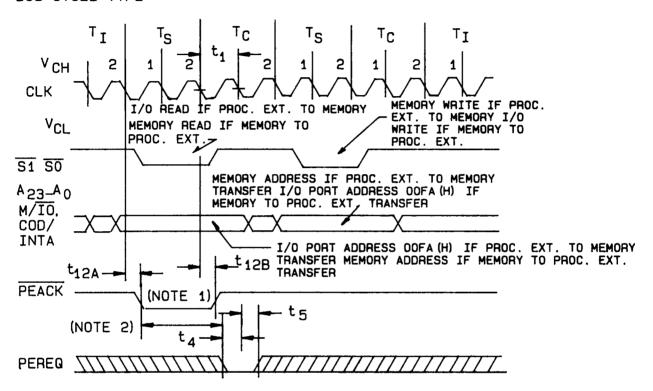

| Asynchronous input setup time <u>8</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>4</sub>    | <br> See figure 3                                                                                      | <br> <br>               | 01                  | <br>  20<br> |           | <u> </u>   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                                                        | <br>  02<br>            | <br>  15<br>        | <br> <br>    |           |            |

| Asynchronous input   t <sub>5</sub>   hold time <u>8</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 01                                                                                                     | 20                      | <br>                | <u> </u>     |           |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | †<br> <br>                                                                                             |                         | <br>  <b>02</b><br> | 15           | <br> <br> |            |

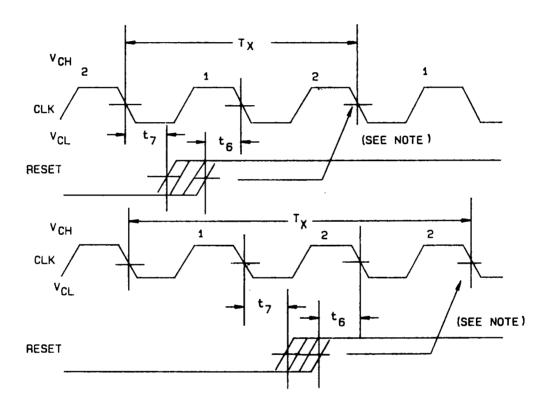

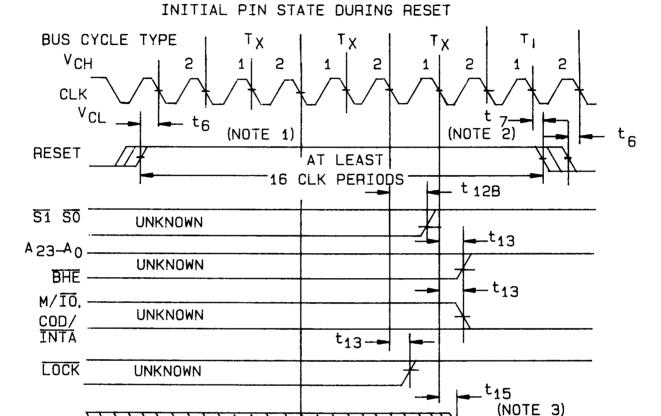

| RESET setup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | t <sub>6</sub>    | <br>                                                                                                   |                         | 01                  | 23           |           |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | <del> </del>                                                                                           |                         | <br>  02<br>        | <br>  10<br> | <br> <br> |            |

| RESET hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>7</sub>    |                                                                                                        |                         | ALL                 | 5            |           | 1          |

| Read data setup<br>time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>8</sub>    |                                                                                                        |                         | 01                  | 8            | <br> <br> | <br>       |

| İ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | <br> <br>                                                                                              |                         | 02                  | <br>  5<br>  | <br> <br> | <br> <br>  |

| Read data hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>9</sub>    | -<br> <br> <br>                                                                                        |                         | 01                  | 8            |           |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                                                        |                         | 02                  | 4            |           |            |

| READY setup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | t <sub>10</sub>   | <del> </del><br>                                                                                       |                         | 01                  | 26           |           |            |

See footnotes at end of table.

t<sub>11</sub>

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90678 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 7    |

02

01

02

20

25

20

READY hold time

### TABLE I. <u>Electrical performance characteristics</u> - Continued.

| <b>李语‱</b> 062-0067                   | SYMBOL           | (世成茂 Conditions 1/                                                                                                                                      | Group A   | Device        | <u>Li</u>               | mits      | i Unit       |

|---------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-------------------------|-----------|--------------|

| 旦问 5302-3007                          | <br> <br>        | Conditions <u>1</u> /<br>供应商 <sub>5°C</sub> ≤ T <sub>C</sub> ≤ +125°C<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>unless otherwise specified                  | subgroups | type          | <br>  Min<br>           | Max       | <u> </u>     |

| Status/PEACK<br>active delay          | t <sub>12a</sub> | <br> C <sub>L</sub> = 100 pF,<br> I <sub>L</sub> = 2.0 mA,<br> See figure 3                                                                             | 9,10,11   | 01            | <br>  5 <u>13</u> /<br> | 22        | ns           |

| <u>9</u> /                            |                  |                                                                                                                                                         |           | 02            | 1                       | 21        | <br> -       |

| Status/PEACK<br>inactive delay        | t <sub>12b</sub> |                                                                                                                                                         |           | <br>  01<br>  | 3 <u>13</u> /           | 30        | <u> </u>     |

| <u>10</u> /                           |                  | <u> </u>                                                                                                                                                |           | 02            | <br>  1<br>             | 24        | <u> </u><br> |

| Address valid delay <u>11</u> /       | <sup>t</sup> 13  |                                                                                                                                                         | 01        | 4 <u>13</u> / | 35                      | 35        |              |

|                                       |                  |                                                                                                                                                         |           | 02            | <br>  1<br>             | 32        | <u> </u>     |

| Write data valid<br>delay <u>11</u> / | t <sub>14</sub>  |                                                                                                                                                         | 01        | 3 <u>13</u> / | 40                      | <br>      |              |

|                                       | <u> </u>         |                                                                                                                                                         | <u> </u>  | 02            | 0                       | 31        | 1            |

| Address/status/data<br>float delay    | t <sub>15</sub>  | See figure 3<br> I <sub>L</sub> = -6.0 mA (V <sub>OH</sub> to float)<br> I <sub>L</sub> = 8.0 mA (V <sub>OL</sub> to float)<br> C <sub>L</sub> = 100 pF |           | 01            | 2 13/                   | 47        | <del> </del> |

| 12/ 13/                               |                  | c                                                                                                                                                       | <u> </u>  | 02            | 0                       | 32        |              |

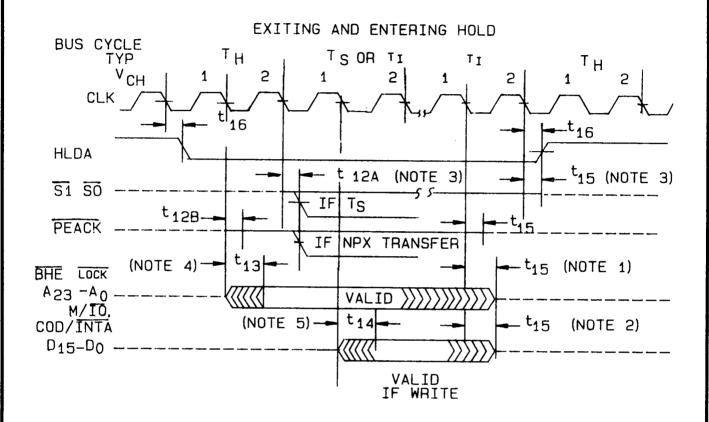

| HLDA valid delay<br><u>14</u> /       | <sup>t</sup> 16  | c <sub>L</sub> = 100 pF,<br>  i <sub>L</sub> = 2.0 mA,                                                                                                  |           | 01            | 3 <u>13</u> /           | 47        | <u> </u>     |

|                                       |                  | See figure 3                                                                                                                                            | 1         | 02            | 0                       | 25        | 1            |

| System CLK rise time                  | t <sub>17</sub>  | 1.0 V to 3.6 V <u>6</u> / <u>13</u> /                                                                                                                   |           | All<br>       |                         | 8         | <u> </u>     |

| System CLK fall time                  | <sup>t</sup> 18  | 3.6 V to 1.0 V <u>6</u> / <u>13</u> /                                                                                                                   | <u> </u>  | All<br>       | <br> <br>               | 8         | <u> </u>     |

| Address valid to status setup time    | t <sub>19</sub>  | <br> C <sub>L</sub> = 100 pF,<br> I <sub>L</sub> = 2.0 mA,<br> See figure 3                                                                             |           | 01            | 27                      | <u> </u>  |              |

| <u>13</u> / <u>15</u> /               |                  | See figure 3                                                                                                                                            |           | 02            | 20                      | <br> <br> | <br> -<br> - |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90678 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>8 |

### TABLE I. <u>Electrical performance characteristics</u> - Continued.

- 暨间時962149(16780141√4)/(全人は大好) 商。 BHE, BUSY, ERROR, INTA of COD/INTA, LOCK, PEACK, SO, SI, READY.

Unless otherwise specified all test conditions shall be at worst case condition.

- $\underline{2}$ /  $V_{IN}$  = 0.8 V, 2.0 V. Relaxed input levels for  $V_{OL}$  and  $V_{OH}$  may be used if separate  $V_{IL}$  and  $V_{IH}$  tests (guaranteeing threshold voltage transmission) are performed.

- 3/ I  $_{

m BHL}$  should be measured after lowering V  $_{

m IN}$  to GND and then raising to 1.0 V on the following pins: 36 through 51, 66 and 67.

- $\underline{4}$ / I<sub>BHH</sub> should be measured after raising V<sub>IN</sub> to V<sub>CC</sub> and then lowering to 3.0 V on the following pins: 4, 5, 6, 36 through 51, 66, 67 and 68.

- 5/ I<sub>IL</sub> should be measured after raising V<sub>IN</sub> to V<sub>CC</sub> and then lowering to 0.0 V on pins 53 and 54.

- 6/ If not tested then guaranteed to the limits specified in table I.

- $\mathcal{U}$   $I_{CCS}$  should be tested with the clock stopped in phase two of the processor clock cycle.

- 8/ Asynchronous inputs are INTR, NMI, HOLD, PEREQ, ERROR and BUSY. This specification is given only for testing purposes to assure recognition of a specific CLK edge.

- 9/ Delay from 1.0 V on the CLK to 1.5 V for minimum (HOLD time) and to 1.5 V for maximum (active delay).

- 10/ Delay from 1.0 V on the CLK to 1.5 V for minimum (HOLD time) and to 1.5 V for maximum (inactive delay).

- 11/ Delay from 1.0 V on the CLK to 1.5 V.

- 12/ Delay from 1.0 V on the CLK to float (no current drive) condition.

- 13/ Tested initially and at process and design changes. Thereafter guaranteed, if not tested, to the limits specified in table I.

- 14/ Delay from 1.0 V on the CLK to 1.5 V.

- 15/ Delay measured from address either reaching 1.5 V (valid) to status going active reaching 0.8 V or status going inactive reaching 1.5 V.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE |                | 5962-90678 |

|-----------------------------------------------------------------|------|----------------|------------|

| DAYTON, OHIO 45444                                              |      | REVISION LEVEL | SHEET 9    |

# 查询"5962-9067801MXA"供应商 (2 PLACES) (2 PLACES) (2 PLACES) (2 PLACES)

FIGURE 1. Case outline Y.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90678  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>10 |

| Symbol                         | Inches   |       | Millim    | eters |

|--------------------------------|----------|-------|-----------|-------|

| <u> </u><br>                   | Min      | Max   | Min       | Max   |

| A                              | .080     | .115  | 2.03      | 2.92  |

| A <sub>1</sub>                 | .070     | .094  | 1.78      | 2.39  |

| В                              | .016     | .021  | 0.41      | 1.53  |

| С                              | .008     | .012  | 0.20      | 0.31  |

| D <sub>1</sub>                 | .926     | .970  | 23.52     | 24.64 |

| е                              | .050 BSC |       | 1.27 BSC  |       |

| [e <sub>1</sub> ]              | .800     | BSC   | 20.32 BSC |       |

| D                              | 1.640    | 1.870 | 41.66     | 47.50 |

| L                              | .350     | . 450 | 8.89      | 11.43 |

| L <sub>1</sub>                 | . 040    | . 060 | 1.02      | 1.52  |

| М                              |          | .0015 |           | 0.038 |

| N                              | 68       |       |           |       |

| N <sub>D</sub> /N <sub>E</sub> | 17       |       |           |       |

| s <sub>1</sub>                 | .050     |       | 1.27      |       |

### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerance for three place decimals is  $\pm .005$ .

- 4. The index feature for terminal 1 identification, optical orientation, or handling purposes shall be within the shaded areas shown on planes 1 and 2. Terminal 1 identification is optional on the surface closet to the seating plane.

- 5. Corner shapes (square notch, radius, etc.) may vary from that shown on the drawing. The irdex corner shall be clearly unique.

- 6. Dimension N: Number of terminals per package edge.

- 7. Dimensioning is in accordance with ANSI Y14.5M 1982.

- 8. Lead coplanarity shall be within .004 inch (0.10 mm) .050 inch (1.27 mm) from package body.

- 9. No overhang of the lead on the braze pad is allowed.

- Dimensions B and C apply to base metal only. Dimension M applies to plating thickness.

The leads on this package style shall be protected from mechanical distortion and damage such that dimensions pertaining to relative lead/body "true positions" and lead "coplanarity" are always maintained until the next higher level package attachment process is complete. Package lead protection mechanisms (tie bars, carriers, etc.) are not shown on the drawing; however, when microcircuit devices contained in this package style are shipped for use in Government equipment, or shipped directly to the Government as spare parts or mechanical qualification samples, lead "true position" and "coplanarity" protection shall be in place.

FIGURE 1. Case outline Y - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-90678  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>11 |

|                                                                                                             |                                                                                                                                                                              | ,                                                                                                            |                                                                                                                       |