# 8-Bit μP-Compatible 12-Bit DAC

**AD7548**

### 1.1 Scope.

This specification covers the detail requirements for a 12-bit monolithic CMOS multiplying digital-to-analog converter for use with 8-bit bus microprocessors. Data is loaded in two bytes, 8+4 (high/low byte), to input holding registers. The complete word is then transferred into the DAC register to update the DAC.

### 1.2 Part Number.

The complete part number per Tables 1 and 2 of this specification is as follows:

| Device | Part Number <sup>1</sup> |

|--------|--------------------------|

| -1     | AD7548S(X)/883B          |

| -2     | AD7548T(X)/883B          |

### NOTE

<sup>1</sup>See paragraph 1.2.3 for package identifier.

### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline:

| ( <b>X</b> ) | Package | Description    |

|--------------|---------|----------------|

| Q            | Q-20    | 20-Pin Cerdip  |

| E            | E-20A   | 20-Contact LCC |

### 1.3 Absolute Maximum Ratings. (T<sub>A</sub> = 25°C unless otherwise noted)

| V <sub>DD</sub> (Pin 18) to DGND                                 |  |  |  |  |  |  |

|------------------------------------------------------------------|--|--|--|--|--|--|

| V <sub>REF</sub> (Pin 19) to AGND                                |  |  |  |  |  |  |

| $V_{RFB}$ (Pin 20) to AGND                                       |  |  |  |  |  |  |

| Digital Input Voltage (Pins 4-17) to DGND0.3V to V <sub>DD</sub> |  |  |  |  |  |  |

| $V_{PIN1}$ , to DGND                                             |  |  |  |  |  |  |

| AGND to DGND                                                     |  |  |  |  |  |  |

| Power Dissipation                                                |  |  |  |  |  |  |

| Up to +75°C                                                      |  |  |  |  |  |  |

| Derates above +75°C                                              |  |  |  |  |  |  |

|                                                                  |  |  |  |  |  |  |

| Operating Temperature Range                                      |  |  |  |  |  |  |

| Operating Temperature Range                                      |  |  |  |  |  |  |

### 1.5 Thermal Characteristics.

Thermal Resistance  $\theta_{JC}=35^{\circ}C/W$  for Q-20 and E-20A  $\theta_{JA}=120^{\circ}C/W$  for Q-20 and E-20A

## AD7548 — SPECIFICATIONS

Table 1.

| 查询"AD7548.                                  | AQ/+"                         | 供应     | Design                             | Sub<br>Group | Sub | Sub<br>Group | Test Condition <sup>1</sup>                                                                                                                     |                  |

|---------------------------------------------|-------------------------------|--------|------------------------------------|--------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Test                                        | Symbol                        | Device | T <sub>min</sub> -T <sub>mex</sub> | 1            | 2,3 | 4            | $V_{DD} = +15V$                                                                                                                                 | Units            |

| Resolution                                  | RES                           | -1,2   | 12                                 |              |     |              |                                                                                                                                                 | Bits             |

| Relative Accuracy                           | RA                            | - 1    | 1                                  | 1            | 1   |              |                                                                                                                                                 | ± LSB max        |

|                                             |                               | -2     | 1/2                                | 1            | 1/2 | 1/2          |                                                                                                                                                 |                  |

| Differential Nonlinearity                   | DNL                           | -1     | 1                                  | 1            | 1   |              | All Grades Guaranteed Monotonic                                                                                                                 | ± LSB max        |

|                                             |                               | -2     | 1/2                                | 1            | 1/2 | 1/2          | to 12 Bits Over Temperature.                                                                                                                    |                  |

| Gain Error <sup>2</sup>                     | A <sub>E</sub>                | -1     | 6                                  | 6            | 6   |              |                                                                                                                                                 | ± LSB max        |

|                                             | 1                             | -2     | 3                                  | 6            | 3   | 3            |                                                                                                                                                 |                  |

| Gain Tempco                                 | dA <sub>E</sub> /dT           | -1,2   | 5                                  |              |     |              |                                                                                                                                                 | ± ppm/°C max     |

| Power Supply Rejection                      | PSRR                          | -1,2   | 0.02                               |              |     |              | $\Delta V_{DD} = \pm 5\%$ .                                                                                                                     | ± %/% max        |

| Output Leakage Current<br>Pin 1             | ,                             | -1,2   | 150                                | 5            | 150 |              | DAC Positor Londod with All On                                                                                                                  | ± nA max         |

|                                             | I <sub>OUT</sub>              | -1,2   | 2                                  | ,            | 130 |              | DAC Register Loaded with All 0's.                                                                                                               |                  |

| Output Current Settling Time                | t <sub>SL</sub>               | -1,2   | 2                                  |              |     |              | $To \pm 1/2 LSB \ of Full Scale Range. \\ I_{OUT} Load = 100\Omega \ and 13pF. \\ DAC Register Alternately Loaded with All 1's and All 0's. \\$ | μs max           |

| Feedthrough Error <sup>3</sup>              | FTE                           | -1,2   | 10                                 |              |     |              | $V_{REF} = \pm 5V$ , 10kHz Sinewave.<br>DAC Register Loaded with All 0's.                                                                       | mV p-p max       |

| Reference Input Resistance<br>Pin 15        | R <sub>I</sub>                | -1,2   | 7                                  | 7            | 7   |              |                                                                                                                                                 | kΩ min           |

|                                             |                               |        | 20                                 | 20           | 20  |              |                                                                                                                                                 | kΩ max           |

| Digital Input High Voltage                  | VIH                           | -1,2   | 2.4                                | 2.4          | 2.4 |              |                                                                                                                                                 | V min            |

| Digital Input Low Voltage                   | $V_{IL}$                      | -1,2   | 0.8                                | 0.8          | 0.8 |              |                                                                                                                                                 | V max            |

| Digital Input Leakage Current               | I <sub>IN</sub>               | 1, 2   | 10                                 | 1            | 10  |              | $V_{IN} = 0V \text{ or } V_{DD}.$                                                                                                               | ±μA max          |

| Digital Input Capacitance                   | Cı                            | -1,2   | 7                                  |              |     |              |                                                                                                                                                 | pF max           |

| Output Capacitance<br>Pin 1                 | C <sub>o</sub>                | -1,2   | 200                                |              |     |              | DAC Register Loaded with All 1's.                                                                                                               | pF max           |

|                                             |                               |        | 100                                |              |     |              | DAC Register Loaded with All 0's.                                                                                                               |                  |

| Supply Current from V <sub>DD</sub>         | I <sub>DD</sub>               | -1,2   | 3                                  | 3            | 3   |              | All Digital Inputs V <sub>IL</sub> or V <sub>IH</sub> .  All Digital Inputs 0 or V <sub>DD</sub> .                                              | mA max<br>mA max |

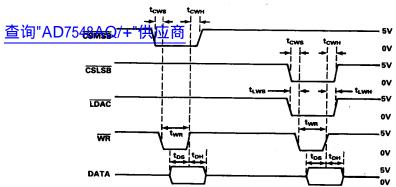

| Data Valid Setup Time <sup>4</sup>          |                               | 1 2    | 230                                | <u> </u>     | 1   |              | UII DIRIGH INDUGAOL ADD                                                                                                                         | ns min           |

| Data Valid Hold Time <sup>4</sup>           | t <sub>DS</sub>               | -1,2   | 50                                 | <u> </u>     |     |              |                                                                                                                                                 | ns min           |

| CSMSB or CSLSB <sup>4</sup>                 | t <sub>DH</sub>               | -1,2   | JU                                 | <u> </u>     |     |              |                                                                                                                                                 | me mm            |

| to WR Setup Time                            | t <sub>CWS</sub>              | -1,2   | 50                                 |              |     |              |                                                                                                                                                 | ns min           |

| CSMSB or CSLSB <sup>4</sup> to WR Hold Time | t <sub>CWH</sub> <sup>4</sup> | -1,2   | 25                                 |              |     |              |                                                                                                                                                 | ns min           |

| LDACto WR Setup Time4                       | tLWS                          | -1,2   | 50                                 |              |     |              |                                                                                                                                                 | ns min           |

| LDAC to WR Hold Time4                       | tLWH                          | -1,2   | 25                                 |              |     |              |                                                                                                                                                 | ns min           |

| Write Pulse Width <sup>4</sup>              | twr                           | -1,2   | 240                                |              |     |              |                                                                                                                                                 | ns min           |

NOTES  $^{1}V_{PIN1} = V_{PIN2} = 0V$ ,  $V_{REF} = +10V$ , unless otherwise noted.  $^{2}Measured$  using internal  $R_{FB}$  and includes effect of leakage current and gain TC.

<sup>&</sup>lt;sup>3</sup>Feedthrough error can be reduced by connecting the metal lid to DGND.

<sup>&</sup>lt;sup>4</sup>Timing per Figure 1.

Table 2.

| Test                                         | Symbol              | Device | <del>Des</del> ign<br>Limit<br>T <sub>min</sub> -T <sub>mex</sub> | Sub<br>Group<br>1 | Sub<br>Group<br>2, 3 | Sub<br>Group<br>4 | Test Condition <sup>1</sup> V <sub>DD</sub> = +5V                                                                                       | Units       |

|----------------------------------------------|---------------------|--------|-------------------------------------------------------------------|-------------------|----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                                              | RES                 | -1,2   | 12                                                                |                   |                      |                   |                                                                                                                                         | Bits        |

|                                              | RA                  | -1     | 1                                                                 | 1                 | 1                    |                   |                                                                                                                                         | ± LSB max   |

| Relative rectaracy                           |                     | -2     | 1/2                                                               | 1                 | 1/2                  | 1/2               |                                                                                                                                         |             |

| Differential Nonlinearity                    | DNL                 | -1     | 1                                                                 | 1                 | 1                    |                   | All Grades Guaranteed Monotonic                                                                                                         | ± LSB max   |

| Differential Noninicality                    | DIVL                | -2     | 1/2                                                               | 1                 | 1/2                  | 1/2               | to 12 Bits Over Temperature.                                                                                                            |             |

| Gain Error <sup>2</sup>                      | A <sub>R</sub>      | -1     | 6                                                                 | 6 .               | 6                    |                   |                                                                                                                                         | ± LSB max   |

| Cam Error                                    | 1.FE                | -2     | 3                                                                 | 6                 | 3                    | 3                 |                                                                                                                                         |             |

| Gain Tempco                                  | dA <sub>E</sub> /dT |        | 5                                                                 | •                 | -                    |                   |                                                                                                                                         | ± ppm/°C ma |

| Power Supply Rejection                       | PSRR                | -1,2   | 0.02                                                              |                   |                      | -                 | $\Delta V_{DD} = \pm 5\%$ .                                                                                                             | ± %/% max   |

|                                              | I SICK              | -1,2   | 0.02                                                              | -                 | <del></del>          |                   | ZVDD ZXXX                                                                                                                               |             |

| Output Leakage Current<br>Pin 1              | LOUT                | -1,2   | 150                                                               | 5                 | 150                  |                   | DAC Register Loaded with All 0's.                                                                                                       | ± nA max    |

| Output Current Settling Time                 | t <sub>SL</sub>     | -1,2   | 2                                                                 |                   |                      |                   | $To \pm 1/2$ LSB of Full Scale Range. $I_{OUT}$ Load = 100 $\Omega$ and 13pF. DAC Register Alternately Loaded with All 1's and All 0's. | μs max      |

| Feedthrough Error <sup>3</sup>               | FTE                 | -1,2   | 10                                                                |                   |                      |                   | $V_{REF} = \pm 5V$ , 10kHz Sinewave.<br>DAC Register Loaded with All 0's.                                                               | mV p-p max  |

| Reference Input Resistance                   | Rı                  |        |                                                                   |                   |                      |                   |                                                                                                                                         |             |

| Pin 15                                       | İ                   | -1,2   | 7                                                                 | 7                 | 7                    | ļ                 | 4                                                                                                                                       | kΩ min      |

|                                              |                     |        | 20                                                                | 20                | 20                   | -                 |                                                                                                                                         | kΩ max      |

| Digital Input High Voltage                   | VIH                 | -1,2   | 2.4                                                               | 2.4               | 2.4                  | ļ                 |                                                                                                                                         | V min       |

| Digital Input Low Voltage                    | VIL                 | -1,2   | 0.8                                                               | 0.8               | 0.8                  | <u> </u>          |                                                                                                                                         | V max       |

| Digital Input Leakage Current                | In                  | -1,2   | 10                                                                | 1                 | 10                   | ļ                 | $V_{IN} = 0V \text{ or } V_{DD}.$                                                                                                       | ±μA max     |

| Digital Input Capacitance                    | Cı                  | -1,2   | 7                                                                 | <u> </u>          |                      |                   |                                                                                                                                         | pF max      |

| Output Capacitance Pin 1                     | c <sub>o</sub>      | -1,2   | 200                                                               |                   |                      |                   | DAC Register Loaded with All 1's.                                                                                                       | pF max      |

|                                              |                     |        | 100                                                               |                   |                      | r                 | DAC Register Loaded with All 0's                                                                                                        |             |

| Supply Current from V                        | Ipp                 | -1,2   | 2                                                                 | 2                 | 2                    |                   | All Digital Inputs VIL or VIH.                                                                                                          | mA max      |

| Supply Current from V <sub>DD</sub>          | *DD                 | 1,2    | 300                                                               | 300               | 300                  |                   | All Digital Inputs 0 or V <sub>DD</sub> .                                                                                               | μA max      |

| Data Valid Setup Time <sup>4</sup>           | tps                 | -1,2   | 290                                                               |                   |                      |                   | T                                                                                                                                       | ns min      |

| Data Valid Hold Time <sup>4</sup>            | t <sub>DH</sub>     | -1,2   | 70                                                                |                   |                      |                   |                                                                                                                                         | ns min      |

| CSMSB or CSLSB <sup>4</sup> to WR Setup Time | tcws                | -1,2   | 50                                                                |                   |                      |                   |                                                                                                                                         | ns min      |

| CSMSB or CSLSB <sup>4</sup> to WR Hold Time  | t <sub>CWH</sub>    | -1,2   | 25                                                                |                   |                      |                   |                                                                                                                                         | ns min      |

| LDACto WR Setup Time <sup>4</sup>            | tLWS                | -1,2   | 50                                                                | <del> </del>      |                      | <u> </u>          |                                                                                                                                         | ns min      |

| LDAC to WR Hold Time <sup>4</sup>            |                     | -1,2   | 25                                                                | 1 -               | +                    | <u> </u>          |                                                                                                                                         | ns min      |

| Write Pulse Width <sup>4</sup>               | t <sub>wr</sub>     | -1,2   | 320                                                               | +                 | +                    | <del> </del>      |                                                                                                                                         | ns min      |

DIGITAL-TO-ANALOG CONVERTERS 8-161

NOTES  $^{1}V_{PIN1} = V_{PIN2} = 0V$ ;  $V_{REF} = +10V$ , unless otherwise stated.  $^{2}$ Measured using internal  $R_{PB}$  and includes effect of leakage current and gain TC.

<sup>&</sup>lt;sup>3</sup>Feedthrough error can be reduced by connecting the metal lid to DGND.

<sup>4</sup>Timing per Figure 1.

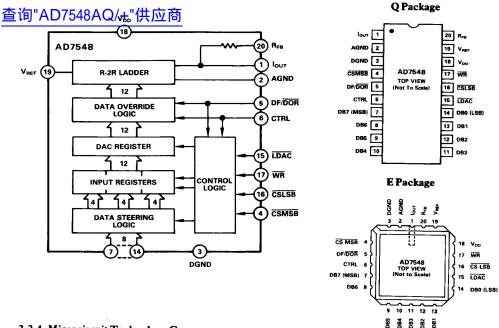

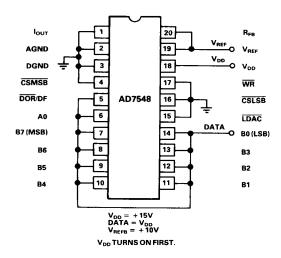

### 3.2.1 Functional Block Diagram and Terminal Assignments.

### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (80).

### 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).

8-162 DIGITAL-TO-ANALOG CONVERTERS

### PIN FUNCTION DESCRIPTION

### PIN THE WORLD A COURT OF

| 1 | IOUT   | DAC current OUT bus. Normally terminated at virtual ground of output amplifier.                                                                                                                   |

|---|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | AGND   | Analog Ground.                                                                                                                                                                                    |

| 3 | DGND   | Digital Ground.                                                                                                                                                                                   |

| 4 | CSMSB  | Chip Select Most Significant (MS) Byte. Active Low Input. Used in combination with WR to load external data into the input register or in combination with WR and LDAC to load external data into |

|   |        | both input and DAC registers.                                                                                                                                                                     |

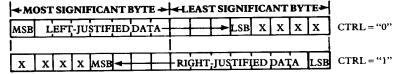

| < | DE/DOE | Data Format/Data Override When this input is LOW, data in the DAC register is forced to one of                                                                                                    |

two override codes selected by CTRL. When the override signal is removed, the DAC output returns to reflect the value in the DAC register. With DF/DOR HIGH, CTRL selects either a left or right justified input data format. For normal operation, DF/DOR is held HIGH.

| DF/DOR | CTRL | FUNCTION                                    |

|--------|------|---------------------------------------------|

| 0      | 0    | DAC register contents overridden by all 0's |

| 0      | 1    | DAC register contents overridden by all 1's |

| 1      | 0    | Left-justified input data selected          |

| 1      | 1    | Right-justified input data selected         |

6 CTRL

**CSLSB**

$\overline{WR}$

16

17

Control Input. See pin 5 description.

X = Don't care states.

| 7  | DB7  | Data Bit 7. Most Significant Bit (MSB).                                                      |

|----|------|----------------------------------------------------------------------------------------------|

| 8  | DB6  | Data Bit 6.                                                                                  |

| 9  | DB5  | Data Bit 5.                                                                                  |

| 10 | DB4  | Data Bit 4.                                                                                  |

| 11 | DB3  | Data Bit 3.                                                                                  |

| 12 | DB2  | Data Bit 2.                                                                                  |

| 13 | DB1  | Data Bit 1.                                                                                  |

| 14 | DB0  | Data Bit 0. Least Significant Bit (LSB).                                                     |

| 15 | LDAC | Load DAC Input, active LOW. This signal, in combination with others, is used to load the DAC |

register from either the input register or the external data bus.

Chip Select Least Significant (LS) Byte. Active LOW input. Used in combination with WR to load

external data into the input register or in combination with WR and LDAC to load external data into both input and DAC registers.

WP ITE Input. This active low signal in combination with others is used in loading external data.

WRITE Input. This active low signal, in combination with others is used in loading external data into the AD7548 input register and in transferring data from the input register to the DAC register.

Table 3.

| WR | CSMSB | CSLSB | LDAC | FUNCTION                                         |

|----|-------|-------|------|--------------------------------------------------|

| 0  | 1     | 0     | 1    | Load LS Byte to Input Register.                  |

| 0  | 1     | 0     | 0    | Load LS Byte to Input Register and DAC Register. |

| 0  | 0     | 1     | 1    | Load MS Byte to Input Register.                  |

| 0  | 0     | 1     | 0    | Load MS Byte to Input Register and DAC Register. |

| 0  | 1     | 1     | 0    | Load Input Register to DAC Register.             |

| 1  | х     | x     | x    | No Data Transfer                                 |

| 18 | $V_{DD}$         | + 5V to + 15V Supply Input. |

|----|------------------|-----------------------------|

|    |                  |                             |

| 19 | V <sub>REF</sub> | Reference Voltage Input.    |

|    |                  |                             |

20 R<sub>FB</sub> Feedback Resistor. Used for normal D/A conversion.

DIGITAL-TO-ANALOG CONVERTERS 8-163

REV. B

- NOTES 1. ALL INPUT SIGNAL RISE AND FALL TIMES MEASURED FROM 10% TO 90% OF +5V. t, = t\_i = 20ns.  $V_{\text{Pl}} + V_{\text{R}}$

- 2. TIMING MEASUREMENT REFERENCE LEVEL IS  $\frac{V_{H}+V_{L}}{c}$

- 3. CSMSB (PIN 4) AND CSLSB (PIN 16) MAY BE INTERCHANGED.

- 4. FOR LEFT-JUSTIFIED DATA CTRL=+0V WITH DF/DOR=+5V. FOR RIGHT-JUSTIFIED DATA CTRL = +5V WITH DF/DOR = +5V.

Figure 1. Control Input Timing Diagram