|                                                                                                     |                                                               |                |         |                                    |                                                |                               |                  |              | REVIS   | SIONS           |              |              |            |             |             |                      |              |      |      |             |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|---------|------------------------------------|------------------------------------------------|-------------------------------|------------------|--------------|---------|-----------------|--------------|--------------|------------|-------------|-------------|----------------------|--------------|------|------|-------------|

| LTR查询                                                                                               | 5962                                                          | -967           | 2801\   | VQC'                               | '供应                                            | DESC                          | RIPTIC           | ON           |         |                 |              |              | D          | ATE (       | YR-MO-      | DA)                  |              | APP  | ROVE | D.          |

| A                                                                                                   | Tec                                                           | chnic          | cal e   |                                    | rial                                           | . cha                         | ınges            | to           | Tabl    | e I.            | Add          |              | 96         | 5-03-       | -08         |                      | М.           | L. 1 | Poel | cing        |

|                                                                                                     |                                                               |                |         |                                    |                                                |                               |                  |              |         |                 |              |              |            |             |             |                      |              |      |      |             |

|                                                                                                     |                                                               |                |         |                                    |                                                |                               |                  |              |         |                 |              |              |            |             |             |                      |              |      |      |             |

| REV<br>SHEET                                                                                        |                                                               |                |         |                                    |                                                |                               |                  |              |         |                 |              |              |            |             |             |                      |              |      |      |             |

| SHEET                                                                                               | A 15                                                          | A 16           | A 17    | Α                                  | A                                              | A                             | A                | A            | A       | A               | A            | A            |            |             |             |                      |              |      |      |             |

| SHEET<br>REV<br>SHEET                                                                               | A 15                                                          | A 16           | A 17    | 18                                 | 19                                             | A 20                          | 21               | 22           | 23      | 24              | 25           | 26           |            |             |             |                      |              |      |      |             |

| SHEET REV SHEET REV STATUS                                                                          |                                                               |                |         | 18<br>REV                          | 19                                             | <del></del> -                 | 21<br>A          | 22<br>A      | 23<br>A | 24<br>A         | 25<br>A      | 26<br>A      | A          | A           | A           | A                    | A            | A    | A    | <del></del> |

| SHEET REV SHEET REV STATUS OF SHEETS                                                                |                                                               |                |         | 18<br>REV<br>SHE<br>PREP           | 19<br>ET<br>ARED E                             | 20                            | 21<br>A<br>1     | 22           | 23      | 24              | 25           | 26<br>A<br>6 | 7<br>FENSE | 8<br>ELECTI | 9<br>RONICS | 10<br>SUPP           | 11<br>LY CEN | 12   | A 13 | <del></del> |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A STAI                                                  | 15<br>NDAR<br>CIRC                                            | 16<br>D<br>UIT |         | 18 REV SHE PREP Th                 | 19 ET ARED E                                   | 20<br>3Y<br>1. Hes            | 21<br>A<br>1     | 22<br>A      | 23<br>A | 24<br>A         | 25<br>A      | 26<br>A<br>6 | 7<br>FENSE | 8<br>ELECTI | 9           | 10<br>SUPP           | 11<br>LY CEN | 12   |      | <del></del> |

| SHEET REV SHEET REV STATUS OF SHEETS  PMIC N/A  STAI MICRO DRA  THIS DRAWING FOR USE BY A           | NDAR<br>CIRC<br>AWING                                         | D<br>UIT       | 17      | 18 REV SHE PREP Th CHEC            | 19 ET ARED E omas N KED B' omas N              | 20<br>3Y<br>4. Hes            | 21<br>A<br>1     | 22<br>A      | 23<br>A | A<br>4          | 25<br>A<br>5 | 26<br>A<br>6 | 7 FENSE D  | 8<br>ELECTI | 9<br>RONICS | 10<br>SUPPI<br>0 454 | 11<br>LY CEN | 12   | 13   | 14          |

| SHEET REV SHEET REV STATUS OF SHEETS  PMIC N/A  STAI  MICRO  DRA  THIS DRAWING                      | NDAR<br>CIRC<br>AWING                                         | D<br>UIT       | 3LE NTS | 18 REV SHE PREP Th CHEC Th APPR Mo | ET  ARED E Omas N  KED BY OMAS N  OVED Enica I | 20 3Y 4. Hes 4. Hes 3Y L. Poe | 21<br>A<br>1     | 22<br>A<br>2 | 23<br>A | A<br>4          | A 5          | A 6 DE       | 7 FENSE D  | 8<br>ELECTI | 9<br>RONICS | 10<br>SUPPI<br>0 454 | 11 LY CEN    | 12   | 13   | 14          |

| SHEET REV SHEET REV STATUS OF SHEETS  PMIC N/A  STAI MICRO DRA  THIS DRAWING FOR USE BY A AND AGENC | NDAR<br>CIRC<br>WING<br>G IS A<br>RLL DEF<br>CIES O<br>T OF D | D<br>UIT       | 3LE NTS | 18 REV SHE PREP Th CHEC Th APPR Mo | ET  ARED E Omas N  KED BY OMAS N  OVED Enica I | 20 3Y 4. Hes 4. Hes BY L. Poe | 21 A 1 s s Lking | 22<br>A<br>2 | 23<br>A | A 4 4 MICR MONO | A 5          | 26 A 6 DE    | 7 FENSE C  | 8 ELECTI    | 9<br>RONICS | 10<br>SUPPI<br>0 454 | 11 LY CEN    | 12   | 13   | A 14        |

<u>DISTRIBUTION STATEMENT A.</u> Approved for public release; distribution is unlimited.

5962-E334-96

#### 1. SCOPE

15 18-50-2-10172 Shawing forms what to f a one part - one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes Q and M) and space application (device class V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

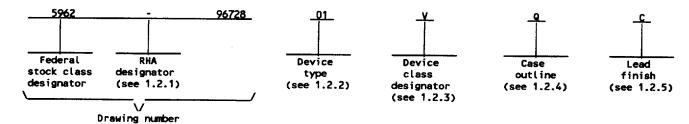

1.2 PIN. The PIN shall be as shown in the following example:

1.2.1 <u>RHA designator</u>. Device class M RHA marked devices shall meet the MIL-I-38535 appendix A specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

Device type

Generic number

Circuit function

01

MD80C86/7

Latchup resistant CMOS static 16-Bit microprocessor

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

M

Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883

or v

Certification and qualification to MIL-1-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | <u>Descriptive designator</u> | <u> Terminals</u> | Package style        |

|----------------|-------------------------------|-------------------|----------------------|

| Q              | CD1P2-T40                     | 40                | Dual-in-line package |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein) for class M or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-96728 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>A | SHEET 2    |

DESC FORM 193A JUL 94

**=** 9004708 0020231 843 **=**

1.3 Absolute maximum ratings. 1/ +8.0 V dc GND-0.5 V dc to  $V_{DD}$  +0.5 V dc -65°C to +150°C Junction temperature (T<sub>J</sub>) s' -------+175°C Lead temperature (soldering 10 seconds) (T<sub>S</sub>) Thermal resistance junction-to-case  $(\theta_{JC})$ : +300 °C Case outline Q 4°C/W 37°C/W Maximum package power dissipation at  $T_A = +125$ °C ( $P_D$ ) 2/ - - -1.35 ₩ 1.4 <u>Recommended operating conditions</u>. 4.5 V dc to +5.5 V dc -55°C to +125°C 0 V dc to +0.8 V dc Input high voltage range (except clock pin)(VIH) - - - - - -2.2 V dc to V<sub>DD</sub> Input high voltage range (clock pin) ( $V_{IH}$ ) -VDD - 0.8 V dc to VDD 2. APPLICABLE DOCUMENTS 2.1 Government specification, standards, bulletin, and handbook. Unless otherwise specified, the following specification, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified SPECIFICATION MILITARY MIL-1-38535 - Integrated Circuits, Manufacturing, General Specification for. STANDARDS MILITARY MIL-STD-883 - Test Methods and Procedures for Microelectronics. - Configuration Management. MIL-STD-973 MIL-STD-1835 - Microcircuit Case Outlines. BULLETIN MILITARY MIL-BUL-103 - List of Standardized Military Drawings (SMD's). HANDBOOK MILITARY MIL-HDBK-780 - Standardized Military Drawings. (Copies of the specification, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability. If device power exceeds package dissipation capability provide heat sinking or derate linearly (the derating is based on  $\Theta_{AA}$ ) at a rate of 27.0 mW/°C. SIZE STANDARD Α MICROCIRCUIT DRAWING 5962-96728 **DEFENSE ELECTRONICS SUPPLY CENTER** DAYTON, OHIO 45444 **REVISION LEVEL** SHEET Α 3 DESC FORM 193A JUL 94

9004708 0020232 78T **=**

#### 3. REQUIREMENTS

- 3. \*\* The Total Total Time in the Litem requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

- 3.2 <u>Design. construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.2 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 2.

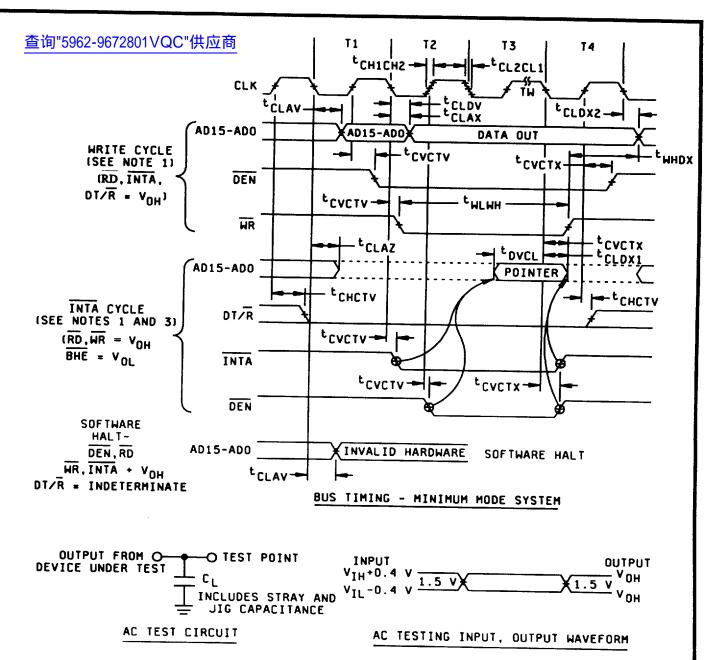

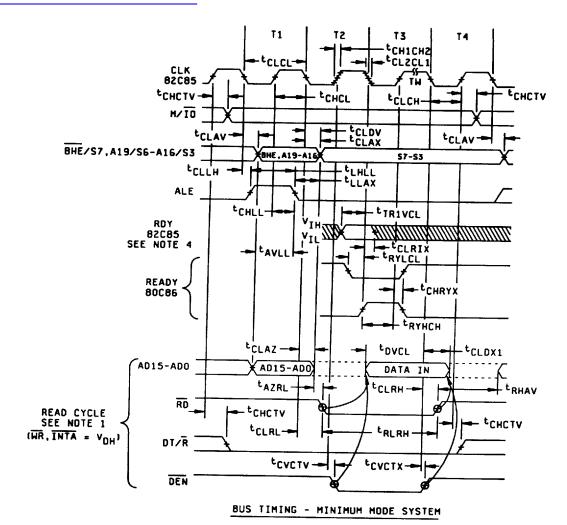

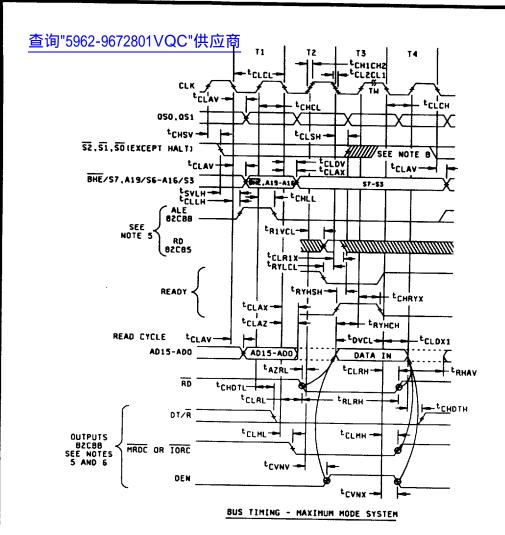

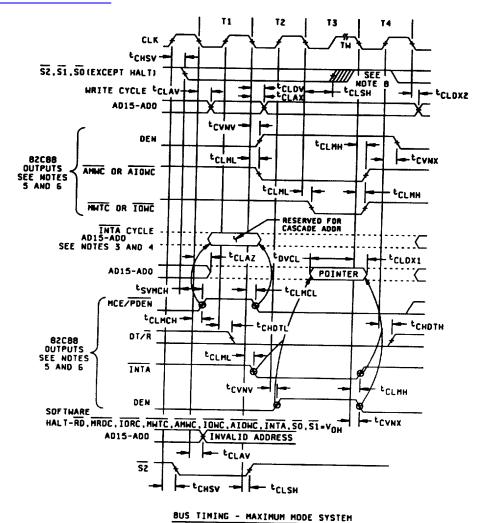

- 3.2.4 Switching waveforms. The switching waveforms shall be as specified in figure 3.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full ambient operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.2 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.1 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-1-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change for device class M. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M.</u> For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-I-38535, appendix A).

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-96728 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>A | SHEET 4    |

DESC FORM 193A JUL 94

**9004708 0020233 616**

| Test                             | Symbol            | Conditions 1/<br>-55°C ≤ T <sub>A</sub> ≤ +125°C<br>unless otherwise specified              | Group A<br>subgroups | Device<br>type | Li                   | mits | Uni<br>- |

|----------------------------------|-------------------|---------------------------------------------------------------------------------------------|----------------------|----------------|----------------------|------|----------|

|                                  |                   | and a chief who a specificat                                                                |                      |                | Min                  | Max  |          |

| Logical "1" input<br>voltage     | VIH               | 2/ 3/<br>V <sub>DD</sub> = 5.5 v                                                            | 1,2,3                | ALL            | 2.2                  |      | v        |

| Logical HOH input<br>voltage     | VIL               | V <sub>DD</sub> = 4.5 v<br>2/3/                                                             | 1,2,3                | ALL            |                      | 0.8  | v        |

| CLK logical "1" input<br>voltage | VIHC              | V <sub>DD</sub> = 5.5 v<br>2/3/                                                             | 1,2,3                | ALL            | V <sub>DD</sub> -0.8 |      | v        |

| CLK logical "0" input<br>voltage | VILC              | V <sub>DD</sub> = 4.5 v<br>2/3/                                                             | 1,2,3                | All            |                      | 0.8  | v        |

| Output high voltage              | VOH               | V <sub>DD</sub> = 4.5 V, I <sub>OH</sub> = -2.5 mA 4/                                       | 1,2,3                | ALL            | 3.0                  |      |          |

|                                  |                   | $V_{DD} = 4.5 \text{ V}, I_{OH} = -100 \mu\text{A} \frac{4}{4}$                             |                      |                | V <sub>DD</sub> -0.4 |      | - V      |

| Output low voltage               | V <sub>OL</sub>   | $V_{DD} = 4.5 \text{ V, } I_{OL} = +2.5 \text{ mA } 4/$                                     | 1,2,3                | ALL            |                      | 0.4  | V        |

| Input leakage current            | IIL               | V <sub>DD</sub> = 5.5 V, V <sub>IN</sub> = GND or V <sub>DD</sub><br>pins: 17-19, 21-23, 33 | 1,2,3                | All            | -1.0                 | +1.0 | μА       |

| Output leakage current           | I <sub>OZL</sub>  | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 0 V or V <sub>DD</sub><br>pins: 26-29, 32       | 1,2,3                | All            | -10                  | +10  | μА       |

| Input current bus hold high      | <sup>I</sup> внн  | V <sub>IN</sub> = 3.0 V, V <sub>DD</sub> = 4.5 V and 5.5 V <u>5</u> /                       | 1,2,3                | All            | -400                 | -40  | μΑ       |

| Input current bus hold low       | IBHL              | V <sub>IN</sub> = 0.8 V, V <sub>DD</sub> = 4.5 V and 5.5 V <u>6</u> /                       | 1,2,3                | All            | 40                   | 400  | μΑ       |

| Standby power supply current     | <sup>I</sup> ccsB | $V_{IN} = V_{DD}$ or GND $V_{DD} = 5.5 \text{ V } \text{Z/}$                                | 1,2,3                | ALL            |                      | 500  | μΑ       |

| Operating power supply current   | <sup>I</sup> CCOP | V <sub>DD</sub> = 5.5 V, V <sub>IN</sub> = V <sub>DD</sub> or GND outputs open, f= 5 MHz    | 1,2,3                | ALL            |                      | 50   | mA       |

| Functional tests                 |                   | See 4.4.1b<br>V <sub>DD</sub> = 4.5 V and 5.5 V<br>f = 5 MHz 8/2/                           | 7,8                  | All            |                      |      |          |

See footnotes at end of table.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                     | 5962-96728 |

|------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>A | SHEET<br>5 |

DESC FORM 193A JUL 94

**■ 9004708 0020234 552 ■**

| 宣问"5962-96728<br>Test                                                              | Symbol             | 共 <del>应商</del><br>Conditions 1                          | V                                     | Group A                               |        | L                     | imits  | Unit |

|------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------|---------------------------------------|---------------------------------------|--------|-----------------------|--------|------|

|                                                                                    |                    | -55°C ≤ T <sub>A</sub> ≤ +125°<br>unless otherwise speci | fied                                  | subgroup                              | s type | Min                   | Max    |      |

| Input capacitance                                                                  | CIN                | See 4.4.1c<br>f = 1 MHz<br>All measurements are          |                                       | 4                                     | ALL    |                       | 25     | pF   |

| Output capacitance                                                                 | Cout               | referenced to device                                     | GND.                                  | 4                                     | ALL    |                       | 25     | pF   |

| I/O capacitance                                                                    | c1/0               |                                                          |                                       | 4                                     | ALL    |                       | 25     | pF   |

| MINIMUM COMPLEXITY SYS                                                             | TEM TIMING         |                                                          |                                       |                                       |        |                       |        |      |

| CLK cycle period                                                                   | tCLCL              | 3/ 9/ V <sub>DD</sub> = 4.5 V                            |                                       | 9,10,11                               | ALL    | 200                   |        | ns   |

| CLK low time                                                                       | tCLCH              | 3/ 2/ V <sub>DD</sub> = 4.5 V                            |                                       | 9,10,11                               | ALL    | 118                   |        | ns   |

| CLK high time                                                                      | tCHCL              | 3/ 2/ V <sub>DD</sub> = 4.5 V                            |                                       | 9,10,11                               | ALL    | 69                    |        | ns   |

| Data in setup time                                                                 | <sup>t</sup> DVCL  | 3/ 9/ V <sub>DD</sub> = 4.5 v                            |                                       | 9,10,11                               | All    | 30                    |        | ns   |

| Data in hold time                                                                  | t <sub>CLDX1</sub> | 3/ 9/ V <sub>DD</sub> = 4.5 v                            |                                       | 9,10,11                               | ALL    | 10                    |        | ns   |

| Ready setup time into device                                                       | <sup>t</sup> RYHCH | 3/ 2/ V <sub>DD</sub> = 4.5 v                            |                                       | 9,10,11                               | ALL    | 118                   |        | ns   |

| Ready hold time into device                                                        | <sup>t</sup> CHRYX | 3/ 9/ V <sub>DD</sub> = 4.5 V                            |                                       | 9,10,11                               | ALL    | 30                    |        | ns   |

| Ready inactive to CLK                                                              | <sup>t</sup> rylcl | 3/ 9/ 10/ V <sub>DD</sub> = 4.5 V                        |                                       | 9,10,11                               | ALL    | -8                    |        | ns   |

| old setup time                                                                     | t <sub>HVCH</sub>  | 3/ 2/ V <sub>DD</sub> = 4.5 V                            |                                       | 9,10,11                               | ALL    | 35                    |        | ns   |

| NTR, NMI, TEST setup<br>time                                                       | tINVCH             | 3/ 9/ 11/ V <sub>DD</sub> = 4.5 V                        | · · · · · · · · · · · · · · · · · · · | 9,10,11                               | All    | 30                    |        | ns   |

| ddress valid delay                                                                 | <sup>t</sup> CLAV  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 v                        |                                       | 9,10,11                               | ALL    | 10                    | 110    | ns   |

| ddress hold time                                                                   | <sup>t</sup> CLAX  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 v                        |                                       | 9,10,11                               | ALL    | 10                    |        | ns   |

| LE width                                                                           | t <sub>LHLL</sub>  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                        |                                       | 9,10,11                               | All    | t <sub>CLCH</sub> -20 |        | ns   |

| LE active delay                                                                    | t <sub>CLLH</sub>  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                        |                                       | 9,10,11                               | ALL    |                       | 80     | ns   |

| see footnotes at end of                                                            | table.             |                                                          |                                       |                                       | ţ      |                       |        | -    |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                    | !                                                        | ZE<br><b>A</b>                        | · · · · · · · · · · · · · · · · · · · |        | 596                   | 2-9672 |      |

|                                                                                    |                    |                                                          |                                       | EVISION L                             | EVEL   | SHEET                 |        |      |

DESC FORM 193A JUL 94

**-** 9004708 0020235 499 **-**

| 查询"5962-967280<br>Test               | Symbol             | Conditions 1/                                                 | Group A<br>subgroups | Device<br>type                        | Limits                 |             | Unit          |

|--------------------------------------|--------------------|---------------------------------------------------------------|----------------------|---------------------------------------|------------------------|-------------|---------------|

|                                      |                    | -55°C ≤ T <sub>A</sub> ≤ +125°C<br>unless otherwise specified | 3.040                |                                       | Min                    | Max         |               |

| HINIMUM COMPLEXITY SYSTI             | EM TIMING          | - CONTINUED.                                                  |                      | · · · · · · · · · · · · · · · · · · · |                        | <del></del> | <del></del> _ |

| ALE inactive delay                   | <sup>t</sup> CHLL  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | ALL                                   |                        | 85          | ns            |

| Address hold time to<br>ALE inactive | <sup>t</sup> LLAX  | 3/ 9/ <u>12</u> / V <sub>DD</sub> = 4.5 V                     | 9,10,11              | ALL                                   | t <sub>CHCL</sub> -10  |             | ns            |

| Data valid delay                     | <sup>t</sup> CLDV  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | ALL                                   | 10                     | 110         | ns            |

| Control active delay 1               | <sup>t</sup> cvcTv | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | ALL                                   | 10                     | 110         | ns            |

| Control active delay 2               | <sup>t</sup> CHCTV | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | ALL                                   | 10                     | 110         | ns            |

| Control inactive delay               | <sup>t</sup> cvctx | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | All                                   | 10                     | 110         | ns            |

| Address float to RD active           | <sup>t</sup> AZRL  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | All                                   | 0                      |             | ns            |

| RD active delay                      | <sup>t</sup> CLRL  | 3/ 9/ 12/ v <sub>DD</sub> = 4.5 y                             | 9,10,11              | ALL                                   | 10                     | 165         | ns            |

| RD inactive delay                    | <sup>t</sup> CLRH  | 3/ 9/ 12/ v <sub>DD</sub> = 4.5 v                             | 9,10,11              | All                                   | 10                     | 150         | ns            |

| RD inactive to next address active   | <sup>t</sup> RHAV  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | ALL                                   | t <sub>CLCL</sub> -45  |             | ns            |

| HLDA valid delay                     | <sup>t</sup> CLHAV | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 v                             | 9,10,11              | All                                   | 10                     | 160         | ns            |

| RD width                             | <sup>t</sup> rlrh  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | All                                   | 2t <sub>CLCL</sub> -75 |             | ns            |

| JR width                             | <sup>t</sup> WLWH  | 3/ 9/ 12/ v <sub>DD</sub> = 4.5 v                             | 9,10,11              | All                                   | 2t <sub>CLCL</sub> -60 |             | ns            |

| Address valid to ALE<br>low          | <sup>t</sup> aval  | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                             | 9,10,11              | All                                   | t <sub>CLCH</sub> -60  |             | ns            |

| Output rise time                     | <sup>t</sup> OLOH  | 3/ 9/ V <sub>DD</sub> = 4.5 V                                 | 9,10,11              | All                                   |                        | 20          | ns            |

| Output fall time                     | toHOL              | 3/ 2/ V <sub>DD</sub> = 4.5 v                                 | 9,10,11              | All                                   |                        | 20          | ns            |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-96728

REVISION LEVEL

A

7

DESC FORM 193A JUL 94

**9**004708 0020236 325

| 查询"5962-967280                   | Symbol              | Conditions 1/                                                                                                       | Group A<br>subgroups | Device<br>type      |       | Limits | Unit                                             |

|----------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|-------|--------|--------------------------------------------------|

|                                  |                     | -55°C ≤ T <sub>A</sub> ≤ +125°C<br>unless otherwise specified                                                       | 3g.                  | (7)                 | Min   | Max    |                                                  |

| MAXIMUM MODE SYSTEM TI           | MING (USING         | 82C88 BUS CONTROLLER)                                                                                               |                      |                     |       |        | ········                                         |

| CLK cycle period                 | t <sub>CLCL</sub>   | 2/ V <sub>DD</sub> = 4.5 v 3/                                                                                       | 9,10,11              | ALL                 | 200   |        | ns                                               |

| CLK low time                     | <sup>t</sup> CLCH   | 2/ V <sub>DD</sub> = 4.5 V 3/                                                                                       | 9,10,11              | ALL                 | 118   |        | ns                                               |

| CLK high time                    | <sup>t</sup> CHCL   | 2/ V <sub>DD</sub> = 4.5 V <u>3</u> /                                                                               | 9,10,11              | ALL                 | 69    |        | ns                                               |

| Data in setup time               | <sup>t</sup> DVCL   | 2/ V <sub>DD</sub> = 4.5 V <u>3</u> /                                                                               | 9,10,11              | ALL                 | 30    |        | ns                                               |

| Data in hold time                | <sup>t</sup> CLDX1  | 2/ V <sub>DD</sub> = 4.5 v <u>3</u> /                                                                               | 9,10,11              | ALL                 | 10    |        | ns                                               |

| Ready setup time into<br>device  | <sup>t</sup> RYHCH  | 2/ V <sub>DD</sub> = 4.5 v <u>3</u> /                                                                               | 9,10,11              | Alt                 | 118   |        | ns                                               |

| Ready hold time into<br>device   | <sup>t</sup> CHRYX  | 2/ V <sub>DD</sub> = 4.5 v <u>3</u> /                                                                               | 9,10,11              | All                 | 30    |        | ns                                               |

| Ready inactive to CLK            | <sup>t</sup> RYLCL  | 2/ V <sub>DD</sub> = 4.5 v <u>3</u> /                                                                               | 9,10,11              | All                 | -8    |        | ns                                               |

| CLK rise time                    | t <sub>CH1CH2</sub> | From 1.0 V to 3.5 V <u>13</u> /<br>V <sub>DD</sub> = 4.5 V                                                          | 9,10,11              | All                 |       | 10     | ns                                               |

| CLK fall time                    | t <sub>CL2CL1</sub> | From 3.5 V to 1.0 V <u>13</u> /<br>V <sub>DD</sub> = 4.5 V                                                          | 9,10,11              | ALL                 |       | 10     | ns                                               |

| RDY setup time into<br>82C84A    | <sup>t</sup> R1VCL  | C <sub>L</sub> = 100 pF, V <sub>DD</sub> = V <sub>DDL</sub> ,<br>f = 1 MHz, V <sub>DD</sub> = 4.5 V,<br>14/ 13/ 15/ | 9,10,11              | All                 | 35    |        | ns                                               |

| RDY hold time into<br>82C84A     | <sup>t</sup> CLR1X  | C <sub>L</sub> = 100 pF, V <sub>DD</sub> = V <sub>DDL</sub> ,<br>f = 1 MHz, V <sub>DD</sub> = 4.5 V,<br>13/14/ 15/  | 9,10,11              | All                 | 0     |        | ns                                               |

| Input rise time<br>(except CLK)  | t <sub>ILIH</sub>   | From 0.8 V to 2.0 V<br>V <sub>DD</sub> = 4.5 V <u>13</u> /                                                          | 9,10,11              | All                 | ····  | 15     | ns                                               |

| nput fall time<br>(except CLK)   | tIHIL               | From 2.0 V to 0.8 V<br>V <sub>DD</sub> = 4.5 V <u>13</u> /                                                          | 9,10,11              | ALL                 |       | 15     | ns                                               |

| See footnotes at end of          | table.              |                                                                                                                     | 1                    | · · · · · · · · · · |       | 1      | <del>-                                    </del> |

| STANDARD<br>MICROCIRCUIT DRAWING |                     |                                                                                                                     | SIZE A               |                     |       | 59     | 62-9672                                          |

| DEFENSE ELECT                    |                     | UPPLY CENTER                                                                                                        | F                    | REVISION            | LEVEL | SHE    | ET .                                             |

DESC FORM 193A JUL 94

**-** 9004708 0020237 26% **-**

| 查询"5962-967280<br>Test                             | Symbol                                               | Conditions 1/<br>-55°C ≤ T <sub>A</sub> ≤ +125°C                                                           | Group A<br>subgroups | Device<br>type | Lis                   | nits                  | Unit        |

|----------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|-----------------------|-------------|

|                                                    |                                                      | unless otherwise specified                                                                                 |                      |                | Min                   | Max                   |             |

| MINIMUM COMPLEXITY SYST                            | EM TIMING                                            |                                                                                                            |                      |                |                       |                       | <del></del> |

| Address float delay                                | tCLAZ                                                |                                                                                                            | 9,10,11              | ALL            | tCLAX                 | 80                    | ns          |

| Status float delay                                 | t <sub>CHSZ</sub>                                    | _                                                                                                          | 9,10,11              | ALL            |                       | 80                    | ns          |

| Data hold_time<br>after WR                         | tWHDX                                                | $C_L = 100 \text{ pF}, V_{DD} = V_{DDL},$<br>$f = 1 \text{ MHz } V_{DD} = 4.5 \text{ V}$<br>$\frac{9}{13}$ | 9,10,11              | ALL            | t <sub>CLCL</sub> -30 |                       | ns          |

| Data hold time                                     | t <sub>CLDX2</sub>                                   |                                                                                                            | 9,10,11              | All            | 10                    |                       | ns          |

| MAXIMUM MODE SYSTEM TIM                            | ING (USING                                           | 82C88 BUS CONTROLLER)                                                                                      |                      |                | <u> </u>              |                       |             |

| Setup time for<br>recognition (INTR,<br>NMI, Test) | tINVCH                                               | 3/ 9/ V <sub>DD</sub> = 4.5 V                                                                              | 9,10,11              | ALL            | 30                    |                       | ns          |

| RQ/GT setup delay                                  | t <sub>GVCH</sub>                                    | 3/ 9/ V <sub>DD</sub> = 4.5 V                                                                              | 9,10,11              | All            | 30                    |                       | ns          |

| RQ hold time into device                           | <sup>t</sup> CHGX                                    | 3/ 10/ 12/ 16/ 9/<br>V <sub>DD</sub> = 4.5 v                                                               | 9,10,11              | ALL            | 40                    | t <sub>CHCL</sub> +10 | ns          |

| Ready active to status passive                     | <sup>t</sup> RYHSH                                   | 3/ 9/ 12/ v <sub>DD</sub> = 4.5 v                                                                          | 9,10,11              | ALL            |                       | 110                   | ns          |

| Status active delay                                | tcHSV                                                | 3/ 9/ <u>12</u> / V <sub>DD</sub> = 4.5 V                                                                  | 9,10,11              | ALL            | 10                    | 110                   | ns          |

| Status inactive delay                              | <sup>t</sup> CLSH                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                          | 9,10,11              | All            | 10                    | 130                   | ns          |

| Address valid delay                                | <sup>t</sup> CLAV                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                          | 9,10,11              | All            | 10                    | 110                   | ns          |

| Address hold time                                  | t <sub>CLAX</sub>                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                          | 9,10,11              | All            | 10                    |                       | ns          |

| Data valid delay                                   | t <sub>CLDV</sub>                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                          | 9,10,11              | Att            | 10                    | 110                   | ns          |

| Address float to read active                       | <sup>t</sup> AZRL                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                          | 9,10,11              | All            | 0                     |                       | ns          |

| RD active delay                                    | tCLRL                                                | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                          | 9,10,11              | ALL            | 10                    | 165                   | ns          |

| See footnotes at end of                            | table.                                               |                                                                                                            |                      | <del></del>    |                       |                       | 1           |

| MICROC                                             | STANDARI<br>CIRCUIT DI                               | D<br>RAWING                                                                                                | SIZE<br><b>A</b>     |                |                       | 596                   | 32-9672     |

| DAYT                                               | DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                                                                                                            |                      | REVISIO        | SHEE                  | SHEET 9               |             |

JUL 94 - 9004708 0020238 1T8 -

| 查询"5962-9672<br><del>Test</del> | Symbol                                               | Conditions 1/ -55°C ≤ T <sub>A</sub> ≤ +125°C unless otherwise specified                                             | Group A<br>subgroups | Device<br>type | Lin                    | nits | Unit        |

|---------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|------------------------|------|-------------|

|                                 |                                                      | unless otherwise specified                                                                                           |                      |                | Min                    | Max  |             |

| MAXIMUM MODE SYSTEM T           | IMING (USIN                                          | G 82C88 BUS CONTROLLER) - CON                                                                                        | INUED.               |                |                        |      |             |

| RD inactive delay               | <sup>t</sup> CLRH                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 v                                                                                    | 9,10,11              | ALL            | 10                     | 150  | ns          |

| RD inactive to next address     | <sup>t</sup> RHAV                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                                    | 9,10,11              | ALL            | t <sub>CLCL</sub> -45  |      | ns          |

| GT active delay                 | tCLGL                                                | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                                    | 9,10,11              | ALL            | 10                     | 85   | ns          |

| GT inactive delay               | tCLGH                                                | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                                    | 9,10,11              | ALL            | 10                     | 85   | ns          |

| RD width                        | <sup>t</sup> RLRH                                    | 3/ 9/ 12/ V <sub>DD</sub> = 4.5 V                                                                                    | 9,10,11              | ALL            | 2t <sub>CLCL</sub> -75 |      | ns          |

| Output rise time                | toLOH                                                | from 0.8 V to 2.0 V<br>2/ V <sub>DD</sub> = 4.5 V                                                                    | 9,10,11              | ALL            |                        | 20   | ns          |

| Output fall time                | <sup>t</sup> OHOL                                    | from 2.0 V to 0.8 V<br>2/ V <sub>DD</sub> = 4.5 V                                                                    | 9,10,11              | Att            |                        | 20   | ns          |

| MINIMUM COMPLEXITY SYS          | TEM TIMING                                           |                                                                                                                      |                      |                |                        | -    | <del></del> |

| CLK rise time                   | t <sub>CH1CH2</sub>                                  | From 1.0 V to 3.5 V <u>13</u> /<br>V <sub>DD</sub> = 4.5 V                                                           | 9,10,11              | ALL            |                        | 10   | ns          |

| CLK fall time                   | t <sub>CL2CL1</sub>                                  | From 3.5 V to 1.0 V <u>13</u> /<br>V <sub>DD</sub> = 4.5 V                                                           | 9,10,11              | ALL            |                        | 10   | ns          |

| DY setup time into<br>82C84A    | <sup>t</sup> R1VCL                                   | C <sub>L</sub> = 100 pF, V <sub>DD</sub> = V <sub>DDL</sub> ,<br>f = 1 MHz, V <sub>DD</sub> = 4.5 VL,<br>14/ 13/ 15/ | 9,10,11              | ALL            | 35                     |      | ns          |

| DY hold time into<br>82C84A     | t <sub>CLR1X</sub>                                   | $C_L = 100 \text{ pF}, V_{DD} = V_{DDL},$<br>$f = 1 \text{ MHz}, V_{DD} = 4.5 \text{ V},$<br>13/14/15/               | 9,10,11              | All            | 0                      |      | ns          |

| nput rise time<br>(except CLK)  | t <sub>ILIH</sub>                                    | From 0.8 V to 2.0 V<br>V <sub>DD</sub> = 4.5 V <u>13</u> /                                                           | 9,10,11              | All            |                        | 15   | ns          |

| nput fall time<br>(except CLK)  | tIHIL                                                | From 2.0 V to 0.8 V<br>V <sub>DD</sub> = 4.5 V <u>13</u> /                                                           | 9,10,11              | All            |                        | 15   | ns          |

| ee footnotes at end of          | table.                                               |                                                                                                                      |                      |                |                        |      | <del></del> |

| STANDARD MICROCIRCUIT DRAWING   |                                                      |                                                                                                                      | SIZE<br><b>A</b>     |                |                        | 596  | 2-96728     |

|                                 | DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                                                                                                                      |                      | EVISION        | LEVEL<br>A             | SHEE | T           |

| Test                                     | Symbol                      | Conditions 1/ -55°C < T <sub>A</sub> < +125°C unless otherwise specified | Group A<br>subgroups | Device<br>type | 1     | Unii |    |

|------------------------------------------|-----------------------------|--------------------------------------------------------------------------|----------------------|----------------|-------|------|----|

|                                          |                             |                                                                          |                      |                | Min   | Max  |    |

| MAXIMUM MODE SYSTEM TIM                  | ING (USING                  | 82C88 BUS CONTROLLER)                                                    |                      |                | +     |      |    |

| Command active delay<br>15/              | <sup>t</sup> CLML           | C <sub>L</sub> = 100 pF,<br>f = 1 MHz, V <sub>DD</sub> = 4.5 V           | 9,10,11              | All            | 5     | 35   | ns |

| 15/<br>Command inactive delay            | <sup>t</sup> CLMH           |                                                                          | 9,10,11              | ALL            | 5     | 35   | ns |

| Address float delay                      | <sup>t</sup> CLAZ           | _                                                                        | 9,10,11              | ALL            | tCLAX | 80   | ns |

| Status float delay                       | tcHSZ                       | _                                                                        | 9,10,11              | ALL            |       | 80   | ns |

| Status valid to ALE<br>high <u>15</u> /  | <sup>t</sup> svlH           |                                                                          | 9,10,11              | All            |       | 20   | ns |

| Status valid to MCE high 15/             | <sup>t</sup> sv <b>m</b> ch |                                                                          | 9,10,11              | ALL            |       | 30   | ns |

| CLK low to ALE high<br>valid <u>15</u> / | <sup>t</sup> CLLH           |                                                                          | 9,10,11              | Ali            |       | 20   | ns |

| ALE inactive delay <u>15</u> /           | t <sub>CHLL</sub>           |                                                                          | 9,10,11              | ALL            | 4     | 18   | ns |

| 15/<br>CLK low to MCE high               | <sup>t</sup> CLMCH          | 13/                                                                      | 9,10,11              | All            |       | 25   | ns |

| MCE inactive delay <u>15</u> /           | <sup>t</sup> CLMCL          |                                                                          | 9,10,11              | Ali            |       | 15   | ns |

| Data hold time                           | <sup>t</sup> CLDX2          | f = 1 MHz V <sub>DD</sub> = 4.5 V<br>C <sub>L</sub> = 100 pF,            | 9,10,11              | ALL            | 10    |      | ns |

| Control active delay                     | <sup>t</sup> cvnv           |                                                                          | 9,10,11              | ALL            | 5     | 45   | ns |

| Control inactive delay                   | <sup>t</sup> cvnx           |                                                                          | 9,10,11              | All            | 10    | 45   | ns |

| Direct control active delay              | <sup>t</sup> CHDTL          |                                                                          | 9,10,11              | Alt            |       | 50   | ns |

| Direct control inactive delay            | <sup>t</sup> CHDTH          | -                                                                        | 9,10,11              | All            |       | 30   | ns |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-96728

REVISION LEVEL

A

11

DESC FORM 193A JUL 94

**9**004708 0020240 856 🖿

| TABLE I. Electrical perform  1查询 = 5962 9672801 VOC "共立管理 to be perform  24 Min/Max in a security of the string to be performed."                                                                                        | ance characterist                     | tics - Continued.                                                   |                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------|-----------------------------|

| 3/ Verified on GO-NO GO test.                                                                                                                                                                                            |                                       |                                                                     |                             |

| 4/ Interchanging of force and sense conditions is permi<br>5/ I <sub>BHH</sub> should be measured after raising V <sub>IN</sub> to V <sub>DD</sub> and<br>following pins; 2-16, 26-32, 34-39.                            | tted.<br>then lowering t              | o valid input high level                                            | of 3.0 V on the             |

| following: pins 2-16, 34-39.                                                                                                                                                                                             | d then raising t                      | o valid input low level o                                           | f 0.8V on the               |

| $I$ / $I_{DDSB}$ tested during clock high time after HALT instring.  8/ $V_{IL} = 0.4 \text{ V}$ , $V_{IH} = 2.6 \text{ V}$ , $V_{ILC} = 0.4 \text{ V}$ , $V_{ICH} = V_{DD}$                                             | uction execution                      | V, V <sub>OH</sub> ≥ 1.5 V.                                         |                             |

| 8/ VIL = 0.4 V, VIH = 2.6 V, VILC = 0.4 V, VICH = VDD - 9/ VDD = 4.5 V, f = 1 MHz, VI = 0.4 V, VIH = 2.6 V, VIH = 10/ Applies only to T2 state (8 ns into T3).  11/ Setup requirement for asynchronous signal to guarant | LC = 0.4 V, VIHC<br>tee recognition ( | = V <sub>DD</sub> -U.4 V, V <sub>QL</sub> ≤ 1.5 v<br>at next clock. | v, v <sub>OH</sub> ≥ 1.5 v. |

| <ul> <li>12/ Load capacitance C<sub>L</sub> = 100 pF.</li> <li>13/ This parameter is guaranteed but not tested. This parameter is guaranteed but not tested. This parameter is characteristic.</li> </ul>                |                                       |                                                                     | esign or process            |

| 14/ Setup requirement for asynchronous signal only to gu 15/ Signal at 82084A or 82088 shown for reference only.                                                                                                         |                                       |                                                                     |                             |

| 16/ Status lines return to their inactive (logic one) st                                                                                                                                                                 | ate after CLK go                      | oes low and READY goes hig                                          | ph.                         |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

|                                                                                                                                                                                                                          |                                       |                                                                     |                             |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER                                                                                                                                                          | SIZE<br><b>A</b>                      |                                                                     | 5062 06720                  |

|                                                                                                                                                                                                                          |                                       | REVISION LEVE                                                       | 5962-96728                  |

| DAYTON, OHIO 45444                                                                                                                                                                                                       |                                       | REVISION LEVEL<br>A                                                 | 12                          |

| DESC FORM 193A  JUL 94  9004708 0020241                                                                                                                                                                                  | 702                                   |                                                                     |                             |

Powered by ICminer.com Electronic-Library Service CopyRight 2003

**--** 9004708 0020241 792 **--**

查询"5962-9672801VOC"供应商

| Device type        |                    | 01                 |                    |

|--------------------|--------------------|--------------------|--------------------|

| Case outline       | 9                  |                    |                    |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |

| 1                  | GND                | 21                 | RESET              |

| 2                  | AD14               | 22                 | READY              |

| 3                  | AD13               | 23                 | TEST               |

| 4                  | AD12               | 24                 | QS1 (INTA)         |

| 5                  | AD11               | 25                 | QSO (ALE)          |

| 6                  | AD10               | 26                 | SO (DEN)           |

| 7                  | AD9                | 27                 | S1 (DT/R)          |

| 8                  | AD8                | 28                 | S2 (M/10)          |

| 9                  | AD7                | 29                 | LOCK (WR)          |

| 10                 | AD6                | 30                 | RQ/GT1 (HLDA)      |

| 11                 | AD5                | 31                 | RQ/GTO (HOLD)      |

| 12                 | AD4                | 32                 | R D                |

| 13                 | AD3                | 33                 | MN/MX              |

| 14                 | AD2                | 34                 | BHE/S7             |

| 15                 | AD1                | 35                 | A19/S6             |

| 16                 | AD0                | 36                 | A18/S5             |

| 17                 | MMI                | 37                 | A17/S4             |

| 18                 | INTR               | 38                 | AD16/S3            |

| 19                 | CLK                | 39                 | AD15               |

| 20                 | GND                | 40                 | v <sub>DD</sub>    |

FIGURE 1. <u>Terminal connection</u>.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-96728

REVISION LEVEL

A

13

DESC FORM 193A

JUL 94

**9004708 0020242 629**

# 查询"5962-9672801VQC"供应商 EXECUTION UNIT RELOCATION RESISTER FILE REGISTER FILE DATA POINTER SEGMENT REGISTERS INDEX REGS MSTRUCTION POINTER 16-BIT ALU OUS INTERFACE UNIT A, A, ATVI TOTA, SEN, ALE, NOTO - LOCK CONTROL AND TIMING 250,051 <u>⋾</u>> इ.इ.ऊ CLK RESET READY HILTER MEMORY INTERFACE C-BUS ES C\$ BUS INTERFACE UNIT \$\$ 03 IP EXECUTION UNIT CL EXECUTION UNIT OL 51 DI FIGURE 2. Functional diagram. SIZE **STANDARD** Α MICROCIRCUIT DRAWING 5962-96728 **DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL** SHEET 14 DESC FORM 193A 9004708 0020243 565 🖿

**JUL 94**

### Note:

All signals switch between V<sub>OH</sub> and V<sub>OL</sub> unless otherwise specified.

RDY is sampled near the end of 12, 13, TW to determine if TW machines states are to be inserted.

3. Two INTA cycles run back-to-back. The MD80C86 local ADDR/DATA bus is inactive during both INTA cycles. Control signals are shown for the second INTA cycle.

4. Signals at MD82C85 are shown for reference only.

5. All timing measurements are made at 1.5 V unless otherwise specified.

6. The Coprocessor may not drive the busses outside the region shown without risking contention.

All input signals (other than CLK) must switch between  $V_{I\downarrow}$  Max - 0.4 V and  $V_{I\downarrow}$  MIN + 0.4. CLK must switch between 0.4 V and 3.9 V.  $t_R$  and  $t_F$  must be less than or equal to 15 ns. CLK  $t_r$  and  $t_f$  must be less than or equal to 10

8. Cascade address is valid between first and second INTA cycle.

Figure 3. <u>Timing waveform and load circuit</u>.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-96728  |

|---------------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                             |                  | REVISION LEVEL<br>A | SHEET<br>15 |

DESC FORM 193A

JUL 94

9004708 0020244 471 🖿

# 查询"5962-9672801VQC"供应商

### NOTES:

- 1.

- Unless otherwise specified, all signals switch between  $V_{QH}$  and  $V_{QL}$ . RDY <u>is s</u>sampled near the end of T2, T3, TW to determine if TW machines states are to be <u>inserted</u>. Two INTA cycles run back-to-back. The device local <u>ADDR</u>/DATA bus is inactive during both INTA cycles. Control for pointer address is shown for the second INTA cycle.

- Signals at 82085 are shown for reference only.

- 6. Unless otherwise specified, all timing measurements are made at 1.5  $\rm V.$

FIGURE 3. <u>Iiming waveform and load circuit</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-96728  |

|---------------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                             |                  | REVISION LEVEL<br>A | SHEET<br>16 |

DESC FORM 193A

**JUL 94**

9004708 0020245 338

#### NOTES:

- Unless otherwise specified, all signals switch between  $V_{OH}$  and  $V_{OL}$ . RDY is sampled near the end of T2, T3, TW to determ<u>ine</u> if TW machines states are to be inserted.

- 3. Cascade address is valid between first and second INTA cycle.

- Two INTA cycles run back-to-back. The device local ADDR DATA bus is inactive during both INTA cycles. Control for pointer address is shown for the second INTA cycle.

- Signals at device at 82C85 and 82C88 are shown for reference only.

- The issuance of the device command and control signals (MRDC MWTC, ANWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high of MD82C88 CEN.

- Unless otherwise specified, all timing measurements are made at 1.5 V.

- Status inactive in state just prior to T4.

FIGURE 3. <u>liming waveform and load circuit</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-96728         |

|---------------------------------------------------------------------------------------------|------------------|---------------------|--------------------|

|                                                                                             |                  | REVISION LEVEL<br>A | SHEET<br><b>17</b> |

DESC FORM 193A

**JUL 94**

**9004708 0020246 274 📼**

# 查询"5962-9672801VQC"供应商

### NOTES:

- Unless otherwise specified, all signals switch between V<sub>OH</sub> and V<sub>OL</sub>.

RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

Cascade address is valid between first and second INTA cycle.

- Two INTA cycles run back-to-back. The device local ADDR/DATA bus is inactive during both INTA cycles. Control for the pointer address is shown for the second INTA cycle.

- Signals for devices 82085 and 82088 are shown for reference only.

- The issuance of the 82088 command and control signals (MRDC MWTC, AMWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high 82088 CEN.

- Unless otherwise specified, all timing measurements are made at 1.5  $\rm V.$

- Status inactive in state just prior to 14.

FIGURE 3. <u>Timing waveform and load circuit</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-96728         |

|---------------------------------------------------------------------------------------------|------------------|---------------------|--------------------|

|                                                                                             |                  | REVISION LEVEL<br>A | SHEET<br><b>18</b> |

**DESC FORM 193A JUL 94**

**■ 9004708 0020247 100 ■**