www.ti.com SBES012-OCTOBER 2008

## **DUAL-CHANNEL IMAGE SENSOR ANALOG FRONT-END**

#### **FEATURES**

- Dual-Channel Image Signal Processing:

41.5-MHz Correlated Double Sampling (CDS)

Provided Sample/Hold (S/H) Mode

- Output Resolution: 16 Bits

- 16-Bit Analog-to-Digital Conversion:

41.5-MHz Conversion Rate (per Channel)

No Missing Codes Ensured

- 75-dB Input-Referred SNR (at 0-dB Gain)

- Programmable Black Level Clamping

- Programmable Gain Amplifier (PGA):

3 dB to +18 dB (through Analog Front Gain)

- Portable Operation:

Low Voltage: 2.7 V to 3.3 V

Low Power: 290 mW at 3.0 V, 36 MHz

#### **DESCRIPTION**

The VSP2590 is a dual-channel analog front-end for processing imager output signals. The device includes a correlated double sampler (CDS), programmable gain amplifier (PGA), analog-to-digital converter (ADC), input clamp, optical black (OB) level clamp loop, serial interface, adjustable sampling timing control, and reference voltage generator. The VSP2590 also provides a sample/hold (S/H) input mode.

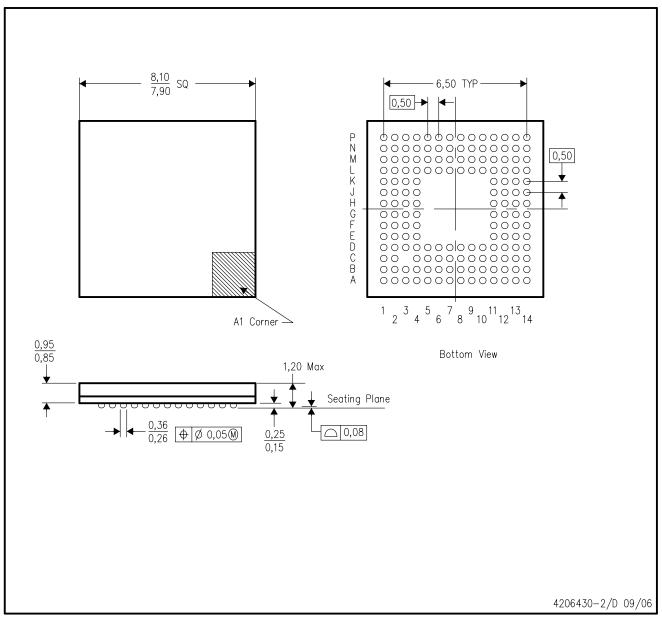

The VSP2590 is offered in a BGA-159 package and operates on a single +3 V supply.

df.dzsc.com

#### SBES042+OGTOBER 2009+ ... A

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|---------|------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| VSP2590 | BGA-159          | ZWV                   | –25°C to +85°C                    | VSDSEOO            | VSP2590ZWV         | Tray, 348                    |

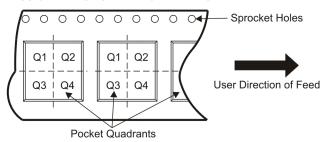

| V3F2590 | BGA-159          | ZVVV                  | -25 C 10 +65 C                    | VSP2590            | VSP2590ZWVR        | Tape and Reel, 1000          |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                                             | VSP2590             | UNIT |

|-----------------------------------------------------------------------------|---------------------|------|

| Supply voltage (AVDD, DLLVDD, DVDD, DRVDD, DIVDD, DIVDD2, CVDD)             | +4                  | V    |

| Supply voltage differences (among VCC pins)                                 | ±0.1                | V    |

| Ground voltage differences (AVSS, DLLVSS, DVSS, DRVSS, DIVSS, DIVSS2, CVSS) | ±0.1                | V    |

| Digital input voltage                                                       | -0.3 to (VDD + 0.3) | V    |

| Analog input voltage                                                        | -0.3 to (VCC + 0.3) | V    |

| Input current (all pins except supplies)                                    | ±10                 | mA   |

| Ambient temperature under bias                                              | -40 to +125         | °C   |

| Storage temperature                                                         | -55 to +150         | °C   |

| Junction temperature                                                        | +150                | °C   |

| Package temperature (IR reflow, peak)                                       | +260                | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

Submit Documentation Feedback

Copyright © 2008, Texas Instruments Incorporated

**\*\*室街®**\$P2590"供应商

SBES012-OCTOBER 2008

## **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = +25$ °C, all power-supply voltages = +3.0 V, and conversion rate = 36 MHz, unless otherwise noted.

|                |                                     |                                                | VSP2560ZWV |         |           |          |

|----------------|-------------------------------------|------------------------------------------------|------------|---------|-----------|----------|

|                | PARAMETER                           | TEST CONDITIONS                                | MIN        | TYP     | MAX       | UNIT     |

| RESOL          | UTION                               |                                                |            |         |           |          |

| Resoluti       | on                                  |                                                |            | 16      |           | Bits     |

| CHANN          | EL                                  |                                                |            |         |           |          |

| Channel        |                                     |                                                |            | 2       |           | Channels |

| CONVE          | RSION RATE                          |                                                |            |         |           |          |

| Maximui        | m conversion/clock rate             | VCC = 3.0 V                                    |            | 36      | 41.5      | MHz      |

| ANALO          | G INPUT (Channels A, B)             |                                                |            |         |           |          |

| Maximui<br>out | m input signal level for full-scale | Gain = -3 dB                                   |            | 1.5     |           | $V_{PP}$ |

| Maximui        | m input signal for full-scale out   | Gain = 0 dB                                    |            | 1.0     |           | $V_{PP}$ |

| Allowabl       | le input range                      |                                                |            |         | 2.5       | $V_{PP}$ |

| Input ca       | pacitance                           | Without package, stray, or ESD capacitance     |            | 15      |           | pF       |

| Input lim      | nit                                 |                                                | GND - 0.3  |         | VCC + 3.3 | V        |

| TRANSI         | FER CHARACTERISTICS (Chan           | nels A, B)                                     | 1          |         | '         |          |

| (DNL)          | Differential nonlinearity           |                                                |            | ±0.8    |           | LSB      |

| (1) (1)        |                                     |                                                |            | ±32     |           | LSB      |

| (INL)          | Integral nonlinearity               | Data range process = 0 mV to 100 mV            |            | ±10     |           | LSB      |

| No miss        | ing codes                           |                                                |            | Ensured |           |          |

| Signal-to      | o-noise ratio <sup>(1)</sup>        | Gain = 0 dB                                    |            | 75      |           | dB       |

| CCD offs       | set correction range                |                                                | -200       |         | 200       | mV       |

| PROGR          | AMMABLE GAIN                        |                                                | 1          |         |           |          |

| Analog (       | gain programmable range             |                                                | -3         |         | +18       | dB       |

| Analog (       | gain programmable step              |                                                |            | 3       |           | dB       |

| Analog (       | gain accuracy                       |                                                |            | ±0.3    |           | dB       |

| Analog (       | gain channel mismatch               |                                                |            | 5       |           | %        |

| Digital g      | ain programmable range              |                                                | 0          |         | 32        | dB       |

| Digital g      | ain programmable step               |                                                |            | 0.032   |           | dB       |

| INPUT (        | CLAMP (Channels A, B)               |                                                | 1          |         |           |          |

| Clamp o        | n-resistance                        |                                                |            | 400     |           | Ω        |

| Clamp le       | evel                                | Use internal reference                         |            | 1.8     |           | V        |

| OPTICA         | L BLACK CLAMP (OBCLP) LO            | OP .                                           | 1          |         |           |          |

|                | DAC resolution                      |                                                |            | 12      |           | Bits     |

| Loop tim       | ne constant                         |                                                |            | 40.7    |           | μs       |

|                |                                     | Programmable range of clamp level              | 1536       |         | 3072      | LSB      |

| Optical b      | plack clamp level                   | OBCLP level at code = 1000 0000 0000b (center) |            | 2048    |           | LSB      |

|                |                                     | OB level program step                          |            | 1       |           | LSB      |

<sup>(1)</sup> SNR = 20 log (full-scale voltage/rms noise).

## **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = +25$ °C, all power-supply voltages = +3.0 V, and conversion rate = 36 MHz, unless otherwise noted.

|                 |                          |                                                     | VSP2560Z |           |      |      |

|-----------------|--------------------------|-----------------------------------------------------|----------|-----------|------|------|

|                 | PARAMETER                | TEST CONDITIONS                                     | MIN      | TYP       | MAX  | UNIT |

| GENER           | AL-PURPOSE 8-BIT DAC (C  | Channels A, B)                                      |          |           |      |      |

| Minimu          | n output voltage         |                                                     |          | 0.1       |      | V    |

| Maximu          | m output voltage         |                                                     |          | 2.9       |      | V    |

| Differen        | tial nonlinearity        |                                                     |          | ±0.25     |      | LSB  |

| Integral        | nonlinearity             |                                                     |          | ±1        |      | LSB  |

| Offset e        | rror                     |                                                     |          | ±100      |      | mV   |

| Gain er         | or                       |                                                     |          | ±5        |      | %    |

| Monoto          | nicity                   |                                                     |          | Ensured   |      |      |

| Minimu          | n load resistance        |                                                     | 10       |           |      | kΩ   |

| Maximu          | m load capacitance       |                                                     |          |           | 1000 | pF   |

| DIGITA          | L INPUTS                 |                                                     |          |           |      |      |

| Logic fa        | mily                     |                                                     |          | CMOS      |      |      |

| V <sub>T+</sub> | Innut voltage            | Low-to-high threshold                               |          | 1.7       |      | V    |

| V <sub>T-</sub> | Input voltage            | High-to-low threshold                               |          | 1.0       |      | V    |

| I <sub>IH</sub> | Innut ourrent            | Logic high, V <sub>IN</sub> = +3 V                  |          |           | ±20  | μΑ   |

| I <sub>IL</sub> | Input current            | Logic low, V <sub>IN</sub> = 0 V                    |          |           | ±20  | μΑ   |

| MCLK o          | lock duty cycle          |                                                     |          | 50        |      | %    |

| Input ca        | pacitance                |                                                     |          | 5         |      | pF   |

| DIGITA          | L OUTPUT (Channels A, B) |                                                     |          |           |      |      |

| Logic fa        | mily                     |                                                     |          | CMOS      |      |      |

| Logic co        | oding                    |                                                     | Straig   | ht binary |      |      |

| V <sub>OH</sub> | Output walta as          | DRVDD = 3.0 V, logic high, $I_{OH} = -2 \text{ mA}$ |          | 2.8       |      | V    |

| V <sub>OL</sub> | Output voltage           | DRVDD = 3.0 V, logic low, I <sub>OL</sub> = 2 mA    |          | 0.2       |      | V    |

| VCC,<br>VDD     | Supply voltage           |                                                     | 2.7      | 3.0       | 3.3  | V    |

|                 |                          | Not using DLL, gain = 0 dB                          |          | 290       |      | mW   |

|                 |                          | Not using DLL, gain = +18 dB                        |          | 310       |      | mW   |

| Power of        | dissipation              | Using DLL, gain = 0 dB                              |          | 320       |      | mW   |

|                 |                          | Using DLL, gain = +18 dB                            |          | 340       |      | mW   |

|                 |                          | Standby mode                                        |          | 4.5       |      | mW   |

| TEMPE           | RATURE RANGE (TOPR)      |                                                     |          |           | 1    |      |

| Operati         | ng temperature           |                                                     | -25      |           | +85  | °C   |

| $\theta_{JA}$   | Thermal resistance       |                                                     |          | +40       |      | °C/W |

Submit Documentation Feedback

Copyright © 2008, Texas Instruments Incorporated

www.情eor/SP2590"供应商

SBES012-OCTOBER 2008

## **TIMING CHARACTERISTICS**

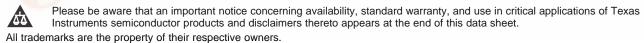

## POWER-ON/POWER-OFF SEQUENCE

Figure 1. Power-On/Power-Off Reset Sequence

## **Reset Standby Function**

| MODE    | REGISTER | CDS        | ADC        | RG<br>CONTROL<br>BUFFER | H1<br>CONTROL<br>BUFFER | H2<br>CONTROL<br>BUFFER | LH<br>CONTROL<br>BUFFER | DLL                   |

|---------|----------|------------|------------|-------------------------|-------------------------|-------------------------|-------------------------|-----------------------|

| Reset   | Clear    | Not active | Not active | Low                     | High                    | Low                     | High                    | Active <sup>(1)</sup> |

| Standby | Active   | Not active | Not active | Low                     | High                    | Low                     | High                    | Active                |

(1) DLL is stopped by a DLL reset of a register.

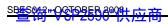

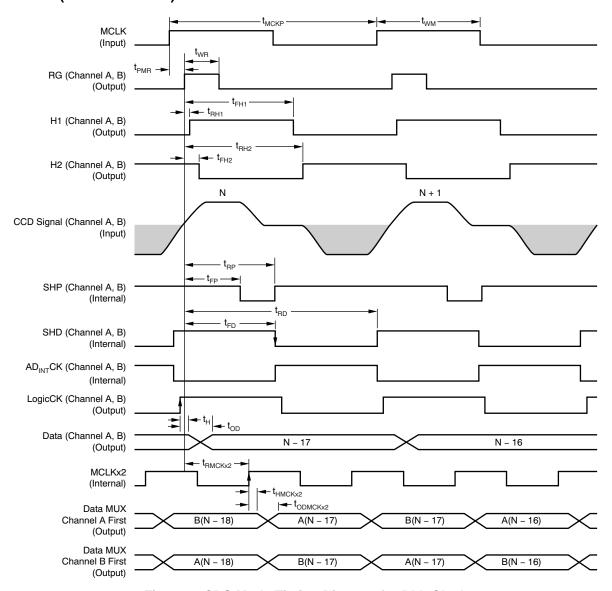

## **DLL CLOCK (PER CHANNEL)**

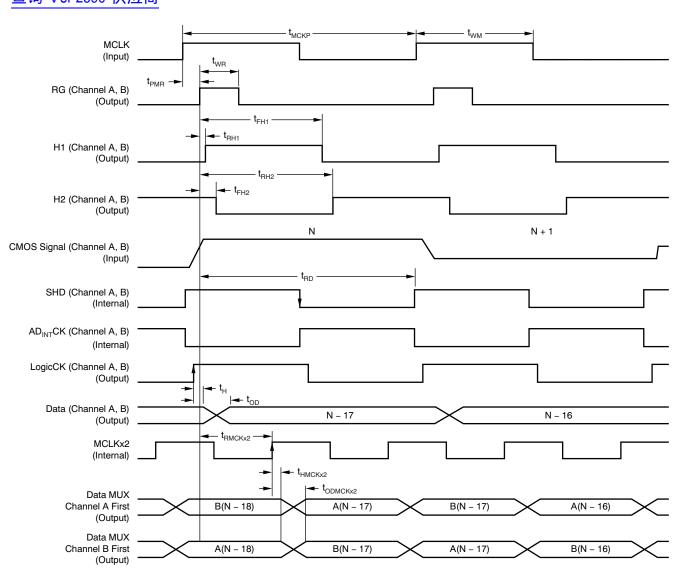

Figure 2. CDS Mode Timing Diagram for DLL Clock

<u>₩豐街•₩SP2590"供应商</u>

SBES012-OCTOBER 2008

# CDS Mode Timing Characteristics for Figure 2<sup>(1)(2)</sup>

|                       | PARAMETER                  | MIN                      | TYP                     | MAX                     | UNIT   |

|-----------------------|----------------------------|--------------------------|-------------------------|-------------------------|--------|

| t <sub>MCKP</sub>     | Master clock period        | _                        | 27                      |                         | ns     |

| t <sub>WMCK</sub>     | Master clock width         | _                        | 13.5                    |                         | ns     |

| t <sub>PMR</sub>      | Delay master clock↑ to RG↑ |                          | 2.0                     |                         | ns     |

| t <sub>WR</sub>       | RG pulse width             | t <sub>MCKP</sub> 4/64   | t <sub>MCKP</sub> 20/64 | t <sub>MCKP</sub> 35/64 | ns     |

| t <sub>RH1</sub>      | Delay RG clock↑ to H1↑     | -t <sub>MCKP</sub> 16/64 | 0                       | t <sub>MCKP</sub> 15/64 | ns     |

| t <sub>FH1</sub>      | Delay RG clock↑ to H1↓     | t <sub>MCKP</sub> 16/64  | t <sub>MCKP</sub> 32/64 | t <sub>MCKP</sub> 47/64 | ns     |

| t <sub>RH2</sub>      | Delay RG clock↑ to H2↑     | t <sub>MCKP</sub> 16/64  | t <sub>MCKP</sub> 32/64 | t <sub>MCKP</sub> 47/64 | ns     |

| t <sub>FH2</sub>      | Delay RG clock↑ to H2↓     | -t <sub>MCKP</sub> 16/64 | 0                       | t <sub>MCKP</sub> 15/64 | ns     |

| t <sub>RLH</sub>      | Delay RG clock↑ to LH↑     | -t <sub>MCKP</sub> 16/64 | 0                       | t <sub>MCKP</sub> 15/64 | ns     |

| t <sub>FLH</sub>      | Delay RG clock↑ to LH↓     | t <sub>MCKP</sub> 16/64  | t <sub>MCKP</sub> 32/64 | t <sub>MCKP</sub> 47/64 | ns     |

| t <sub>RP</sub>       | Delay RG clock↑ to SHP↑    | t <sub>MCKP</sub> 10/64  | t <sub>MCKP</sub> 26/64 | t <sub>MCKP</sub> 41/64 | ns     |

| t <sub>FP</sub>       | Delay RG clock↑ to SHP↓    | -t <sub>MCKP</sub> 3/64  | t <sub>MCKP</sub> 13/64 | t <sub>MCKP</sub> 28/64 | ns     |

| t <sub>RD</sub>       | Delay RG clock↑ to SHD↑    | t <sub>MCKP</sub> 42/64  | t <sub>MCKP</sub> 58/64 | t <sub>MCKP</sub> 73/64 | ns     |

| t <sub>FD</sub>       | Delay RG clock↑ to SHD↓    | t <sub>MCKP</sub> 11/64  | t <sub>MCKP</sub> 27/64 | t <sub>MCKP</sub> 42/64 | ns     |

| t <sub>RMCKx2</sub>   | Delay RG clock↑ to 2MCLK↑  | t <sub>MCKP</sub> 5/64   | t <sub>MCKP</sub> 21/64 | t <sub>MCKP</sub> 36/64 | ns     |

| SDLL                  | DLL step                   |                          | t <sub>MCKP</sub> /64   |                         | ns     |

| t <sub>H</sub>        | Data hold time             | 1.3                      | 1.7                     | 2.5                     | ns     |

| t <sub>OD</sub>       | Data output delay          | 2.6                      | 3.7                     | 6.1                     | ns     |

| t <sub>HMCLKx2</sub>  | MUX data hold time         | 1.7                      | 2.3                     | 3.7                     | ns     |

| t <sub>ODMCLKx2</sub> | MUX data output delay      | 3.4                      | 2.6                     | 7.2                     | ns     |

| CDL                   | Master clock latency       | _                        | 17                      | _                       | Clocks |

$T_{\text{FP}} < T_{\text{RP}}.$  When a master clock stops, the DLL stops and returns to a standby condition.

SBESNAH OCTOBER 2004 应商 www.ti.com

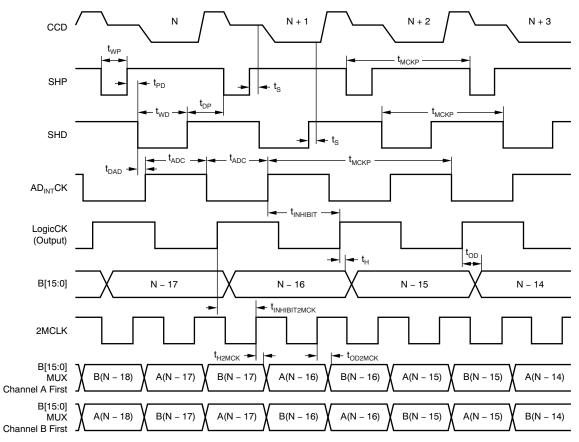

Figure 3. S/H Mode Timing Diagram for DLL Clock

<del>"≝街®</del>\$₽2590"供应商

SBES012-OCTOBER 2008

# S/H Mode Timing Characteristics for Figure 3<sup>(1)(2)</sup>

|                       | PARAMETER                  | MIN                      | TYP                     | MAX                     | UNIT   |

|-----------------------|----------------------------|--------------------------|-------------------------|-------------------------|--------|

| t <sub>MCKP</sub>     | Master clock period        | _                        | 27                      |                         | ns     |

| t <sub>WMCK</sub>     | Master clock width         | _                        | 13.5                    |                         | ns     |

| t <sub>PMR</sub>      | Delay master clock↑ to RG↑ |                          | 2.0                     |                         | ns     |

| t <sub>WR</sub>       | RG pulse width             | t <sub>MCKP</sub> 4/64   | t <sub>MCKP</sub> 20/64 | t <sub>MCKP</sub> 35/64 | ns     |

| t <sub>RH1</sub>      | Delay RG clock↑ to H1↑     | -t <sub>MCKP</sub> 16/64 | 0                       | t <sub>MCKP</sub> 15/64 | ns     |

| t <sub>FH1</sub>      | Delay RG clock↑ to H1↓     | t <sub>MCKP</sub> 16/64  | t <sub>MCKP</sub> 32/64 | t <sub>MCKP</sub> 47/64 | ns     |

| t <sub>RH2</sub>      | Delay RG clock↑ to H2↑     | t <sub>MCKP</sub> 16/64  | t <sub>MCKP</sub> 32/64 | t <sub>MCKP</sub> 47/64 | ns     |

| t <sub>FH2</sub>      | Delay RG clock↑ to H2↓     | -t <sub>MCKP</sub> 16/64 | 0                       | t <sub>MCKP</sub> 15/64 | ns     |

| t <sub>RLH</sub>      | Delay RG clock↑ to LH↑     | -t <sub>MCKP</sub> 16/64 | 0                       | t <sub>MCKP</sub> 15/64 | ns     |

| t <sub>FLH</sub>      | Delay RG clock↑ to LH↓     | t <sub>MCKP</sub> 16/64  | t <sub>MCKP</sub> 32/64 | t <sub>MCKP</sub> 47/64 | ns     |

| t <sub>RD</sub>       | Delay RG clock↑ to SHD↑    | t <sub>MCKP</sub> 42/64  | t <sub>MCKP</sub> 58/64 | t <sub>MCKP</sub> 73/64 | ns     |

| t <sub>FD</sub>       | Delay RG clock↑ to SHD↓    |                          | t <sub>MCKP</sub> 27/64 |                         | ns     |

| t <sub>RMCLKx2</sub>  | Delay RG clock↑ to 2MCLK↑  | t <sub>MCKP</sub> 5/64   | t <sub>MCKP</sub> 21/64 | t <sub>MCKP</sub> 36/64 | ns     |

| SDLL                  | DLL step                   |                          | t <sub>MCKP</sub> /64   |                         | ns     |

| t <sub>H</sub>        | Data hold time             | 1.3                      | 1.7                     | 2.5                     | ns     |

| t <sub>OD</sub>       | Data output delay          | 2.6                      | 3.7                     | 6.1                     | ns     |

| t <sub>HMCLKx2</sub>  | MUX data hold time         | 1.7                      | 2.3                     | 3.7                     | ns     |

| t <sub>ODMCLKx2</sub> | MUX data output delay      | 3.4                      | 2.6                     | 7.2                     | ns     |

| CDL                   | Master clock latency       | _                        | 17                      | _                       | Clocks |

$T_{\text{FP}} < T_{\text{RP}}.$  When a master clock stops, the DLL stops and returns to a standby condition.

## **EXTERNAL CLOCK (PER CHANNEL)**

Figure 4. CDS Mode Timing Diagram for External Clock

## CDS Mode Timing Characteristics for Figure 4<sup>(1)</sup>

|                          | PARAMETER                                                   | MIN | TYP  | MAX | UNIT   |

|--------------------------|-------------------------------------------------------------|-----|------|-----|--------|

| t <sub>MCKP</sub>        | Clock period                                                |     | 27   |     | ns     |

| t <sub>ADC</sub>         | AD <sub>INT</sub> CK high or low level                      |     | 13.5 |     | ns     |

| $t_{WP}$                 | SHP pulse width                                             |     | 6    |     | ns     |

| $t_{WD}$                 | SHD pulse width                                             |     | 13.5 |     | ns     |

| t <sub>PD</sub>          | SHP↑ to SHD↓                                                |     | 0    |     | ns     |

| t <sub>DP</sub>          | SHD↑ to SHP↓                                                |     | 9    |     | ns     |

| t <sub>S</sub>           | Sampling delay                                              |     | 3    |     | ns     |

| t <sub>DAD</sub>         | SHD↓ to AD <sub>INT</sub> CK↑                               |     | 0    |     | ns     |

| t <sub>INHIBIT</sub>     | Inhibit clock period from AD <sub>INT</sub> CK↑ to LogicCK↑ | 4   | 7    | 10  | ns     |

| t <sub>H</sub>           | Data hold time                                              | 1.3 | 1.7  | 2.5 | ns     |

| t <sub>OD</sub>          | Data output delay                                           | 2.6 | 3.7  | 6.1 | ns     |

| t <sub>HMCLKx2</sub>     | MUX data hold time                                          | 1.7 | 2.3  | 3.7 | ns     |

| t <sub>ODMCLKx2</sub>    | MUX data output delay                                       | 3.4 | 2.6  | 7.2 | ns     |

| t <sub>INHIBIT2MCK</sub> | Inhibit clock period from LogicCK↑ to 2MCLK↑                | 1.3 | 3.7  | 6.1 | ns     |

| DL                       | Data latency                                                |     | 17   |     | Clocks |

<sup>(1)</sup>  $t_{WP} + t_{PD}$  should be nearly equal to  $t_{WD} + t_{DP}$ .

<u>₩豐梅♥♥\$P2590"供应商</u>

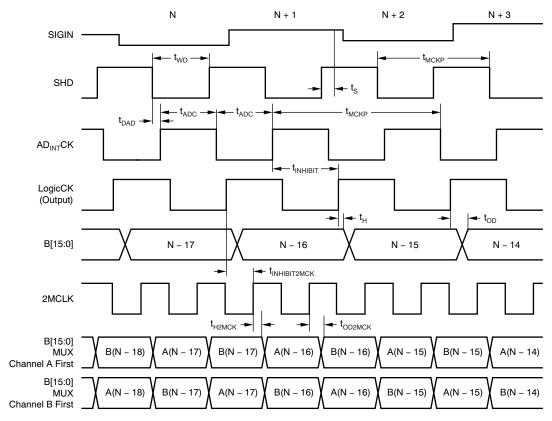

Figure 5. S/H Mode Timing Diagram for External Clock

## S/H Mode Timing Characteristics for Figure 5<sup>(1)</sup>

|                          | PARAMETER                                                   | MIN | TYP  | MAX | UNIT   |

|--------------------------|-------------------------------------------------------------|-----|------|-----|--------|

| t <sub>MCKP</sub>        | Clock period                                                |     | 27   |     | ns     |

| t <sub>ADC</sub>         | AD <sub>INT</sub> CK high or low level                      |     | 13.5 |     | ns     |

| t <sub>WD</sub>          | SHD pulse width                                             |     | 6    |     | ns     |

| t <sub>S</sub>           | Sampling delay                                              |     | 3    |     | ns     |

| t <sub>DAD</sub>         | SHD↓ to AD <sub>INT</sub> CK↑                               |     | 0    |     | ns     |

| t <sub>INHIBIT</sub>     | Inhibit clock period from AD <sub>INT</sub> CK↑ to LogicCK↑ | 4   | 7    | 10  | ns     |

| t <sub>H</sub>           | Data hold time                                              | 1.3 | 1.7  | 2.5 | ns     |

| t <sub>OD</sub>          | Data output delay                                           | 2.6 | 3.7  | 6.1 | ns     |

| t <sub>HMCLKx2</sub>     | MUX data hold time                                          | 1.7 | 2.3  | 3.7 | ns     |

| t <sub>ODMCLKx2</sub>    | MUX data output delay                                       | 3.4 | 2.6  | 7.2 | ns     |

| t <sub>INHIBIT2MCK</sub> | Inhibit clock period from LogicCK↑ to 2MCLK↑                | 1.3 | 3.7  | 6.1 | ns     |

| DL                       | Data latency                                                |     | 17   |     | Clocks |

<sup>(1)</sup>  $t_{WP} + t_{PD}$  should be nearly equal to  $t_{WD} + t_{DP}$ .

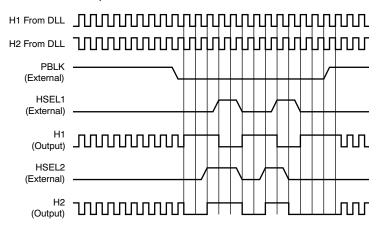

## H1, H2, HSEL1, HSEL2, AND PBLK

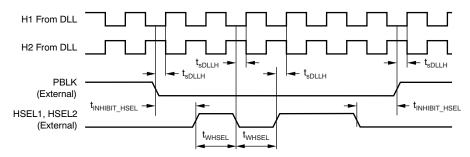

#### H1 and H2 Timing While PBLK is Low (per channel)

When PBLK is low, H1 is fixed high and H2 is fixed low. For the duration that PBLK is low, H1 and H2 can be toggled only by the HSEL1 and HSEL2 input.

Figure 6. H1 and H2 Timing Diagram

## HSEL1, HSEL2, and PBLK Timing

Figure 7. HSEL1, HSEL2, and PBLK Timing Diagram

## Timing Characteristics for Figure 7

| PARAMETER                  |                                                 | MIN                | TYP | MAX                | UNIT |

|----------------------------|-------------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>INHIBIT_</sub> HSEL | HSEL high period inhibit timing (from PBLK)     | -t <sub>MCKP</sub> |     | +t <sub>MCKP</sub> | ns   |

| t <sub>WHSEL</sub>         | HSEL high/low period                            | t <sub>MCKP</sub>  |     |                    | ns   |

| t <sub>sDLLH</sub>         | Setup time H1/H2 (from DLL) to PBLK/HSEL1/HSEL2 | 800                |     |                    | ps   |

**^唑特•**\$P2590"(共長

SBES012-OCTOBER 2008

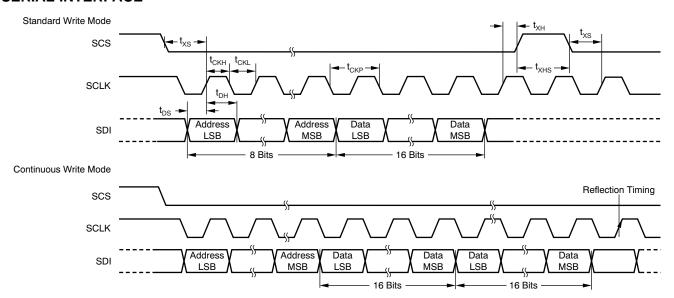

#### **SERIAL INTERFACE**

Figure 8. Serial Interface Timing Diagram

### **Update Timing**

#### **Immediate Update:**

The data shift operation should decode at the rising edge of SCLK while S<sub>LOAD</sub> is low. 16 bits of input data are loaded to the parallel latch in the VSP2590 at the rising edge of SCS.

#### **External Sync Update:**

Register update timing is synchronized with the falling edge of UPDATE\_REG.

### **Continuous Writing**

Continuous write mode is used when transmitting a large set of data. Receiving data initiates at the falling edge of S<sub>LOAD</sub> and continues while S<sub>LOAD</sub> is low. It is only necessary to transmit the starting address data; after that transmission, the address increments by one automatically. The data stream then consists of the starting address followed by the data for that register, then the data for the next register, and so on. The device accepts data for sequential registers as long as  $\tilde{S}_{LOAD}$  is low. When  $S_{LOAD}$  goes high, no more registers are written to.

### Over or Shortage Data Input

16-bit data are counted by SCLK. Any over or shortage data are ignored.

## Timing Characteristics for Figure 8

|                  | PARAMETER                            |    | TYP | MAX | UNIT |

|------------------|--------------------------------------|----|-----|-----|------|

| t <sub>CKP</sub> | Clock period                         | 50 |     |     | ns   |

| t <sub>CKH</sub> | Clock high pulse width               | 25 |     |     | ns   |

| t <sub>CKL</sub> | Clock low pulse width                | 25 |     |     | ns   |

| t <sub>DS</sub>  | Data setup time                      | 15 |     |     | ns   |

| t <sub>DH</sub>  | Data hold time                       | 15 |     |     | ns   |

| t <sub>XS</sub>  | S <sub>LOAD</sub> to SCLK setup time | 20 |     |     | ns   |

| t <sub>XH</sub>  | SCLK to CS hold time                 | 50 |     |     | ns   |

| t <sub>XHS</sub> | CS width                             | 50 |     |     | ns   |

Copyright © 2008, Texas Instruments Incorporated

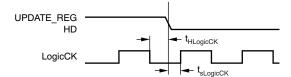

### **REGISTER UPDATE**

Figure 9. Register Update Timing Diagram

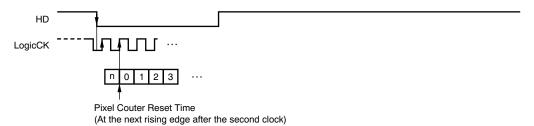

## **PIXEL COUNT-UP START TIMING**

Figure 10. Pixel Count-Up Timing Diagram

Figure 11. LogicCK Timing Diagram

## **Timing Characteristics for Figure 11**

| PARAMETER             |                                                | MIN | TYP | MAX | UNIT |

|-----------------------|------------------------------------------------|-----|-----|-----|------|

| t <sub>SLogicCK</sub> | Setup time LogicCK to UPDATE_REG/UPDATE_INL/HD | 800 |     |     | ps   |

| t <sub>HLogicCK</sub> | Hold time LogicCK to UPDATE_REG/UPDATE_INL/HD  | 2.0 |     |     | ns   |

<u>₩營销<sup>®</sup>切SP2590"供应商</u>

SBES012-OCTOBER 2008

## **PIN CONFIGURATION**

## **ZWV PACKAGE** BGA-159 (TOP VIEW)

|   | 1       | 2      | 3        | 4       | 5       | 6      | 7     | 8         | 9      | 10         | 11       | 12         | 13                | 14      |

|---|---------|--------|----------|---------|---------|--------|-------|-----------|--------|------------|----------|------------|-------------------|---------|

| Α | AVSSA   | COBA   | TEST_ref | CMA     | REFNA   | REFPA  | CVDDA | LogicCKAD | MnSHPA | MnLogicCKA | CVDDA    | BYPDA      | DLLVSSA           | MCLKA   |

| В | AVDDA   | AVSSA  | BYPCMA   | REFVSSA | REFVDDA | GNDG   | CVSSA | MCLKx2in  | MnSHDA | PBLK       | CVSSA    | DLLVSSA    | DLLVDDA           | DLLVDDA |

| С | CCDINA  | AVSSA  |          | DOUT21  | DOUT17  | DOUT13 | DVSS  | DOUT9     | DOUT5  | DOUT1      | DVSS     | DVDD       | DVSS              | DVDD    |

| D | CCDGNDA | AVSSA  | DVDD     | DOUT23  | DOUT19  | DOUT15 | DVDD  | DOUT11    | DOUT7  | DOUT3      | RGA      | H2A        | H1A               | LHA     |

| Ε | AVDDA   | AVDDA  | UDACOUT1 | DOUT25  |         |        |       |           |        |            | DRVDD    | DRVDD      | DRVSS             | DRVSS   |

| F | CLPDMA  | DIVSSA | DIVDDA   | DOUT27  |         |        |       |           |        |            | HSEL1    | HSEL2      | TEST_UPDATE       | SCLK    |

| G | CLPOBA  | DIVSSA | DOUT31   | DOUT29  |         |        |       |           |        |            | TEST_IN  | UPDATE_REG | S <sub>LOAD</sub> | DIVSS2  |

| Н | CLPOBB  | DIVSSB | DOUT30   | DOUT28  |         |        |       |           |        |            | TEST_OUT | SDI        | RESET<br>(XCLR)   | DIVSS2  |

| J | CLPDMB  | DIVSSB | DIVDDB   | DOUT26  |         |        |       |           |        |            | TEST_IN  | DIVDD2     | DIVSS2            | DIVSS2  |

| K | AVDDB   | AVDDB  | UDACOUT2 | DOUT24  |         |        |       |           |        |            | DRVDD    | DRVDD      | DRVSS             | DRVSS   |

| K | CCGNDB  | AVSSB  | DVDD     | DOUT22  | DOUT18  | DOUT14 | DVDD  | DOUT10    | DOUT6  | DOUT2      | RGB      | H2B        | H1B               | LHB     |

| K | CCDINB  | AVSSB  | DVSS     | DOUT20  | DOUT16  | DOUT12 | DVSS  | DOUT8     | DOUT4  | DOUT0      | DVSS     | DVDD       | DVSS              | DVDD    |

| K | AVDDB   | AVSSB  | ВҮРСМВ   | REFVSSB | REFVDDB | GNDG   | CVSSB | TEST_IN   | MnSHDB | HD         | CVSSB    | DLLVSSB    | DLLVDDB           | DLLVDDB |

| K | AVSSB   | COBB   | TEST_ref | СМВ     | REFNB   | REFPB  | CVDDB | LogicCKBD | MnSHPB | MnLogicCKB | CVDDB    | BYPDB      | DLLVSSB           | MCLKB   |

## **TERMINAL FUNCTIONS**

| TERMINAL |            |     |                                                                        |

|----------|------------|-----|------------------------------------------------------------------------|

| NAME     | NO.        | I/O | DESCRIPTION                                                            |

| A1       | AVSSA      | Р   | Analog GND (channel A)                                                 |

| A2       | COBA       | AO  | OB loop output voltage connected to a 0.1-μF capacitor (channel A)     |

| A3       | Test_ref   | AO  | Test setting pin (Hi-Z)                                                |

| A4       | CMA        | AO  | Analog common dc reference connected to a 0.1-μF capacitor (channel A) |

| A5       | REFNA      | AO  | ADC negative reference connected to a 0.1-µF capacitor (channel A)     |

| A6       | REFPA      | AO  | ADC positive reference connected to a 0.1-µF capacitor (channel A)     |

| A7       | CVDDA      | Р   | Mask block power supply (channel A)                                    |

| A8       | LogicCKAD  | DO  | Logic clock output (channel A) for digital chip and total output       |

| A9       | MnSHPA     | DIO | SHP monitor out/external SHP input (channel A)                         |

| A10      | MnLogicCKA | DIO | MCLKx2 monitor out/external logicCK input (channel A)                  |

| A11      | CVDDA      | Р   | HTG block power supply (channel A)                                     |

| A12      | BYPDA      | AO  | DLL bypass connected to DLLVDD 1000-pF capacitor (channel A)           |

| A13      | DLLVSSA    | Р   | DLL GND (channel A)                                                    |

| A14      | MCLKA      | DI  | Masker clock (channel A) input                                         |

| B1       | AVDDA      | Р   | Analog power supply (channel A)                                        |

| B2       | AVSSA      | Р   | Analog GND (channel A)                                                 |

| В3       | BYPCMA     | AO  | Analog positive reference connected to a 0.1-μF capacitor (channel A)  |

| B4       | REFVSSA    | Р   | Reference block GND (channel A)                                        |

| B5       | REFVDDA    | Р   | Reference block power supply (channel A)                               |

| B6       | GNDG       | Р   | SUB GND                                                                |

| В7       | CVSSA      | Р   | Mask block GND (channel A)                                             |

| B8       | MCLKx2in   | DI  | External CLKx2 input                                                   |

| В9       | MnSHDA     | DIO | SHD monitor out/external SHD input (channel A)                         |

| B10      | PBLK       | DI  | Pre-blanking signal input; connect to DVDD when PBLK is not used       |

| B11      | CVSSA      | Р   | HTG block GND (channel A)                                              |

| B12      | DLLVSSA    | Р   | DLL GND (channel A)                                                    |

| B13      | DLLVDDA    | Р   | DLL power supply (channel A)                                           |

| B14      | DLLVDDA    | Р   | DLL power supply (channel A)                                           |

| C1       | CCDINA     | Al  | CCD/CMOS sensor signal input (channel A)                               |

## **TERMINAL FUNCTIONS (continued)**

| TER  | TERMINAL    |     | TERMINAL FORCTIONS (CONTINUES)                                        |  |  |  |  |  |

|------|-------------|-----|-----------------------------------------------------------------------|--|--|--|--|--|

| NAME | NO.         | 1/0 | DESCRIPTION                                                           |  |  |  |  |  |

| C2   | AVSSA       | Р   | Analog GND (channel A)                                                |  |  |  |  |  |

| C4   | DOUT21      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| C5   | DOUT17      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| C6   | DOUT13      | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| C7   | DVSS        | Р   | Digital GND                                                           |  |  |  |  |  |

| C8   | DOUT9       | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| C9   | DOUT5       | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| C10  | DOUT1       | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| C11  | DVSS        | Р   | Digital GND                                                           |  |  |  |  |  |

| C12  | DVDD        | Р   | Digital power supply                                                  |  |  |  |  |  |

| C13  | DVSS        | Р   | Digital GND                                                           |  |  |  |  |  |

| C14  | DVDD        | Р   | Digital power supply                                                  |  |  |  |  |  |

| D1   | CCDGNDA     | Al  | CCD GND connection/CMOS sensor signal input (channel A)               |  |  |  |  |  |

| D2   | AVSSA       | Р   | Analog GND (channel A)                                                |  |  |  |  |  |

| D3   | DVDD        | Р   | Digital power supply                                                  |  |  |  |  |  |

| D4   | DOUT23      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| D5   | DOUT19      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| D6   | DOUT15      | DO  | Data output, MSB (channel B/MUX)                                      |  |  |  |  |  |

| D7   | DVDD        | Р   | Digital power supply                                                  |  |  |  |  |  |

| D8   | DOUT11      | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| D9   | DOUT7       | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| D10  | DOUT3       | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| D11  | RGA         | DO  | RG pulse output (channel A)                                           |  |  |  |  |  |

| D12  | H2A         | DO  | H2 pulse output (channel A)                                           |  |  |  |  |  |

| D13  | H1A         | DO  | H1 pulse output (channel A)                                           |  |  |  |  |  |

| D14  | LHA         | DO  | LH pulse output (channel A)                                           |  |  |  |  |  |

| E1   | AVDDA       | Р   | Analog power supply (channel A)                                       |  |  |  |  |  |

| E2   | AVDDA       | Р   | Analog power supply (channel A)                                       |  |  |  |  |  |

| E3   | UDACOUT1    | AO  | Universal DAC1 output                                                 |  |  |  |  |  |

| E4   | DOUT25      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| E11  | DRVDD       | Р   | Digital out power supply                                              |  |  |  |  |  |

| E12  | DRVDD       | Р   | Digital out power supply                                              |  |  |  |  |  |

| E13  | DRVSS       | Р   | Digital out GND                                                       |  |  |  |  |  |

| E14  | DRVSS       | Р   | Digital out GND                                                       |  |  |  |  |  |

| F1   | CLPDMA      | DI  | CLPDM pulse input (channel A); connect to DVDD when CLPDM is not used |  |  |  |  |  |

| F2   | DIVSSA      | P   | CLKGEN GND supply (channel A)                                         |  |  |  |  |  |

| F3   | DIVDDA      | P   | CLKGEN power supply (channel A)                                       |  |  |  |  |  |

| F4   | DOUT27      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| F11  | HSEL1       | DI  | Horizontal mask timing 1; connect to GND when HSEL1 is not used       |  |  |  |  |  |

| F12  | HSEL2       | DI  | Horizontal mask timing 2; connect to GND when HSEL2 is not used       |  |  |  |  |  |

| F13  | TEST_Update | DI  | Test setting pin; connect to DVDD                                     |  |  |  |  |  |

| F14  | SCLK        | DI  | Serial interface clock                                                |  |  |  |  |  |

| G1   | CLPOBA      | DI  | CLPOB pulse input (channel A); connect to DVDD when CLPOB is not used |  |  |  |  |  |

| G2   | DIVSSA      | P   | CLKGEN GND supply (channel A)                                         |  |  |  |  |  |

| G3   | DOUT31      | DO  | Data output, MSB (channel A)                                          |  |  |  |  |  |

| G4   | DOUT31      | DO  | Data output (channel A)                                               |  |  |  |  |  |

| G11  |             | DI  |                                                                       |  |  |  |  |  |

|      | TEST_IN     |     | Test setting pin; connect to GND                                      |  |  |  |  |  |

| G12  | UPDATE_REG  | DI  | Serial interface signal                                               |  |  |  |  |  |

| G13  | SLOAD       | DI  | SPI signal                                                            |  |  |  |  |  |

| G14  | DIVSS2      | Р   | Serial interface GND                                                  |  |  |  |  |  |

<u>₩營销<sup>®</sup>切SP2590"供应商</u>

SBES012-OCTOBER 2008

## **TERMINAL FUNCTIONS (continued)**

| TERMINAL   |          |     |                                                                       |  |  |  |  |  |

|------------|----------|-----|-----------------------------------------------------------------------|--|--|--|--|--|

| NAME       | NO.      | 1/0 | DESCRIPTION                                                           |  |  |  |  |  |

| H1         | CLPOBB   | DI  | CLPOB pulse input (channel B); Connect to DVDD when CLPOB is not used |  |  |  |  |  |

| H2         | DIVSSB   | Р   | CLKGEN GND supply (channel B)                                         |  |  |  |  |  |

| H3         | DOUT30   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| H4         | DOUT28   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| H11        | TEST_OUT | DO  | Test setting pin (normal operation = Hi-Z)                            |  |  |  |  |  |

| H12        | SDI      | DI  | SRI signal                                                            |  |  |  |  |  |

| H13        | RESET    | DI  | System reset; connect to DVDD when RESET is not used                  |  |  |  |  |  |

| H14        | DIVSS2   | Р   | Serial interface GND                                                  |  |  |  |  |  |

| J1         | CLPDMB   | DI  | CLPDM pulse input (channel B); connect to DVDD when CLPDM is not used |  |  |  |  |  |

| J2         | DIVSSB   | Р   | CLKGEN GND supply (channel B)                                         |  |  |  |  |  |

| J3         | DIVDDB   | Р   | CLKGEN power supply (channel B)                                       |  |  |  |  |  |

| J4         | DOUT26   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| J11        | TEST_IN  | DI  | Test setting pin; connect to GND                                      |  |  |  |  |  |

| J12        | DIVDD2   | Р   | Serial interface power supply                                         |  |  |  |  |  |

| J13        | DIVSS2   | Р   | Serial interface GND                                                  |  |  |  |  |  |

| J14        | DIVSS2   | Р   | Serial interface GND                                                  |  |  |  |  |  |

| K1         | AVDDB    | Р   | Analog power supply (channel B)                                       |  |  |  |  |  |

| K2         | AVDDB    | Р   | Analog power supply (channel B)                                       |  |  |  |  |  |

| K3         | UDACOUT2 | AO  | Universal DAC2 output                                                 |  |  |  |  |  |

| K4         | DOUT24   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| K11        | DRVDD    | Р   | Digital out power supply                                              |  |  |  |  |  |

| K12        | DRVDD    | Р   | Digital out power supply                                              |  |  |  |  |  |

| K13        | DRVSS    | Р   | Digital out GND                                                       |  |  |  |  |  |

| K14        | DRVSS    | Р   | Digital out GND                                                       |  |  |  |  |  |

| L1         | CCDGNDB  | Al  | CCD GND connection/CMOS sensor signal input (channel B)               |  |  |  |  |  |

| L2         | AVSSB    | Р   | Analog GND (channel B)                                                |  |  |  |  |  |

| L3         | DVDD     | Р   | Digital power supply                                                  |  |  |  |  |  |

| L4         | DOUT22   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| L5         | DOUT18   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| L6         | DOUT14   | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| L7         | DVDD     | Р   | Digital power supply                                                  |  |  |  |  |  |

| L8         | DOUT10   | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| L9         | DOUT6    | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| L10        | DOUT2    | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| L11        | RGB      | DO  | RG pulse output (channel B)                                           |  |  |  |  |  |

| L12        | H2B      | DO  | H2 pulse output (channel B)                                           |  |  |  |  |  |

| L13        | H1B      | DO  | H1 pulse output (channel B)                                           |  |  |  |  |  |

| L14        | LHB      | DO  | LH pulse output (channel B)                                           |  |  |  |  |  |

| M1         | CCDINB   | Al  | CCD/CMOS sensor signal input (channel B)                              |  |  |  |  |  |

| M2         | AVSSB    | P   | Analog GND (channel B)                                                |  |  |  |  |  |

| M3         | DVSS     | P   | Digital GND                                                           |  |  |  |  |  |

| M4         | DOUT20   | DO  | Data output (channel A)                                               |  |  |  |  |  |

| M5         | DOUT16   | DO  | Data output, LSB (channel A)                                          |  |  |  |  |  |

| M6         | DOUT12   | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| M7         | DVSS     | P   | Digital GND                                                           |  |  |  |  |  |

| M8         | DOUT8    | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

| M9         | DOUT4    | DO  | Data output (channel B/MUX)                                           |  |  |  |  |  |

|            | DOUT0    | DO  | Data output (channel B/MUX)  Data output, LSB (channel B/MUX)         |  |  |  |  |  |

| M10<br>M11 | DOUTO    | P   | Data output, LSB (channel B/MUX)  Digital GND                         |  |  |  |  |  |

|            |          |     |                                                                       |  |  |  |  |  |

| M12        | DVDD     | Р   | Digital power supply                                                  |  |  |  |  |  |

## **TERMINAL FUNCTIONS (continued)**

| TER  | TERMINAL   |     |                                                                        |

|------|------------|-----|------------------------------------------------------------------------|

| NAME | NO.        | I/O | DESCRIPTION                                                            |

| M13  | DVSS       | Р   | Digital GND                                                            |

| M14  | DVDD       | Р   | Digital power supply                                                   |

| N1   | AVDDB      | Р   | Analog power supply (channel B)                                        |

| N2   | AVSSB      | Р   | Analog GND (channel B)                                                 |

| N3   | BYPCMB     | AO  | Analog positive reference connected to a 0.1-µF capacitor (channel B)  |

| N4   | REFVSSB    | Р   | Reference block GND (channel B)                                        |

| N5   | REFVDDB    | Р   | Reference block power supply (channel B)                               |

| N6   | GNDG       | Р   | SUB GND                                                                |

| N7   | CVSSB      | Р   | Mask block GND (channel B)                                             |

| N8   | TEST_IN    | DI  | Test setting pin; connect to GND                                       |

| N9   | MnSHDB     | DIO | SHD monitor out/external SHD input (channel B)                         |

| N10  | HD         | DI  | HD timing pulse input; connect to DVDD when HD is not used             |

| N11  | CVSSB      | Р   | HTG block GND (channel B)                                              |

| N12  | DLLVSSB    | Р   | DLL GND (channel B)                                                    |

| N13  | DLLVDDB    | Р   | DLL power supply (channel B)                                           |

| N14  | DLLVDDB    | Р   | DLL power supply (channel B)                                           |

| P1   | AVSSB      | Р   | Analog GND (channel B)                                                 |

| P2   | COBB       | AO  | OB loop output voltage connected to a 0.1 μF-capacitor (channel B)     |

| P3   | Test_ref   | AO  | Test setting pin (Hi-Z)                                                |

| P4   | CMB        | AO  | Analog common dc reference connected to a 0.1-µF capacitor (channel A) |

| P5   | REFNB      | AO  | ADC negative reference connected to a 0.1-μF capacitor (channel B)     |

| P6   | REFPB      | AO  | ADC positive reference connected to a 0.1-μF capacitor (channel B)     |

| P7   | CVDDB      | Р   | Mask block power supply                                                |

| P8   | LogicCKBD  | DO  | Logic clock output (channel B) for digital chip and total output       |

| P9   | MnSHPB     | DIO | SHP monitor out/external SHP input (channel B)                         |

| P10  | MnLogicCKB | DIO | External logicCK input (channel B)                                     |

| P11  | CVDDB      | Р   | HTG block power supply (channel B)                                     |

| P12  | BYPDB      | AO  | DLL bypass connected to DLLVDD 1000-pF capacitor (channel B)           |

| P13  | DLLVSSB    | Р   | DLL GND (channel B)                                                    |

| P14  | MCLKB      | DI  | Masker clock input (channel B)                                         |

SBES012-OCTOBER 2008

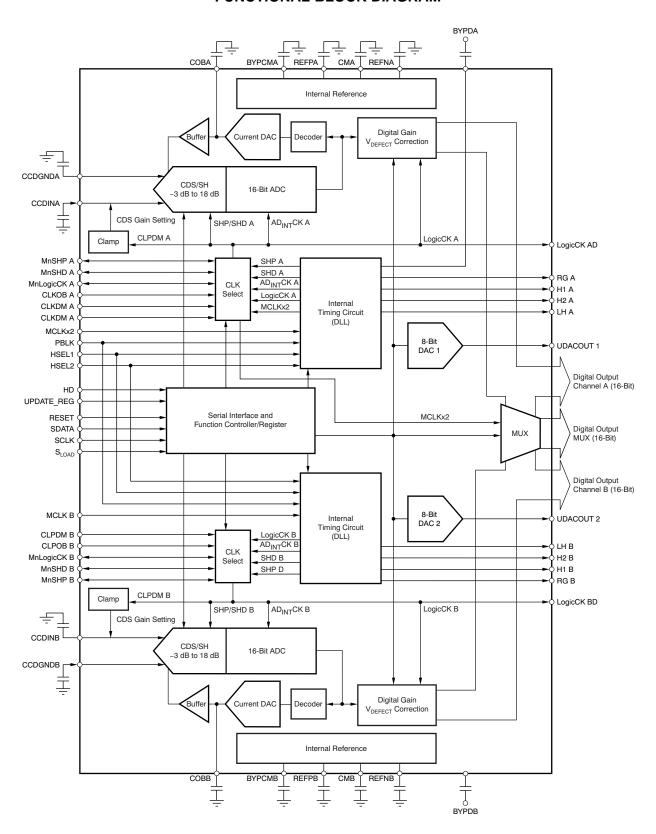

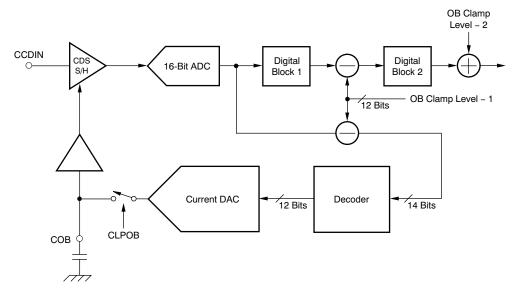

### **FUNCTIONAL BLOCK DIAGRAM**

#### SYSTEM DESCRIPTION

#### **OVERVIEW**

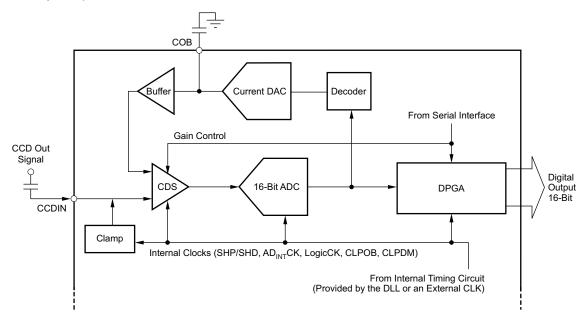

The VSP2590 is a dual-channel analog front-end device for processing imager output signals. A simplified block diagram is shown in Figure 12. The VSP2590 includes a sample/hold mode (S/H), programmable gain amplifier (PGA), analog-to-digital converter (ADC), input clamp, optical black (OB) level clamp loop, serial interface, timing control, and reference voltage generator. The device also provides a correlated double sampler (CDS) input mode. This CDS input mode consists of reconfiguration from the S/H circuit. The input mode is selected through the serial interface. Both the S/H and CDS modes provide analog gain for the input circuit.

All functions and parameters (such as PGA gain control, operation mode, and other settings) can be changed via the serial interface. All parameters are reset to default values when the serial interface activates a software reset.

The PGA of the VSP2590 provides both analog and digital gain. Digital PGA is a multi-gain function. This function can set different gain coefficients for each set of two pixels. The OB offset code can also set different offsets for every two pixels.

Figure 12. Simplified Block Diagram (Single Channel)

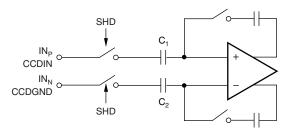

### SAMPLE-AND-HOLD (S/H) MODE

In S/H mode, the input circuit of the VSP2590 is configured as a sample-and-hold mode by the serial interface setting. Figure 13 shows a simplified input circuit of the S/H mode. In this mode, the input signal is sampled by the SHD signal.

Figure 13. S/H Input Mode Block Diagram

Submit Documentation Feedback

Copyright © 2008, Texas Instruments Incorporated

**₩營排®の**SP2590"供应商

SBES012-OCTOBER 2008

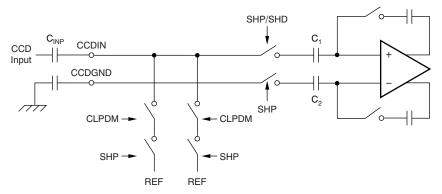

## CORRELATED DOUBLE SAMPLER (CDS) MODE

In CDS mode, the input circuit of the VSP2590 is reconfigured as correlated double sampler (CDS) by the serial interface setting. Figure 14 shows a simplified input circuit of the CDS mode.

Figure 14. CDS Input Mode Block Diagram

### **INPUT CLAMP**

In the CCD input mode, CCDIN of the VSP2590 is connected to the buffered CCD output through capacitive coupling; therefore, an input clamp is necessary. The purpose of the input clamp is to restore the dc component of the input signal that was lost during ac coupling and establish the desired dc bias point for CDS. The block diagram of Figure 14 also illustrates the input clamp. The input level is clamped to the internal reference voltage during the dummy pixel interval. More specifically, the clamping function becomes active when both CLPDM and SHP are active.

Immediately after device power on, the clamp voltage of the input capacitor is not charged. For a fast charge-up of the clamp voltage, the VSP2590 provides a boost-up circuit.

#### 16-BIT ADC

The VSP2590 also provides a high-speed, 16-bit ADC. This ADC uses a fully differential, pipelined architecture with correction. This architecture is very advantageous for realizing better linearity at a lower signal level because large linearity errors tend to occur at specific points in the full-scale range, and the linearity improves for a level of signal below that specific point. The ADC ensures 16-bit resolution for the entire full-scale range.

Copyright © 2008, Texas Instruments Incorporated

## OPTICAL BLACK (OB) LEVEL LOOP AND OB CLAMP LEVEL

The VSP2590 has a built-in optical black (OB) offset self-calibration circuit (OB loop) that compensates the OB level by using OB pixels that are output from the CCD image sensor. A block diagram of the OB loop and OB clamp circuit is shown in Figure 15. CCD offset is compensated by converging this calibration circuit while activating CLPOB during a period when OB pixels are output from the CCD.

Figure 15. OB Loop and OB Level Clamp

Because the DPGA (which is a gain stage) is outside the OB loop, OB levels are not affected even when the gain changes.

The converging time of the OB loop is determined based on the capacitor value connected to the COB terminal and the output from the current output digital-to-analog converter (DAC) of the loop. The time constant, T<sub>J</sub>, can be obtained from Equation 1:

$$T = \frac{C}{16384 \times I_{MIN}} \tag{1}$$

#### Where:

- C is the capacitor value connected to COB

- I<sub>MIN</sub> is the minimum current (0.15 μA) of the current DAC, which is the current equivalent to 1 LSB of the DAC output.

When C = 0.1  $\mu$ F, T is 40.7  $\mu$ s.

Slew rate (SR) can be obtained from Equation 2:

$$SR = \frac{I_{MAX}}{C}$$

(2)

#### Where:

- C is the capacitor value connected to COB

- I<sub>MAX</sub> is maximum current (153 μA) of the current DAC, which is the current equivalent to 1023 LSB of the DAC output.

DAC output current multiplication is provided. This function increases the DAC output current through serial interface as multiples of x2, x4, and x8. Increased DAC current shortens the time constant of the OB loop. In the case where the OB level drastically changes and must quickly settle the loop, this function is effective.

Immediately after power on, the COB capacitor voltage is not charged. For fast start-up, a COB voltage boost-up circuit is provided.

22

The OB clamp level can be set from 1536 to 3072 in 1-LSB steps, and provide a multi-OB level function that can be set to different offset values for each two-pixel pair. Table 1 lists the input code and OB clamp level.

Table 1. Input Code and OB Clamp Level

| CODE                      | 16-BIT CLAMP LEVEL (LSB) |

|---------------------------|--------------------------|

| 0110 0000 0000b           | 1536                     |

| 0110 0000 0001b           | 1537                     |

| _                         | _                        |

| 0111 1111 1110b           | 2046                     |

| 0111 1111 1111b           | 2047                     |

| 1000 0000 0000b (default) | 2048                     |

| _                         | _                        |

| 1011 1111 1111b           | 3071                     |

| 1100 0000 0000b           | 3072                     |

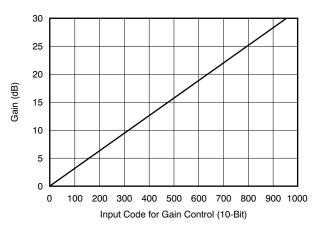

#### PROGRAMMABLE GAIN

The VSP2590 gain ranges from -3 dB to 50 dB. The desired gain is set through a combination of analog gain and the digital programmable gain amplifier (DPGA). Both gain controls through the serial interface.

Analog gain can be programmed from -3 dB to 18 dB in 3-dB steps. The -3-dB gain is provided for large input signals (such as over 1.0 V). Digital gain can be programmed from 0 dB to 32 dB in 0.032-dB steps. The digital gain changes linearly in proportion to the setting code. The relationship between the input code and digital gain is shown in Figure 16.

Figure 16. Setting Code versus Gain

### **CLOCKING AND DLL**

The VSP2590 requires the following clocks for proper operation: MCLK is the system clock, SHP is the sampling pedestal level of the sensor signal, SHD is the sampling data level of the sensor signal, AD<sub>INT</sub>CK outputs the ADC data, CLPOB is the optical black level clamp, and CLPDM is the input clamp.

The VSP2590 has built-in DLL circuits that enable the required sampling clocks (SHP, SHD, and  $AD_{INT}CK$ ) and the horizontal timing pulse of RG, H1, H2, and LH to be generated.

The PBLK timing signal (input from the pin) transmits the blanking period timing. In this period, high-speed horizontal timing pulses (RG, H1, H2, and LH) are masked and the trigger timing of H1 and H2 is transmitted as the external timing pulse of HSEL1 and HSEL2, respectively.

#### **OUTPUT MULTIPLEXING**

The VSP2590 allows selection of the output mode by the serial interface, dual channel mode, and multiplexing output mode. Output order in the multiplexing mode is selectable as channel A first or channel B first.

Copyright © 2008, Texas Instruments Incorporated

SBESQH3+QCTOBER 30Q针应商

www.ti.com

#### **VOLTAGE REFERENCE**

All reference voltages and bias currents used on the device are created from internal bandgap circuitry. The VSP2590 has a symmetrically independent voltage reference for each channel.

Both channels of the SH/CDS and the ADC use three primary reference voltages: REFP (1.5 V), REFN (1.0 V), and CM (1.275 V) of individual references. REFP and REFN are buffered on-chip. CM is derived as the midrange voltage of the resistor chain internally connecting REFP and REFN. The ADC full-scale range is determined by twice the difference voltage between REFP and REFN.

REFP, REFN, and CM should be heavily decoupled with appropriately-sized capacitors.

#### **HOT PIXEL REJECTION**

Sometimes, OB pixel output signals from the CCD include unusual level signals that are caused by pixel defection. If this level reaches a full-scale level, it may affect OB level stability. The VSP2590 has a function that rejects the unusually large pixel levels (hot pixels) in the OB pixel. This function may contribute to CCD yield improvement that is caused by OB pixel failure.

Rejection level for hot pixels is programmable through the serial interface. When hot pixels come from the CCD, the VSP2590 omits it and replaces the previous pixel level with the OB level calculation.

### **V<sub>CCD</sub> DEFECT COMPENSATION**

The VSP2590 provides a  $V_{CCD}$  defect compensation function. This function can compensate  $V_{CCD}$  defects by 32 points.

Submit Documentation Feedback

Copyright © 2008, Texas Instruments Incorporated

www.HsomSP2590"供应商

## **REGISTER DEFINITIONS**

## **Table 2. Register Definitions**

| ADDRESS | REGISTER    | BIT        | NAME         | DESCRIPTION                                  | CIRCUIT OPERATION CONDITION                                                                      | UPDATE<br>TIMING |  |  |

|---------|-------------|------------|--------------|----------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|--|--|

|         |             | 0          | STB          | STB mode                                     | 0 = Normal (circuit operates)<br>1 = STB mode<br>Default = 0                                     |                  |  |  |

|         |             | 1          | REG_RST      | Register reset                               | 0 = Normal (circuit operates)<br>1 = clear all registers<br>Default = 0                          |                  |  |  |

|         |             | 2          | DLL_STB      | DLL standby                                  | 0 = DLL operates<br>1 = DLL reset (CLK stop)<br>Default = 0                                      |                  |  |  |

|         |             | 3          | DLL_RST      | DLL reset                                    | 0 = DLL reset<br>1 = DLL operates<br>Default = 1                                                 |                  |  |  |

|         |             | 5:4        | PT           | CLPOB loop current control                   | 00b = 6.2 μA<br>01b = 12.4 μA<br>11b = 49.6 μA<br>Default = 00b                                  |                  |  |  |

|         |             | 7:6        | _            | Reserved                                     | Fixed at 0 Default = 00b                                                                         |                  |  |  |

| 0       | Config      | 8          | INPPOL       | S/H mode data level polarity                 | 0 = positive data level (S/H mode)<br>1 = Negative data level (S/H mode)<br>Default = 0          | Immediate        |  |  |

|         |             | 9          | INPMOD       | Input mode select                            | 0 = CDS mode<br>1 = S/H mode<br>Default = 0                                                      |                  |  |  |

|         |             | 10         | CLKPOL       | Sampling clock polarity change for S/H mode  | 0 = SHP/SHD negative sampling<br>1 = SHP/SHD positive sampling<br>Default = 0                    |                  |  |  |

|         |             | 11         | _            | Reserved                                     | Fixed at 0<br>Default = 0                                                                        |                  |  |  |

|         |             | 12         | ExtEn        | Clock selection (DLL or external)            | 0 = DLL CLK provided to system<br>1 = External CLK provided to system<br>Default = 0             |                  |  |  |

|         |             | 13         | MonMode      | Monitor out enable or disable                | 0 = No signal appears at the monitor pin<br>1 = Signal appears at the monitor pin<br>Default = 0 |                  |  |  |

|         |             | 15:14      | _            | Reserved                                     | Fixed at 0<br>Default = 00b                                                                      |                  |  |  |

|         |             | 2:0        | HdrvAB       | RG/H1/H2 pin drive ability select            | 000b = 3 mA                                                                                      |                  |  |  |

|         |             | 3          | _            | Reserved                                     | Default = 001b Fixed at 0                                                                        |                  |  |  |

|         |             | 3          | _            | Neserveu                                     | Default = 0<br>000b = 3 mA                                                                       |                  |  |  |

|         | 1/0 "       | 6:4        | OutEn_ana    | Output buffer drive ability (analog output)  | 001b = 2 mA 111b = Hi-Z                                                                          |                  |  |  |

| 1       | I/O config  | 7          | _            | _                                            | Default = 001b  Fixed at 0 Default = 0                                                           | Immediate        |  |  |

|         |             | 10:8 OutEr | OutEn_dig    | Output buffer drive ability (digital output) | 000b = 3 mA                                                                                      |                  |  |  |

|         |             | 15:11      | _            | Reserved                                     | Fixed at 0 Default = 00000b                                                                      |                  |  |  |

|         | 00 1 15     | 11:0       | OB level 0-A | _                                            | OB level is limited as 1536 to 3072 (LSB) Default = 1000 0000 0000b                              |                  |  |  |

| 2       | OB_level0_A | 15:12      | _            | Reserved                                     | Fixed at 0<br>Default = 0000b                                                                    | Immediate        |  |  |

| 2       | OB level0_B | 11:0       | OB level 0-B | _                                            | OB level is limited as 1536 to 3072 (LSB)<br>Default = 1000 0000 0000b                           | Immodiate        |  |  |

| 3       | Op levelo_B | 15:12      | _            | Reserved                                     | Fixed at 0 Default = 0000b                                                                       | Immediate        |  |  |

## **Table 2. Register Definitions (continued)**

| ADDRESS | REGISTER    | BIT            | NAME        | DESCRIPTION            | CIRCUIT OPERATION CONDITION                                         | UPDATE<br>TIMING |                       |             |           |

|---------|-------------|----------------|-------------|------------------------|---------------------------------------------------------------------|------------------|-----------------------|-------------|-----------|

| 4–7     | _           | _              | _           | Reserved               | Fixed at 0                                                          | Immediate        |                       |             |           |

|         | DAC1        | 7:0            | _           | Universal DAC 1 level  | Universal DAC 1 level = 256 steps<br>Default = 0000 0000b           |                  |                       |             |           |

| 8       |             | 8              | _           | Universal DAC 1 on/off | 0 = On<br>1 = Off<br>Default = 0                                    | Immediate        |                       |             |           |

|         |             | 15:9           | _           | Reserved               | Fixed at 0<br>Default = 000 0000b                                   |                  |                       |             |           |

|         |             | 7:0            | _           | Universal DAC 2 level  | Universal DAC 2 level = 256 steps<br>Default = 0000 0000b           |                  |                       |             |           |

| 9       | DAC2        | 8              | _           | Universal DAC 2 on/off | 0 = On<br>1 = Off<br>Default = 0                                    | Immediate        |                       |             |           |

|         |             | 15:9           | _           | Reserved               | Fixed at 0<br>Default = 000 0000b                                   |                  |                       |             |           |

| 10      | _           | _              | _           | Reserved               | Fixed at 0                                                          | Register update  |                       |             |           |

| 11      | Analog Gain | Analog Gain    | Analog Gain | Analog Gain            | 2:0                                                                 | Gain             | Analog gain selection | 000b = 0 dB | Immediate |

|         |             |                |             |                        |                                                                     |                  | Default = 000b        | minediate   |           |

|         |             | 15:3           | _           | Reserved               | Fixed at 0 Default = 0 0000 0000 0000b                              |                  |                       |             |           |

|         |             | 1:0            | OBFIL       | _                      | 00 = No filter<br>01 = 1st-order<br>10 = 2nd-order<br>Default = 00b |                  |                       |             |           |

|         |             | 2              | _           | Reserved               | Fixed at 0<br>Default = 0                                           |                  |                       |             |           |

|         |             | 3              | Shrink_OB   | _                      | 0 = Shrink OB period<br>1 = OB period not shrunk<br>Default = 0     |                  |                       |             |           |

| 12      | OB_loop     | 7:4            | _           | Reserved               | Fixed at 0<br>Default = 0000b                                       | Immediate        |                       |             |           |

|         |             | 12:8           | HPIX level  | _                      | Rejection level (LSB) = (hpix level + 1) x 128<br>Default = 11111b  |                  |                       |             |           |

|         |             | 13 HPIX enable |             | _                      | 0 = Disabled<br>1 = Enable hot pixel rejection<br>Default = 0       |                  |                       |             |           |

|         |             | 15:14          | _           | Reserved               | Fixed at 0<br>Default = 00b                                         |                  |                       |             |           |

<u>₩豐梅♥\\$P2590"供应商</u>

SBES012-OCTOBER 2008

## **Table 2. Register Definitions (continued)**

| ADDRESS | REGISTER          | BIT   | NAME              | DESCRIPTION                        | CIRCUIT OPERATION CONDITION                                                                                                                                                           | UPDATE<br>TIMING                                                                                                                                                                    |                                                                                                                                                                                                                                                             |                                                                         |  |

|---------|-------------------|-------|-------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

|         |                   | 1:0   | SKIP_MODE         | Skip SHP/SHD/RG                    | 0 = No skips<br>1 = 2 skips<br>2 = 4 skips<br>Default = 00b                                                                                                                           |                                                                                                                                                                                     |                                                                                                                                                                                                                                                             |                                                                         |  |