www.ti.com

# 20-W STEREO DIGITAL AUDIO POWER AMPLIFIER

Check for Samples: TAS5701

## **FEATURES**

- Audio Input/Output

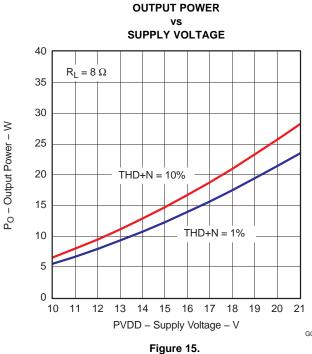

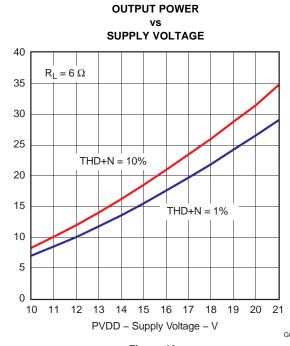

- 20-W Into an 8-Ω Load From an 18-V Supply

- Wide PVDD Range (0 V to 21 V)

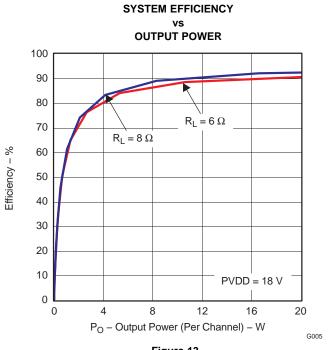

- Efficient Class-D Operation Eliminates

Need for Heat Sinks

- Two Serial Audio Inputs (3 Audio channels)

- Supports 32-kHz to 192-kHz Sample Rates (LJ/RJ/I<sup>2</sup>S)

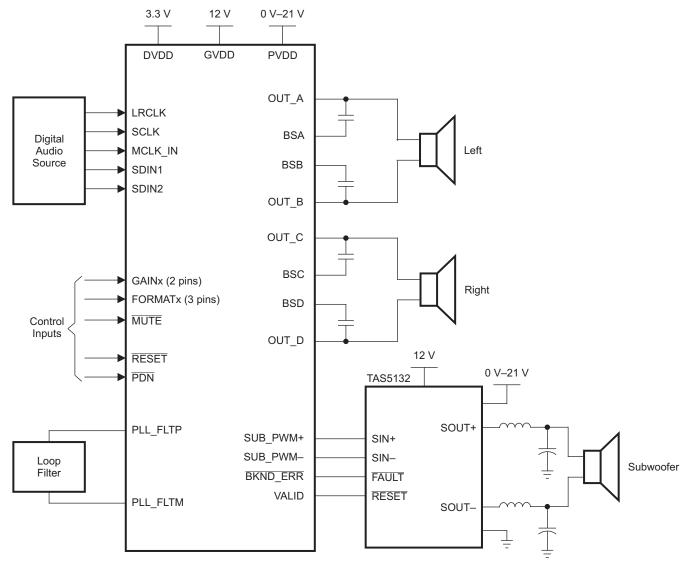

- Line-Level Subwoofer PWM Outputs

- Audio/PWM Processing

- BD (Filter-free) Modulation Supporting Bridge-Tied Loads ONLY

- 4-Step Volume Control (0 dB, 6 dB, 12 dB, 18 dB)

- All Channels Share Same Control

- Soft Mute (50% Duty Cycle)

- DC Blocking Filters

- Fixed Maximum Modulation Limit At 97.7%

- 2100-dB SNR Measured at Maximum

Output With THD+N = 1%, 1 kHz,

A-Weighted Noise, Gain = 0 dB

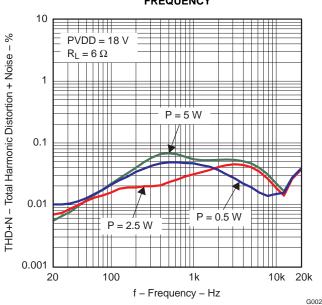

- THD < 0.1% at 1/2 Rated Power

### General Features

- 5-V Tolerant Inputs (See pin list for details on which inputs are 5-V tolerant)

- Shutdown Mode for Low Power Consumption

- Thermal and Short-Circuit Protection

- Autodetect: Automatically Detect Sample-Rate Changes – No Need for External Microprocessor Intervention

# **DESCRIPTION**

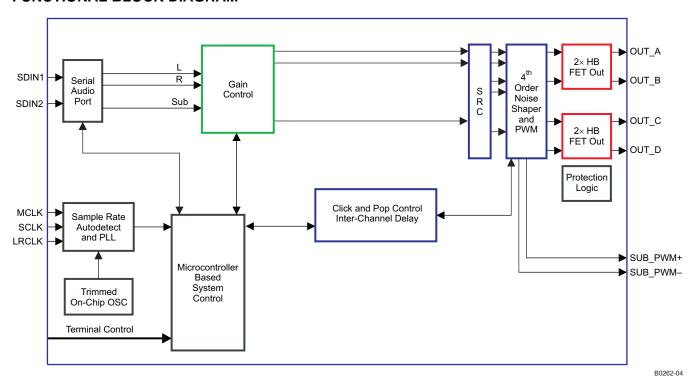

The TAS5701 is a 20-W efficient, digital audio power amplifier for driving stereo bridge-tied speakers. Two serial data inputs support up to 3 discrete audio channels. The SDIN1 input is routed to the internal left and right outputs. The SDIN2 input is dedicated to the SUB\_PWM± outputs.

The TAS5701 is a clock slave-only device receiving clocks from external sources. The TAS5701 operates at a 384-kHz switching rate for 32-, 48-, 96-, and 192-kHz data and 352.8-kHz switching rate 44.1-,88.2-, and 176.4-kHz data. The 8x oversampling combined with the fourth-order noise shaper provides a flat noise floor and excellent dynamic range from 20 Hz to 20 kHz.

lf.dzsc.com

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# SIMPLIFIED APPLICATION DIAGRAM

B0264-08

<u>www.描som</u>AS5701"供应商

# **FUNCTIONAL BLOCK DIAGRAM**

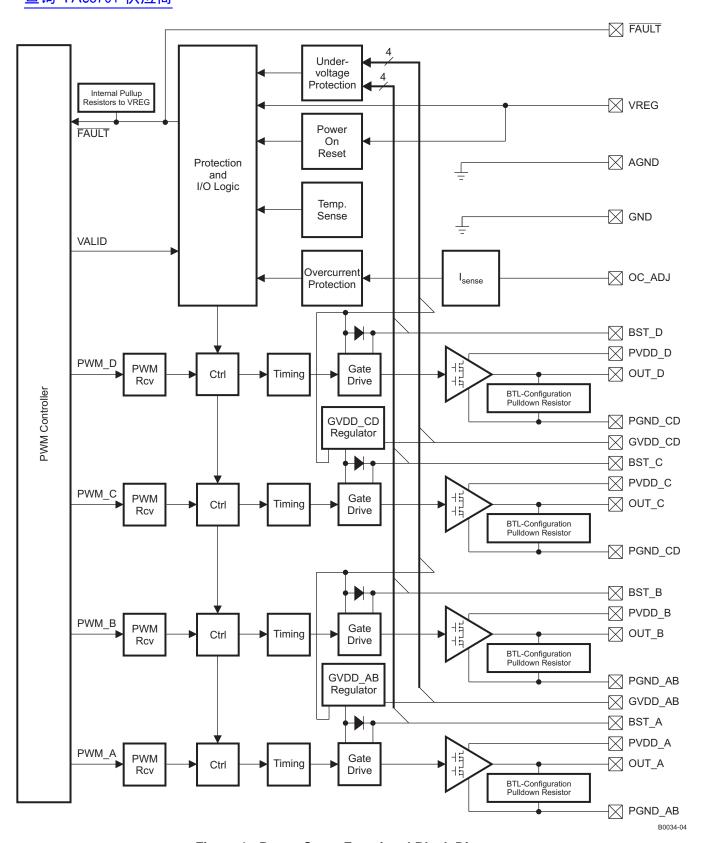

Figure 1. Power Stage Functional Block Diagram

# 64-PIN, HTQFP PACKAGE (TOP VIEW)

### **PAP Package** (Top View) Δ. PVDD PVDD BST BST 55 56 OUT A \_\_\_ 48 ☐ OUT D PVDD A 2 47 PVDD D PVDD A 3 46 PVDD D BST\_A [ 4 45 BST\_D GVDD\_CD GVDD\_AB [ 5 44 VDD □ 6 43 **VREG** 7 TEST1 □ 42 **GND** OC ADJ \_\_\_ 8 41 **GND** SUB\_PWM+ 9 FAULT 40 AVDD [ 39 SUB\_PWM-10 **VALID** AVSS □ 11 38 PLL FLTM [ 37 **BKND ERR** 12 PLL\_FLTP [ 13 36 **MCLK** VR ANA □ 14 35 □ DVDD DVDD $\square$ 15 34 ☐ CONFIG\_1 RESET \_\_\_\_ 16 33 CONFIG 2 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 VR\_DIG [ VREG\_EN | OSC\_RES | SDIN2 SDIN1 DVSSO MUTE LRCLK SCLK DVSS -ORMAT0 GAIN 0 **-ORMAT2** GAIN\_1

# P0071-03

### **PIN FUNCTIONS**

| PIN      |     | I/O <sup>(1)</sup> | 5-V      | TERMINATION | DESCRIPTION                                                                                                                                                                               |  |

|----------|-----|--------------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | 1/0(1)             | TOLERANT | (2) (3)     | DESCRIPTION                                                                                                                                                                               |  |

| AVDD     | 10  | Р                  |          |             | 3.3-V Analog power supply                                                                                                                                                                 |  |

| AVSS     | 11  | Р                  |          |             | Analog 3.3-V supply ground                                                                                                                                                                |  |

| BKND_ERR | 37  | DI                 |          | Pullup      | Active low. A back-end error sequence is initiated by applying a logic low to this pin. Connect to an external power stage. If no external power stage is used, connect directly to DVDD. |  |

| BST_A    | 4   | Р                  |          |             | High-side bootstrap supply for half-bridge A                                                                                                                                              |  |

| BST_B    | 57  | Р                  |          |             | High-side bootstrap supply for half-bridge B                                                                                                                                              |  |

| BST_C    | 56  | Р                  |          |             | High-side bootstrap supply for half-bridge C                                                                                                                                              |  |

TYPE: A = analog; D = 3.3-V digital; P = power/ground/decoupling; I = input; O = output

Product Folder Link(s): TAS5701

All pullups are 20-µA weak pullups and all pulldowns are 20-µA weak pulldowns. The pullups and pulldowns are included to assure proper input logic levels if the terminals are left unconnected (pullups  $\rightarrow$  logic 1 input; pulldowns  $\rightarrow$  logic 0 input). Devices that drive inputs with pullups must be able to sink 50 µA while maintaining a logic-0 drive level. Devices that drive inputs with pulldowns must be able to source 50 µA while maintaining a logic-1 drive level.

If desired, low-ESR capacitance values can be implemented by paralleling two or more ceramic capacitors of equal value. Paralleling capacitors of equal value provides an extended high-frequency supply decoupling. This approach avoids the potential of producing parallel resonance circuits that have been observed when paralleling capacitors of different values.

# **PIN FUNCTIONS (continued)**

| PIN      |        | (4)                | 5-V      | TERMINATION | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------|--------------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.    | I/O <sup>(1)</sup> | TOLERANT | (2) (3)     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BST_D    | 45     | Р                  |          |             | High-side bootstrap supply for half-bridge D                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CONFIG_2 | 33     | Р                  |          | Pulldown    | Input/output configuration. Connect this terminal directly to GND.                                                                                                                                                                                                                                                                                                                                                                                           |

| CONFIG_1 | 34     | Р                  |          | Pulldown    | Input/output configuration. Connect this terminal directly to DVDD.                                                                                                                                                                                                                                                                                                                                                                                          |

| DVDD     | 15, 35 | Р                  |          |             | 3.3-V Digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DVSS     | 26     | Р                  |          |             | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DVSSO    | 20     | Р                  |          |             | Oscillator ground                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FAULT    | 9      | DO                 |          |             | Overtemperature, undervoltage, and overcurrent fault reporting. Active low indicates fault. If high, normal operation.                                                                                                                                                                                                                                                                                                                                       |

| FORMAT2  | 30     | DI                 |          | Pulldown    | Digital data format select MSB.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FORMAT1  | 31     | DI                 |          | Pulldown    | Digital data format select LSB.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FORMAT0  | 32     | DI                 |          | Pulldown    | Digital data format select.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GAIN_1   | 28     | DI                 | 5-V      |             | MSB of gain select.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GAIN_0   | 29     | DI                 | 5-V      |             | LSB of gain select. GAIN_0 and GAIN_1 allow 4 possible gain selections.                                                                                                                                                                                                                                                                                                                                                                                      |

| GND      | 41, 42 | Р                  |          |             | Analog ground for power stage.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GVDD_AB  | 5      | Р                  |          |             | Gate drive voltage for half-bridges A and B (10.8 V to 13.2 V)                                                                                                                                                                                                                                                                                                                                                                                               |

| GVDD_CD  | 44     | Р                  |          |             | Gate drive voltage for half-bridges C and D (10.8 V to 13.2 V)                                                                                                                                                                                                                                                                                                                                                                                               |

| LRCLK    | 22     | DI                 | 5-V      |             | Input serial audio data left/right clock (sampling rate clock)                                                                                                                                                                                                                                                                                                                                                                                               |

| MCLK     | 36     | DI                 | 5-V      |             | Clock master input. The input frequency of this clock can range from 4.9 MHz to 49 MHz.                                                                                                                                                                                                                                                                                                                                                                      |

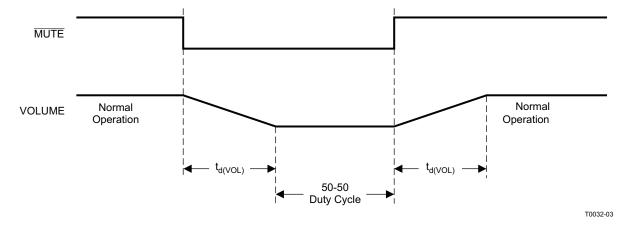

| MUTE     | 21     | DI                 | 5-V      | Pullup      | Performs a soft mute of outputs, active-low. A logic low on this pin sets the outputs equal to 50% duty cycle. A logic high on this pin allows normal operation. The mute control provides a noiseless volume ramp to silence. Releasing mute provides a noiseless ramp to previous volume.                                                                                                                                                                  |

| OC_ADJ   | 8      | AO                 |          |             | Analog overcurrent programming. Requires 22-k $\Omega$ resistor to ground.                                                                                                                                                                                                                                                                                                                                                                                   |

| OSC_RES  | 19     | AO                 |          |             | Oscillator trim resistor. Connect an 18.2-k $\Omega$ (1% tolerance is required) resistor to DVSSO.                                                                                                                                                                                                                                                                                                                                                           |

| OUT_A    | 1, 64  | 0                  |          |             | Output, half-bridge A                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT_B    | 60, 61 | 0                  |          |             | Output, half-bridge B                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT_C    | 52, 53 | 0                  |          |             | Output, half-bridge C                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT_D    | 48, 49 | 0                  |          |             | Output, half-bridge D                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PDN      | 17     | DI                 | 5-V      | Pullup      | Power down, active-low. PDN stops all clocks, and outputs stop switching whenever a logic low is applied. When PDN is released, the device powers up all logic, starts all clocks, and performs a soft start that returns to the previous configuration changes to FORMATx and GAINx pins are ignored on PDN cycling.                                                                                                                                        |

| PGND_AB  | 62, 63 | Р                  |          |             | Power ground for half-bridges A and B                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PGND_CD  | 50, 51 | Р                  |          |             | Power ground for half-bridges C and D                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PLL_FLTM | 12     | AO                 |          |             | PLL negative loop filter terminal                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PLL_FLTP | 13     | Al                 |          |             | PLL positive loop filter terminal                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PVDD_A   | 2, 3   | Р                  |          |             | Power supply input for half-bridge output A (0 V–21 V)                                                                                                                                                                                                                                                                                                                                                                                                       |

| PVDD_B   | 58, 59 | Р                  |          |             | Power supply input for half-bridge output B (0 V–21 V)                                                                                                                                                                                                                                                                                                                                                                                                       |

| PVDD_C   | 54, 55 | Р                  |          |             | Power supply input for half-bridge output C (0 V–21 V)                                                                                                                                                                                                                                                                                                                                                                                                       |

| PVDD_D   | 46, 47 | Р                  |          |             | Power supply input for half-bridge output D(0 V–21 V)                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET    | 16     | DI                 | 5-V      | Pullup      | Reset, active-low. A system reset is generated by applying a logic low to this terminal. RESET is an asynchronous control signal that sets the VALID outputs low, and places the PWM in the hard mute state (stop switching). Gain is immediately set to full attenuation. Upon the release of RESET, if PDN is high, the system performs a 4-ms to 5-ms device initialization and sets the gain and format to the settings determined by the hardware pins. |

SLOS559A - JUNE 2008 - REVISED AUGUST 2010

**≝街<sup>™</sup>AS5701"供应商**

# **PIN FUNCTIONS (continued)**

| PIN      |     | (1)                | 5-V      | TERMINATION |                                                                                                                                                                             |  |  |

|----------|-----|--------------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. | I/O <sup>(1)</sup> | TOLERANT | (2) (3)     | DESCRIPTION                                                                                                                                                                 |  |  |

| SCLK     | 23  | DI                 | 5-V      |             | Serial audio data clock (shift clock). SCLK is the serial audio port input data bit clock.                                                                                  |  |  |

| SDIN1    | 25  | DI                 | 5-V      |             | Serial audio data 1 input is one of the serial data input ports. SDIN1 supports three discrete (stereo) data formats.                                                       |  |  |

| SDIN2    | 24  | DI                 | 5-V      |             | Serial audio data 2 input is one of the serial data input ports. SDIN2 supports three discrete (stereo) data formats.                                                       |  |  |

| SUB_PWM- | 39  | DO                 |          |             | Subwoofer negative PWM output. BD modulated signal.                                                                                                                         |  |  |

| SUB_PWM+ | 40  | DO                 |          |             | Subwoofer positive PWM output. BD modulated signal.                                                                                                                         |  |  |

| TEST1    | 7   | DI                 |          |             | Test pin. Connect directly to GND.                                                                                                                                          |  |  |

| VALID    | 38  | DO                 |          |             | Output indicating validity of ALL PWM channels, active-high. This pin is connected to an external power stage. If no external power stage is used, leave this pin floating. |  |  |

| VDD      | 6   | Р                  |          |             | Power supply for VREG (10.8 V to 13.2 V)                                                                                                                                    |  |  |

| VR_ANA   | 14  | Р                  |          |             | Internally regulated 1.8-V analog supply voltage. This terminal must not be used to power external devices.                                                                 |  |  |

| VR_DIG   | 27  | Р                  |          |             | Internally regulated 1.8-V analog supply voltage. This terminal must not be used to power external devices.                                                                 |  |  |

| VREG     | 43  | Р                  |          |             | Digital regulator output. Not to be used for powering external circuitry.                                                                                                   |  |  |

| VREG_EN  | 18  | DI                 |          | Pulldown    | Voltage regulator enable. Connect directly to GND.                                                                                                                          |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                                         |                                                                     | VALUE                                                                  | UNIT |

|-----------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------|------|

|                                         | GVDD, VDD                                                           | -0.3 to 13.2                                                           |      |

|                                         | PVDD                                                                | -0.3 to 23                                                             |      |

| Output clamp curr<br>Operating free-air | DVDD                                                                | -0.3 to 3.6                                                            | V    |

|                                         | AVDD                                                                | -0.3 to 3.6                                                            | V    |

|                                         | OUT_X to GND_X                                                      | -0.3 to 30                                                             |      |

|                                         | BST_X to GND_X                                                      | -0.3 to 43.2                                                           |      |

| Input voltage                           | 3.3-V digital input                                                 | -0.5 to DVDD + 0.5                                                     | V    |

| input voitage                           | 5-V tolerant <sup>(2)</sup> digital input                           | -0.3 to 23<br>-0.3 to 3.6<br>-0.3 to 3.6<br>-0.3 to 30<br>-0.3 to 43.2 | V    |

| Input clamp curre                       | ent, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> > 1.8 V) | ±20                                                                    | mA   |

| Output clamp cu                         | rrent, $I_{OK}$ ( $V_O < 0$ or $V_O > 1.8 \text{ V}$ )              | ±20                                                                    | mA   |

| Operating free-ai                       | ir temperature                                                      | 0 to 85                                                                | °C   |

| Operating junction                      | on temperature range                                                | 0 to 150                                                               | °C   |

| Storage tempera                         | ture range, T <sub>stg</sub>                                        | -40 to 125                                                             | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operation conditions are not implied. Exposure to absolute-maximum conditions for extended periods may affect device reliability. (2) 5-V tolerant inputs are PDN, RESET, MUTE, SCLK, LRCLK, MCLK, SDIN1, SDIN2.

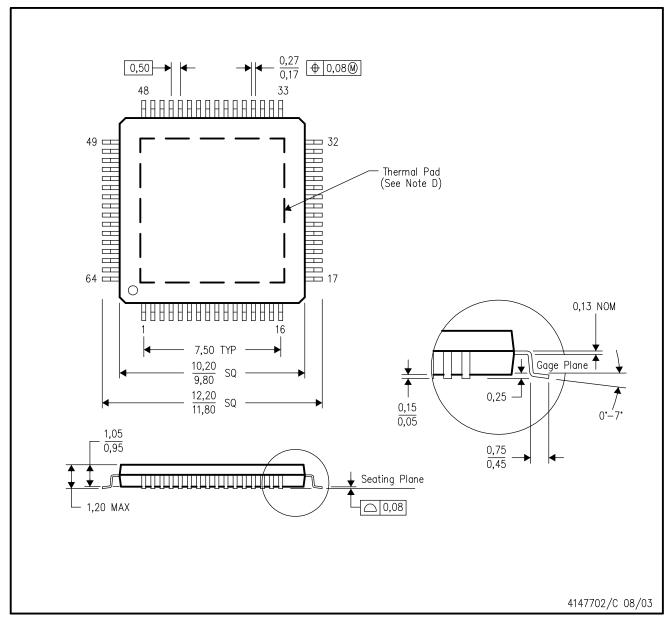

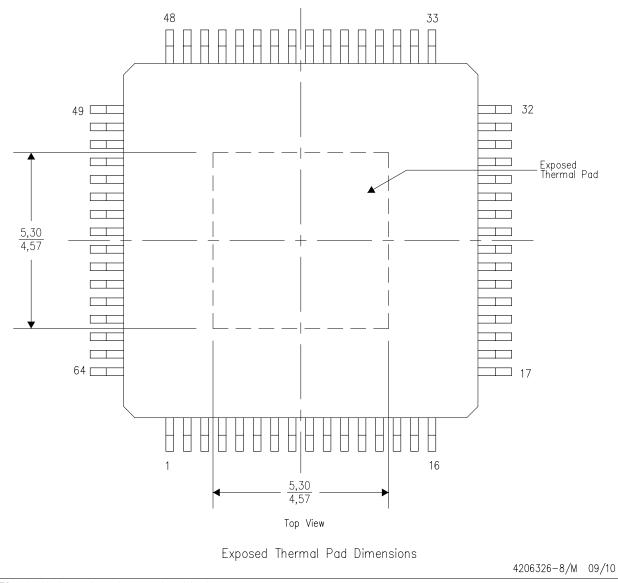

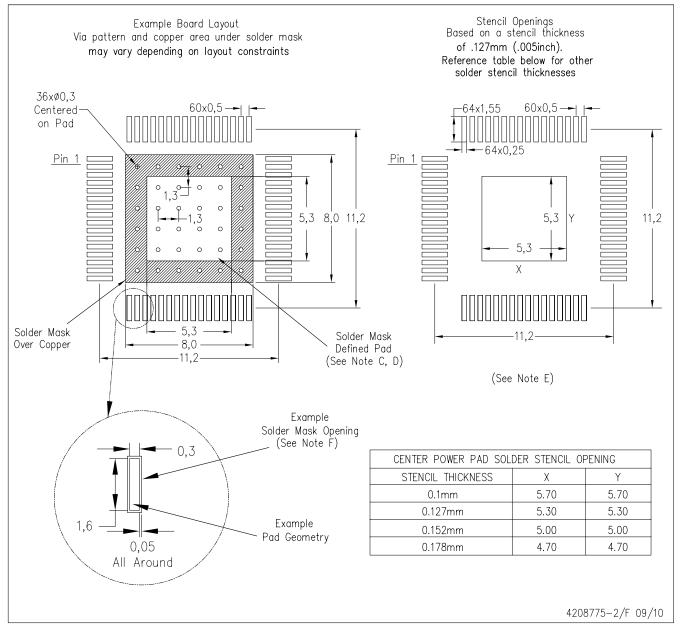

# THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)(2)</sup>             | TAS5701       | LIMITO |

|-------------------------|----------------------------------------------|---------------|--------|

|                         | THERMAL METRIC                               | PAP (64 PINS) | UNITS  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 27.2          |        |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 16            |        |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 13            | °C/W   |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.1           | *C/vv  |

| ΨЈВ                     | Junction-to-board characterization parameter | 7.9           |        |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 0.9           |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                       | <u> </u>                             | ·                                                       | MIN  | NOM | MAX  | UNIT |

|-----------------------|--------------------------------------|---------------------------------------------------------|------|-----|------|------|

|                       | Gate drive supply voltage            | GVDD, VDD                                               | 10.8 | 12  | 13.2 | V    |

|                       | Output bridge supply voltage         | PVDD                                                    | 0    |     | 21   | V    |

|                       | Digita supply voltage                | DVDD                                                    | 3    | 3.3 | 3.6  | V    |

|                       | Analog supply voltage                | AVDD                                                    | 3    | 3.3 | 3.6  | V    |

| V <sub>IH</sub>       | High-level input voltage             | 3.3-V TTL, 5-V tolerant                                 | 2    |     |      | V    |

| V <sub>IL</sub>       | Low-level input voltage              | 3.3-V TTL, 5-V tolerant                                 |      |     | 0.8  | V    |

| T <sub>A</sub>        | Operating ambient temperature range  |                                                         | 0    |     | 85   | °C   |

| TJ                    | Operating junction temperature range |                                                         | 0    |     | 150  | °C   |

| R <sub>L</sub> (BTL)  |                                      |                                                         | 6.0  | 8   |      |      |

| R <sub>L</sub> (SE)   | Load impedance                       | Output filter: L = 22 $\mu$ H, C = 680 nF.              | 3.2  | 4   |      | Ω    |

| R <sub>L</sub> (PBTL) |                                      |                                                         | 3.2  | 4   |      |      |

| L <sub>O</sub> (BTL)  |                                      |                                                         |      | 10  |      |      |

| L <sub>O</sub> (SE)   | Output-filter inductance             | Minimum output inductance under short-circuit condition |      | 10  |      | μΗ   |

| L <sub>O</sub> (PBTL) |                                      | Short should somalion                                   |      | 10  |      |      |

# **PWM OPERATION AT RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                            | TEST CONDITIONS                       | MODE                        | VALUE | UNIT |

|--------------------------------------|---------------------------------------|-----------------------------|-------|------|

|                                      | 32-kHz data rate ±2%                  | 12x sample rate             | 384   | kHz  |

| Output sample rate 2x–1x oversampled | 44.1-, 88.2-, 176.4-kHz data rate ±2% | 8x, 4x, and 2x sample rates | 352.8 | kHz  |

| Oversamplea                          | 48-, 96-, 192-kHz data rate ±2%       | 8x, 4x, and 2x sample rates | 384   | kHz  |

# PLL INPUT PARAMETERS AND EXTERNAL FILTER COMPONENTS

|                    | PARAMETER                                | TEST CONDITIONS                                                         | MIN | TYP | MAX  | UNIT  |

|--------------------|------------------------------------------|-------------------------------------------------------------------------|-----|-----|------|-------|

| f <sub>MCLKI</sub> | Frequency, MCLK (1 / t <sub>cyc2</sub> ) |                                                                         | 4.9 |     | 49.2 | MHz   |

|                    | MCLK duty cycle                          |                                                                         | 40% | 50% | 60%  |       |

|                    | MCLK minimum high time                   | ≥2-V MCLK = 49.152 MHz, within the min and max duty cycle constraints   | 8   |     |      | ns    |

|                    | MCLK minimum low time                    | ≤0.8-V MCLK = 49.152 MHz, within the min and max duty cycle constraints | 8   |     |      | ns    |

|                    | LRCLK allowable drift before LRCLK reset |                                                                         |     |     | 4    | MCLKs |

|                    | External PLL filter capacitor C1         | SMD 0603 Y5V                                                            |     | 47  |      | nF    |

|                    | External PLL filter capacitor C2         | SMD 0603 Y5V                                                            |     | 4.7 |      | nF    |

|                    | External PLL filter resistor R           | SMD 0603, metal film                                                    |     | 470 |      | Ω     |

Product Folder Link(s): TAS5701

<sup>(2)</sup> For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator.

**₩營物門**AS5701"供应商

# **ELECTRICAL CHARACTERISTICS**

# **DC Characteristics**

|                            | PARAMETE                                                     | $VDD = 3.3 \text{ V}, \text{ R}_{L} = 8 \Omega \text{ (unless)}$ <b>R</b>                                                           | TEST CONDITIONS                      | MIN | TYP  | MAX | UNIT   |

|----------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|------|-----|--------|

| V <sub>OH</sub>            | High-level output voltage                                    | 3.3-V TTL and 5-V tolerant (1)                                                                                                      | $I_{OH} = -4 \text{ mA}$             | 2.4 |      |     | ٧      |

| V <sub>OL</sub>            | Low-level output voltage                                     | 3.3-V TTL and 5-V tolerant (1)                                                                                                      | I <sub>OL</sub> = 4 mA               |     |      | 0.5 | ٧      |

| I <sub>IL</sub>            | Low-level input current                                      | LRCLK, <u>SCLK, SDIN</u> x, MCLK,<br>GAIN_x, <del>VREG_EN,</del><br>FORMATx, CONFIG_x                                               | V <sub>I</sub> = 0 V, DVDD = 3.6 V   |     |      | ±2  | μА     |

|                            | ·                                                            | BKND_ERR, RESET, PDN, MUTE                                                                                                          | V <sub>I</sub> = 0 V, DVDD = 3.6 V   |     |      | ±50 | ·<br>L |

|                            |                                                              | $\overline{\text{RESET}}, \overline{\text{PDN}}, \overline{\text{MUTE}}, \overline{\text{GAIN\_x}}, \\ \overline{\text{BKND\_ERR}}$ | V <sub>I</sub> = 3.6 V, DVDD = 3.6 V |     |      | ±2  | l      |

| I <sub>IH</sub>            | High-level input current                                     | VREG_EN, FORMAT_x,<br>CONFIG_x, LRCLK, SCLK,<br>SDINx, MCLK                                                                         | V <sub>I</sub> = 3.6 V, DVDD = 3.6 V |     |      | ±50 | μА     |

|                            |                                                              | RESET, PDN, MUTE, LRCLK, SCLK, SDINx, MCLK, GAIN_x                                                                                  | V <sub>I</sub> = 5.5 V, DVDD = 3.6 V |     |      | ±50 | l      |

|                            |                                                              |                                                                                                                                     | Normal mode, 50% duty cycle          |     | 65   | 80  | ı,     |

| $I_{DD}$                   | Input digital supply current                                 | Supply voltage (DVDD, AVDD)                                                                                                         | Power down (PDN = low)               |     | 8    | 16  | mA     |

|                            |                                                              |                                                                                                                                     | Reset (RESET = low)                  |     | 23   | 33  |        |

|                            |                                                              |                                                                                                                                     | Normal mode, 50% duty cycle          |     | 5    | 10  | l.     |

| $I_{\text{GVDD}}$          | Gate supply current per GVDD_xx input                        |                                                                                                                                     | RESET = 0                            |     | 2.2  | 4   | mA     |

|                            | OVBB_XX IIIput                                               |                                                                                                                                     | PDN = 0                              |     | 2.2  | 4   |        |

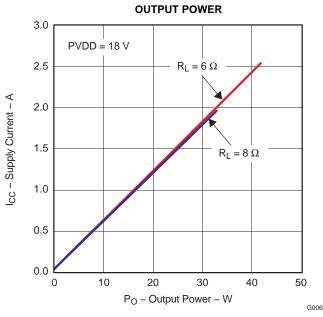

| I <sub>PVDD</sub>          | Input power supply current                                   |                                                                                                                                     | No load                              |     | 30   | 60  | mA     |

| $I_{PVDD}(\overline{PDN})$ | Power-down current                                           |                                                                                                                                     | No load, $\overline{PDN} = 0$        |     | 1    | 100 | μΑ     |

| I <sub>PVDD</sub> (RESET)  | Reset current                                                |                                                                                                                                     | No load, RESET = 0                   |     | 1    | 100 | μА     |

| _                          | Drain-to-source resistance, LS                               | T <sub>J</sub> = 25°C, includes metallization resistance                                                                            |                                      |     | 140  |     | 0      |

| r <sub>DS(on)</sub>        | Drain-to-source resistance, HS                               | T <sub>J</sub> = 25°C, includes metallization resistance                                                                            |                                      | 140 |      |     | mΩ     |

| I/O Protection             |                                                              |                                                                                                                                     |                                      | •   |      |     |        |

| $V_{uvp}$                  | Undervoltage protection limit                                | PVDD falling                                                                                                                        |                                      |     | 9.2  |     | V      |

| V <sub>uvp,hyst</sub>      | Undervoltage protection limit                                | PVDD rising                                                                                                                         |                                      |     | 9.6  |     | V      |

| OTE (2)                    | Overtemperature error                                        |                                                                                                                                     |                                      |     | 150  |     | °C     |

| OTE <sub>HYST</sub> (2)    | Extra temperature drop required to recover from error        |                                                                                                                                     |                                      |     | 30   |     | °C     |

| OLPC                       | Overload protection counter                                  | f <sub>PWM</sub> = 384 kHz                                                                                                          |                                      |     | 1.25 |     | ms     |

| loc                        | Overcurrent limit protection                                 | $R_{OCP} = 22 \text{ k}\Omega$                                                                                                      |                                      |     | 4.5  |     | Α      |

| Гост                       | Overcurrent response time                                    |                                                                                                                                     |                                      |     | 150  |     | ns     |

| R <sub>OCP</sub>           | OC programming resistor range                                | Resistor tolerance = 5% for typical value; the minimum resistance should not be less than 20 $k\Omega$ .                            |                                      | 20  | 22   |     | kΩ     |

| R <sub>PD</sub>            | Internal pulldown resistor at the output of each half-bridge | Connected when RESET is active to provide bootstrap capacitor charge.                                                               |                                      |     | 3    |     | kΩ     |

<sup>(1) 5-</sup>V tolerant inputs are PDN, RESET, MUTE, SCLK, LRCLK, MCLK, SDIN1, SDIN2, GAIN\_0, and GAIN\_1.

Specified by design.

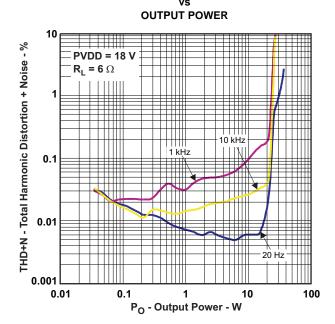

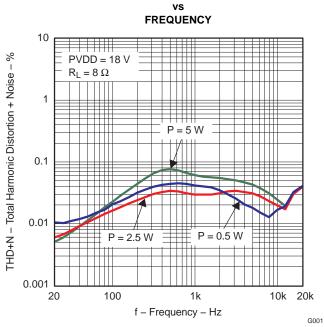

# **AC Characteristics (BTL)**

PVDD\_X = 18 V, BTL mode,  $R_L = 8 \Omega$ ,  $R_{OC} = 22 k\Omega$ ,  $C_{BST} = 33$ -nF, audio frequency = 1 kHz, AES17 filter,  $F_{PWM} = 384$  kHz,  $T_A = 25$ °C (unless otherwise noted). All performance is I naccordance with recommended operating conditions, unless otherwise specified.

|                | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TEST CONDITIONS                                           | MIN TYP | MAX | UNIT |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------|-----|------|

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PVDD = 18 V, 10% THD, 1-kHz input signal                  | 20.0    |     |      |

| Б              | Device systems are showned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PVDD = 18 V, 7% THD, 1-kHz input signal                   | 18.6    |     | 14/  |

| P <sub>0</sub> | Power output per channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PVDD = 12 V, 10% THD, 1-kHz input signal                  |         |     | W    |

|                | Signal   PVDD = 18 V, 7% THD, 1-kHz input signal   PVDD = 12 V, 10% THD, 1-kHz input signal   PVDD = 12 V, 7% THD, 1-kHz input signal   PVDD = 12 V, 7% THD, 1-kHz input signal   PVDD = 18 V, P <sub>O</sub> = 10 W (half-power)   0.1%   PVDD = 12 V, P <sub>O</sub> = 4.5 W (half-power)   0.08%   1 W   0.05%   1 W |                                                           |         |     |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PVDD = 18 V, P <sub>O</sub> = 10 W (half-power)           | 0.1%    |     |      |

| THD+N          | Total harmonic distortion + noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PVDD = 12 V, P <sub>O</sub> = 4.5 W (half-power)          | 0.08%   |     |      |

| V <sub>n</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 W                                                       | 0.05%   |     |      |

| V <sub>n</sub> | Output integrated noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A-weighted                                                | 50      |     | μV   |

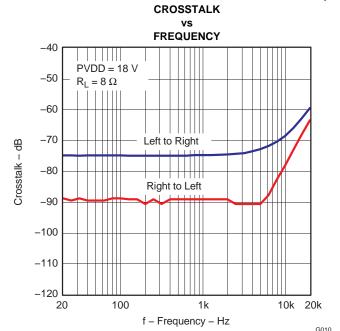

|                | Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P <sub>O</sub> = 1 W, f = 1 kHz                           | -73     |     | dB   |

| SNR            | Signal-to-noise ratio (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A-weighted, f = 1 kHz, maximum power at THD < 1%          | 101     |     | dB   |

| P <sub>D</sub> | Power dissipation due to idle losses (I <sub>PVDD_X</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P <sub>O</sub> = 0 W, 4 channels switching <sup>(2)</sup> | 0.6     |     | W    |

<sup>(1)</sup> SNR is calculated relative to 0-dBFS input level.

<sup>(2)</sup> Actual system idle losses are affected by core losses of output inductors.

**₩營物**AS5701"供应商

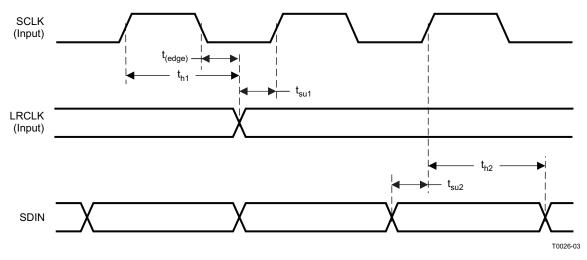

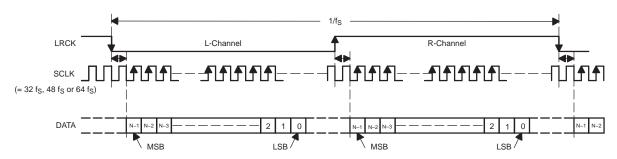

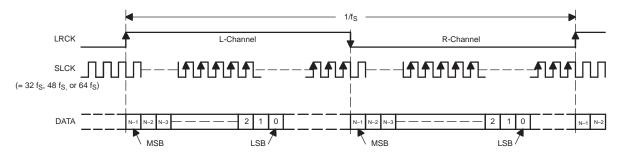

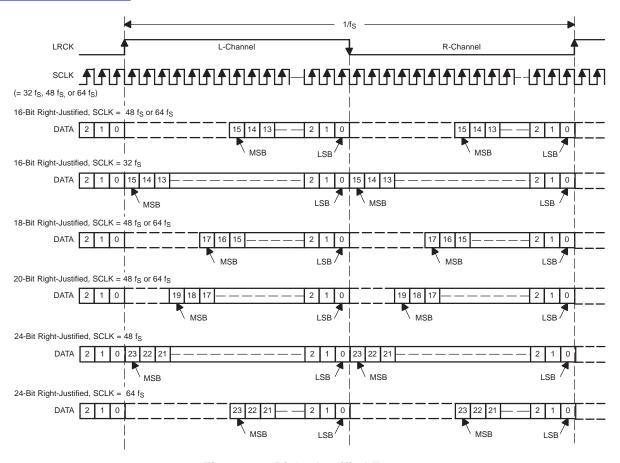

# **SERIAL AUDIO PORTS SLAVE MODE**

Serial audio ports slave mode over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                 | TEST<br>CONDITIONS     | MIN   | TYP | MAX    | UNIT           |

|---------------------|-----------------------------------------------------------|------------------------|-------|-----|--------|----------------|

| f <sub>SCLKIN</sub> | Frequency, SCLK 32 × $f_S$ , 48 × $f_S$ , 64 × $f_S$      | C <sub>L</sub> = 30 pF | 1.024 |     | 12.288 | MHz            |

| su1                 | Setup time, LRCLK to SCLK rising edge                     |                        | 10    |     |        | ns             |

| t <sub>h1</sub>     | Hold time, LRCLK from SCLK rising edge                    |                        | 10    |     |        | ns             |

| su2                 | Setup time, SDIN to SCLK rising edge                      |                        | 10    |     |        | ns             |

| h2                  | Hold time, SDIN from SCLK rising edge                     |                        | 10    |     |        | ns             |

|                     | LRCLK frequency                                           |                        | 32    | 48  | 192    | kHz            |

|                     | SCLK duty cycle                                           |                        | 40%   | 50% | 60%    |                |

|                     | LRCLK duty cycle                                          |                        | 40%   | 50% | 60%    |                |

|                     | SCLK rising edges between LRCLK rising edges              |                        | 32    |     | 64     | SCLK<br>edges  |

| (edge)              | LRCLK clock edge with respect to the falling edge of SCLK |                        | -1/4  |     | 1/4    | SCLK<br>period |

Figure 2. Slave Mode Serial Data Interface Timing

# **HARDWARE SELECT PINS**

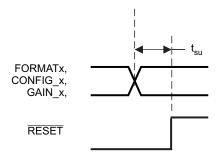

over recommended operating conditions (unless otherwise noted)

| PARAMETER                                                                  | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>su</sub> Setup time, FORMATx, CONFIG_x, GAIN_x to RESET rising edge | 100 |     |     | μS   |

Figure 3. Mode Pins Setup Time

Copyright © 2008–2010, Texas Instruments Incorporated Submit Documentation Feedback

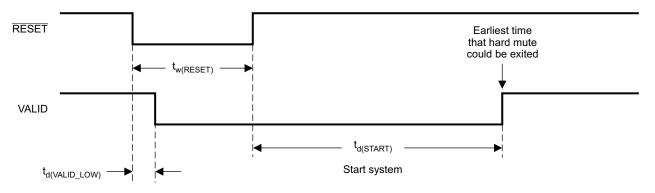

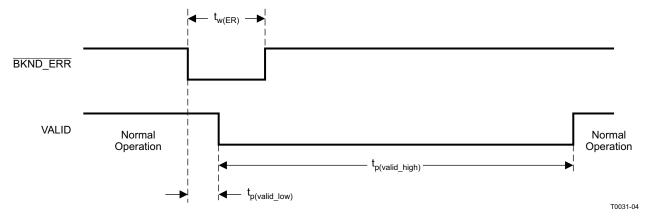

# RESET TIMING (RESET) AND POWER-ON RESET

Control signal parameters over recommended operating conditions (unless otherwise noted)

|                           | PARAMETER                                       | MIN | TYP | MAX | UNIT |

|---------------------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>d(VALID_LOW)</sub> | Time to assert VALID (reset to power stage) low |     | 100 |     | ns   |

| t <sub>w(RESET)</sub>     | Pulse duration, RESET active                    | 100 | 200 |     | ms   |

| t <sub>d(START)</sub>     | Time to start-up                                |     | 3.6 |     | ms   |

T0029-05

Figure 4. Reset Timing

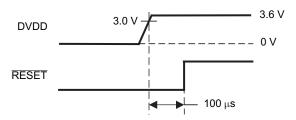

When power is applied to DVDD,  $\overline{\text{RESET}}$  must be held low for at least 100  $\mu s$  after DVDD reaches 3.0 V.

Figure 5. Power-On Reset Timing

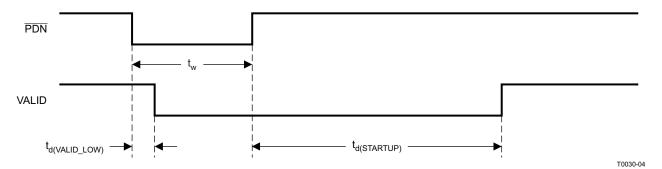

# POWER-DOWN (PDN) TIMING

Control signal parameters over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                       | MIN | TYP | MAX | UNIT |

|-------------------------|-------------------------------------------------|-----|-----|-----|------|

| $t_{d(VALID\_LOW)}$     | Time to assert VALID (reset to power stage) low |     | 725 |     | μS   |