# MGR1595NNCP1595A

# Current Mode PWM Converter for Low Voltage Outputs

The NCP1595/NCP1595A is a current mode PWM buck converter with integrated power switch and synchronous rectifier. It can provide up to 1.5 A output current with high conversion efficiency. High frequency PWM control scheme can provide a low output ripple noise. Thus, it allows the usage of small size passive components to reduce the board space. In a low load condition, the controller will automatically change to PFM mode for provides a higher efficiency at low load. Additionally, the device includes soft–start, thermal shutdown with hysteresis, cycle–by–cycle current limit, and short circuit protection. This device is available in compact 3x3 DFN package.

#### **Features**

- High Efficiency 95% @ 3.375 V

- Synchronous Rectification for Higher Efficiency in PWM Mode

- Integrated MOSFET

- Fully Internal Compensation

- High Switching Frequency, 1.0 MHz

- Low Output Ripple

- Cycle-by-cycle Current Limit

- Current Mode Control

- Short Circuit Protection

- Built-in Slope Compensation for Current Mode PWM Converter

- ±1.5% Reference Voltage

- Thermal Shutdown with Hysteresis

- Ext. Adjustable Output Voltage

- Fast Transient Response

- Low Profile and Minimum External Components

- Designed for Use with Ceramic Capacitor

- Compact 3x3 DFN Package

- These are Pb-Free Devices

#### **Typical Applications**

- Hard Disk Drives

- USB Power Device

- Wireless and DSL Modems

#### ON Semiconductor®

http://onsemi.com

DFN6 3\*3 MM, 0.95 PITCH CASE 506AH

#### MARKING DIAGRAMS

1 N1595 ALYW

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

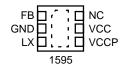

#### PIN CONNECTIONS

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

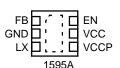

**Figure 1. Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                                                               | Symbol                             | Value                              | Unit       |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------|

| Power Supply (Pin 4, 5)                                                                                                              | V <sub>IN</sub>                    | 7.0<br>-0.3 (DC)<br>-1.0 (100 ns)  | V          |

| Input / Output Pins<br>Pin 1,3,6                                                                                                     | V <sub>IO</sub>                    | 6.5,<br>-0.3 (DC)<br>-1.0 (100 ns) | V          |

| Thermal Characteristics 3x3 DFN Plastic Package Maximum Power Dissipation @ T <sub>A</sub> = 25°C Thermal Resistance Junction–to–Air | P <sub>D</sub><br>R <sub>θJA</sub> | 1450<br>68.5                       | mW<br>°C/W |

| Operating Junction Temperature Range (Note 4)                                                                                        | T <sub>J</sub>                     | -40 to + 150                       | °C         |

| Operating Ambient Temperature Range                                                                                                  | T <sub>A</sub>                     | -40 to + 85                        | °C         |

| Storage Temperature Range                                                                                                            | T <sub>stg</sub>                   | - 55 to +150                       | °C         |

| Moisture Sensitivity Level (Note 3)                                                                                                  |                                    | 1                                  | -          |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: ESD data available upon request.

- This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM) 2.0 kV per JEDEC standard: JESD22–A114. Machine Model (MM) 200 V per JEDEC standard: JESD22–A115.

- 2. Latchup Current Maximum Rating: 150 mA per JEDEC standard: JESD78.

- 3. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

- 4. The maximum package power dissipation limit must not be exceeded.

$$P_D = \frac{T_{J(max)} - T_A}{R_{\theta,JA}}$$

**查卡的TRICAL\_SCHARACITERISTIES**立 商  $\overline{V_{IN}} = 5.0 \text{ V, } V_{OUT} = 1.2 \text{ V, } T_A = 25 ^{\circ}\text{C for typical value, } -40 ^{\circ}\text{C} \leq T_A \leq 85 ^{\circ}\text{C for min/max values unless otherwise noted)}$

| Characteristic                                                                                                                         | Symbol                | Min   | Тур   | Max      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-------|----------|------|

| Operating Voltage                                                                                                                      | $V_{IN}$              | 4.0   | -     | 5.5      | V    |

| Under Voltage Lockout Threshold                                                                                                        | $V_{UVLO}$            | 3.2   | 3.5   | 3.8      | V    |

| Under Voltage Lockout hysteresis                                                                                                       | V <sub>UVLO_HYS</sub> |       | 180   |          | mV   |

| P FET Leakage Current (Pin 5, 4) $T_A = 25^{\circ}C$ $T_A = -40^{\circ}C$ to $85^{\circ}C$                                             | I <sub>LEAK-P</sub>   |       | 1.0   | 10<br>15 | μΑ   |

| N FET Leakage Current (Pin 3, 2)<br>$T_A = 25^{\circ}C$<br>$T_A = -40^{\circ}C$ to 85°C                                                | I <sub>LEAK-N</sub>   |       | 1.0   | 10<br>15 | μА   |

| FEEDBACK VOLTAGE                                                                                                                       |                       |       |       |          |      |

| FB Input Threshold ( $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ )                                                              | $V_{FB}$              | 0.788 | 0.800 | 0.812    | V    |

| FB Input Current                                                                                                                       | I <sub>FB</sub>       |       | 10    | 100      | nA   |

| Overvoltage Protect Higher than FB Threshold (T <sub>A</sub> = 25°C)                                                                   | V <sub>OVP</sub>      | 2.0   | 5.0   | 10.0     | %    |

| THERMAL SHUTDOWN                                                                                                                       |                       |       |       |          |      |

| Thermal Shutdown Threshold (Note 5)                                                                                                    | T <sub>SHDN</sub>     | TBD   | 160   | _        | °C   |

| Hysteresis                                                                                                                             | T <sub>SDHYS</sub>    |       | 30    |          | °C   |

| PWM SMPS MODE                                                                                                                          |                       |       |       |          |      |

| Minimum ON-Time                                                                                                                        | TON <sub>MIN</sub>    |       | 100   |          | ns   |

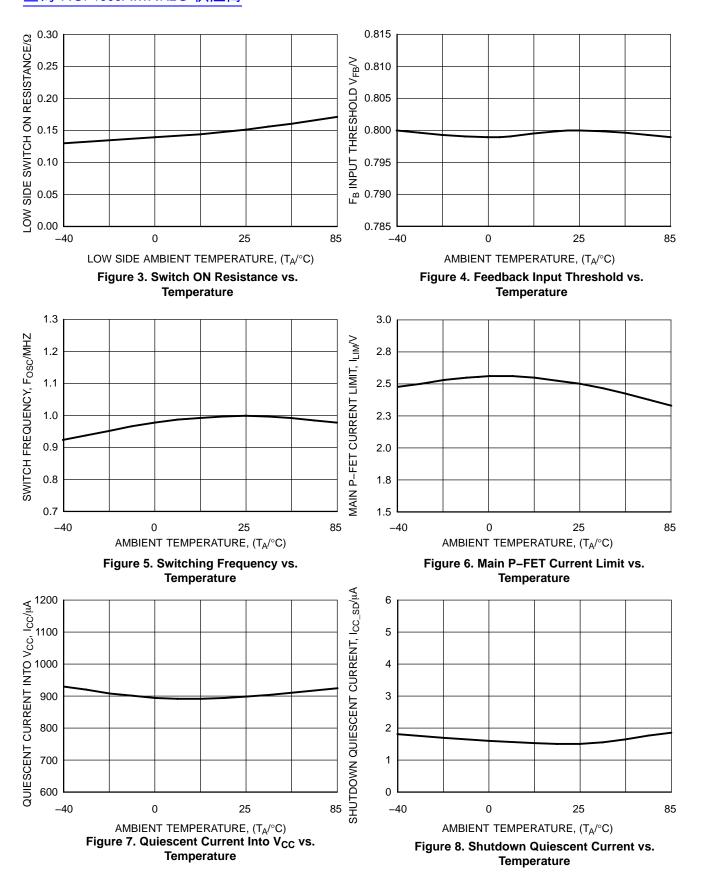

| Switching Frequency (T <sub>A</sub> = -40°C to 85°C)                                                                                   | Fosc                  | 0.8   | 1.0   | 1.2      | MHz  |

| Internal PFET ON–Resistance ( $I_{LX}$ = 100 mA, $V_{IN}$ = 5.0 V, $T_A$ = 25°C) (Note 5)                                              | R <sub>DS(ON)_P</sub> | -     | 0.2   | 0.3      | Ω    |

| Internal NFET ON–Resistance ( $I_{LX}$ = 100 mA, $V_{IN}$ = 5.0 V, $T_A$ = 25°C) (Note 5)                                              | R <sub>DS(ON)_N</sub> | -     | 0.15  | 0.22     | Ω    |

| Maximum Duty Cycle                                                                                                                     | D <sub>MAX</sub>      | -     | -     | 100      | %    |

| Soft-Start Time ( $V_{IN} = 5.0 \text{ V}$ , $V_o = 1.2 \text{ V}$ , $I_{LOAD} = 0 \text{ mA}$ , $T_A = 25^{\circ}\text{C}$ ) (Note 6) | T <sub>SS</sub>       | -     | 1.0   | -        | ms   |

| Main PFET Switch Current Limit (Note 5)                                                                                                | I <sub>LIM</sub>      | 2.0   | 2.5   |          | Α    |

| ENABLE (NCP1595A)                                                                                                                      |                       |       |       |          |      |

| Enable Threshold High (NCP1595A Only)                                                                                                  | V <sub>EN_H</sub>     | 1.8   |       |          | V    |

| Enable Threshold Low                                                                                                                   | V <sub>EN_L</sub>     |       |       | 0.4      | V    |

| Enable bias current ( EN = 0 V)                                                                                                        | I <sub>EN</sub>       |       | 500   | TBD      | nA   |

| Total Device                                                                                                                           |                       |       |       |          |      |

| Quiescent Current Into V <sub>CCP</sub> (V <sub>IN</sub> = 5 V, V <sub>FB</sub> = 1.0 V, T <sub>A</sub> = 25°C)                        | I <sub>CCP</sub>      |       | 10    |          | μΑ   |

| Quiescent Current Into V <sub>CC</sub> (V <sub>IN</sub> = 5 V, V <sub>FB</sub> = 1.0 V, T <sub>A</sub> = 25°C)                         | I <sub>CC</sub>       |       | 900   |          | μΑ   |

| Shutdown Quiescent Current into $V_{CC}$ and $V_{CCP}$ (NCP1595A Only) (EN = 0, $V_{IN}$ = 5 V, $V_{FB}$ = 1.0 V, $T_A$ = 25°C)        | I <sub>CC_SD</sub>    |       | 1.5   | 3.0      | μΑ   |

|                                                                                                                                        |                       |       |       |          | _    |

<sup>5.</sup> Values are design guarantee.6. Design guarantee, value depends on voltage at V<sub>OUT</sub>.

# 型制于WICTIONS PASSARIR TION 实应商

| Pin#     | Symbol | Pin Description                                                                                                                     |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| NCP1595  |        |                                                                                                                                     |

| 1        | FB     | Feedback pin. Part is internally compensated. Only necessary to place a voltage divider or connect the output directly to this pin. |

| 2        | GND    | Ground                                                                                                                              |

| 3        | LX     | Pin connected internally to power switch. Connect externally to inductor.                                                           |

| 4        | VCCP   | Power connection to the power switch.                                                                                               |

| 5        | VCC    | IC power connection.                                                                                                                |

| 6        | NC     | No Connection                                                                                                                       |

| NCP1595A |        | •                                                                                                                                   |

|          |        |                                                                                                                                     |

| 1 | FB   | Feedback pin. Part is internally compensated. Only necessary to place a voltage divider or connect the put directly to this pin.                                                                 |  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2 | GND  | Ground                                                                                                                                                                                           |  |

| 3 | LX   | Pin connected internally to power switch. Connect externally to inductor.                                                                                                                        |  |

| 4 | VCCP | Power connection to the power switch.                                                                                                                                                            |  |

| 5 | VCC  | IC power connection.                                                                                                                                                                             |  |

| 6 | EN   | Device Enable pin. This pin has an internal current source pull up. No connect is enable the device. With this pin pulled down below 0.4 V, the device is disabled and enters the shutdown mode. |  |

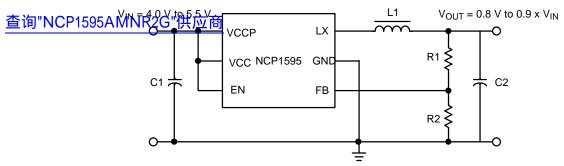

Figure 2. Detail Block Diagram

# ZEXTERNAL COMPONENT BEFERENCE DATA

| Device               | V <sub>OUT</sub> | Inductor Model                            | Inductor (L1) | C <sub>IN</sub> (C1) | C <sub>OUT</sub> (C2) | R1   | R2   |

|----------------------|------------------|-------------------------------------------|---------------|----------------------|-----------------------|------|------|

| NCP1595/<br>NCP1595A | 3.3 V            | CDC5D23 3R3 (1 A)<br>CDRH6D38 3R3 (1.5 A) | 3.3 μΗ        | 22 μF<br>22 μF x 2   | 22 μF<br>22 μF x 2    | 31 k | 10 k |

| NCP1595/<br>NCP1595A | 2.5 V            | CDC5D23 3R3 (1 A)<br>CDRH6D38 3R3 (1.5 A) | 3.3 μΗ        | 22 μF<br>22 μF x 2   | 22 μF<br>22 μF x 2    | 21 k | 10 k |

| NCP1595/<br>NCP1595A | 1.5 V            | CDC5D23 3R3 (1 A)<br>CDRH6D38 3R3 (1.5 A) | 3.3 μΗ        | 22 μF<br>22 μF x 2   | 22 μF<br>22 μF x 2    | 8 k  | 10 k |

| NCP1595/<br>NCP1595A | 1.2 V            | CDC5D23 3R3 (1 A)<br>CDRH6D38 3R3 (1.5 A) | 3.3 μΗ        | 22 μF<br>22 μF x 2   | 22 μF<br>22 μF x 2    | 5 k  | 10 k |

# 查询"NCP1595AMNR2G"供应简 CHARACTERISTICS

100  $V_{IN} = 4.0 \ V$ 90 V<sub>IN</sub> = 5.0 V 80 70 60 50 V<sub>OUT</sub> = 3.3 V 40  $L=3.3\;\mu H$  $C_{IN} = 22 \mu F$ 30  $C_{OUT} = 22 \mu F$ 20 100 1000 10000 10

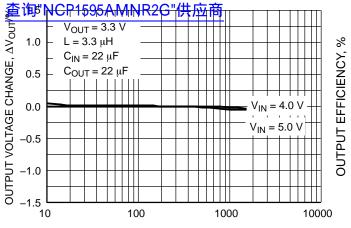

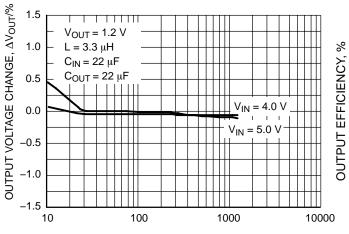

Figure 9. Output Voltage Change vs. Output Current

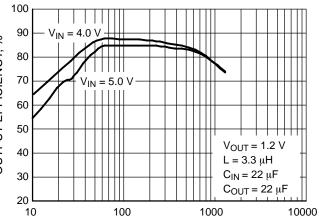

Figure 10. Efficiency vs. Output Current

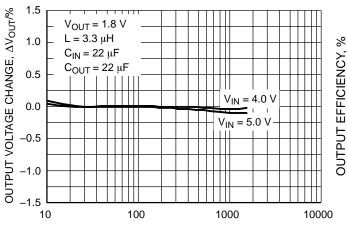

Figure 11. Output Voltage Change vs.

Output Current

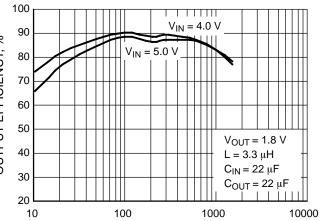

Figure 12. Efficiency vs. Output Current

Figure 14. Output Voltage Change vs.

Output Current

Figure 13. Efficiency vs. Output Current

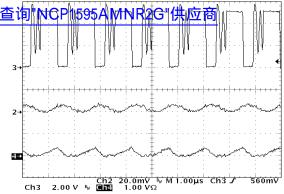

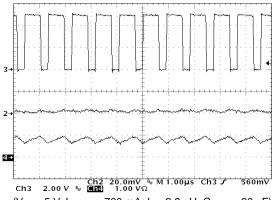

$(V_{IN}=5~V,~I_{LOAD}=100~mA,~L=3.3~\mu H,~C_{OUT}=20~\mu F)~Upper~Trace:~L_{\chi}~Pin~Switching~Waveform,~2~V~/~div.~Middle~Trace:~Output~Ripple~Voltage,~20~mV~/~div.~Lower~Trace:~Inductor~Current,~1~A~/~div.~$

Figure 15. DCM Switching Waveform for  $V_{OUT} = 3.3 \text{ V}$

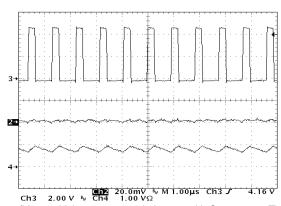

$(V_{IN}=5~V,~I_{LOAD}=100~mA,~L=3.3~\mu H,~C_{OUT}=20~\mu F)$  Upper Trace:  $L_X$  Pin Switching Waveform, 2 V / div. Middle Trace: Output Ripple Voltage, 20 mV / div. Lower Trace: Inductor Current, 1 A / div.

Figure 17. DCM Switching Waveform for  $V_{OUT} = 1.2 \text{ V}$

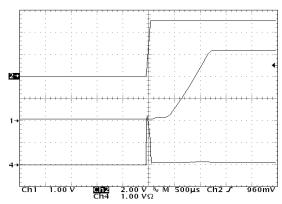

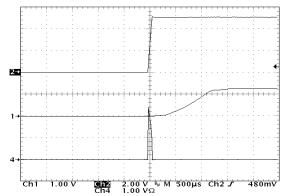

$(V_{IN} = 5 \text{ V}, I_{LOAD} = 10 \text{ mA}, L = 3.3 \mu\text{H}, C_{OUT} = 20 \mu\text{F x 2})$

Upper Trace: Input Voltage, 2 V/ div. Middle Trace: Output Voltage, 1 V/ div. Lower Trace: Input Current, 1 A / div.

Figure 19. Soft-Start Waveforms for V<sub>OUT</sub> = 3.3 V

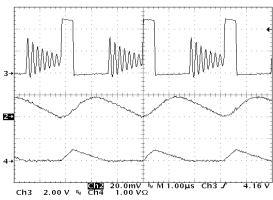

$(V_{IN}=5~V,~I_{LOAD}=700~mA,~L=3.3~\mu H,~C_{OUT}=20~\mu F)$  Upper Trace: Lx Pin Switching Waveform, 2 V / div. Middle Trace: Output Ripple Voltage, 20 mV / div. Lower Trace: Inductor Current, 1 A / div.

Figure 16. CCM Switching Waveform for  $V_{OUT} = 3.3 \text{ V}$

$(V_{IN}$  = 5 V,  $I_{LOAD}$  = 700 mA, L = 3.3  $\mu H,\,C_{OUT}$  = 20  $\mu F)$  Upper Trace:  $L_X$  Pin Switching Waveform, 2 V / div. Middle Trace: Output Ripple Voltage, 20 mV / div. Lower Trace: Inductor Current, 1 A / div.

Figure 18. CCM Switching Waveform for  $V_{OUT} = 1.2 \text{ V}$

(V  $_{IN}$  =  $\,$  5 V, I  $_{LOAD}$  = 10 mA, L = 3.3  $\mu H,\,C_{OUT}$  = 20  $\mu F$  x 2)

Upper Trace: Input Voltage, 2 V/ div. Middle Trace: Output Voltage, 1 V / div. Lower Trace: Input Current, 1 A / div.

Figure 20. Soft-Start Waveforms for V<sub>OUT</sub> = 1.2 V

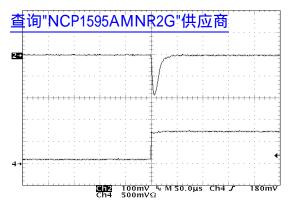

(V<sub>IN</sub> = 5 V, L = 3.3  $\mu$ H, C<sub>OUT</sub> = 20  $\mu$ F x 2)

Upper Trace: Output Dynamic Voltage, 100 mV / div.

Lower Trace: Output Current, 500 mA / div.

Figure 21. Load Regulation for V<sub>OUT</sub> = 3.3 V

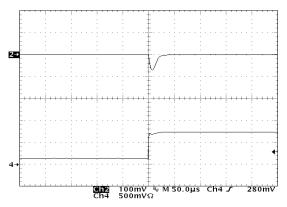

(V<sub>IN</sub> = 5 V, L = 3.3 H, C<sub>OUT</sub> = 20  $\mu$ F x 2)

Upper Trace: Output Dynamic Voltage, 100 mV / div.

Lower Trace: Output Current, 500 mA / div.

Figure 23. Load Regulation for V<sub>OUT</sub> = 1.2 V

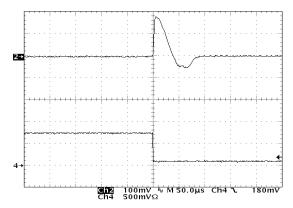

(V<sub>IN</sub> = 5 V, L = 3.3  $\mu$ H, C<sub>OUT</sub> = 20  $\mu$ F x 2)

Upper Trace: Output Dynamic Voltage, 100 mV / div.

Lower Trace: Output Current, 500 mA / div.

Figure 22. Load Regulation for V<sub>OUT</sub> = 3.3 V

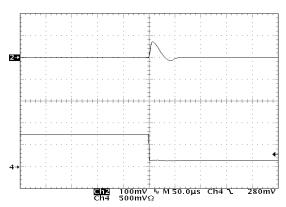

$(V_{IN} = 5 \text{ V}, L = 3.3 \text{ H}, C_{OUT} = 20 \mu\text{F x 2})$

Upper Trace: Output Dynamic Voltage, 100 mV / div.

Lower Trace: Output Current, 500 mA / div.

Figure 24. Load Regulation for V<sub>OUT</sub> = 1.2 V

# 查询"NCP1595AMNR2G"供应商

#### Introduction

NCP1595 operates as a current mode buck converter with switching frequency at 1.0 MHz. The P-Channel main switch is set by the positive edge of the clock cycle going into the PWM latch. The main switch is reset by the PWM latch in the following three cases:

- 1. PWM comparator output trips as the peak inductor current signal reaches a threshold level established by the error amplifier.

- 2. The inductor current has reached the current limit.

- 3. Overvoltage at output occurs.

After a minimum dead time, the N-Channel synchronized switch will turn on and the inductor current will ramp down. If the inductor current ramps down to zero before the initiation of next clock cycle, the regulator runs at discontinuous conduction mode (DCM). Otherwise the regulator is at continuous conduction mode (CCM). The N-Channel switch will turn off when the clock cycle starts. The duty cycle is given by the ratio of output voltage to input voltage. The duty cycle is allowed to go to 100% to increase transient load response when going from light load to heavy load.

#### **Error Amplifier and Slope Compensation**

A fully internal compensated error amplifier is provided inside NCP1595. No external circuitry is needed to stabilize the device. The error amplifier provides an error signal to the PWM comparator by comparing the feedback voltage (800 mV) with internal voltage reference of 1.2 V.

Current mode converter can exhibit instability at duty cycles over 50%. A slope compensation circuit is provided inside NCP1595 to overcome the potential instability. Slope compensation consists of a ramp signal generated by the synchronization block and adding this to the inductor current signal. The summed signal is then applied to the PWM comparator.

#### Soft-Start and Current Limit

A soft start circuit is internally implemented to reduce the in-rush current during startup. This helps to reduce the output voltage overshoot.

The current limit is set to allow peak switch current in excess of 2 A. The intended output current of the system is 1.5 A. The ripple current is calculated to be approximately 350 mA with a 3.3  $\mu H$  inductor. Therefore, the peak current at 1.5 A output will be approximately 1.7 A. A 2 A set point will allow for transient currents during load step. The current limit circuit is implemented as a cycle–by–cycle current limit. Each on–cycle is treated as a separate situation. Current limiting is implemented by monitoring the P–Channel switch current buildup during conduction with a current limit comparator. The output of the current limit comparator resets the PWM latch, immediately terminating the current cycle.

#### **Over-Voltage Protection**

Overvoltage occurs when the feedback voltage exceeds 5% of its regulated voltage. In this case, the P-Channel main switch will be reset and the N-Channel synchronized switch is turn on to sink current from the output voltage which helps to drop its feedback voltage back to the regulated voltage.

#### Thermal Shutdown

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event when maximum junction temperature is exceeded. When activated, typically at 160°C, the shutdown signal will disable the P–Channel and N–Channel switch. The thermal shutdown circuit is designed with 30°C of hysteresis. This means that the switching will not start until the die temperature drops by this amount. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended as a substitute for proper heat sinking. NCP1595 is contained in the thermally enhanced DFN package.

# 查询"NCP1595AMNR2G"供应商

#### APPLICATION INFORMATION

#### **Output Voltage Selection**

The output voltage is programmed through an external resistor divider connect from  $V_{OUT}$  to FB then to GND.

For internal compensation and noise immunity, the resistor from FB to GND should be in 10 k to 20 k ranges. The relationship between the output voltage and feedback resistor is given by:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R1}{R2}\right)$$

(eq. 1)

V<sub>OUT</sub>: Output voltage V<sub>FB</sub>: Feedback Voltage

R1: Feedback resistor from V<sub>OUT</sub> to FB. R2: Feedback resistor from FB to GND.

#### Input Capacitor selection

In the PWM buck converter, the input current is pulsating current with switching noise. Therefore, a bypass input capacitor must choose for reduce the peak current drawn from the power supply. For NCP1595, low ESR ceramic capacitor of 10  $\mu F$  should be used for most of cases. Also, the input capacitor should be placed as close as possible to the  $V_{CCA}$  pin for effective bypass the supply noise.

#### Inductor selection

The inductor parameters are including three items, which are DC resistance, inductor value and saturation current. Inductor DC resistance will effect the convector overall efficiency, low DC resistor value can provide a higher efficiency. Thus, inductor value are depend on the inductor

ripple current, input voltage, output voltage, output current and operation frequency, the inductor value is given by:

$$\Delta_{\rm IL} = \frac{V_{\rm OUT}}{L \times F_{\rm SW}} \times \left(1 - \frac{V_{\rm OUT}}{V_{\rm IN}}\right)$$

(eq. 2)

$\Delta IL$ : peak to peak inductor ripple current

L: inductor value

FSW: switching frequency

After selected a suitable value of the inductor, it should be check out the inductor saturation current. The saturation current of the inductor should be higher than the maximum load plus the ripple current.

$$\Delta_{\text{IL}(MAX)} = \Delta_{\text{IOUT}(MAX)} + \frac{\Delta_{\text{IL}}}{2}$$

(eq. 3)

$\begin{array}{ll} \Delta_{IL(MAX)} & : Maximum \ inductor \ current \\ \Delta_{IOUT(MAX)} & : Maximum \ output \ current \end{array}$

#### **Output Capacitor selection**

Output capacitor value is based on the target output ripple voltage. For NCP1595, the output capacitor is required a ceramic capacitors with low ESR value. Assume buck converter duty cycle is 50%. The output ripple voltage in PWM mode is given by:

$$\Delta_{\text{VOUT}} pprox \Delta_{\text{IL}} imes iggl( rac{1}{4 imes \text{FSW} imes \text{C}_{\text{OUT}}} + \text{ESR} iggr) ext{(eq. 4)}$$

In general, value of ceramic capacitor using 20  $\mu F$  should be a good choice.

#### ORDERING INFORMATION

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP1595MNR2G  | DFN-6<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP1595AMNR2G | DFN-6<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# 查询"NCP1595AMNR2G"供应商

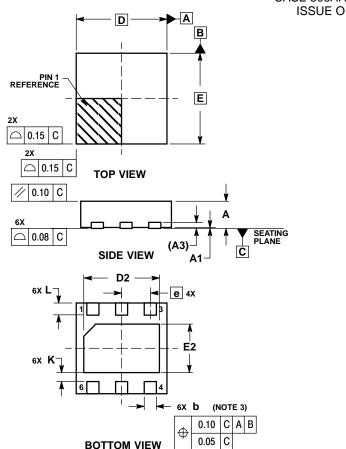

#### PACKAGE DIMENSIONS

# **DFN6 3\*3 MM, 0.95 PITCH**CASE 506AH-01

#### NOTES:

- DIMENSIONS AND TOLERANCING PER ASME Y14 5M 1994

- 2. CONTROLLING DIMENSION: MILLIMETERS.

- 3. DIMESNION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL

- 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |          |      |  |  |

|-----|-------------|----------|------|--|--|

| DIM | MIN         | MAX      |      |  |  |

| Α   | 0.80        | 0.90     | 1.00 |  |  |

| A1  | 0.00        | 0.03     | 0.05 |  |  |

| А3  | 0           | .20 REF  |      |  |  |

| ь   | 0.35        | 0.40     | 0.45 |  |  |

| D   | 3           | 3.00 BSC |      |  |  |

| D2  | 2.40        | 2.50     | 2.60 |  |  |

| Е   | 3.00 BSC    |          |      |  |  |

| E2  | 1.50        | 1.60     | 1.70 |  |  |

| е   | 0.95 BSC    |          |      |  |  |

| K   | 0.21        |          |      |  |  |

| L   | 0.30        | 0.40     | 0.50 |  |  |

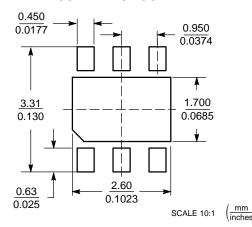

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**Europe, Middle East and Africa Technical Support:** Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5773–3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative